From: https://www.linkedin.com/pulse/ensuring-dft-integrity-functional-netlist-eco-gof-heidi-zheng-ovq4c

In functional netlist ECO, one critical risk often goes unnoticed that DFT logic can be unintentionally broken during ECO implementation. This happens because DFT logic typically remains disabled during ECO operations, and the DFT and ECO flows are managed by different teams using separate methodologies. As a result, verifying and restoring DFT integrity after an ECO can lead to long turnaround times and inefficient iteration cycles.

GOF ECO addresses this challenge with a DFT-friendly ECO flow that allows designers to make functional changes while fully preserving DFT functionality. This article introduces the DFT-aware capabilities and DFT Design Rule Checking (DRC) features built into GOF ECO.

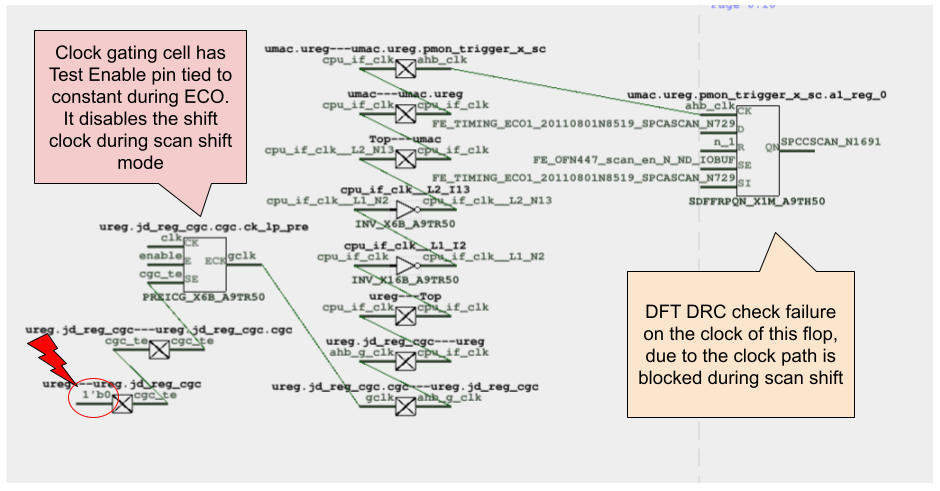

A common issue in manual ECOs is mistakenly tying the scan shift enable pin to a constant (e.g., zero) instead of connecting it to the proper scan shift control signal. Such an error can easily go undetected in traditional flows but is automatically flagged by GOF ECO’s DFT DRC, as illustrated in Figure 1.

Figure 1: Example of DFT DRC catching a scan enable connection error

GOF ECO ensures that all DFT structures remain unaffected during functional ECO implementation. It automatically sets DFT logic into inactive mode and excludes it from ECO processing using dedicated APIs such as:

set_pin_constant

set_net_constant

set_ignore_output

set_ignore_pin

This guarantees that scan logic, test points, and control signals retain their intended behavior.

When functional changes involve flops in scan chains, GOF ECO preserves scan integrity through two possible solutions:

Solution 1: Convert the destination flop to a scan-type flop (adding scan_in and scan_enable pins).

Solution 2: Insert a MUX before the D input of the destination flop, with its select signal driven by scan_enable.

Both methods maintain a clean and testable scan path.

GOF ECO ensures that all clock and reset signals are well-controlled and glitch-free in test mode. The DFT DRC verifies:

Defined DFT clocks for all scan flops

Clock and reset controllability in test mode

Absence of multiple active paths that may cause glitches

DFT test points remain fully accessible and functional after an ECO. GOF ECO:

Preserves test point connectivity

Constrains DFT signals during ECO

Checks for violations or loss of controllability through DFT DRC

For more details on DFT-friendly ECO practices, refer to the official documentation link.

GOF ECO integrates a powerful DFT Design Rule Checker that validates DFT integrity after each ECO. It automatically detects a variety of issues, including:

ERROR_MULTI_PATHS: Broken or ambiguous scan chains

ERROR_END_CONST: Scan chain ends connected to constants

ERROR_DFT_TESTPOINT_DRIVEN: Test points driven by non-controllable signals

ERROR_DFT_TESTPOINT_GLITCH: Test points with multiple active paths (potential glitches)

ERROR_CLOCK_UNDEFINED: Flops driven by undefined DFT clocks

ERROR_RESET_GLITCH / ERROR_SET_GLITCH: Reset or set signals with glitch-prone active paths

With these DFT-aware capabilities, GOF ECO provides designers a robust, automated, and DFT-safe ECO flow, reducing verification effort and ensuring testability remains intact throughout the design cycle.