Original URL: https://www.linkedin.com/pulse/enhancing-functional-eco-precision-leveraging-pre-layout-heidi-zheng-5oztc

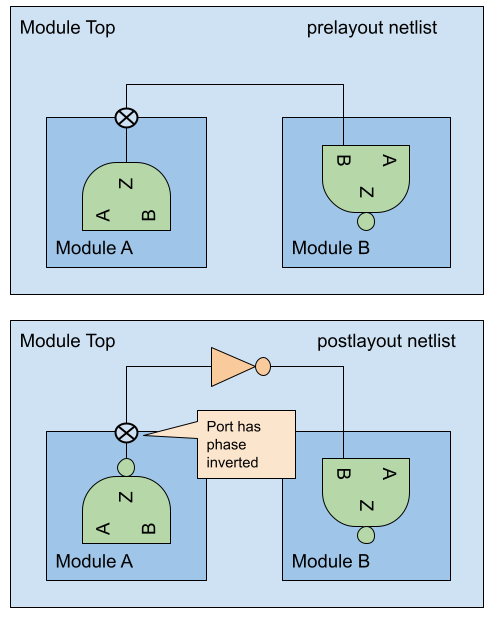

In a functional netlist ECO, detecting the boundary phase relationship between the Reference Netlist and the Implementation Netlist is crucial when ports undergo changes. During the place and route process, backend tools may alter the phases of ports. Illustrated in Figure 1, the redistribution of phase from Module A to Module B results in an inversion of the phase at the boundary of Module A between the pre-layout and post-layout netlists.

Figure 1: Port phase inverted in P&R

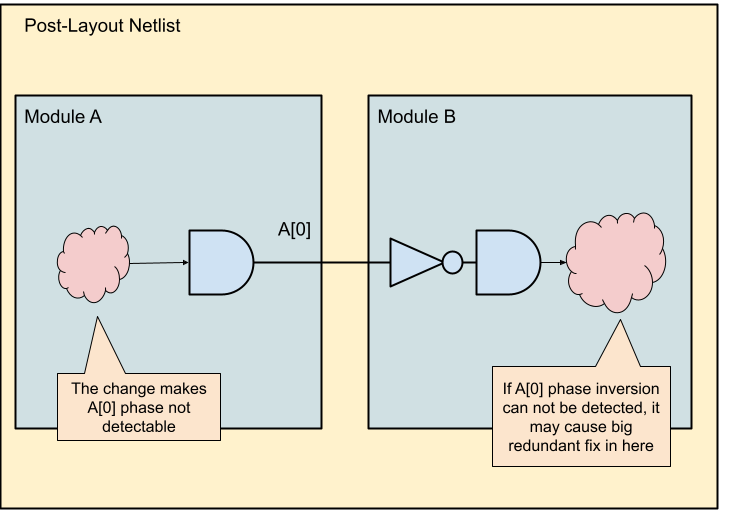

These alterations in phase within the design can significantly impact the efficacy of functional ECO. Incorrectly identifying the phase of a port can lead to unnecessary and redundant ECO patches. Moreover, modifications in the Reference Netlist can render ports inequivalent when they are part of the logic changes' fanout. For example, in Figure 2, if the logic driving port A[0] undergoes modifications in functional ECO, determining the phase relationship solely by comparing the Reference Netlist and the Implementation Netlist becomes not possible. By default, the ECO tool might assume the phases are equal, potentially resulting in extensive redundant fixes downstream in Module B's logic.

Figure 2: Port phase optimization affects ECO quality

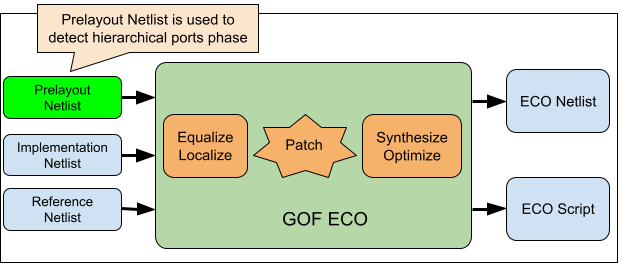

One solution to address this issue is by utilizing the original pre-layout netlist. By comparing it with the Implementation Netlist during ECO, any differences can be readily identified, including phase changes in ports. The phase change details from the Pre-layout Netlist and the Implementation Netlist can then inform the ECO process when comparing the Reference Netlist to the Implementation Netlist. This approach helps prevent redundant fixes resulting from inaccurate phase detection.

Figure 3: GOF ECO reads in original pre-layout netlist to determine port phase

The GOF ECO script provided below incorporates the -ori_syn option within the read_design command to enable the inclusion of the pre-layout netlist, facilitating the identification of port phase changes.

read_library("tsmc.lib");

read_design('-ref', "reference.gv");

read_design('-imp', "implementation.gv"); # Full post layout netlist

read_design('-ori_syn', "pre_layout.gv"); # Full prelayout, equal to implementation.gv

set_top("SOC_TOP");

fix_design;

report_eco();

write_verilog("ecoed.gv"); # Full post layout netlist after ECOGOF platform integrates four functional components: ECO, Formal, LEC and Debug. To access detailed information about GOF, please visit the website https://nandigits.com