在芯片设计的漫长征途中,验证(Verification)往往占据了整个研发周期70%以上的时间和资源。如何确保芯片在流片(Tape-out)前实现“零缺陷”?基于行业主流的验证体系,下面为您解析芯片的五大核心验证技术。

动态仿真(Dynamic Simulation)是芯片验证中最基础、也是应用最广泛的手段。它的核心逻辑非常直观:工程师搭建一个虚拟的验证环境(Testbench),将设计代码(DUT)置于其中,通过施加各种激励信号,观察芯片的输出反馈是否符合预期。这就好比在一个虚拟的实验室里,用软件模拟电流在电路中的流动。

在实际工程中,事件驱动仿真(Event-based Simulation)是最常用的模式。仿真器会精准捕捉每一个信号电平的变化(事件),无论是时钟上升沿还是数据的翻转,甚至包括电路中的微小延时和毛刺。这种方法的优势在于“所见即所得”,配合UVM(通用验证方法学),工程师可以拥有极高的调试可视性,能够精确定位到任何一行代码的逻辑错误。

然而,随着芯片规模的扩大,完全模拟每一个电平跳变会变得极慢。为了解决性能瓶颈,基于周期的仿真(Cycle-based Simulation)应运而生。它采取了一种更宏观的视角,忽略时钟周期内部的信号波动,只计算每个时钟边缘时的电路状态。虽然这牺牲了部分时序细节,无法检测异步电路的亚稳态问题,但它将仿真速度提升了10到100倍,非常适合在功能验证的中后期进行大规模的回归测试(Regression)。

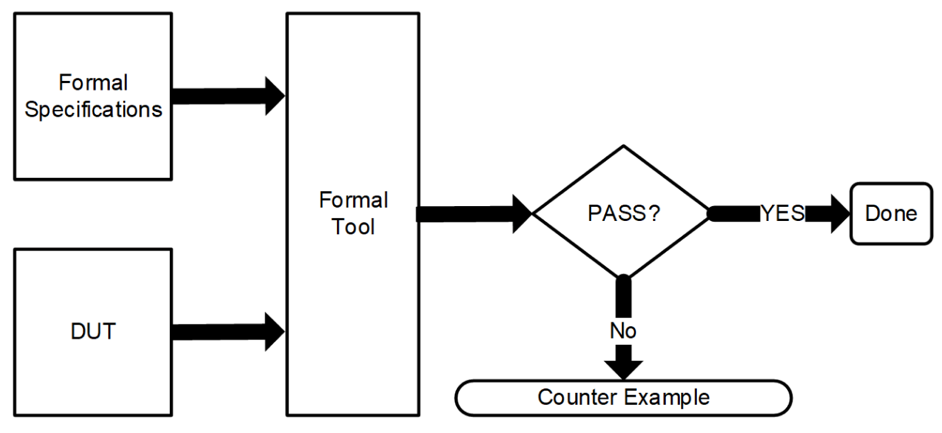

动态仿真是通过“随机尝试”来寻找Bug,而形式验证(Formal Verification)就是一种通过数学方法验证设计是否满足规范的技术。它不依赖测试矢量或仿真,而是通过对所有输入组合进行逻辑证明,确保设计在任何场景下都能正确工作。相比之下,传统仿真只能覆盖有限的测试情况,难以稳妥揭露各种边界和角落情况。

属性检查 Property Checking:

用SystemVerilog中的断言定义设计必须满足的行为,形式工具进行证明或反例查找。

等价性检查 Equivalence Checking:

比较设计前后不同阶段(例如RTL与综合netlist)是否功能等效,确保优化未破坏意图。

模型检查 Model Checking:

构建设计模型,再通过穷举状态空间验证是否满足所有指定属性。

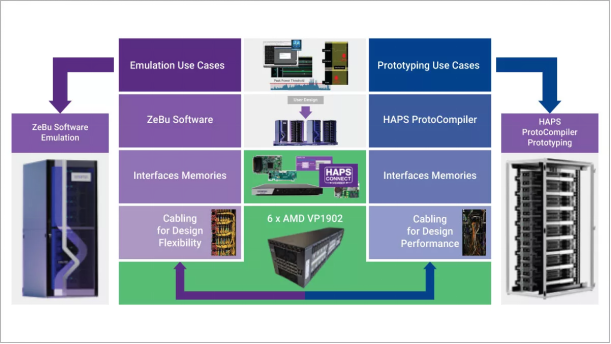

当验证对象上升到CPU、GPU或手机SoC这种亿门级规模时,传统的软件仿真速度只有几Hz,启动一次操作系统可能需要数周时间,这在分秒必争的市场竞争中是不可接受的。此时,我们就需要硬件仿真器(Emulator)。

硬件仿真(Emulation)的本质是用专门设计的硬件(通常是海量的定制处理器阵列或商用FPGA阵列)来模拟目标芯片的行为。它将RTL代码编译到底层硬件架构中,从而实现比软件仿真快1000倍甚至100万倍的运行速度。

这种技术的最大价值在于实现了验证流程的左移”(Shift-Left)。在芯片还未流片回来之前,软件团队就可以利用Emulator启动操作系统、调试驱动程序甚至运行真实的应用程序。虽然Emulation设备昂贵,但它能在几小时内完成软件仿真需要几年才能跑完的测试量,是高端芯片公司缩短上市周期的核心利器。

FPGA原型验证(FPGA Prototyping)与Emulation看起来很像,都是用硬件跑代码,但两者的侧重点完全不同。Emulation侧重于“调试”,保留了强大的波形抓取和断点功能;而FPGA原型验证则侧重于“速度”和“真实接口连接”。

通过将ASIC代码移植到现成的FPGA开发板上,我们可以获得接近真实芯片的运行频率(通常可达数十MHz到上百MHz)。这使得我们可以直接将验证平台连接到真实的物理接口上——比如直接插上USB设备、连接真实的网线或摄像头进行测试。这种实战演练是发现软硬件协同Bug的最后一道防线,也常被用于向客户展示早期的Demo原型。

前面介绍的方法都在验证芯片“功能对不对”,而静态时序分析(Static Timing Verification)则是要确保芯片“跑得稳不稳”。它不进行动态的逻辑模拟,而是通过算法穷举分析电路中所有的逻辑路径,计算信号传播的延迟。

STA的核心任务是检查建立时间(Setup Time)和保持时间(Hold Time)是否满足工艺库的要求。这就好比检查高铁线路的调度,必须确保信号在规定的时间内到达下一站,既不能晚点(Setup违例),也不能早到导致数据错乱(Hold违例)。这是芯片后端设计(Back-end)中最重要的签核(Sign-off)标准,任何时序违例都可能导致芯片流片后无法工作或频率达不到标称值。

“芯想事珹”,先进制程IC设计与SoC定制技术交流分享平台。