前些天用AI写了一个fifo《我用CodeBuddy写了一个async fifo》,今天写了一个testbench仿了一下,居然有发现了两个bug。

第一个是语法错,寄存器定义成了wire类型。

wire [ADDR_WIDTH:0] wr_ptr_gray_sync1;

wire [ADDR_WIDTH:0] wr_ptr_gray_sync2;

wire [ADDR_WIDTH:0] rd_ptr_gray_sync1;

wire [ADDR_WIDTH:0] rd_ptr_gray_sync2;

always @(posedge wr_clk or negedge wr_rst_n) begin

if (!wr_rst_n) begin

rd_ptr_gray_sync1 <= {ADDR_WIDTH+1{1'b0}};

rd_ptr_gray_sync2 <= {ADDR_WIDTH+1{1'b0}};

end else begin

rd_ptr_gray_sync1 <= rd_ptr_gray;

rd_ptr_gray_sync2 <= rd_ptr_gray_sync1;

end

end

always @(posedge rd_clk or negedge rd_rst_n) begin

if (!rd_rst_n) begin

wr_ptr_gray_sync1 <= {ADDR_WIDTH+1{1'b0}};

wr_ptr_gray_sync2 <= {ADDR_WIDTH+1{1'b0}};

end else begin

wr_ptr_gray_sync1 <= wr_ptr_gray;

wr_ptr_gray_sync2 <= wr_ptr_gray_sync1;

end

end

第二个bug是fifo的满标志没有拉高。

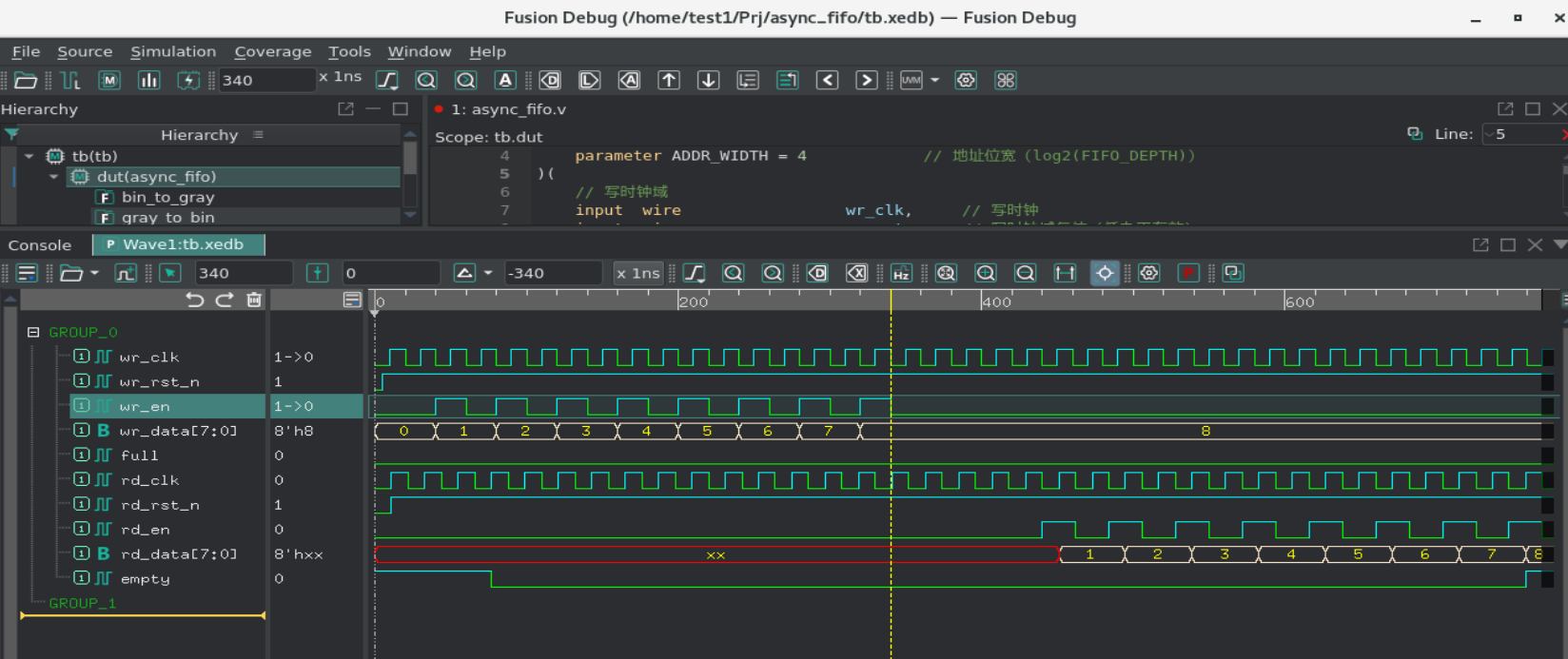

写了一个简单的testbench,编译仿真,得到波形如下。深度为8的fifo,在写完第8个数据后,满标志full并没有拉高。

galaxsim -R \

-sverilog \

-timescale=1ns/1ps \

-debug_access \

-f file.lst

空标志没有问题,有数据写进来,empty拉低,读完8个数据后,empty又回到高电平。

assign full_int = (wr_ptr_gray == {~rd_ptr_gray_sync2[ADDR_WIDTH:ADDR_WIDTH-1],

rd_ptr_gray_sync2[ADDR_WIDTH-2:0]});

assign empty_int = (rd_ptr_gray == wr_ptr_gray_sync2);

具体啥问题下次再说了。