rtl有没有语法错,有时候动态仿真真靠不住。如果靠dc综合来排错有点太靠后期了。用spyglass来静态检查rtl到是个不错的方法,速度快,还全面。下面介绍用spyglass检查rtl语法的入门级操作。

一、打开spyglass,读入rtl

直接敲命令spyglass就行。

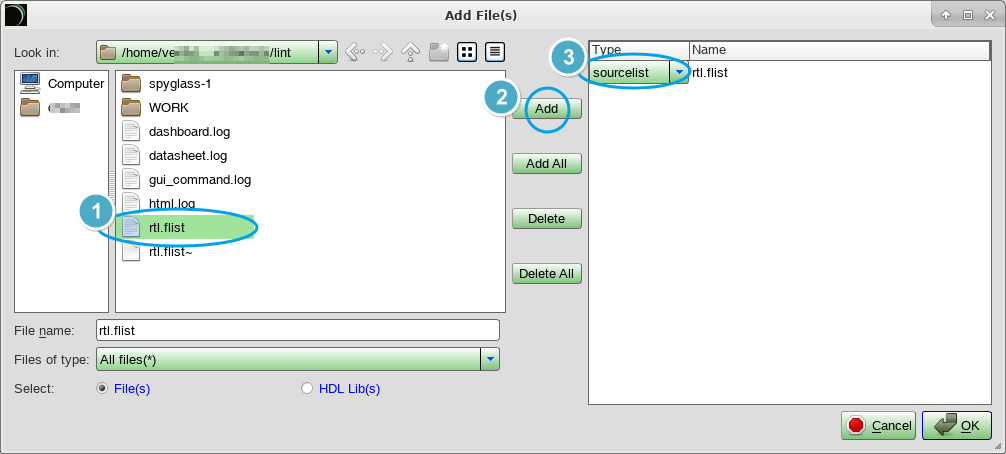

点左侧按钮“Add File”,选中rtl file list(注意:file list中的路径要相对当前路径有效),点“Add”加到右侧,再选择文件类型为“sourcelist”,最后点“OK”。

当然如果源文件不多,也可以选中每一个verilog文件,分别添加。

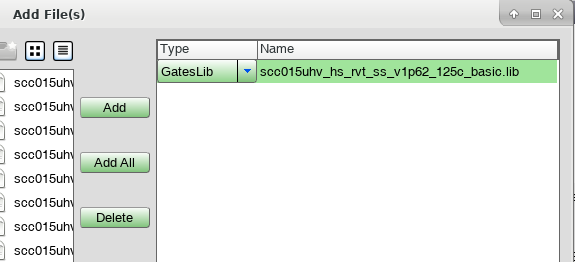

二、读入stdcell库

如果rtl中例化了stdcell、sram等IP,则需要再读入他们的lib库(corner不重要,任意选一个就行,比如ss_v1p62_125c)。还是通过“Add File”,选择xxx.lib后,type自动识别到GatesLib。

注:不需要读stdcell .v的仿真模型。

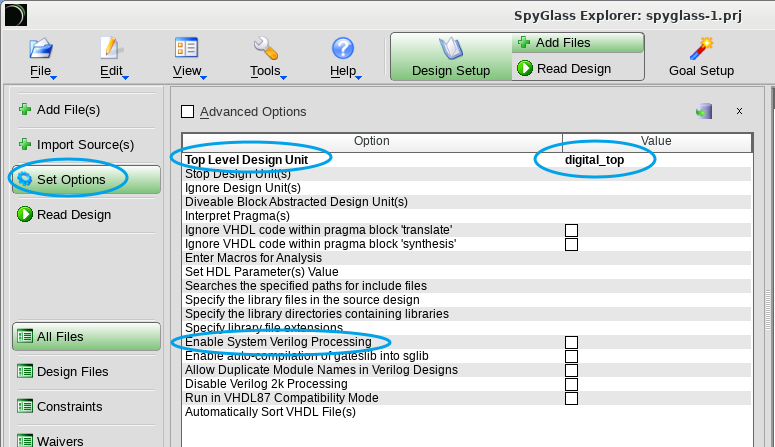

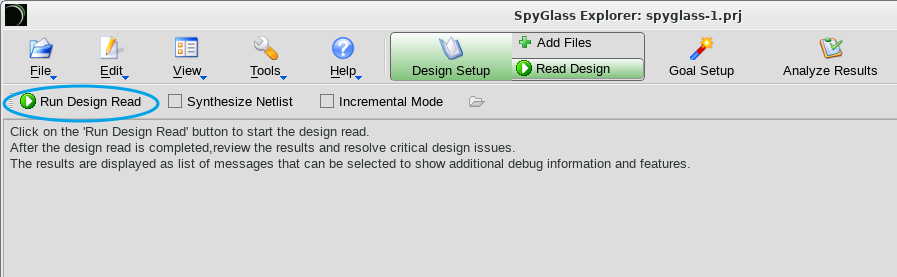

三、设置顶层模块名等后进行“Read Design”

左侧点“Set Options”,top level design unit的value处填入顶层模块名。根据需要可能需要使能systemverilog语言,默认是关闭的。其它option看实际需要。最后点左侧“Read Design”->“Run Design Read”进行编译RTL。

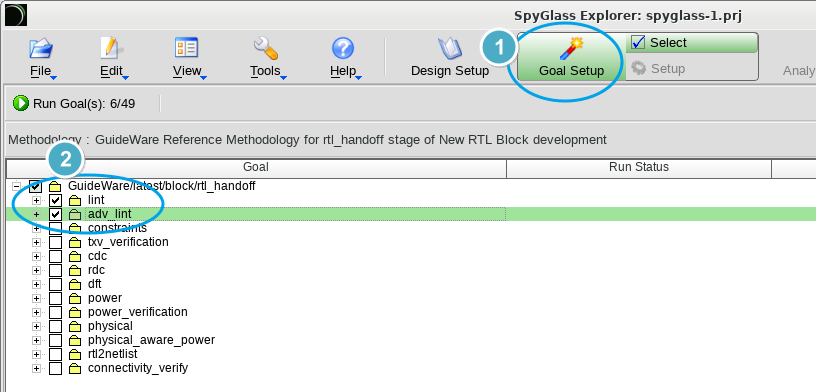

四、设置语法检查项,进行语法检查

点击顶部工具条“Goal Setup”,勾上lint、adv_lint,点“Run Goal”。等片刻,就可以生成语法检查报告,再根据warning和error进行排查和修改RTL。

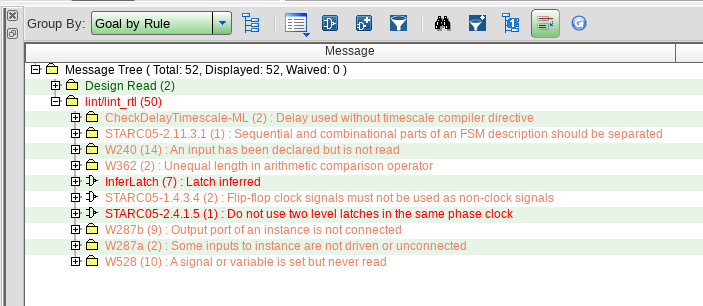

五、哪些warning和error应该特别注意?

下面总结了几点要特别注意的问题:

| 序号 | 检查项 | 检查的原因或者影响 |

|---|---|---|

| 1 | 多驱动 | 正常数字逻辑不会带多驱,很可能代码写错了。可能造成内部短路。 |

| 2 | 输入悬空 | 一般是忘记赋值,或者接线了。大概率会造成功能缺失。 |

| 3 | 组合逻辑循环 | 一般是代码写错,正常逻辑不会有这种循环。 |

| 4 | latch | 很可能是组合逻辑或者状态机忘记else或default状态。会造成时序更复杂,电路容易不稳定。 |

最后,需要说明的是动态仿真、静态lint、综合工具编译报错都是语法检查的手段,实际项目中几种方法需要同时使用,才能保证尽量少出bug。

分享数字集成电路设计中的经验和方法。分享让工作更轻松。