Coral NPU 是由谷歌研究团队设计的开源 IP,可免费集成到面向可穿戴设备(如耳机、增强现实 (AR) 眼镜和智能手表)的超低功耗系统芯片(SoC)中。Coral 是一种神经处理单元(NPU),也称为 AI 加速器或深度学习处理器。

Coral NPU 是一种高效的机器学习推理硬件加速器。它通过降低处理器(ALU)操作的控制开销以及数据在内存层次结构中传输的距离,从而减少 SoC 的能耗。

Coral NPU 的指令集针对机器学习进行了领域优化,具有面向特定应用的算术运算和数据路径,能够高效地为计算引擎提供数据。

这种专门设计与传统 CPU 形成对比。CPU 具有高度的灵活性,提供通用的指令集、可访问的内存模型以及统一的软件 API。这使它们能够使用标准编译器和工具,利用广泛的生态系统投资。然而,这种通用可编程性使 CPU 在人工智能方面效率低下,每焦耳计算能力远低于专用设计,因为它们缺乏领域专用性。

另一方面,较旧的机器学习加速器并不稳健。虽然它们通常效率很高,但编程困难,有限的计算资源复用能力,且对函数调用执行的支持较差。相比之下,Coral NPU 被设计为既高效又稳健。它是一种节能、可用 C 语言编程的加速器,能够解决这种权衡问题。

Coral NPU 基于 32 位 RISC-V 指令集架构(ISA)。可扩展的行业标准 RISC-V ISA 使开发者能够创建优化且可定制的计算解决方案,从定制处理器到硬件/软件协同设计。通过在 ISA 上扩展自定义计算功能,Coral NPU 成为运行机器学习推理操作的理想硬件加速器,例如:

图像分类

人物检测

姿态估计

Transformer(神经网络)

Coral NPU使AI硬件采用以软件为中心的方法,同时在运行于CPU、GPU和NPU上的AI工作负载之间提供统一的编程模型。RISC-V通过允许选择适当的标准认证扩展(例如向量和矩阵操作),实现针对特定应用和工作负载的领域特定定制。有关RISC-V规范的完整列表,请参见官方RISC-V规范。

本 Coral NPU 文档提供:

面向商用硅设计师和学术界的硬件参考和 IP 集成指南

使用软件工具链在硬件上编译和运行机器学习模型的指导

Coral NPU 的开源代码库可在 GitHub 上获取。

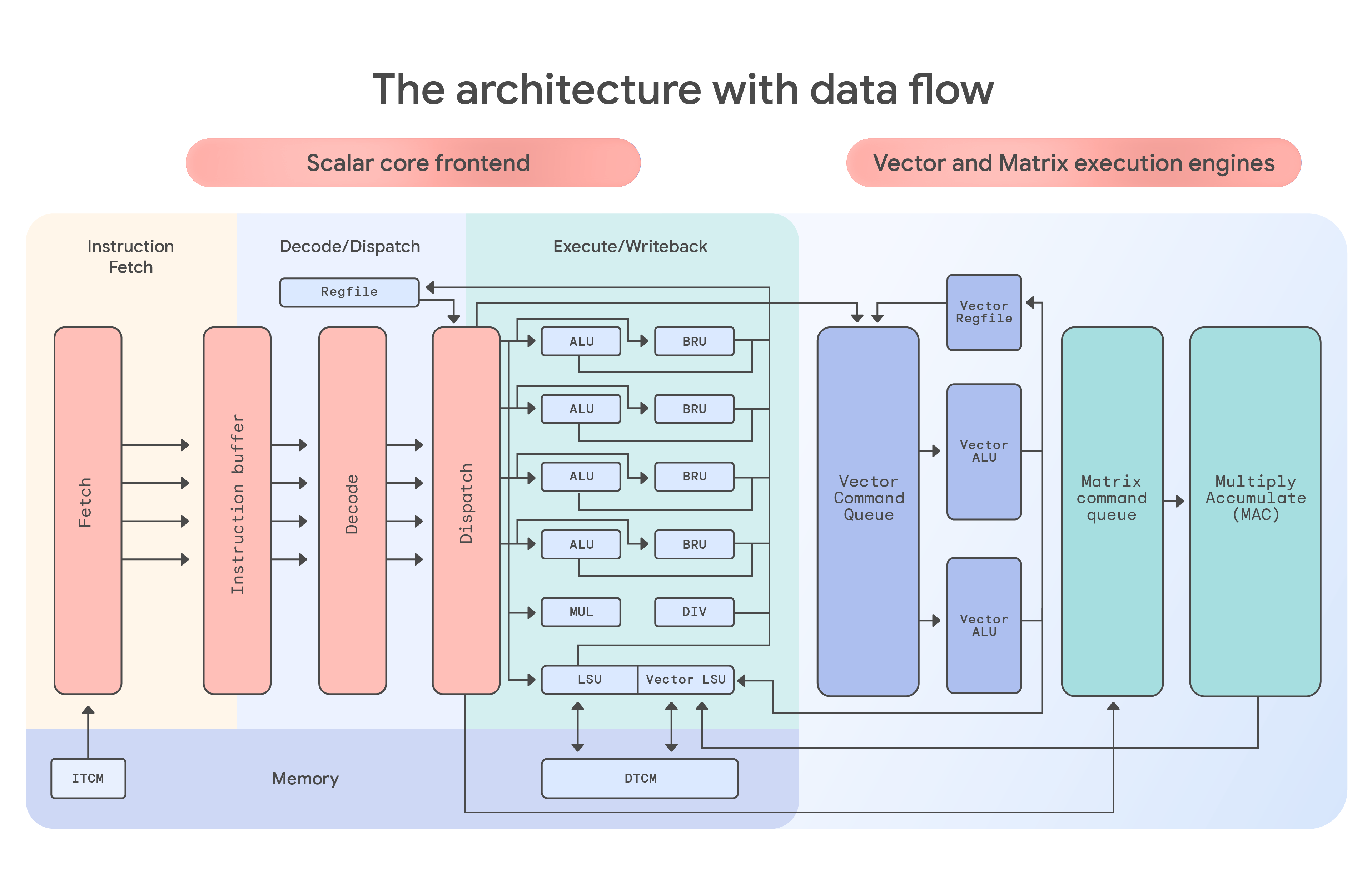

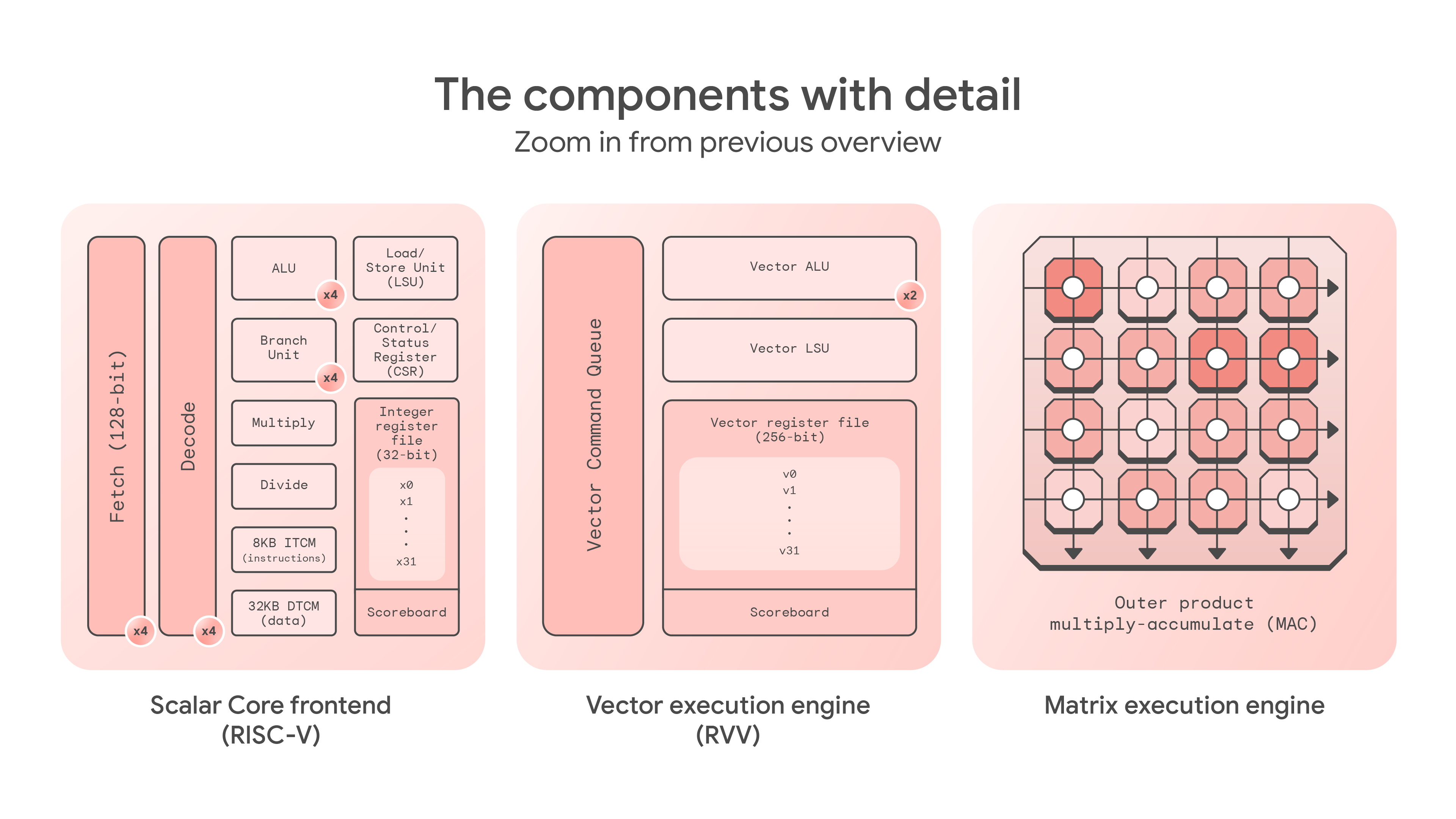

Coral NPU 包含三个协同工作的不同处理器组件:矩阵、向量(SIMD)和标量。这里 SIMD(单指令多数据)和向量这两个术语是同义使用的。

| 子部件 | 描述 |

|---|---|

| Fetch / decode | 获取并解释程序指令 |

| Scoreboard | 管理指令依赖,以防冲突 |

| ALU | 算术逻辑单元 |

| BRU | 分支单元:控制程序的流程(循环、跳转) |

| LSU | 加载/存储单元:在寄存器和内存之间移动数据 |

| CSR | 控制/状态寄存器 |

| ITCM | 指令紧耦合存储器 |

| DTCM | 数据紧耦合内存 |

| SIMD | 单指令、多数据 |

| MAC | 乘加运算执行引擎 |

Coral NPU 提供以下顶级功能集:

RV32IMF_Zve32x RISC-V 指令集

应用程序和操作系统内核的 32 位地址空间

四级处理器,顺序调度,乱序退休

四路标量,两路矢量调度

128 位 SIMD,256 位(未来)流水线

8 KB ITCM 内存(用于指令的紧耦合内存)

32 KB DTCM 内存(用于数据的紧耦合内存)

两种内存均为单周期延迟 SRAM,比缓存内存更高效

AXI4 总线接口,可作为主设备和从设备与外部内存交互,并允许外部 CPU 配置 Coral NPU

支持 GNU 调试器(GDB)

Coral NPU 的 RV32IMF_Zve32x 规范包括对 RISC-V ISA 基础的以下扩展:

RV32IM – 这个标签表示 RISC-V 32 位基础指令集,包含 I(整数)和 M(乘法、除法)扩展(操作)

有关已批准和正在进行的扩展的完整列表,请参阅 RISC-V 规范;这里给出部分列表以便快速参考

I – 基础整数指令集

M – 整数乘法与除法标准扩展

F – 单精度浮点数标准扩展

V – 向量操作标准扩展;参见 RISC-V 规范 PDF

Zve32x – V(向量操作)的子集,请参考 RISC-V 提议规范中的“Zve* 嵌入式处理器向量扩展”

标量核心特性

RV32IM 前端,用于驱动 ML 和 SIMD 后端的命令队列

三十一 个 32 位标量寄存器(x1 – x31),x0 固定为零

每个 RV32_Zicsr 的各种控制和状态寄存器(CSR)

向量执行引擎特性

支持数据宽度 8, 16, and 32 bits

31个 256-bit 向量寄存器 (v0 – v31)

例如 int32 x 8-bit

8 x 8 x 32-bit 累加器 (acc<8><8>)

矩阵执行引擎功能

量化外积乘累加 (MAC) 引擎

4 x 8 位乘法累计到 32 位累加器

每周期 256 次 MAC

Coral NPU 的自定义向量和矩阵计算功能将在未来 RISC-V 标准可用时进行迁移以遵循标准。

下面显示了 Coral NPU 架构的更详细视图。