一、在vcs仿真脚本里增加统计代码覆盖率的选项

在vcs里增加-cm选项,把需要统计的代码覆盖率类型选上。常见的代码覆盖率类型有:

line:行覆盖率

cond:条件覆盖率

fsm:状态机覆盖率

tgl:toggle覆盖率

branch:分支覆盖率

assert:断言覆盖率

另外,通过-cm_hier指定到rtl top层,只统计RTL部分,排除掉验证环境、仿真model等模块。

vcs

-cm line+cond+fsm+tgl+branch+assert

-cm_hier cm_hier.file

+tree tb.u_chip_top.u_digital_top

设置好覆盖率option之后,仿真log的末尾有提示仿真过程中记录了哪些覆盖率类型。

---------------------------------------------------------------------------

VCS Coverage Metrics: during simulation line, cond, FSM, branch, tgl was monitored

---------------------------------------------------------------------------

V C S S i m u l a t i o n R e p o r t

二、用urg合并覆盖率

urg是vcs自带的一个工具,用来合并覆盖率数据。下面是一个使用例子:

urg -full64 -dbname merged.vdb/test -dir \

tc_testcase1/simv.vdb \

tc_testcase2/simv.vdb \

tc_testcase3/simv.vdb

也可以借助find ... | xargs,

find . -name "simv.vdb" | xargs urg -full64 -dbname merged.vdb/test -dir

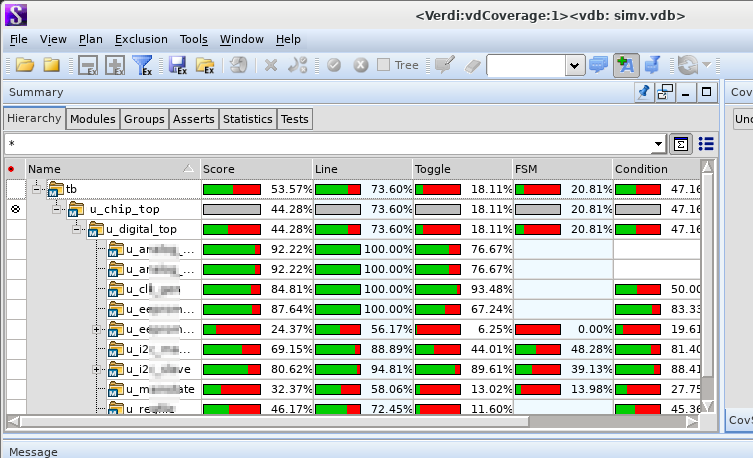

三、用verdi查看覆盖率报告

1、verdi直接查看单个case的覆盖率

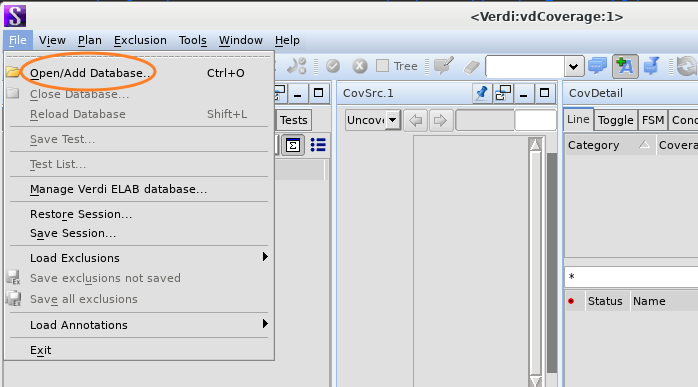

对于单个case,可以直接用命令verdi -cov先打开gui,再点菜单上的Open/Add Database...,选择当前目录下的simv.vdb,就可以看到覆盖率报告了。

2、verdi直接查看多个case的vdb,verdi会自动合并

对于多个testcase,每个case只仿真了芯片的部分功能,真实覆盖率需要合并后查看。

可以写个脚本,把多个case下的simv.vdb用-covdir选项拼接到一起,下面是一个例子:

import os

tclist = ['tc_testcase1', 'tc_testcase2', 'tc_testcase3']

cmd = verdi -cov

for tc in tclist:

cmd += ' -covdir' + tc + '/simv.vdb'

os.system(cmd)

运行脚本就可以看到合并之后的代码覆盖率报告了。

3、verdi查看第二步手工合并后的merged.vdb

verdi -cov -covdir merged.vdb

4、也可以用dve查看(新版本的vcs不自带dve,需要单独安装dve)

dve -full64 -cov -covdir merged.vdb