一、把dc、icc2、fc产生svf转成文本格式

1、综合时设置记录vsdc

2、如果综合已经做完了,没法重新跑,也可以手工把二进制svf转成文本格式

编写一个tcl脚本:

然后在formality里执行这个tcl脚本

3、在做formality时,也会当前目录下自动生成一个formality_svf/svf.txt。

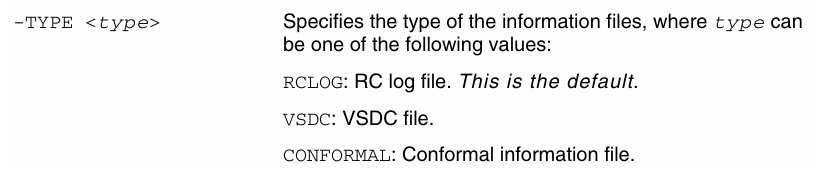

二、在cadence conformal lec里读入文本格式的svf

这是cadence conformal的命令帮助,其中-type vsdc即是读取synopsys dc的svf文件。

其中,选项-report可以报出svf读进来后哪些规则生效了。

三、文本格式svf的其它作用

1、文本格式的svf,除了提供给conformal,也可以提供其它工具,比如nandigits的gof lec和gof eco,阿卡思的AveCEC。

2、如果rtl有修改,或者网表有eco,这时的svf就不一定准确反映真实的电路。我们可以转成svf.txt,按需修改后,再用formality做lec。

四、一些说明

需要说明的是,synopsys svf描述的是ref(golden)变成imp(revised)的规则、变动、优化项。

在icc2、fusion compiler里会对网表优化,所以在icc2和fusion compiler里应当要记录svf。这样rtl比apr网表更容易pass。

如果是icc,工具并不支持记录svf文件,因此建议关闭icc的一些高级优化选项。要么就可能需要手工编写这些优化规则来指导formality了。比如,apr里进行了multi-bit flip-flop的de-bank、rebank。避免在apr阶段进行ungroup,甚至打散整个层次,这会造成formality的巨大麻烦。