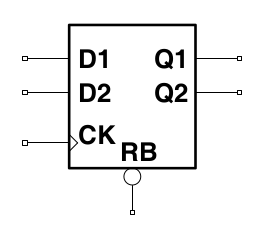

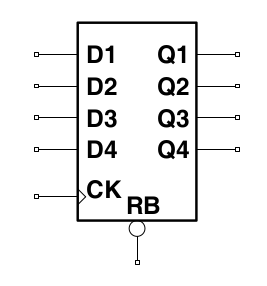

先进工艺里,或者少数老工艺里,有一种flipflop,把2个或多个dff做在一起了。如下图,左侧是2 dff合并,右侧是4 dff 合并。

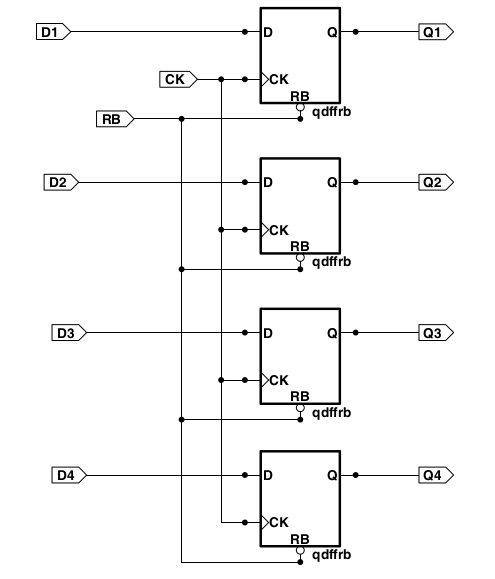

逻辑上等价于下面的电路:

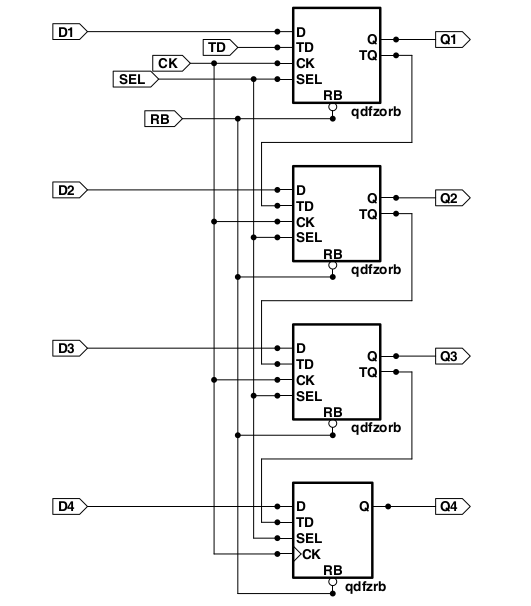

如下图,在multibit flipflop电路里已经把chain串好了。如下图:

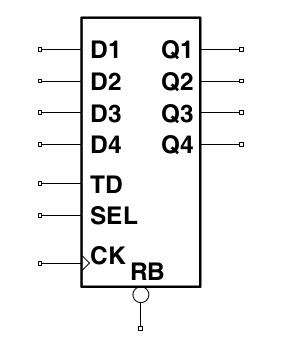

所以,multibit flipflop的符号,只需要一个TD(SI, scan data input),而不是4个TD。如下:

multibit flipflop的主要优势是功耗。但对timing不友好,实际timing会差一些。

另外面积也会稍小。下面是某库中的面积对比。可见2DFF高度是两倍,4DFF高度是4倍,但宽度稍小。

| CELL | Width | Height |

|---|---|---|

| QDFFRBTDX1 | 8.36 | 2.66 |

| Q2DFFRBTDX1 | 7.98 | 5.32 |

| Q4DFFRBTDX1 | 7.98 | 10.64 |

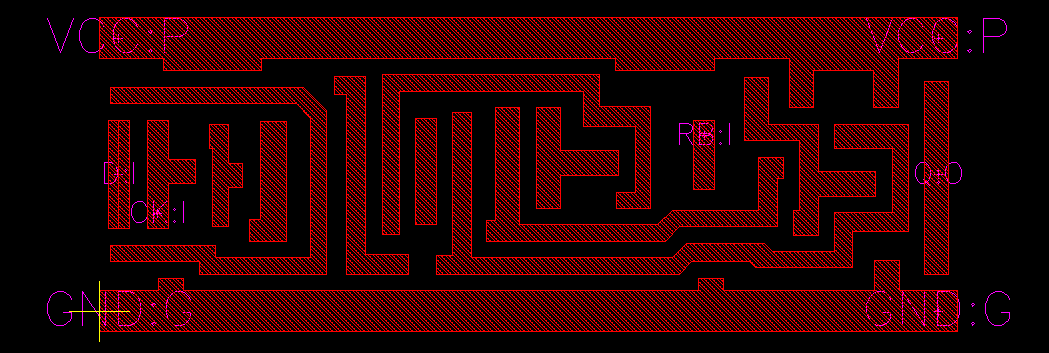

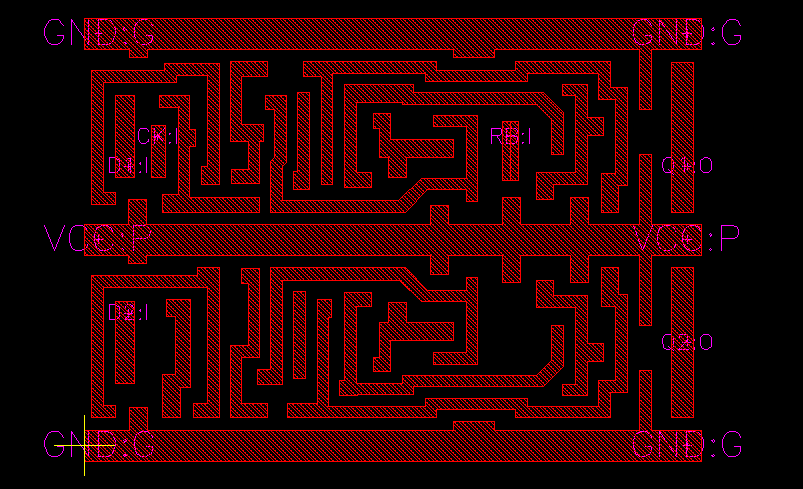

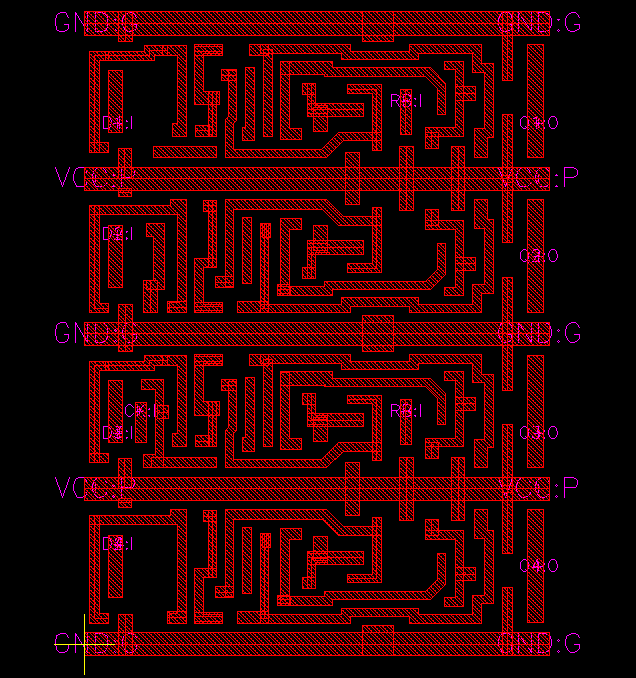

我们看到高度不同,是单DFF的多倍高度。从下图gds Metal1上来看,也能看出来。要注意的是,2DFF和4DFF的VCC和GND与单bit DFF是兼容的,仍然是VCC和GND每行交替。在做floorplan和create row时,需要按照兼容的方式创建。

单bit DFF

2bit DFF

4bit DFF

查看工艺lib库带不带multibit FF的方法是用grep,比如grep 'ff_bank'关键字。

在综合脚本开头,读入RTL之前,设置option:

在compile之前设置multibit的mode,如下:

compile后可以report检测multibit的结果:

在开启multibit选项后,必须要记录svf文件。在dc脚本的一开头设置svf,如下:

svf文件里记录着多个dff的合并方式,用guide_multibit来描述。用formality做等价性验证时需要先读入svf指导文件,告诉formality,在综合时是如何优化multibit flipflop的。