Icarus Verilog是由Stephen Williams开发的Verilog仿真工具,官网http://iverilog.icarus.com,代码开源在https://github.com/steveicarus/iverilog 。

在github仓库里,有一份developer quick start文档,我们就从这个文档来看看Icarus Verilog是如何工作的。

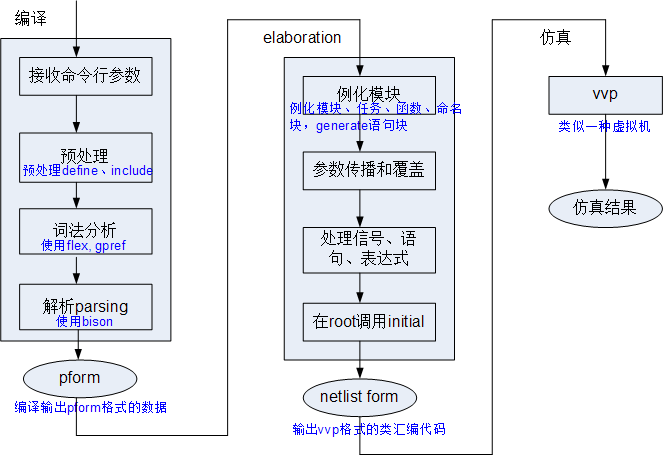

与商业仿真器相同,也是分成三个步骤——编译、elaboration、仿真。

编译就是从接收命令行参数开始,到预处理(verilog宏展开,文件include,条件编译),Verilog语法解析(关键字识别、语法解析),最后转换成内部的数据结构(就是用各种class、结构体,如module、net、scope、generate、statement、expression等)的过程。

简单的讲,就是识别Verilog文件,转成内部的数据库。经过编译后,各个Verilog文件在库里是独立的。

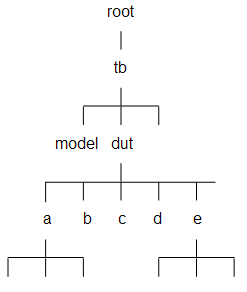

而elaboration就是把库里的数据,有机的组织成一个树型结构,树的顶端是root,往下是tb或者设计顶层,然后是例化的子模块。如下图:

elaboration的过程中还需要处理parameter的传播、defparam的覆盖,根据generate语句来产生实际的电路等。

另外Verilog的系统函数(如𝑓𝑖𝑛𝑖𝑠ℎ、finish、display、$dumpfile等)也是在这一步进行识别,然后与仿真器预实现的函数库(.so或.a)进行关联。

经过处理后,这个树型结构就可以准确的表达整个设计(包括testbench)。

elaboration还会根据优化选项进行一定的优化,简化树型结构。比如,去除设计层次,用信号命名来表示原层次关系。还可以进行边界优化,合并组合逻辑。合理的优化会很大程度上加速仿真。

elaboration最终会输出一个类似汇编的vvp文件。

仿真时读入vvp文件,送进vvp虚拟机执行。我们可以简单地理解成类java虚拟机的一种东西。可以像模拟电路一样,按照仿真时间1ns、1ns的执行,也可以用事件驱动的方式来往前推进。我们知道verilog里,时序逻辑是以时钟沿来执行的,组合逻辑是按敏感列表变化来执行。在需要时才做计算,可以节省90%以上的计算量。

从Icarus Verilog源码来看,主要有两个方面难度较大。

一是,Verilog语言的parser。

二是,vvp虚拟机的执行机制。

能否用于商业用途,一个是看License许可。另一个是看功能和性能。虽然Icarus Verilog能完成Verilog 2005写的设计和Testbench的仿真,但目前企业的主流验证方法是SystemVerilog+UVM。从这个角度看不能满足需求。

尽管如此,Icarus Verilog对我们还是很有启发意义,很多优秀的商业EDA软件也是从改进开源软件起家的。

分享数字集成电路设计中的经验和方法。分享让工作更轻松。