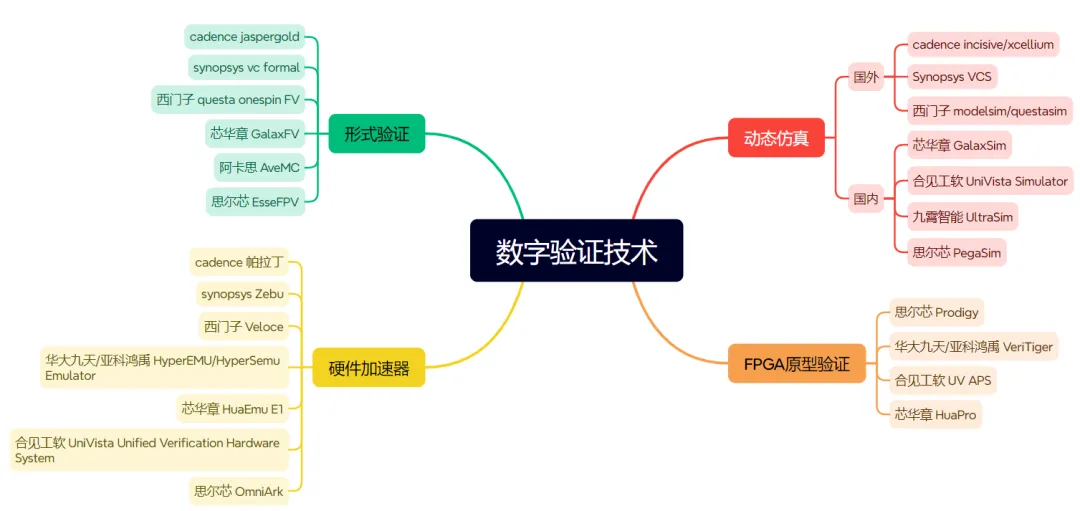

数字验证有两种技术,动态仿真和静态形式验证(动态仿真也可以实时用sva来检查)。两种是互补的,各解决一部分问题。

动态仿真是传统的数字电路验证方式,如用synopsys vcs、cadence nc来仿真。耗时长,验不全面。一般依赖于代码覆盖率和功能覆盖率来确认验证是否达到目标。代码覆盖率验证后期意义不大,不能反映功能是否正确,而功能覆盖率是否全面取决于是否100%定义清楚了验证计划。

而静态形式验证是一种数学公式的证明,理论上可以遍历所有情况。但也有缺点,逻辑复杂后遍历时间长,不适用于大设计,只能用于模块级。且在国内没有普及,大部分验证工程师并不熟悉形式验证这种技术,只有少数大公司在用。

在动态仿真很慢时,最简单的方式就是开发FPGA原型验证系统,把RTL放到FPGA跑,来验证功能。这种方式前期硬件开发周期长,需要专门的硬件工程师来维护和调试。所以出现了专门做原型验证系统的公司,针对常见SOC的需求开发一套通用的开发板,甚至开发一套自动化工具或者脚本来减少代码移植的工作。

后来又出现了硬件加速器(国内不少公司在做,如芯华章,华大九天,合见等),主要原理硬件加速器工具自动把RTL代码放到FPGA或者定制ASIC中去跑,并能实时与UVM验证环境互交和通信,也可以抓取仿真波形。工程师学习成本低,效率大大提高。硬件加速器不局限于linux服务器的性能,解决了动态仿真耗时长的问题。在大型SOC、GPU等芯片研发中得到应用。但成本很高,如cadence一台帕拉丁千万起,并且买的只是使用权。

综上,任何一种验证技术都不能解决全部问题,需要相互补充,发挥每个验证技术的长处,才能在项目中得到最好的效果。

分享数字集成电路设计中的经验和方法。分享让工作更轻松。