# VC SpyGlass Lint<sup>®</sup> User Guide

Version S-2021.09-SP2, March 2022

# **Copyright Notice and Proprietary Information**

© 2022 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Trademarks**

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html.

All other product or company names may be trademarks of their respective owners.

#### Free and Open-Source Software Licensing Notices

If applicable, Free and Open-Source Software (FOSS) licensing notices are available in the product installation.

#### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

www.synopsys.com

# Synopsys Statement on Inclusivity and Diversity

Synopsys is committed to creating an inclusive environment where every employee, customer, and partner feels welcomed. We are reviewing and removing exclusionary language from our products and supporting customer-facing collateral. Our effort also includes internal initiatives to remove biased language from our engineering and working environment, including terms that are embedded in our software and IPs. At the same time, we are working to ensure that our web content and software applications are usable to people of varying abilities. You may still find examples of non-inclusive language in our software or documentation as our IPs implement industry-standard specifications that are currently under review to remove exclusionary language.

# **Contents**

| Introduction                                                          | 7  |

|-----------------------------------------------------------------------|----|

| About this Guide                                                      | 8  |

| Contents of this Manual                                               | 9  |

| Getting Started                                                       | 11 |

| Verification Compiler (VC) Platform                                   | 12 |

| VC Static and Formal Solution                                         | 13 |

| VC SpyGlass Lint                                                      | 14 |

| Licensing Requirements                                                |    |

| Key Features of VC SpyGlass Lint                                      | 15 |

| VC SpyGlass Lint Methodology Flow                                     | 16 |

| Reading the Design                                                    | 17 |

| Setting Up Design Environment                                         |    |

| VC SpyGlass Fundamentals for Lint                                     | 19 |

| Support for DesignWare (DW) Components                                |    |

| Reusing the Pre-compiled DW Components                                |    |

| Selecting DW Components for Elaboration                               |    |

| Language Support                                                      |    |

| Running the VC Static Shell                                           |    |

| Changing the VC Static Session Name and Location                      |    |

| Sample Design Setup                                                   |    |

| Saving and Restoring Sessions Using save_session and restore_session. |    |

| Updating Application Variable Settings                                | 24 |

| Reading the Liberty Files                                             |    |

| The search_path and link_library Variable                             |    |

| Using Black Boxes in VC SpyGlass Lint                                 | 28 |

| Reading the Design                                                    |    |

| Application Variables that Impact Reading a Design                    |    |

| Performing VC SpyGlass Lint Checks                                    |    |

| Analyzing Reports                                                     | 36 |

| Working with Methodo  | ologies and Goals             | 37 |

|-----------------------|-------------------------------|----|

| Terminology           |                               | 38 |

| Development Phase     | s and Methodologies:          | 40 |

| Development Leve      | ls                            | 40 |

|                       | elopment                      |    |

|                       | ration and Implementation     |    |

|                       | es                            |    |

|                       | lopmentlopment on block level |    |

|                       | mopriment on block level      |    |

|                       | olock level                   |    |

|                       | SoC level                     |    |

|                       |                               |    |

|                       | block level                   |    |

| Netlist Handoff on    | SoC level                     | 44 |

| Layout Handoff        |                               | 45 |

| Understanding Guid    | eWare Goals                   | 46 |

| Setting Up Methodo    | logy/Goals                    | 47 |

| Running Custom Go     | als                           | 53 |

|                       |                               |    |

| Using VC SpyGlass Lin | t                             | 55 |

|                       | ss Lint in Tcl Shell Mode     |    |

|                       | t in VC SpyGlass Lint         |    |

|                       | le                            |    |

| Building a Design l   | Jsing Analyze and Elaborate   | 58 |

| Building a Design \   | With read_file                | 58 |

| Using Built-in Tcl Co | mmands                        | 59 |

| Running Lint Checks   | 5                             | 60 |

|                       | 5                             |    |

| 2 , , ,               | d Modules                     |    |

|                       | Similar Tags                  |    |

|                       |                               |    |

|                       | rting                         |    |

|                       | SpyGlass Lint                 |    |

| Native VC SpvGlas     | s Lint Waivers                | 67 |

| Using Tags in VC SpyGlass Lint                                                                     | 71  |

|----------------------------------------------------------------------------------------------------|-----|

| About VC SpyGlass Lint tags                                                                        | 72  |

| Creating the Configuration File                                                                    |     |

| Configuring Tag Parameters                                                                         |     |

| Inferring Hanging Clocks                                                                           |     |

| Support for STARC and STARC02 Tag Mapping                                                          |     |

|                                                                                                    |     |

| VC SpyGlass Functional Lint                                                                        | 81  |

| Invoking VC SpyGlass Functional Lint                                                               | 83  |

| Analyzing VC SpyGlass Lint Results                                                                 | 87  |

| Understanding VC SpyGlass Lint Violation Database                                                  |     |

| Configuring Message Tags                                                                           |     |

| Debugging Lint Violations Using Tcl                                                                |     |

| Examples of Violation Fields                                                                       |     |

| Filtering Messages                                                                                 |     |

| Operations on Tag Definitions                                                                      |     |

| Reports Generated by VC SpyGlass Lint                                                              | 103 |

| Appendix A - Supported Commands                                                                    | 111 |

| Application Variables                                                                              | 112 |

| enable_lint                                                                                        | 112 |

| enable_clk_rst_infer_potential                                                                     | 112 |

| infer_unique_bbox                                                                                  |     |

| language_check_hierarchy_format                                                                    |     |

| lang_check_report_input_path                                                                       |     |

| lint_debug                                                                                         |     |

| lint_dump_hanging_clocks                                                                           |     |

| lint_enable_coverage_flow                                                                          |     |

| lint_enable_pgpinslint_enable_smart_tag_execution                                                  |     |

| lint_formal_disable_stage_name                                                                     |     |

| lint_functional_mode                                                                               |     |

|                                                                                                    |     |

| IINL IGNORE SYNCRESEL FOR ASYNCHOD                                                                 |     |

| lint_ignore_syncreset_for_asyncfloplint ignore redundant field waiver                              |     |

| lint_ignore_syncreset_for_asynchop<br>lint_ignore_redundant_field_waiver<br>lint_load_goal_results | 117 |

|    | lint_no_of_formal_processes                                                                                                                                                                                                                                                                                                 | 118                                                                                                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|    | lint_no_of_lang_processes                                                                                                                                                                                                                                                                                                   | 118                                                                                                   |

|    | lint_report_all_paths                                                                                                                                                                                                                                                                                                       | 119                                                                                                   |

|    | lint_report_same_similar_rules                                                                                                                                                                                                                                                                                              | 119                                                                                                   |

|    | lint_report_whole_path                                                                                                                                                                                                                                                                                                      | 120                                                                                                   |

|    | lint_spyglass_waiver_report                                                                                                                                                                                                                                                                                                 | 120                                                                                                   |

|    | lint_traverse_depth                                                                                                                                                                                                                                                                                                         | 120                                                                                                   |

|    | quick_lint_mode                                                                                                                                                                                                                                                                                                             |                                                                                                       |

|    | elab_summary_report_max_inst                                                                                                                                                                                                                                                                                                | 122                                                                                                   |

|    | enable_generate_label_naming                                                                                                                                                                                                                                                                                                |                                                                                                       |

|    | ignore_encrypted_module_violations                                                                                                                                                                                                                                                                                          |                                                                                                       |

|    | enable_gw_optional_tag                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|    | report_all_hdl_errors                                                                                                                                                                                                                                                                                                       | 124                                                                                                   |

| LI | NT Commands                                                                                                                                                                                                                                                                                                                 | 126                                                                                                   |

|    | check_lint                                                                                                                                                                                                                                                                                                                  |                                                                                                       |

|    | report_lint                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

|    | report_violations                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|    | waive_lint                                                                                                                                                                                                                                                                                                                  |                                                                                                       |

|    | view_fl_viol_summary                                                                                                                                                                                                                                                                                                        |                                                                                                       |

|    | get_flp_summary                                                                                                                                                                                                                                                                                                             | 137                                                                                                   |

|    | 9 = 1 = 7                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| LI | NT Configure Commands                                                                                                                                                                                                                                                                                                       | 139                                                                                                   |

| LI | NT Configure Commands  configure_lint_tag                                                                                                                                                                                                                                                                                   | <b>139</b><br>139                                                                                     |

| LI | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter                                                                                                                                                                                                                                                     | <b>139</b><br>139<br>141                                                                              |

| LI | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter  configure_lint_functional_setup                                                                                                                                                                                                                    | 139<br>139<br>141<br>142                                                                              |

| LI | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter  configure_lint_functional_setup  configure_lint_methodology                                                                                                                                                                                        | 139<br>139<br>141<br>142<br>143                                                                       |

| LI | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter  configure_lint_functional_setup  configure_lint_methodology  configure_lint_rca                                                                                                                                                                    | 139<br>139<br>141<br>142<br>143<br>144                                                                |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup.                                                                                                                                                  | 139<br>141<br>142<br>143<br>144<br>146                                                                |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup                                                                                                                                                   | 139<br>141<br>142<br>143<br>144<br>146<br>148                                                         |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup. atabase Commands all_clock_gates                                                                                                                 | 139<br>141<br>142<br>143<br>144<br>146<br>148<br>148                                                  |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup ntabase Commands all_clock_gates all_clocks                                                                                                        | 139<br>141<br>142<br>143<br>144<br>146<br><b>148</b><br>148                                           |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup. atabase Commands all_clock_gates all_clocks. all_connected                                                                                       | 139<br>141<br>142<br>143<br>144<br>146<br>148<br>148<br>148                                           |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup. ntabase Commands all_clock_gates all_clocks all_connected all_designs                                                                            | 139<br>141<br>142<br>143<br>144<br>146<br>148<br>148<br>148<br>150                                    |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup  Itabase Commands all_clock_gates all_clocks. all_connected all_designs all_fanin                                                                 | 139 139 141 142 143 144 146 148 148 148 150 150                                                       |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup  Itabase Commands all_clock_gates all_clocks. all_connected all_designs all_fanin all_fanout                                                      | 139<br>141<br>142<br>143<br>144<br>146<br>148<br>148<br>148<br>150<br>150                             |

|    | NT Configure Commands configure_lint_tag configure_lint_tag_parameter. configure_lint_functional_setup configure_lint_methodology configure_lint_rca configure_lint_setup.  ntabase Commands all_clock_gates all_clocks. all_connected all_designs all_fanin all_fanout all_inputs                                          | 139 141 142 143 144 146 148 148 148 150 150 152 154                                                   |

|    | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter.  configure_lint_functional_setup  configure_lint_methodology  configure_lint_rca  configure_lint_setup.  ntabase Commands  all_clock_gates  all_clocks  all_connected  all_designs  all_fanin  all_fanout  all_inputs  all_instances               | 139 141 142 143 144 146 148 148 148 150 150 155 154 155                                               |

|    | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter.  configure_lint_functional_setup  configure_lint_methodology  configure_lint_rca  configure_lint_setup.  atabase Commands  all_clock_gates  all_clocks.  all_connected  all_designs  all_fanin  all_fanout  all_inputs  all_instances  all_outputs | 139 141 142 143 144 146 148 148 148 150 150 155 155                                                   |

|    | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter  configure_lint_functional_setup  configure_lint_rca  configure_lint_setup  Itabase Commands  all_clock_gates  all_clocks  all_connected  all_designs  all_fanin  all_fanout  all_inputs  all_instances  all_outputs  change_link                   | 139<br>139<br>141<br>142<br>143<br>144<br>146<br>148<br>148<br>150<br>150<br>152<br>154<br>155<br>155 |

|    | NT Configure Commands  configure_lint_tag  configure_lint_tag_parameter.  configure_lint_functional_setup  configure_lint_methodology  configure_lint_rca  configure_lint_setup.  atabase Commands  all_clock_gates  all_clocks.  all_connected  all_designs  all_fanin  all_fanout  all_inputs  all_instances  all_outputs | 139 139 141 142 143 144 146 148 148 148 150 150 152 154 155 156 157                                   |

| create_bus                    |     |

|-------------------------------|-----|

| create_cell                   |     |

| create_net                    |     |

| create_port                   |     |

| define_user_attribute         |     |

| disconnect_net                |     |

| find                          |     |

| get_cells                     |     |

| get_designs                   |     |

| get_lib_cells                 |     |

| get_lib_pins                  |     |

| get_lib_timing_arcs           |     |

| get_libs                      |     |

| get_link                      |     |

| get_nets                      |     |

| get_object_name               |     |

| get_pins                      |     |

| get_ports                     |     |

| get_timing_arcs               |     |

| insert_buffer                 |     |

| list_designs                  |     |

| list_instance                 |     |

| list_libs                     |     |

| remove_attribute              |     |

| remove_buffer                 |     |

| remove_bus                    |     |

| remove_cell                   |     |

| remove_net                    |     |

| remove_port                   |     |

| report_cell                   |     |

| report_link                   |     |

| report_net                    |     |

| report_port                   | 204 |

| set_always_on_cell            | 206 |

| set_attribute                 |     |

| set_get_command_message_limit |     |

| set_isolation_cell            |     |

| set_level_shifter_cell        |     |

| set_pg_pin_model              |     |

| set_pin_model                 |     |

| set_power_switch_cell         | 213 |

|    | set_retention_cell                          | 214   |

|----|---------------------------------------------|-------|

|    | set_top_module                              | 215   |

| Co | mmon Commands                               | 216   |

|    | add_tag_field                               |       |

|    | analyze                                     |       |

|    | change names                                |       |

|    | check hdl lib                               |       |

|    | checkpoint_session                          | 221   |

|    | configure_module_synthesis                  | 221   |

|    | configure_libcell_uniquification            | 222   |

|    | configure_tcl_command                       | 222   |

|    | configure_unobservable_logic_identification |       |

|    | configure_waiver_filter_field               | . 224 |

|    | create_clock                                | 225   |

|    | create_generated_clock                      |       |

|    | create_interface_wrapper                    |       |

|    | create_reset                                |       |

|    | create_static                               |       |

|    | define_design_lib                           |       |

|    | define_name_rules                           |       |

|    | diff_database                               |       |

|    | disable_tag_field                           |       |

|    | elaborate                                   |       |

|    | generate_waiver_commands                    |       |

|    | get_blackbox                                |       |

|    | get_clock_relationship                      |       |

|    | get_constant_sources                        |       |

|    | get_exception                               |       |

|    | get_field_subfield                          |       |

|    | get_glassbox                                |       |

|    | get_license                                 |       |

|    | get_no_msg_reporting_tags                   |       |

|    | get_pi_drive_clock                          |       |

|    | get_readmsg_attribute                       |       |

|    | get_readmsg_field                           |       |

|    | get_readmsg_ids                             |       |

|    | get_readmsg_names                           |       |

|    | get_readmsg_names                           |       |

|    | get_supported_tags                          |       |

|    | get_violation_waiver                        |       |

|    | get waiver attribute                        | ノ51   |

|      | get_waivers                      |     |

|------|----------------------------------|-----|

|      | index_database                   |     |

|      | infer_clock_roots                | 252 |

|      | infer_reset_roots                |     |

|      | infer_setup                      | 253 |

|      | link                             |     |

|      | link_design                      | 256 |

|      | list_all_waiver_files            | 257 |

|      | llib                             | 257 |

|      | man                              |     |

|      | merge_database                   | 259 |

|      | read_fileread_file               | 259 |

|      | read_sdc                         | 264 |

|      | remove_case_analysis             | 265 |

|      | remove_clock                     | 265 |

|      | remove_clock_groups              |     |

|      | remove_generated_clocks          | 267 |

|      | rename_tag                       |     |

|      | report_mode                      | 269 |

|      | report_names                     |     |

|      | report_properties                |     |

|      | report_read                      |     |

|      | report_read_violations           |     |

|      | report_session_data              | 274 |

|      | report_tag                       | 274 |

|      | reset_mode                       |     |

|      | set_case_analysis                | 276 |

|      | waive_read                       | 277 |

|      | Command Sanity Checks            | 280 |

|      | Errors Generated by Tcl Commands |     |

|      | ·                                |     |

| Miar | ating Waivers                    | 297 |

| nigi |                                  |     |

|      | Working with Waivers             |     |

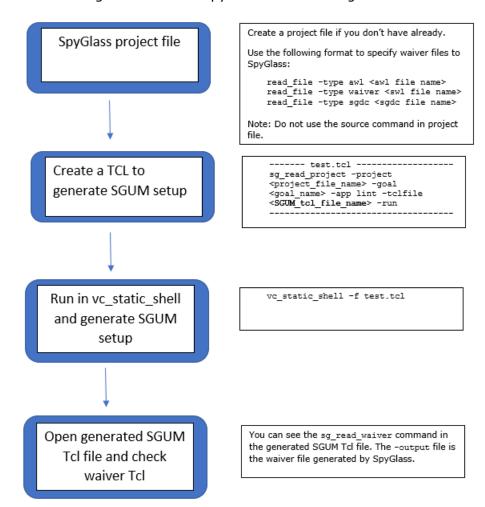

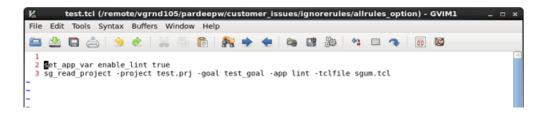

|      | SpyGlass to SGUM Migration Flow  |     |

|      | SpyGlass to VCUM Migration Flow  |     |

|      | Migrating Waivers                |     |

|      | Applying Waivers                 |     |

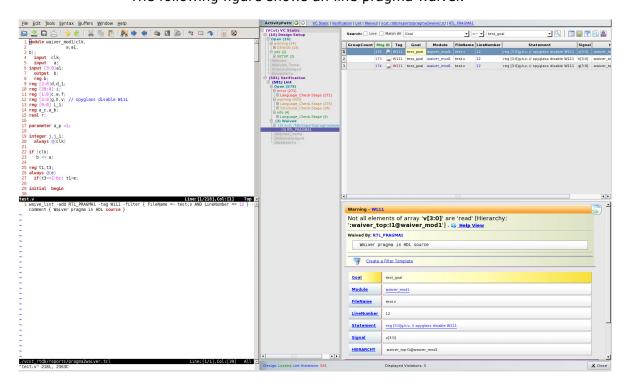

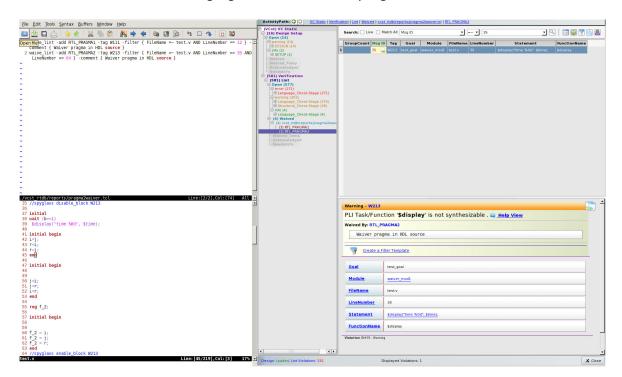

|      | Migrating Pragma Waivers         | 296 |

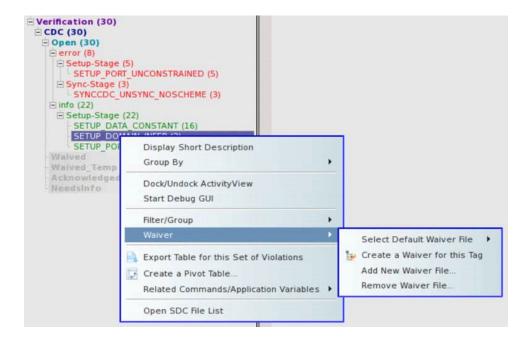

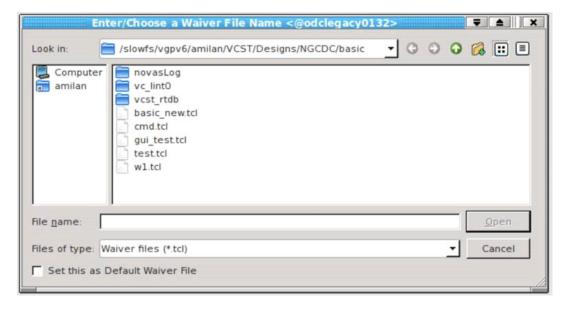

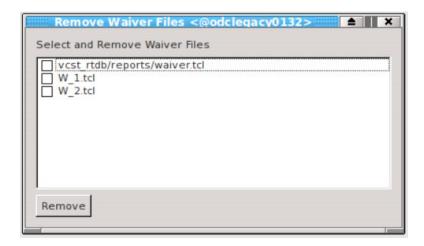

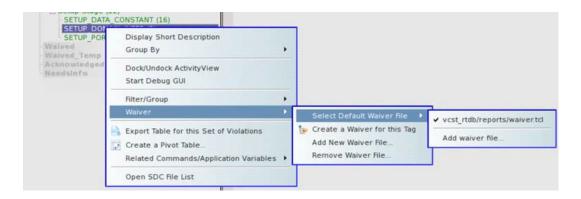

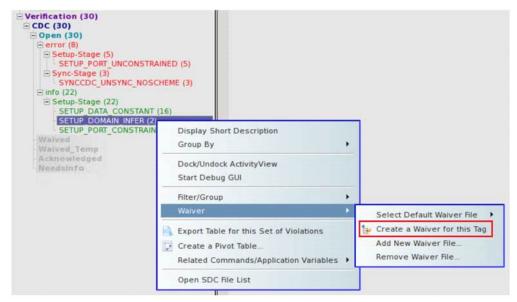

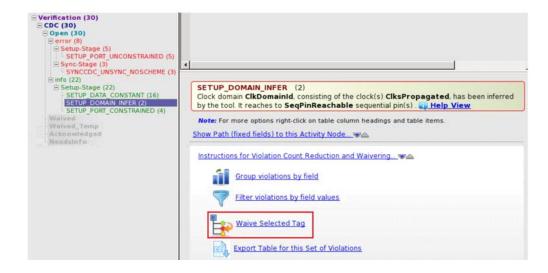

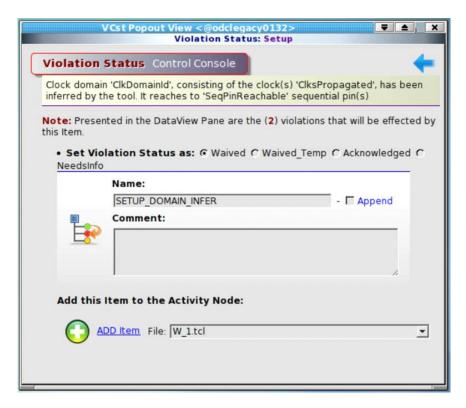

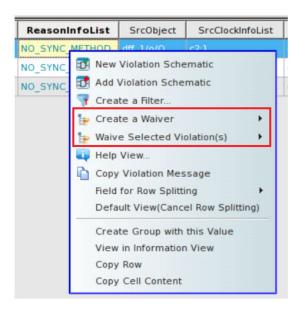

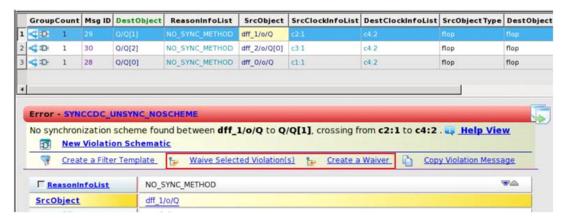

|      | Waiving Using GUI                | 299 |

|      | Managing Waivers                 | 299 |

|      |                                  |     |

| Creating a Waiver                                 | 302 |

|---------------------------------------------------|-----|

| Waive all Messages of a Tag                       |     |

| Waive Messages Selectively                        |     |

| Reporting Waivers                                 | 309 |

| Debugging Aids                                    | 310 |

| Waiver-related Commands and Application Variables | 311 |

| Application Variables                             |     |

| Commands                                          | 311 |

| Waiver Configuration Commands                     | 312 |

| Waiver TCL Commands                               | 312 |

# Introduction

This chapter provides an overview of VC SpyGlass Lint and includes the following sections:

- About this Guide

- Contents of this Manual

#### **About this Guide**

The VC SpyGlass Lint User Guide describes the concepts, features, usage, and tags of VC SpyGlass Lint, which enable you to use the Verilog or SystemVerilog designs against various coding standards and design tags.

# **Contents of this Manual**

The VC SpyGlass Lint User Guide consists of the following sections:

| Section                                 | Description                                                                                                                   |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Getting Started                         | Provides an overview of VC SpyGlass Lint.                                                                                     |  |  |

| Reading the Design                      | Describes how to read a design in VC SpyGlass Lint.                                                                           |  |  |

| Working with<br>Methodologies and Goals | Provides information on using methodologies and goals.                                                                        |  |  |

| Using VC SpyGlass Lint                  | Provides reference information for the built-in Tcl commands implemented in VC SpyGlass Lint.                                 |  |  |

| Using Tags in VC<br>SpyGlass Lint       | Provides detailed procedures for how to configure and use the prepackaged tags to check your HDL code.                        |  |  |

| VC SpyGlass Functional<br>Lint          | Describes the VC SpyGlass Functional Lint flow.                                                                               |  |  |

| Analyzing VC SpyGlass<br>Lint Results   | Describes the VC SpyGlass Lint violations, how to debug Lint Violations Using Tcl, and reports generated by VC SpyGlass Lint. |  |  |

| Appendix A - Supported<br>Commands      | Describes the SDC commands, Tcl commands, configure commands and application variables supported by VC SpyGlass Lint.         |  |  |

| Migrating Waivers                       | Describes migrating waivers in VC SpyGlass Lint.                                                                              |  |  |

Contents of this Manual

# **Getting Started**

This section introduces Verification Compiler (VC) Platform, VC SpyGlass, and VC SpyGlass Lint and is organized into the following sections:

- Verification Compiler (VC) Platform

- VC Static and Formal Solution

- VC SpyGlass Lint

# Verification Compiler (VC) Platform

Today's electronic consumer market is driven by a huge demand for mobility, portability, and reliability. Additional functionality, performance, and bandwidth are very important for maximizing semiconductor sales in addition to faster time-to-market and product quality. The evolution of applications, such as cellular phones, laptops, PDAs, computers, mobile multimedia devices, and portable systems, has seen an exponential growth in battery operated systems.

The increase in design complexities and shrinking technologies, where more and more functionality is being added into smaller area of a chip has brought in a new set of challenges in System-on-Chip (SoC) verification. With adoption of advanced techniques and sophisticated tools, which helps in verifying SoC connectivity, signal integrity, power management, and functionality of analog components, hardware-software co-verification has become inevitable.

This brings in a need for a unified and integrated verification environment with seamless flow and reuse of the information across different domains/levels to achieve faster results.

Verification Compiler Platform is a next-generation verification solution that provides a scalable environment, where sophisticated tools work seamlessly with each other throughout the flow to accomplish various verification tasks using integration of technologies. It helps in optimizing design iterations and recompilations, shortens debug cycles, and enables steady integration and interoperability between individual verification tools.

13

#### **VC Static and Formal Solution**

Traditionally, simulation-based dynamic verification techniques have been the mainstay of functional verification. As modern day SoC designs become more complex, the adoption of static verification techniques is important.

Synopsys' VC Static and Formal verification solution offers the nextgeneration comprehensive VC Formal verification solution, VC SpyGlass Lint, VC SpyGlass CDC, VC SpyGlass RDC, and VC Low Power verification solution.

Synopsys' VC Static and Formal verification solution combines the best-inclass technologies for improved ease-of-use, accuracy, and performance. It also provides with low violation noise and excellent debug capabilities. This solution enables designers and verification engineers to quickly and easily find and fix bugs in RTL before simulation; therefore, reducing the time needed before software bring-up, hardware emulation, and prototyping.

VC LP is a multi-voltage, static low power rule checker that allows engineers to rapidly verify designs that use voltage control-based techniques for power management. VC LP is part of the Synospys Eclypse Flow. VC LP also helps in pipe-cleaning the power intent of the design that is captured in IEEE 1801 Unified Power Format (UPF) before such intent is used as a golden reference for implementation and other verification tools. Further, VC LP verifies the implemented power-intent later in the design flow.

VC Formal verification offers property checking that consists of mathematical techniques to test properties or assertions to ensure the correct functionality of RTL designs. For more information, see the VC Formal Verification User Guide.

VC SpyGlass Lint, a static verification tool, performs system-to-netlist verification using prepackaged tags to check Verilog, SystemVerilog, VHDL designs against various coding standards and design tags. After you elaborate your design in the VC Lint environment, you can use built-in Tcl queries, prepackaged checks, and a set of predefined procedures to run interactive queries on your design.

RTL code is verified for connectivity correctness between two nodes of a design using the VC Formal Connectivity Checking solution. For more information, see the VC Formal Connectivity Checking User Guide.

RTL is further verified for functionality and policy compliance. Model checking technique exhaustively and automatically checks whether a

model adheres to a given specification and verifies correct properties of finite-state systems. For more information, see the VC Formal Verification User Guide.

VC SpyGlass RDC performs reset verification to report issues, such as metastability, glitches, and functional failures leading to silicon failure. It also provides advanced RDC capabilities, such as performing RDC synchronization in sequential crossing paths, memory modeling, and extracting reset order automatically from the simulation database. In addition, it generates RDC reports that you can use to identify synchronization issues in the design. You can also waive and filter violations.

# VC SpyGlass Lint

VC SpyGlass Lint is a system-to-netlist checker tool that comes with prepackaged tags to check Verilog or SystemVerilog designs against various coding standards and design tags.

After you elaborate your design in the VC SpyGlass Lint environment, you can use the built-in Tcl shell and a set of predefined procedures to run interactive queries on your design. With full support for Verilog 2001 and IEEE Std 1800-2005 SystemVerilog design constructs, combined with extensive RTL and netlist checks, VC SpyGlass Lint can check your designs for errors that may cause problems in the downstream simulation, synthesis, and equivalence checking flows. The best way to learn the tool is to test one of your designs with the Checker and the prepackaged policies (sets of tags). The prepackaged tags are designed to meet the best coding guidelines and practices followed in the industry.

VC SpyGlass Lint is a design checker tool that comes with a rich set of prepackaged tags to check Verilog and SystemVerilog designs against various coding standards and design tags.

You use the Checker to designate Verilog or SystemVerilog input files that you want to compare against coding tags that you select with the click of a mouse. The Checker analyzes your Verilog and SystemVerilog source code against the selected tags and generates a report indicating which lines in the code violate the tags. You can then:

- Open the report in the GUI and debug the reported violations

- Generate schematics to debug structural checks.

- Navigate directly from the violation message in the GUI to its source code in your HDL files.

- Create filters and waivers for better report management

### **Licensing Requirements**

VC SpyGlass Lint requires the 'VC-LINT-BASE & checker' licenses. Ensure that these licenses are available before you run VC SpyGlass Lint.

### **Key Features of VC SpyGlass Lint**

The key features and benefits of using VC SpyGlass LINT for static verification in a typical design are as follows:

- Improved total runtime and PEAK memory

- Unified compilation

- Management of large memories and does not require options to handle large memories during synthesis

- Word-level traversal and avoidance of bit level traversal (if needed)

- Consistent handling of clocks and resets

- Multi-message and multi-line support

- Tag-specific reports

- Noise reduction using the allviol parameter

- V2k language support

- VHDL2008 support

- Complete IEEE 1800-2005 System Verilog design constructs

- Saving and restoring elaborated design view

# **VC SpyGlass Lint Methodology Flow**

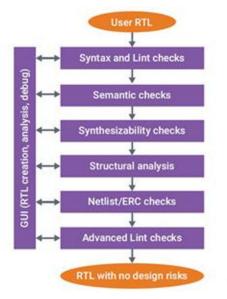

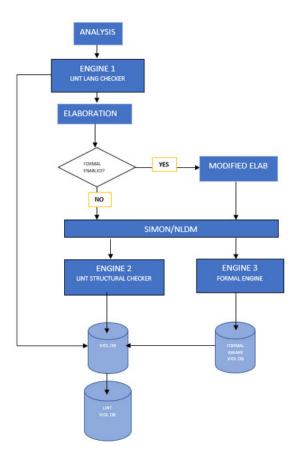

Figure 1 shows the VC SpyGlass Lint methodology flow.

FIGURE 1. VC SpyGlass Lint Methodology Flow

# **Reading the Design**

This section describes how you can get started with VC SpyGlass Lint.

# Setting Up Design Environment

You must provide the synthesizable design files (RTL/Netlist) to perform Lint verification.

#### **Licensing and Installation**

This release of VC Static Platform is a standalone platform and must be installed in an empty directory, using the latest version of the Synopsys Installer. Do not install this release over an existing release of a Synopsys tool.

For installation instructions, see the  $vc\_static\_INSTALL\_README.txt$  file in the product download directory. For detailed installation instructions, see the Synopsys Installation Guide at the following address:

http://www.synopsys.com/install

Before running Synopsys tools, you must have installed and configured the Synopsys Common Licensing (SCL) software, retrieved your license key file, and defined the license file environment variable. For detailed information about SCL installation and setup, see the Synopsys Licensing Quickstart Guide at the following address:

http://www.synopsys.com/licensing

For more information on the VC Static license keys, see section *VC Static Product Installation Notes*.

# VC SpyGlass Fundamentals for Lint

VC SpyGlass Lint uses the synthesizable RTL files to perform Lint verification. The tool provides you with commands that you can use to create and verify Lint setup, perform various checks on the design.

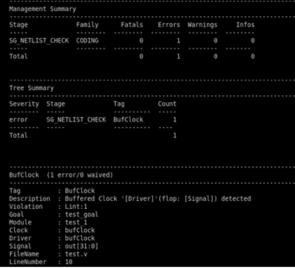

VC SpyGlass Lint reports the results of the checks performed on the design in the form of violation tags. A violation tag can be an Error, Warning, or Info type depending on the type of violation reported.

### Support for DesignWare (DW) Components

VC Static supports usage of DesignWare components in the RTL. To compile DW components, use the dw analyze command as shown below:

```

dw analyze -dwroot <DC-install-path> <dir-name>

```

#### Where:

- <DC-install-path> specifies the path to Design Compiler

- <dir-name> specifies the directory where the compiled DW is stored

For example, consider the following command:

```

dw_analyze -dwroot /global/apps/syn_2016.12-SP3

NG DW WORK 1712

```

In the above command, /global/apps/syn\_2016.12-SP3 specifies the path to DC and NG\_DW\_WORK\_1712 is the name of the directory where the compiled DW is generated.

### Reusing the Pre-compiled DW Components

You can use DW components that are compiled in a previous major release by saving the compiled DW components to an appropriate location that is accessible by other users. Users can use this compile in all Service Pack releases of the major VC Static release. You need to recompile the DW components when you move to the next major VC Static release.

For example, if you compile DW components in the VC Static 2017.12 release and save it at a central location, all users can use the compile in all the VC Static 2017.12-SP\* releases.

To use such compiled DW components, use the following command:

```

set_app_var_vsi_dwroot <path>/NG_DW_WORK_1712

```

Where, <path> specifies the directory where the compiled DW components are stored.

**NOTE:** You can save the compiled DW components on your local machine and use it in successive SP\* releases as well.

### **Selecting DW Components for Elaboration**

If both RTL and DW pre compiled libraries are present in a design, VC SPYGLASS, by default, uses the RTL definition for elaboration. This might lead to creation of blackboxes of the DesignWare components in the design.

Set the prefer\_dw\_over\_rtl application variable to true to enable VC SpyGlass to use the DW pre-compiled libraries instead of RTL.

### Language Support

VC Static platform supports the following industry standard HDLs:

- Verilog (1995, v2k)

- VHDL ('87, '93, 2008)

- SystemVerilog 1800-2005, and 2009

- Mixed Language Design

# Running the VC Static Shell

VC SpyGlass Lint uses the pivotal environment variable, VC\_STATIC\_HOME. This variable must be set to point to the installation directory as shown in the following code snippet. In the installation directory, you can find the bin, lib, doc and other directories.

```

% setenv VC_STATIC_HOME /tools/synopsys/vcst

```

Optionally, you can add \$VC\_STATIC\_HOME/bin to your \$PATH. To start the VC Static tool, execute the following command:

```

% $VC STATIC HOME/bin/vc static shell

```

To invoke the VC Static platform from the shell in the 64-bit mode (default mode), use the following command:

```

%vc static shell

```

#### **VC Static Shell Command Line Options**

The following command line options are available for VC Static. The options might be abbreviated by leaving out the text in parenthesis; for example, either -f or -file can be used to give the name of a script file to execute.

#### **Syntax**

```

%vc static shell -help

Usage: /~/Release/bin/vc static shell

[-batch]Start tool in batch mode (non-interactive).

[-cmd log file <log name>] Name of command log file in current

directory.

[-f(ile) <file name>]Script file to exec after setup.

[-qui]Start the GUI ActivityView.

[-h(elp)]Print this help message.

[-id | -ID] Give more information about application build/

env.

[-lic wait <minutes>] Wait for license for #minutes.

[-no init]Don't load .synopsys vcst.setup files.

[-no restore] Remove previous session and start a new one.

[-no ui]Starts the tool without the GUI/UI process.

[-output log file <log name>]Capture console output in given

log file.

[-read only] Restore a previous session in read-only mode.

[-restore] Restore a previous session.

[-session <session name>]Use the <session name> directory

```

for the runtime database.

debug options:

[-echo] Echo the environment but do not invoke the executable.

#### Use Model

Using vc\_static\_shell in batch mode

%vc static shell -f vcst.tcl -batch

Using vc\_static\_shell in interactive mode

%vc static shell -f vcst.tcl

**NOTE:** When you use the -batch option, VC Static automatically quits the shell even when quit is not explicitly specified in the vcst.tcl file or when an unexpected error occurs and the full run is not complete. This is useful for regression runs.

### Changing the VC Static Session Name and Location

After vc\_static\_shell is run in any user work directory, VC Static creates a default session (work database directory) in the current working area called *vcst\_rtdb* [VC Static Run Time Data Base] along with default log files. The default session name is *vcst*.

You can change the name of the session and the location of the session at the time of invoking vc static shell.

%vc\_static\_shell -session my\_path/my\_session <other commands>

This command creates a database directory named *my\_session\_rtdb* in the ./my\_path directory.

### Sample Design Setup

The following script file is a sample script that you can use to run VC SpyGlass Lint flow in vc\_static\_shell.

### Note to set respective app\_vars' and other settings in below order.

# Basic VC SpyGlass LINT TCL file.

```

# Edit, fill in <options> and uncomment any settings/commands,

then save.

#Settings to enable VC SpyGlass LINT flowset app var

enable lint true

#Following command reads Cell library files in .db format set

search path < Path to directory which contain db files> set

link library <db file list which located in search path> Refer

to the Reading the Liberty Files section for details.

### Enabling/Disabling VC Spyglass LINT tags

configure lint tag -enable -tag "<tag name>" -goal <goal name>

configure lint tag parameter -tag "<tag name>" -parameter

<parameter name>

-value {<value>} -goal <goal name>

###

configure lint setup -goal <goal name>

### Set below settings after the "Enabling/Disabling VC

Spyglass LINT tags" settings

#### Design read

define design lib WORK -path ./WORK/VCS

analyze -format <Verilog/sverilog/vhdl> {-f <file list> }

-vcs {<vcs command>}

elaborate <top module name>

#Command to check LINT

check lint

#Following command generates verbose report

report lint -verbose -file <File name> -limit 0

# Show results in GUI

```

view activity

# Saving and Restoring Sessions Using save\_session and restore session

VC SpyGlass Lint enables you to save the results of the run after the check\_lint TCL command and restore the results in the subsequent run from the same point. You can use GUI based debugging, applying waivers and report generation in the restored run.

When you exit the vc\_static\_shell, the results of the current session are not automatically saved. To save the session setup and run data, use the save\_session command. The command uses the following syntax:

```

save_session

-session <session name>

```

where, -session <session\_name> specifies the name to be used to save the session.

To restore a saved session, use the restore\_session command. The command uses the following syntax:

```

restore_session

[-session <session_name>]

```

where, -session <session\_name> specifies the name of a previously saved session.

### **Updating Application Variable Settings**

VC SpyGlass Lint offers a list of application variables that can be used as per your requirements. To see the list of all the available application variables and their current settings in the vc\_static\_shell, use the following command:

```

%vc_static_shell> printvar (or)

%vc_static_shell> report_app_var

```

The printvar command reports all variables including user-defined variables while the report\_app\_var command reports only the VC Static and Formal application variable settings.

#### Example 1

```

%vc_static_shell> printvar

.....

.....

lint_enable_coverage_flow = "false"

lint_enable_pgpins = "false"

lint_enable_smart_tag_execution = "false"

lint_functional_mode = "false"

lint_ignore_encrypted_violations = "false"

lint_ignore_syncreset_for_asyncflop = "false"

....

....

```

#### Example 2

vc static shell> report app var \*lint\*

| Variable                                    | Value      | Туре | Default | Constraints |

|---------------------------------------------|------------|------|---------|-------------|

|                                             |            |      |         |             |

| enable_lint                                 | false      | bool | false   |             |

| lint_debug                                  | 0          | int  | 0       |             |

| <pre>lint_enable_ coverage_flow</pre>       | false      | bool | false   |             |

| <pre>lint_enable_ pgpins</pre>              | false      | bool | false   |             |

| <pre>lint_enable_smart _tag_execution</pre> | t<br>false | bool | false   |             |

#### Example 3

```

vc_static_shell> report_app_var lint_functional_mode

-verbose

Variable Value Type Default Constraints

------

lint_

functional_

mode false bool false

# Enables formal aware lint

```

You can change the default behavior of VC SpyGlass Lint by changing the default settings of the application variables. You can use the set\_app\_var command to change the setting of an application variable. The following example shows how to set a variable:

```

vc static shell> set app var lint enable coverage flow true

```

# Reading the Liberty Files

For pure RTL designs, supplying liberty files is not necessary, However, supplying liberty files is necessary for RTL designs with pre-instantiated cells and for most logical/physical netlist designs. You must provide all the required liberty files using search\_path and link\_library application variables before reading the design. After the link\_library and search\_path commands are set, read the design using the read\_file command.

#### The search\_path and link\_library Variable

The search\_path application variable specifies a sequence of directories where VC SpyGlass Lint looks for the library (.db) files. The specified directories are searched before a new library file is loaded.

%vc static shell> set app var search path <list of all the paths>

- Specify all the paths where VC SpyGlass Lint should search for the library files and design files. The paths might be absolute or relative to the directory from which VC SpyGlass Lint is invoked.

- If multiple paths are present, specify the paths as space separated values in double quotation marks.

- The search\_path variable supports environment variables.

- The search\_path variable does not support wildcard characters.

The link\_library application variable specifies a list of .db library files to be searched when a cell instantiation is to be resolved.

%vc\_static\_shell> set\_app\_var link\_library <list of .db files>

- Specify all the library files that should be read.

- Only Liberty .db files (not .lib files) are read in by the tool.

- If multiple .db files are present, specify the paths as space separated values in double quotation marks.

- The link\_library variable does not support environment variables.

#### Example

```

%vc_static_shell> set_app_var search_path ". path1 path2 ..."

%vc_static_shell> set_app_var link_library "lib1 lib2 ... libN"

```

# Using Black Boxes in VC SpyGlass Lint

A black box is either categorized as an automatic black box or a userdefined black box as described below:

■ A user defined black box is created using the Tcl command set\_blackbox. This needs to be done before using the analyze/read file commands.

For example, to black-box the module moduleA, use the following command:

```

set_blackbox -designs {moduleA}

read file -format verilog -top top <design file name.v>

```

■ An automatic black box is marked by the tool automatically. To see the designs marked as a black box, use the following command:

```

vc static shell> get blackbox -designs

```

VC SpyGlass Lint issues the following message for each black boxed module instance:

```

Note-[SM BB SKIP] Skipping blackboxed Module/Entity

```

In a design that contains one or more black boxes, the black boxes are elaborated with the following implicit hardware:

- Each input port of a black box is connected inside the corresponding module entity to one input of one implicit combinatorial gate (of undefined type).

- Each output port of a black box is driven inside the corresponding module by one output of one implicit combinatorial gate (of undefined type).

- Each inout port of a black box has both characteristics above as an input and an output port.

VC SpyGlass Lint does not perform tag checking for black-boxed modules and all modules that are instantiated in a black-boxed module.

# Reading the Design

VC SpyGlass Lint reads design in RTL (verilog, VHDL, SystemVerilog) and netlist (verilog) formats.

VC SpyGlass Lint provides the following commands to read a design:

■ read\_file: Read in design source files, and link design in memory. This command can be used to load design in a single language (Verilog/SV or VHDL). Using this command, you can specify all source files in one command in a single language environment. The files get analyzed and then elaborated. Upon completion of the command the complete design has been loaded and is ready to be used. The command returns 1 on success and 0 on failure.

#### Syntax:

```

%vc static shell> read file -help

Usage: read file

# Reading design files

[-top <top design>]

(Name of the top design)

[-library <library name>] (Remaps work library to library name)

[-define <list of verilog defines>] (Verilog/SV defines)

[-work <work library>] (alias for -library)

[-netlist]

(Verilog Netlist Reader)

[-parameters <comma-separated list of ordered or named

parameters>](design parameters)

[-vcs <vcs command line>] (VCS Command line for reading design)

[-vcs elab <vcs elaborate command line>] (VCS Command line for

elaborating design)

[-format <file format>]

(Verilog/SV defines: Values: verilog,

sverilog, vhdl, mdb)

(Process SVA/PSL during compilation

[-sva]

using 2009 semantics)

[-sva2005]

(Process SVA/PSL during compilation

using 2005 semantics)

[-v2kconfig <configuration-name>] (Specifies the v2k

configuration)

[-buildTop <dut name>]

(Specifies the DUT down from which

```

```

synthesis model is generated)

[-multi step]

(Load design in multi-step mode)

[-cov <metric type>]

(Enables coverage instrumentation

during compilation)

[-llk <llk type>]

(Creates livelock goals during

compilation)

(Enables AEP extraction during

[-aep <aep type>]

compilation)

[-inject fault <fault type>] (Injects behavioral faults in the

design for doing sign-off with

formal)

[-j <number of processes>] (Specifies the number of processes to

use for parallel compilation: Value

>= 1)

(List of input files)

[slist]

```

**NOTE:** For details on how to compile a design using the VCS standard switches, see the VCS® MX/VCS® MXi<sup>™</sup> User Guide. You can download this document from Solvnet.

analyze: Analyzes the specified HDL source files and stores the design templates into the specified library in a format that is ready to elaborate to form linkable cells of a full design. Using this command, you can specify multiple source files in a single language in one command. On completion of the command, all specified files are analyzed and are ready for elaboration. The command returns 1 on success and 0 on failure.

#### Syntax:

Feedback

```

[-vcs <vcs_cmd>] (VCS Command line for reading design)

[design file list] (List of source files)

```

**NOTE:** When you use the -vcs switch, the vlogan and vhdlan arguments and switches must be enclosed in curly braces.

#### **Examples:**

```

analyze -format verilog {test.v}

analyze -format vhdl {test.vhd}

analyze -format vhdl -vcs {-vhdl08} test.vhd

analyze -format vhdl -vcs {-f filelist_vhdl.f}

analyze -format verilog -vcs {+define+g90d -f sources_ng.f}

analyze -format verilog -vcs { +incdir+src/./sim_1 -f

sources_ng.f}

analyze -format verilog -vcs { +incdir+src/./sim_1 -f

sources_ng.f}

```

elaborate: Builds a design from the intermediate format of a Verilog module, a VHDL entity and architecture, or a VHDL configuration. Using this command, the user can elaborate design from pre-analyzed design files, from a specified top module. This command returns 1 on success and 0 on failure.

#### Syntax

```

%vc static shell> elaborate -help

Usage: elaborate # Elaborate the design, which is analyzed

using analyze command

[-work <library name>]

(Specifies the library name to which

work is to be mapped)

[-library <library name>] (Specifies the library name to which

work is to be mapped)

[-architecture <arch name>] (Specifies the name of the

architecture)

[-parameters <param list>] (Specifies a list of design

parameters enclosed in quotation

marks)

[-file parameters <file list>] (Specifies a list of files that

contain parameter specifications)

[-vcs <vcs cmd>]

(VCS Command line for elaborating

```

|                                                                                                                                                             | design)                                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| [-sva]                                                                                                                                                      | (Process SVA/PSL during compilation using 2009 semantics)                                        |  |

| [-sva2005]                                                                                                                                                  | (Process SVA/PSL during compilation using 2005 semantics)                                        |  |

| [-v2kconfig <configuration-name>] (Specifies the v2k configuration)</configuration-name>                                                                    |                                                                                                  |  |

| <pre>[-buildTop <dut name="">]</dut></pre>                                                                                                                  | (Specifies the DUT down from which synthesis model is generated)                                 |  |

| <pre>[-cov <metric_type>]</metric_type></pre>                                                                                                               | (Enables coverage instrumentation during compilation)                                            |  |

| [-llk <llk_type>]</llk_type>                                                                                                                                | (Creates livelock goals during compilation)                                                      |  |

| <pre>[-aep <aep_type>]</aep_type></pre>                                                                                                                     | (Enables AEP extraction during compilation)                                                      |  |

| [-inject_fault <fault_type:< td=""><td><pre>&gt;](Injects behavioral faults in the<br/>design for doing sign-off with<br/>formal)</pre></td></fault_type:<> | <pre>&gt;](Injects behavioral faults in the<br/>design for doing sign-off with<br/>formal)</pre> |  |

| <pre>[-j <number_of_processes>]</number_of_processes></pre>                                                                                                 | (Specifies the number of processes to use for parallel compilation: Value >= 1)                  |  |

| design_name                                                                                                                                                 | (Specifies the name of the design to build)                                                      |  |

**NOTE:** (1) If there is one design top, it must not be passed using vcs arguments, that is, elaborate -vcs {designtop}. It must be passed as follows: elaborate designtop

(2) For a model with testbench, you must pass the arguments as follows: elaborate dut\_top -vcs "tb\_top"

Where, "dut\_top" is the design top, and "tb\_top" is the testbench top.

(3) Set the cdc\_number\_of\_processes application variable before the sg\_read\_project command to specify if value of the -j argument of the elaborate command should be generated in the internal.tcl and vc\_setup.tcl files created by the sg\_read\_project command.

■ read\_verilog: Reads in one or more design or library files in Verilog format.

#### Syntax:

read\_vhdl: Reads in one or more designs or library files in VHDL format.

#### Syntax

read\_sverilog: Reads in one or more design or library files in SystemVerilog format.

#### Syntax

## Application Variables that Impact Reading a Design

There are few application variables that affect the design read and database generation. Before you start reading the design, ensure that you review and set these application variables as per your design read requirements.

- analyze\_skip\_translate\_body

- hierarchy\_delimiter

- sh\_continue\_on\_error

- language\_check\_hierarchy\_format

- enable\_timing\_arc\_for\_bbox\_detection

- prefer\_lib\_or\_rtl\_model

For details on each of these application variables, refer to the man pages.

# **Performing VC SpyGlass Lint Checks**

Performing VC SpyGlass Lint checks involves performing language checks, performing structural checks.

To perform LINT checks, use the following command:

```

%vc_static_shell> check_lint

%vc_static_shell> check_lint -help

Usage: check lint # Invoke VC SpyGlass Lint application

```

# **Analyzing Reports**

After performing VC SpyGlass Lint checks, analyze the reports that VC SpyGlass Lint generates.

# Working with Methodologies and Goals

GuideWare is the testing platform to check the functionality of various goals by running them on different types of designs. The designer keeps modifying and adding goals until the desired coverage is achieved from these goals.

This section explains the following topics:

- "Terminology"

- "Development Phases and Methodologies:"

- "RTL Handoff"

- "Layout Handoff"

- "Understanding GuideWare Goals"

- "Setting Up Methodology/Goals"

- "Running Custom Goals"

# **Terminology**

This section defines some commonly used terms that have a specific meaning in the VC SpyGlass environment.

- Tag: In VC SpyGlass environment, a 'Tag' represents the atomic unit of RTL analysis and checking performed by the VC SpyGlass software. Although a 'Tag' can be configured, it cannot be further sub-divided to select what analysis is performed.

- Violation Message: A violation message (or simply a message) is unit of VC SpyGlass reporting. When a VC SpyGlass 'Tag' detects a design condition not consistent with the rule requirement, it reports each such occurrence as a (violation) message. In addition to text message, such report usually contains other supporting data, such as back-reference in RTL source code where such problem originates, schematic highlight of the problem, detailed tables and graphs (as in power activity over time), waveform for a formal 'witness' (such as a false path proven to be not a false path), and so on.

- Parameter: In VC SpyGlass environment, a 'Parameter' is like an option to a tag that dictates the tag behavior. Parameters are typically used to make the tag do specific or detailed analysis of the RTL.

- Goal: A VC SpyGlass goal is a collection of relevant tags that are grouped together to perform a specific task. In addition to the tag list, a goal may further configure the parameters and redefine severity labels assigned to these tags. VC SpyGlass software release contains a useful set of many widely applicable goals. However, a user may fine-tune existing goals or create new goals to meet their specific design and workflow needs.

- Methodology: A VC SpyGlass methodology is a set of relevant goals that are grouped together to achieve a particular design goal. In addition to software, these sub-methodologies contain detailed documentation to assist customer in understanding specific usage and debug nuances.

- Severity: A VC SpyGlass violation message is tagged with an attribute, called severity, which helps to identify the criticality of reported message, within the context of a goal and sub-methodology being run. VC SpyGlass supports four main severity classes: FATAL, ERROR, WARNING, and INFO. A VC SpyGlass tag or goal can define a (severity) text label belonging to one of the above classes, and attach it to a tag.

#### Terminology

- Waivers: A VC SpyGlass 'waiver' is a method for user to review a tag (violation) message and flag a specific occurrence (or set of occurrences) as acceptable in context of their design and workflow. This is a very important mechanism to flag an apparently non-compliant design scenario as intended and verified by actual design or verification engineer. In the SoC design workflow, the VC SpyGlass waivers play a very significant role both in Block regressions and in Block handoff to SoC integration and implementation teams.

- SGDC: SGDC is an abbreviation for 'VC SpyGlass Design Constraints', and is used to capture additional designer intent of the block/SoC functionality which are not obvious at RTL/netlist. SGDC is used for capturing a wide variety of design intent, related with clock domain crossing, power, testability, etc.

## **Development Phases and Methodologies:**

A VC SpyGlass methodology is a set of relevant goals which represents a sign-off phase of ASIC development. Methodology includes goals which are arranged with pre-defined parameter.

## **Development Levels.**

Currently we use lint at two major development levels, block level SoC level.

#### **Block level Development**

The process of the development of a new RTL goes through progressive RTL refinement starting with simpler goals that meet the functional requirements, such as functional correctness and simulation and synthesis readiness of the code. As the RTL code and design constraints mature, the design goals evolve to performance, testability, and meeting handoff requirements. In this field of use, this design phase recommends three methodology flow.

#### **SoC level Integration and Implementation**

During SoC design or a subset of design (sub-system) that has been integrated by using various blocks, consistency across blocks is required.

This field of use involves checks related to inter-block/inter-IP issues. In addition, it ensures that block constraints are consistent with SoC constraints. In this field of use, this design phase recommends a four-stage flows.

## **Development phases**

## **Initial RTL Development**

The initial RTL design goal set contains a set of checks for the stage of the

Development Phases and Methodologies:

project when the RTL is still in coding development and may not be functionally complete. The idea is not necessarily to be clean all at once but provide a starting point for getting to the clean RTL.

The design team faces the following lint related challenges during this stage:

- Issues related with correct code capture

- Issues related with simulation and synthesis

- Issues with basic connectivity

- Issues related with basic structure like combinational loops and multiple drivers

#### **Initial RTL Development on block level**

During this stage, an initial version of the RTL is completed, and an initial set of SGDC constraints are available. This stage involves basic structural and sanity checks of the design (and constraints, wherever appropriate). In addition, issues related to connectivity, synthesizability, preliminary clocks, and reset integrity issues, such as glitches and clock-MUXing are also checked during this stage.