Jawar Singh · Saraju P. Mohanty Dhiraj K. Pradhan

# Robust SRAM Designs and Analysis

# Robust SRAM Designs and Analysis

# Robust SRAM Designs and Analysis

Jawar Singh

Indian Institute of Information Technology

Design and Manufacturing

Dumna Airport Road

Jabalpur

India

Dhiraj K. Pradhan University of Bristol Merchant Venturers Building Woodland Rd. Bristol United Kingdom Saraju P. Mohanty University of North Texas Discovery Park, 3940 N. Elm, Room F247 Denton USA

ISBN 978-1-4614-0817-8 ISBN 978-1-4614-0818-5 (eBook) DOI 10.1007/978-1-4614-0818-5 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2012936831

#### © Springer Science+Business Media New York 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

Jawar Singh dedicated this work to his grandmother Narayni Devi and grandfather late shri Kehari Singh

Saraju P. Mohanty would like to dedicate this work to Uma, parents, and sisters.

Dhiraj K. Pradhan would like to dedicate this work to his family

## **Preface**

During the past decades, Complementary Metal Oxide Semiconductor (CMOS) technology has emerged as the dominant fabrication method and became the exclusive choice for semiconductor memories. Particularly, Static Random Access Memories (SRAMs) that play a significant role in the memory hierarchy of a modern computer system and continue to be a critical component across wide range of microelectronics applications from consumer wireless to high performance server processors, multimedia and System-on-Chip (SoC) products. SRAM bitcells in general are made of minimum geometry devices for high density to keep pace with CMOS technology scaling; as a result, they are the first to suffer from technology scaling induced side effects. Therefore, several alternate SRAM bitcell circuits and architectures have recently been proposed to meet the nano-regime challenges such as low-power, process variation and soft errors. Emphasis is also given on alternate devices such as Tunnel Field Effect Transistors (TFETs) based SRAM bitcells for low power applications.

The objective of this book is to provide a systematic and comprehensive insight which aids the understanding of SRAM bitcell circuits, architectures, and design and analysis techniques. The nano-regime challenges such as low-power, process variation and soft errors are the core issues considered while designing and analyzing the SRAM bitcells in depth. Robust SRAM designs and analysis techniques show circuit and embedded system designers, researchers, and engineers various aspect of design and analysis of SRAM bitcell circuits and arrays. The above concepts are further elaborated to provide in depth guidance to large cache design needed in embedded and portable systems. The text provides alternative topologies to six-transistor (6T) SRAM which are more robust when implemented using state-of-the-art nano-scale CMOS technology. Topologies for low-power SRAM bitcells are classified on the basis of their robustness and elaborated along with their merits and de-merits. Various quality metrics are discussed to meet the small and large sized cache memories.

The content of this book is directed to nano-scale VLSI design engineers, graduate students in electrical engineering, and computer scientists who are about to start their research in SRAM design. It is an important source for engineers

viii Preface

who intended to develop and understand the different aspects of SRAM. The text assumed that readers have basic knowledge and familiarity with electronic circuits and devices. The goal of this book is to train the VLSI design engineers and students to design SRAM and cache architecture rationally.

This book provides a sufficient amount of fundamentals to become familiar with the terminology of the SRAM design and analysis. The main objective is to achieve in depth knowledge in few topics such as operation, design and analysis of CMOS and TFET based SRAMs. The book is organized in six chapters: (1) Introduction to SRAM, (2) Design Metrics of SRAM Bitcell, (3) Singleended SRAM Bitcell Design, (4) 2-Port SRAM Bitcell Design, (5) SRAM Bitcell Design using Unidirectional Devices, and (6) NBTI and its effect on SRAM. The introductory description of the SRAM serves as a basis for understanding the importance of SRAM in memory hierarchy and need of basic building blocks for the realization of cache memories. Basic operations and static and dynamic stability analysis for small and large sized caches show how conventional methods do not provide adequate data points for stability analysis. Case study of single-ended six-transistor and 2-port SRAM bitcells based cache modules show the complete design flow of SRAMs. The implications in realizing of SRAM using unidirectional devices such as TFETs are studied in details and two different SRAM bitcells using TFETs are compared with standard six-transistor CMOS SRAM bitcell. Finally, the impact of Negative Bias Temperature Instability is studied on different SRAM configurations.

Authors of this book are grateful to all the people without whom the work could not have been accomplished. Saraju P. Mohanty will like to acknowledge Dean College of Engineering at UNT. He will acknowledge CSE department chairman, colleagues, and staff for their support. He will like to acknowledge all his past and current students.

Authors would like to thank invaluable support from our families during the preparation of this book. Jawar Singh would like to express his appreciation to his wife Jyoti, their daughter Jeevika and son Siyon for their understanding and support. Saraju P. Mohanty would like to express thanks to Uma, parents, and sisters.

Jawar Singh Saraju P. Mohanty Dhiraj K. Pradhan

# Contents

| 1 | Intr | oduction to SRAM                                       |

|---|------|--------------------------------------------------------|

|   | 1.1  | CMOS Technology Scaling                                |

|   | 1.2  | Why SRAM?                                              |

|   | 1.3  | SRAM Architecture                                      |

|   |      | 1.3.1 SRAM Bitcell                                     |

|   |      | 1.3.2 Address Decoders                                 |

|   |      | 1.3.3 Precharge Circuit                                |

|   |      | 1.3.4 Sense Amplifiers                                 |

|   |      | 1.3.5 Write Drivers                                    |

|   | 1.4  | SRAM Design Issues and Challenges                      |

|   |      | 1.4.1 Conflicting Device Size Requirements             |

|   |      | 1.4.2 Process Variation                                |

|   |      | 1.4.3 Bitline Leakage Current                          |

|   |      | 1.4.4 Partial Write Disturbance                        |

|   |      | 1.4.5 Soft Errors                                      |

|   | 1.5  | SRAM Bitcell Topologies                                |

|   |      | 1.5.1 Non-isolated Read-Port SRAM Bitcell Topologies   |

|   |      | 1.5.2 Isolated Read-Port SRAM Bitcell Topologies       |

|   |      | 1.5.3 Low-Leakage Asymmetric SRAM Bitcell              |

|   | 1.6  | Summary                                                |

| 2 | Desi | gn Metrics of SRAM Bitcell                             |

|   | 2.1  | Standard 6T SRAM Bitcell: An Overview                  |

|   |      | 2.1.1 Read Operation                                   |

|   |      | 2.1.2 Read SNM Measurement                             |

|   |      | 2.1.3 Write Operation                                  |

|   |      | 2.1.4 Write SNM Measurement                            |

|   |      | 2.1.5 Relationships Between Transistor Drive Strengths |

|   | 2.2  | Other SRAM Bitcell Stability Metrics                   |

|   |      | 2.2.1 N-Curve Stability Metrics                        |

|   |      | 2.2.2 Static Voltage and Current Metrics 4             |

x Contents

|   |      | 2.2.3 Power Metrics                                                  | 43  |

|---|------|----------------------------------------------------------------------|-----|

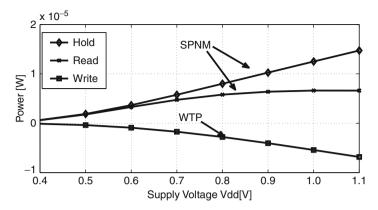

|   |      | 2.2.4 Dependencies of SPNM and WTP                                   | 43  |

|   |      | 2.2.5 Dependence on the Bitcell Ratio                                | 44  |

|   |      | 2.2.6 Dependence on the Supply Voltage <b>V</b> <sub><b>DD</b></sub> | 45  |

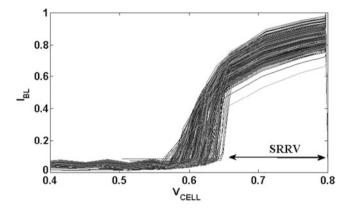

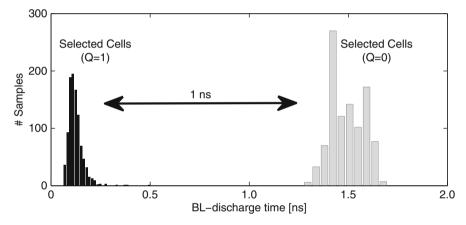

|   | 2.3  | Bitline Measurement Design Metrics                                   | 45  |

|   |      | 2.3.1 Read Stability Measurement                                     | 46  |

|   |      | 2.3.2 Writeability Measurement                                       | 49  |

|   | 2.4  | Dynamic Stability Analysis                                           | 51  |

|   |      | 2.4.1 Dynamic Read Stability                                         | 52  |

|   |      | 2.4.2 Dynamic Write Stability                                        | 54  |

|   | 2.5  | Summary                                                              | 56  |

| 3 | Sing | gle-Ended SRAM Bitcell Design                                        | 57  |

| • | 3.1  | Introduction                                                         | 57  |

|   | 3.2  | SRAM Bitcell Topologies                                              | 59  |

|   | ·    | 3.2.1 Transmission Gate Based Access 6T (TG-6T) SRAM Bitcell         | 59  |

|   |      | 3.2.2 Separate Read-Port 8T SRAM Bitcell                             | 61  |

|   | 3.3  | Single-Ended 6T SRAM (SE-SRAM) Bitcell                               | 62  |

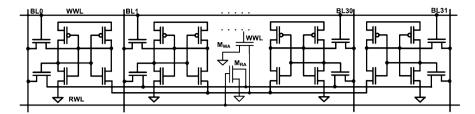

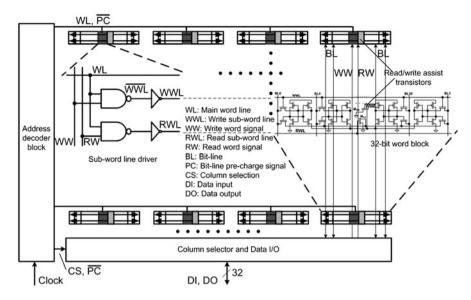

|   | 0.0  | 3.3.1 Array Organization of SE 6T SRAM Bitcell                       | 64  |

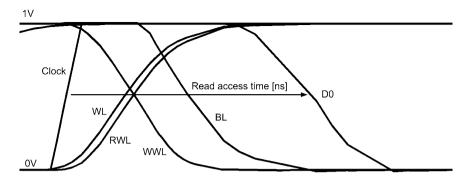

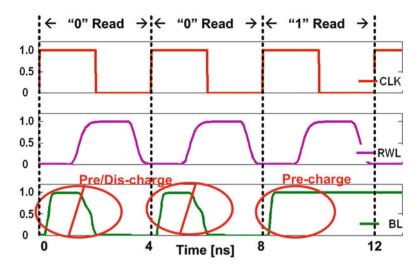

|   |      | 3.3.2 Read Operation                                                 | 65  |

|   |      | 3.3.3 Write Operation                                                | 66  |

|   | 3.4  | Read Stability and Write Ability Margins                             | 67  |

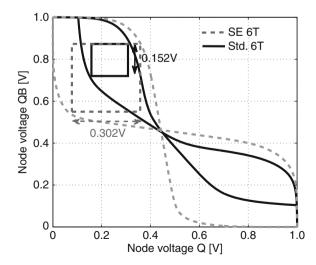

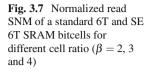

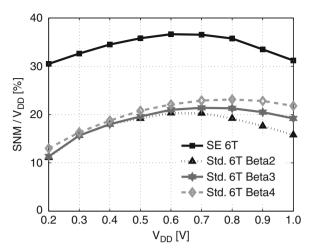

|   |      | 3.4.1 Read Stability Margin (SNM)                                    | 67  |

|   |      | 3.4.2 Write-Ability Margin (WAM)                                     | 68  |

|   | 3.5  | Sizing of Read and Write Assist Transistors in SE 6T Bitcell         | 71  |

|   |      | 3.5.1 Sizing of Read Assist Transistor                               | 72  |

|   |      | 3.5.2 Sizing of Write Assist Transistor                              | 76  |

|   |      | 3.5.3 Floor Plan to Eliminate the PWD                                | 76  |

|   | 3.6  | Performance and Power Dissipation                                    | 78  |

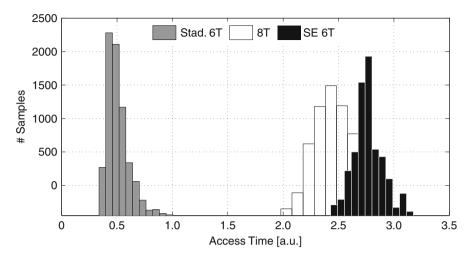

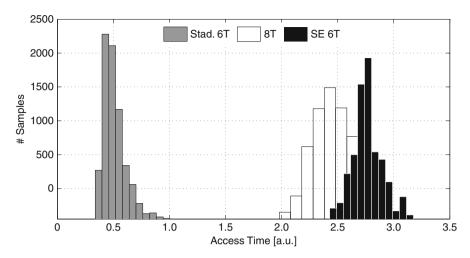

|   |      | 3.6.1 Read Access Time Distribution                                  | 79  |

|   |      | 3.6.2 Power and Leakage Dissipation                                  | 80  |

|   | 3.7  | Summary                                                              | 82  |

| 4 | 2.Pc | ort SRAM Bitcell Design                                              | 83  |

| 7 | 4.1  | Introduction                                                         | 83  |

|   | 4.2  | Existing 2-Port SRAM Bitcells.                                       | 85  |

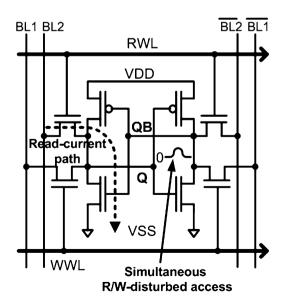

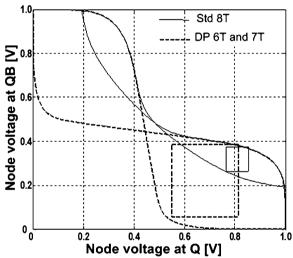

|   | 7.2  | 4.2.1 Standard 8T SRAM Bitcell.                                      | 85  |

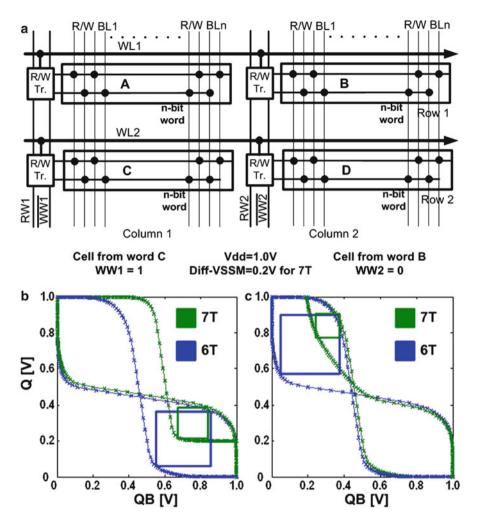

|   |      | 4.2.2 Differential Biasing 7T SRAM Bitcell                           | 86  |

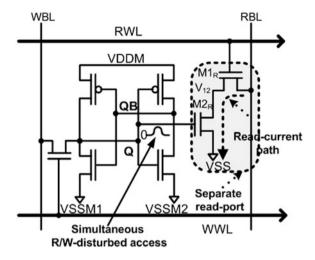

|   | 4.3  | 2-Port 6T SRAM Bitcell.                                              | 88  |

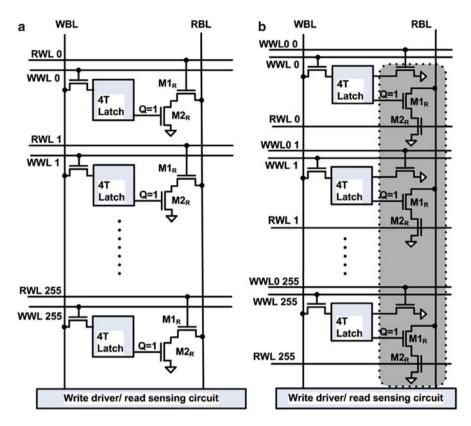

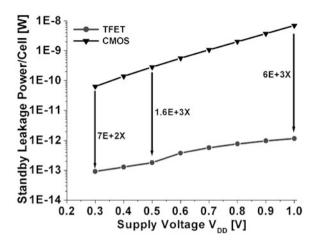

|   | ٦.٥  | 4.3.1 Array Organization                                             | 89  |

|   |      | 4.3.2 Read and Write Operations in 2-Port 6T Bitcell                 | 90  |

|   | 4.4  | Reconfigured Read-Port of a 2-Port of Bitcell                        | 91  |

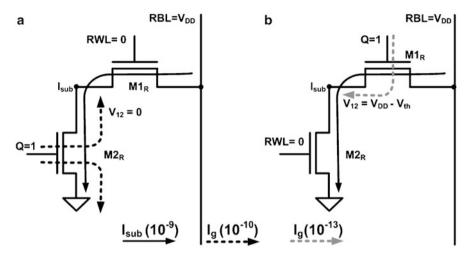

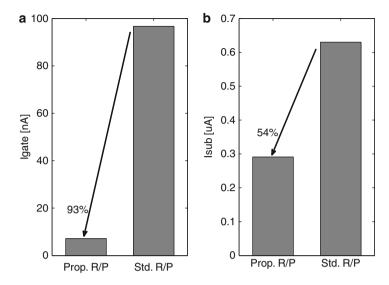

|   | 7.7  | 4.4.1 RBL Leakage and Gate Tunnelling Currents                       | 94  |

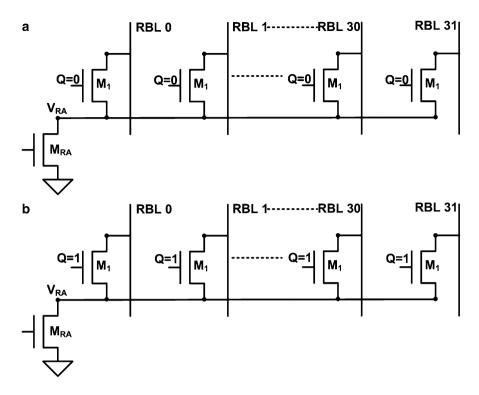

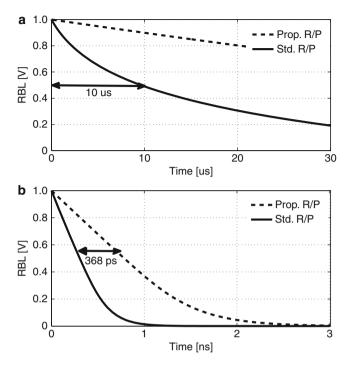

|   |      | 4.4.2 Read Bitline Leakage Scenario-1                                | 95  |

|   |      | 4.4.3 Read Bitline Leakage Scenario-2                                | 96  |

|   |      | TITIS ROUG DIGITIO LOGRAZO DOGITATIO-4                               | /() |

Contents xi

|    | 4.5  | Simultaneous Read/Write Access in 2-Port 6T-SRAM            | 99  |

|----|------|-------------------------------------------------------------|-----|

|    |      | 4.5.1 Reading Word A                                        | 100 |

|    |      | 4.5.2 Writing Word A                                        | 100 |

|    |      | 4.5.3 Simultaneous R/W Word A and C                         | 101 |

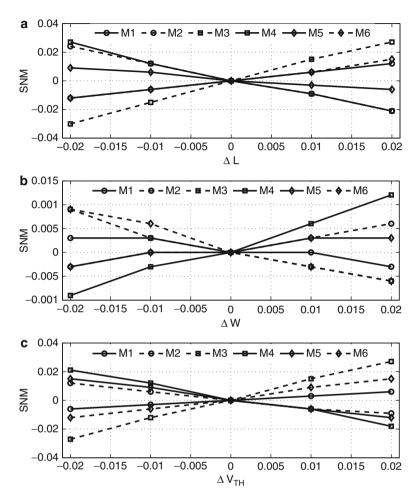

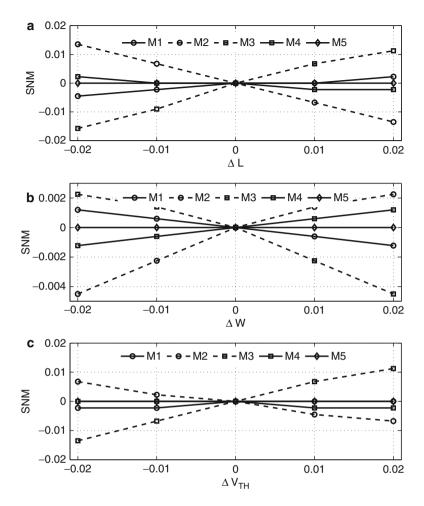

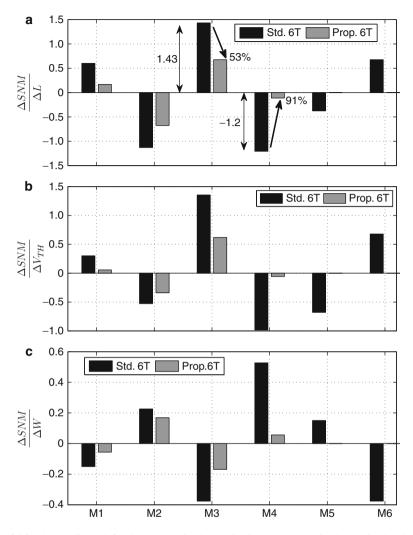

|    | 4.6  | SRAM Process Variation Sensitivity                          | 101 |

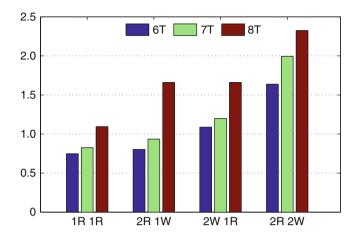

|    | 4.7  | Area, Power and Performance of the 2-Port SRAM Bitcells     | 105 |

|    |      | 4.7.1 Area Overhead with Multi-port Capabilities            | 106 |

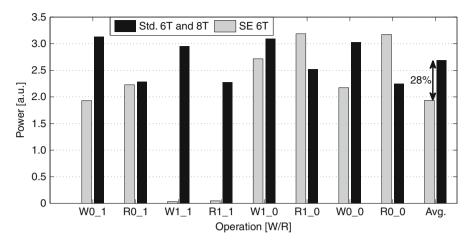

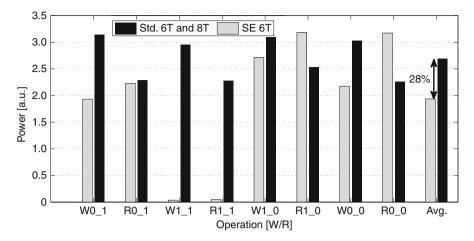

|    |      | 4.7.2 Power Dissipation                                     | 109 |

|    |      | 4.7.3 Performance                                           | 109 |

|    | 4.8  | Summary                                                     | 111 |

| 5  | SRA  | AM Bitcell Design Using Unidirectional Devices              | 113 |

|    | 5.1  | Introduction                                                | 113 |

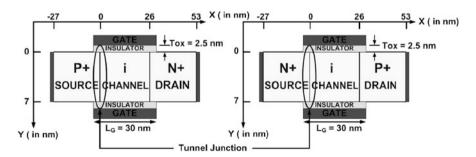

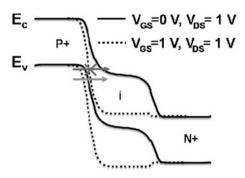

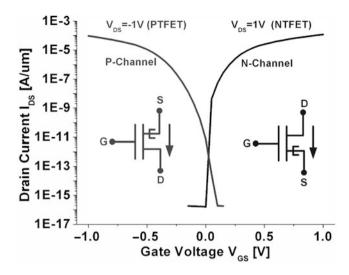

|    | 5.2  | Tunneling Transistors                                       | 115 |

|    | 5.3  | Development of TFETs Behavioural Model                      | 118 |

|    | 5.4  | Implications of Asymmetric Current on SRAM Design           | 120 |

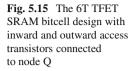

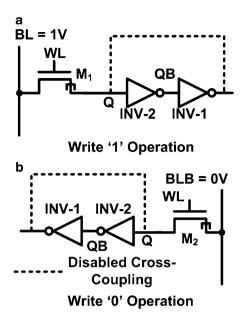

|    |      | 5.4.1 Inward Access Transistors SRAM Bitcell Topology       | 122 |

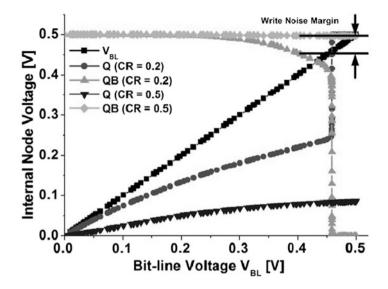

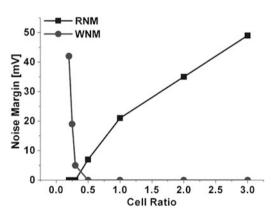

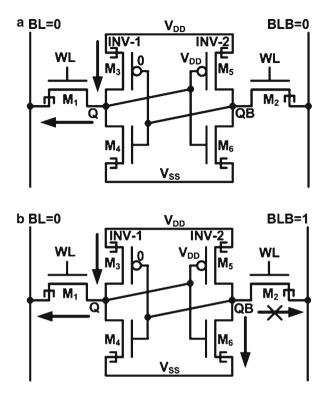

|    |      | 5.4.2 Outward Access Transistors SRAM Bitcell Topology      | 125 |

|    | 5.5  | A Case Study of a 6T TFET SRAM Bitcell Design               | 127 |

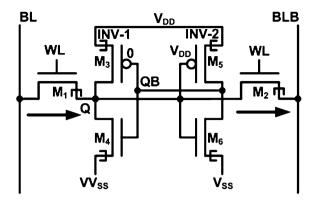

|    |      | 5.5.1 Read Operation in 6T TFET SRAM Bitcell                | 128 |

|    |      | 5.5.2 Write Operation in 6T TFET SRAM Bitcell               | 129 |

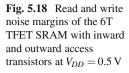

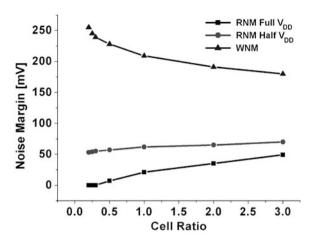

|    | 5.6  | SRAM Bitcell Design Metrics                                 | 130 |

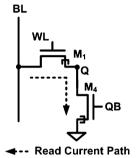

|    |      | 5.6.1 SRAM Bitcell Stability                                | 131 |

|    |      | 5.6.2 SRAM Bitcell Performance                              | 132 |

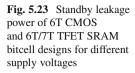

|    |      | 5.6.3 Leakage Power                                         | 134 |

|    |      | 5.6.4 Area                                                  | 134 |

|    | 5.7  | Summary                                                     | 135 |

| 6  | NBT  | FI and Its Effect on SRAM                                   | 137 |

| •  | 6.1  | Introduction                                                | 137 |

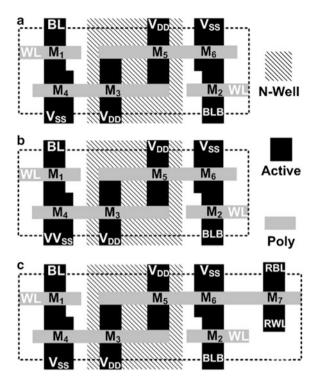

|    | 6.2  | The Physics of Negative Bias Temperature Instability        |     |

|    |      | (NBTI) and Its Impact                                       | 139 |

|    | 6.3  | NBTI Model                                                  | 142 |

|    | 6.4  | SRAM Bitcells Under NBTI                                    | 143 |

|    | 6.5  | Leakage Energy Saving Techniques in Caches                  | 146 |

|    |      | 6.5.1 Leakage Energy Saving Cache Configurations            | 147 |

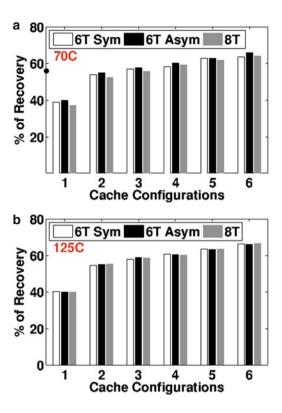

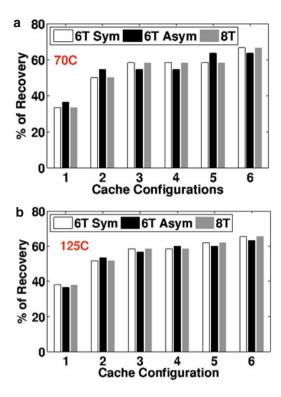

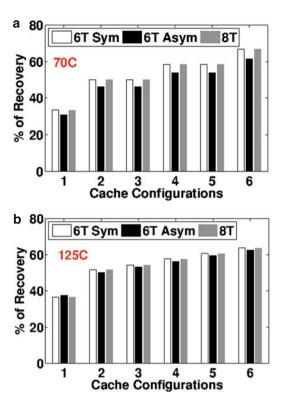

|    | 6.6  | Stability Recovery Under Different Cache Configurations     | 149 |

|    |      | 6.6.1 Read SNM Recovery                                     | 149 |

|    |      | 6.6.2 WNM Recovery                                          | 151 |

|    | 6.7  | Effect of NBTI Under Process Variation                      | 152 |

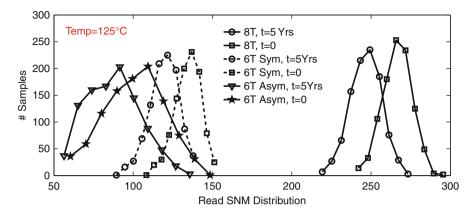

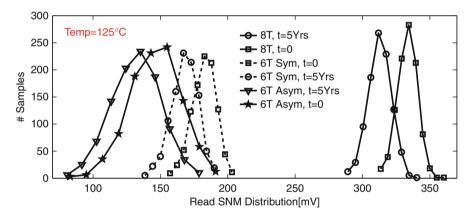

|    |      | 6.7.1 Read SNM Distribution Under Process Variation         | 153 |

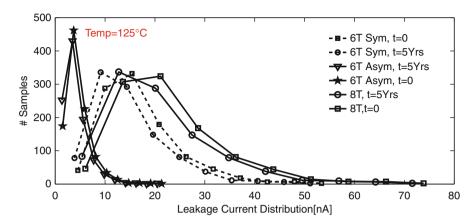

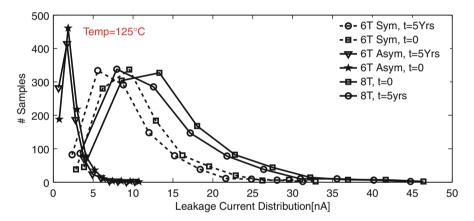

|    |      | 6.7.2 Leakage Current Distribution Under Process Variations | 154 |

|    | 6.8  | Summary                                                     | 155 |

| D. | fore | 200                                                         | 157 |

| ĸ  | eren | ices                                                        | 157 |

| In | dev  |                                                             | 165 |

# Chapter 1 Introduction to SRAM

### 1.1 CMOS Technology Scaling

CMOS technology scaling driven by Moore's law has rapidly increased VLSI designs performance by five orders of magnitude in last four decades. According to Moore's law, which was historically formulated in 1965, states the doubling of the number of transistors per generation on an integrated circuit almost every 2 years (usually 18–24 months) [80]. Since that time, Moore's law has become the fundamental guideline for the semiconductor industry to scale down the process technologies of the future generations. The semiconductor industry is understandably desperate to see the pace of Moore's law continue, and that pace is dependent on the technology that can create those ever-shrinking transistors and to overcome the associated challenges of technology scaling. He also stated that the manufacturing cost per function in microprocessor would drop-off exponentially for future generation technologies.

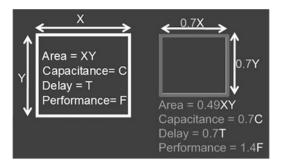

In general, scaling the minimum feature size, length and width by about 30% (Moore's magic number) for each new technology generation, theoretically yields the following:

- 1. Doubles the device density, while area lowers by  $(0.7*Y \times 0.7*X) \sim 50\%$ , packing in more devices in the same area, which effectively lowers the cost per transistor:

- 2. Reduces the total capacitance by 30% which allow gate delays to decrease by 30%, resulting in increase in operating speed up to 43%;

- 3. Accordingly the power consumption ( $Power \propto CV^2 f$ ) should decrease for a given circuit by 30–65% due to smaller transistors and lower supply voltage [16].

Figure 1.1, illustrates the CMOS technology scaling. This 30% magic number dictates the next generation of CMOS technology according to Moore's low. The idea of technology scaling is very attractive. The Semiconductor industry has worked very aggressively to continue this trend of technology scaling, however, the pace of this aggressive scaling has been slow down in the recent past. In order

**Fig. 1.1** Illustration of CMOS technology scaling for future generations

to drive next generation technology node from the Moore's magic number, if the current technology node is 65 nm then the next technology node is (65\*0.7) 45 nm. Similarly, all other technology generations have been derived.

Scaling supply voltage drastically reduces the dynamic power due to quadratic relation with supply voltage and static power. However, simply lowering  $V_{DD}$  will increase delay, so the device threshold voltage,  $V_{TH}$ , must also decrease in order to maintain the drive current. Lowering  $V_{TH}$  leads to an exponential increase in leakage power. Moreover, minimum feature sized and closely matched devices matter significantly, particularly when designing Static Random Access Memories (SRAMs), therefore, they are the first to suffer from the exponential trends of scaling. The continued scaling of CMOS technology has resulted several problems these include process induced variations, soft errors, transistor degradation due to ageing etc. However, these problems were less severe in the earlier generations.

## 1.2 Why SRAM?

The origination of the concept of the MOSFET based memory was first commercialized and perfected in the seventies. Robert Dennard of IBM envisaged the dynamic memory cell using a single MOSFET and a capacitor in 1968 [30]. The first MOSFET based dynamic random access memory (DRAM) chip with 2k-bits was developed in 1971 with several process improvements in leakage control. However, DRAM performance has not kept the pace with the performance of the processors from the very beginning [29,42] due to long access time and more power hungry. The dynamic nature of DRAM requires that the memory must be refreshed periodically so as not to lose the content of the memory cells.

The growing gap between the processors and the DRAM performance has dictated the need of different levels of memory hierarchy in the processor architectures. The memory hierarchy ranges from high-performance, small sized but expensive on-chip memories to slower, large sized but inexpensive off-chip memories such as DRAM, magnetic or optical memories. To meet the system performance requirements, the processor tries to keep frequently used data and

1.2 Why SRAM? 3

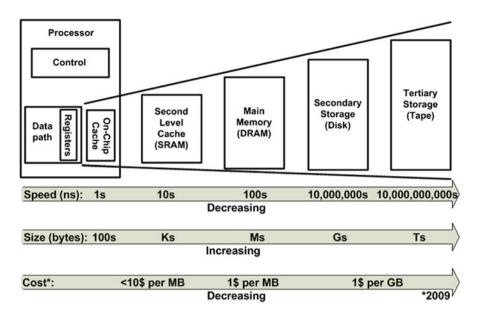

Fig. 1.2 Typical memory hierarchy of a modern computer system

instructions closer to itself, that is, in the faster on-chip memory, which is referred as "cache" memory. A typical memory hierarchy of a modern computer system is depicted in Fig. 1.2. The on-chip cache memories are often called L1, L2 and even L3. The different levels of cache memories are static random access memories (SRAMs) and they dominate the memory hierarchy in performance but they are often integrated in a lesser capacity due to area limitations and the high cost per bit. The speed and the cost per bit decrease as one moves from registers to tertiary storage, however, data storage capacity increases.

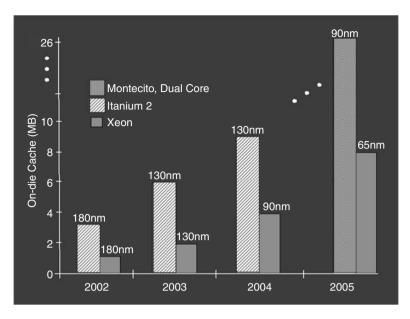

SRAMs continue to be critical component across a wide range of microelectronics applications from consumer wireless to high performance server processors, multimedia and System on Chip (SoC) applications. Modern high performance processors and SoC application demands more on-chip memory to meet the performance and throughput requirements. However, it is also not feasible to embedded large amount of memory needed into the chip due to area limitations and the high cost per bit. Figure 1.3 shows the increasing trend of on-die cache memory for different processors based on different technology nodes. It is also projected that the percentage of embedded SRAM in SoC products will increase further from the current 84% to as high as 94% by the year 2014 [48]. Furthermore, their is a huge demand of cache memory in modern computer systems as microprocessors design paradigm has been shifted to multi-core architectures. As shown in Fig. 1.3, the amount of on-die cache in Montecito, Dual Core, Intel processor has increased significantly as compared to Xeon single core processor.

Fig. 1.3 The amount of on-die cache memory for different processors based on different technologies

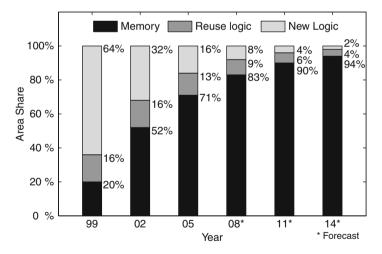

Fig. 1.4 Typical trend of memory and logic area on an system-on-chip (SoC) die [48]

Typical trend of embedded memory and logic area on a system-on-chip (SoC) is also shown in Fig. 1.4. This trend shows that how the share of SRAM on a die has drastically increased from 20% in 1999 to 94% as forecast in 2014. This growing trend is mainly to provide faster access by eliminating the delay across the chip interface. Also embedded memories are designed with rules more

1.3 SRAM Architecture 5

aggressive than the rest of the logic on a SoC die, therefore, they have dense packing which makes them more prone to manufacturing defects. This trend has mainly grown due to ever increased demand of performance and higher memory bandwidth requirement to minimize the latency, therefore, larger L1, L2 and even L3 caches are being integrated on-die. Hence, it may not be an exaggeration to say that the SRAM is a good technology representative and a powerful workhorse for the realization of modern SoC applications and high performance processors. In addition, SRAM scaling signifies the huge potential of decreasing the cost per function in microprocessors as well.

#### 1.3 SRAM Architecture

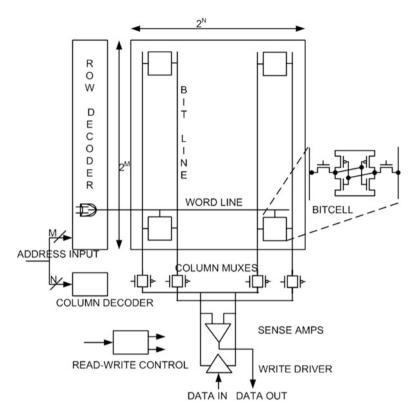

An SRAM cache consists of an array of bi-stable memory bitcells along with peripheral circuitries, such as address (row and column) decoders, sense amplifiers, write drivers and bitline pre-charge circuits etc. Peripheral circuitries enable reading from and writing into the array. A classic SRAM memory architecture is shown in Fig. 1.5. The memory array consists of  $2^n$  words of  $2^m$  bits each. An SRAM array is composed of millions of identical bitcells. For example, a 32 Mb cache memory is composed of 33,554,432 bitcells, a number so great that even an exceptionally rare event can have a noticeable impact on product yield. As a result, small improvement in reliability, performance and saving in static power will have a great impact on the entire processor or SoC product. Therefore, optimization of the SRAM bitcell designs for a target application is an active area of research. In high performance processors, operating speed and bitcell area are the prime concern in order to have high density caches, while, maintaining an adequate reliability. However, in energy constrained applications such as sensor nodes or medical implants, energy efficiency and reliability are the main issues.

A memory bitcell is a circuit capable of storing a single bit of information – "1" or "0". They share a common wordline (WL) in each row and a bitline pairs (BL, complement of BL) in each column of an SRAM array. The dimensions of each SRAM array are limited by its electrical characteristics such as capacitances and resistances of the bitlines and wordlines used to access bitcells at uniform delay in the array. Memory arrays are organized such that the horizontal and vertical dimensions are of the same order of magnitude. Therefore, large size memories may be folded into multiple blocks with limited number of rows and columns. After folding, in order to meet the bit and word line capacitance requirement each row of the memory contains  $2^k$  words, so the array is physically organized as  $2^{n-k}$  rows and  $2^{m+k}$  columns. Every bitcell can be randomly addressed by selecting the appropriate wordline (WL) and bitline pairs (BL, complement of BL), respectively, activated by the row and the column decoders.

Fig. 1.5 A general SRAM array structure

#### 1.3.1 SRAM Bitcell

An SRAM bitcell is the basic building block of the SRAM array, as shown in the inset of Fig. 1.5. Each bitcell eircuit is capable of storing single bit of information. It provides non-destructive read operation, write capability and data storage as long as the SRAM bitcell is powered up. A standard six transistor (6T) SRAM bitcell consists of two cross coupled inverters and two access transistors connected to each data storage node. The inverter pair forms a latch and holds the binary information. True and complimentary version of the binary data are stored in the storage nodes. The access transistors allow access to data storage nodes during read and write operations and also provides isolation from the other neighbouring circuits during hold state. The bitcells are accessed horizontally by asserting the wordline during read and write operation. When wordline of a row is asserted 'HIGH', all the memory bitcells in the selected row become "active" and can be ready for read and write operations. To decode m wordlines, one needs  $log_2m$  address bits. An SRAM bitcell has three modes of operation: read, write and standby; or in other words, it can be in three different states such as reading, writing or data retention.

1.3 SRAM Architecture 7

#### 1.3.2 Address Decoders

To implementing an N-word memory where each word is M bits wide, a general approach is to arrange the memory words in a linear fashion. In order to read or write, each word is selected with N select lines to access N independent locations. However, this approach seems very simple and works well for small memories, but puts in trouble if N is large (for larger memories). For instance, in a 32 Mb (2<sup>25</sup>) word-oriented SRAM with a 32-bit ( $2^5$ ) word width, N =  $2^{20}$  (N = 1,048,576) select lines are needed - one for every word. However, for a 32 Mb bit-oriented SRAM, N becomes  $2^{25}$  (33,554,432). Hence, a large number ( $\sim$ 1 million) of select lines or signals are needed to address this word-oriented memory, if arranged in a linear fashion. As a result, this (linear) approach leads to insurmountable wiring (interconnects) and packaging requirement. In order to reduce the number of select lines or in other word the number of interconnects, a address decoder is inserted. Address decoder allows the number of select lines in the SRAM to be reduced by a factor of  $log_2N$ , where N is the number of independent locations. For instance, in a 32 Mb (2<sup>25</sup>) word-oriented SRAM with a 32-bit (2<sup>5</sup>) word width, this approach reduces the number of select lines from  $\sim 1$  million to 20 ( $log_2 2^{(25-5)} = 20$ ) address bits A0, A1,...A19. This SRAM can be orgnized in 32 blocks each of which has 1.024 rows and 1.024 columns

There are two types of decoders used in the SRAM, that is, row decoder and the column decoder. The design of these decoders has substantial impact on the SRAM performance and power consumption. Row decoders are needed to select one row of wordlines out of a set of rows in the array according to address bits. While column decoder select the particular bitline pairs out of the sets of bitline pairs in the selected row. A fast decoder can be implemented using AND/NAND and OR/NOR gates. These decoders can be implemented in two different styles, namely static and dynamic. The choice of a design styles depends on the SRAM area, performance, power consumption and architectural considerations. The static NAND-type structure can be chosen because of its low power consumption during the decoded row transitions. While dynamic structure can be chosen because of its speed and power improvement over the static NAND gate based decoder.

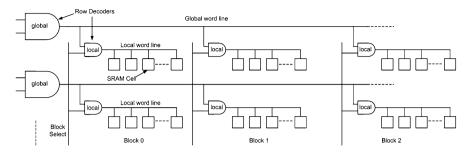

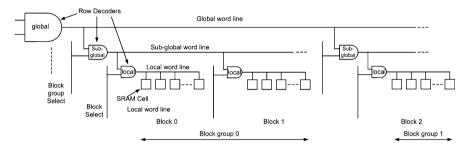

For large SRAM arrays where total address space is A0, A1,...A19 address bits. In this address space, row decoder requires 10 bits row decoder and 10 bits for column decoder. For the implementation of a row decoder 10-input NOR gate is needed per row. This poses different challenges such as large fan-in which has negative impact on the performance, power dissipation etc. Therefore, splitting a large gate into small logic lavels in general produces a faster, area efficient and cheaper implementation. However, for small single-block memories single stage row decoders are good choice. Today most memories split the row decoder into several blocks decoded by separte decoder stages. The split or multi stage decoder approach has proven to be more efficient for larger memories, it reduces the number of transistor, fan-in, power and loading on the address input buffers. The multi stage decoder structures are classified into two broad categories such as Divided Wordline (DWL) [43] and Hierarchical Word Decoding (DWD) [119] structures.

Fig. 1.6 Divided wordline row decoder [43]

Fig. 1.7 Hierarchical Word Decoding (DWD) scheme [119]

Figure 1.6 shows the DWL structure in which SRAM is partitioned into blocks. In order to read or write a block, local wordline is activated when both global wordline and block select are asserted. Since, only one block is activated at a time for read or write operation, as a result the DWL structure reduces both wordline delay and power consumption. For high density and large SRAMs greater than 4 Mb, the hierarchical wordline decoding structure, as shown in Fig. 1.7 was proposed to cope with increased delay and power consumption.

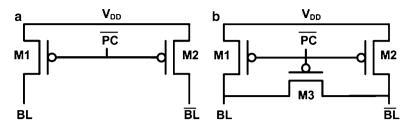

# 1.3.3 Precharge Circuit

In all SRAMs, for each column in the bitcell array there is a bitline pair (BL and complement of BL). Each pair of bitlines is connected to a precharge circuit. The function of this circuit is to pull-up the bit lines of a selected coulmn to  $V_{DD}$  level and perfectly equalized them before the read or write operation. A typical precharge circuit is shown in Fig. 1.8a. It is composed of a pair of PMOS transistors and a precharge circuit enable signal  $(\overline{PC})$ , when both the transistors are in ON state, that is,  $\overline{PC}$  is active low, bitlines (BL and complement of BL) are connected to  $V_{DD}$ . Recently, two transistor precharge circuit shown in Fig. 1.8a has been replaced by a three transistor configuration as shown in Fig. 1.8b. In this precharge circuit

1.3 SRAM Architecture 9

Fig. 1.8 Precharge circuits for SRAM array

transistor M1 and M2 connect the bitlines (BL and complement of BL) to  $V_{DD}$  for pull-up, while transistor M3 equalizes both the bitlines. In precharge circuit PMOS transistors are commonly used because they have good  $V_{DD}$  passing capacity.

# 1.3.4 Sense Amplifiers

Sense Amplifiers (SA) are one of the most important peripheral circuits in the CMOS Static Random Access Memories, and become a separate class of circuits in the literature. The primary function of a SA in SRAMs is to amplify a small differential voltage developed on the bitlines during read access and translate it to full swing digital output signal. A small differential voltage is developed by pulling down one of the precharged bitline by the read access bitcell. Due to small bitcell size and large bitlines capacitance, time required for read operation increases significantly, or in other words, read access time increases. These circuits have strong impact on the read access time of a memory (or performance), as they are used to retrieve the stored data in the memory array by amplifying small signal variations on the bitlines.

The design of fast, low-power and robust SA circuits is a challenge, due to the fact that in modern memory design bitlines exhibit a significantly large capacitance. A large number of bitcells per bitlines are generally embedded in modern SRAMs to increase the array density, increased sensitivity to process variations, environmental conditions and device mismatch. Hence, these challenges set limits in the sensing speed, robustness and introduces extra signal delay. The sense amplifier design, furthermore, depends on the timing requirements and layout constraints of the memory system. To alleviate some of the above challenges, sense amplifiers are often employ devices with non-minimum length and width. A sense amplifier is characterized by the following parameters: gain A, sensitivity S, current and voltage offsets  $V_{\it off}$  and  $I_{\it off}$ , common mode rejection ratio  $\it CMMR$ , rise time  $t_{\it rise}$ , fall time  $t_{\it fall}$ , and sense delay  $t_{\it sense}$ .

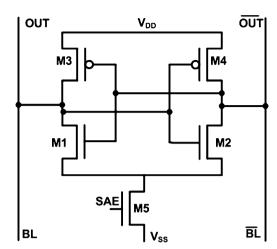

Figure 1.9 shows a commonly used current-mirror differential sense amplifier. The differential sensing is widely used to reject the common-mode noise that may present on both the bitlines. This noise may be induced on both SA inputs or bitline pair (BL and complement of BL) due to power spikes, capacitive coupling between

Fig. 1.9 Commonly used current-mirror differential sense amplifier

bitlines and between wordline and bitlines. This noise then attenuated by the value of CMMR and the true differential signal is amplified. Sensing operation in this commonly used current mirror differential sense amplifier begins with setting up the SA operating point by precharging and equalizing of the both the SA inputs, that is, the bitline pair (BL and complement of BL) of a selected column. Once both bitlines are precharged and equalized, wordline WL is asserted to activate the read-accessed bitcells that started build-up of the differential voltage on the bitlines. Once the differential voltage exceeds the sensitivity of the SA or overcomes the offset of SA, Sense Amplifier Enable (SAE) signal is issued to trigger the SA which amplifies the differential voltage caused by the bitcell (connecting one of the bitline to ground via one of the access and pull-down transistor) on the bitlines to full-swing digital output level. The read operation completes with the de-assertion of the SAE and WL. The gain A of a current-mirror sense amplifier is given by Eq. 1.1, and it is typically set to around ten.

$$A = -g_{mM1}(r_{o2}||r_{o4}) (1.1)$$

Where  $g_{mM1}$  is the transconductance of transistor M1, and  $r_{o2}$  and  $r_{o4}$  are small-signal output resistance of transistor M2 and M4, respectively. The gain A is directly related to the width of transistor M2 and M4 and can be increased by widening these transistor or by increasing the biasing current.

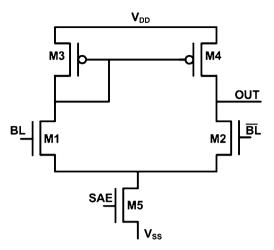

Another, most commonly used sense amplifier is latch-type, as shown in Fig. 1.10. This amplifier is comprised of two cross coupled inverters and a transistor M5 which isolates it from the bitlines and prevents the discharge of bitline on the '0' storage node. Sense operation in this type of sense amplifier begins with biasing it in the high gain metastable state by precharging and equalizing its inputs (or both bitlines). Additional pass transistors are commonly used to isolate the bitlines connected to precharge circuits. Once a differential voltage is developed

1.3 SRAM Architecture 11

**Fig. 1.10** Latch-type sense amplifier

**Fig. 1.11** Transmission gates based write driver circuit

on the bitlines exceed the sensitivity of the sense amplifier, Sense Amplifier Enable (SAE) signal is enabled and the bitlines isolation pass through transistors are turned off. The feed-back mechanism of this amplifier immediately picks up the differential voltage and drives the outputs to the full swing differential voltage.

#### 1.3.5 Write Drivers

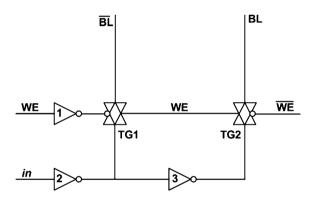

Write drivers are used by a group of columns in an SRAM array to control the bitline pair (BL and complement of BL) during write operation. As the bitline pair is precharged to  $V_{DD}$  before every operation, the write driver has just to act the pull down one of the two bitlines below the write margin of the SRAM cell during write operation according to the input data. There are different types of write drivers commonly used in SRAM array, some of the typical write driver circuits are discussed below. The write driver circuit shown in Fig. 1.11 comprises

**Fig. 1.12** Pass gates based write driver circuit

**Fig. 1.13** AND gates based write driver circuit

of two transmission gates (TG1 and TG2) and three inverter buffers (INV-1,INV-2 and INV-3). Inverter buffer 2 and 3 writes the data in to the bitlines (BL and complement of BL) via TG1 and TG2. Write driver is enabled by the Write Enable (WE) signal and drives the bitlines to data in. The TG1 and TG2 are activated by WE and its complementary  $\overline{WE}$ , as a result one of the bitline is discharged through the NMOS transistor of either inverter (INV-2 or INV-3). A successful write operation is ensured in the SRAM bitcell by pulling down the one of the bitlines well below the write margin of the bitcell. Therefore, the pull down strength of INV-2 and INV-3 plays a significant role in the write operation.

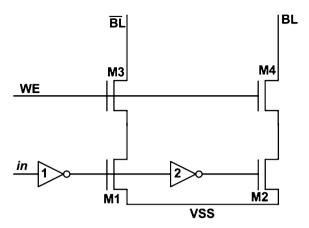

The write driver shown in Fig. 1.12 writes data through two stacked NMOS transistors, that is, M1, M3 and M2, M4, which form two pass-transistor AND gates. Write driver is enabled by the WE signal which activates the transistor M3 and M4, while data *in* enables the transistor M1 or M2 depending upon the input data through inverter buffers (INV-1 and INV2). When WE is enabled, one of the bitline (BL and complement of BL) is discharged from precharged level to ground through one of the transistor M1 or M2 depending upon the input data. Figure 1.13 shows another

implementation of a write driver. In this write driver, when WE is asserted, the combination of WE and data *in* turn on one of the pass transistor M1 or M2. As a result activated transistor (either M1 or M2) discharges the one of the bitline (BL and complement of BL) to the ground level. In SRAM architecture, only one write driver is needed per coulumn in an SRAM array, as a result, write drivers can be upsized to discharge large capacitive bitlines for a successful and faster write operation.

#### 1.4 SRAM Design Issues and Challenges

Unfortunately, the pace of ever-shrinking transistors has brought up many difficult challenges that threaten to stop the exponential trend of doubling the number of transistors per generation and drop-off of manufacturing cost. Perhaps some of the greatest challenges of technology scaling are exponential increase of leakage power, power density and device mismatch (process variation). As technology scales down leakage current increases exponentially and reliability goes down significantly due to poor stability noise margins and process variation. These technology scaling-induced side effects are further exacerbated by reduced supply voltage introduced in order to achieve energy efficiency or low-voltage operation. Achieving low-voltage operation in SRAM faces several challenges such as originating from process variation, related to bitcell read and write stability, sensing, and inefficient Computer Aided Design (CAD) methodologies.

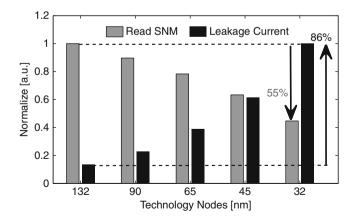

Figure 1.14 shows the comparison of normalized read Static Noise Margin (SNM) and leakage current of a 6T SRAM bitcell for different technology nodes. The minimum feature sized devices with cell ratio ( $\beta = 2$ ), is used for simulation using Predictive Technology Models (PTM) [88, 123]. It can be seen from the Fig. 1.14 that the read SNM of 6T bitcell is gradually decreasing with technology

Fig. 1.14 Comparison of read SNM and leakage current of standard 6T SRAM bitcell for different technology nodes

scaling, while the leakage current is exponentially increasing. Moving from 130 to 32 nm technology node, there is 55% reduction in the read SNM while there is 86% increase in leakage current. Therefore, alternative array structure and bitcell design topologies or methodologies are needed for nano-regime technologies that provide low standby power and higher stability margins. In the line of array structures, interleaved structure is commonly used while non-interleaved structure has been atteracted attention recently. Recently, several SRAM bitcell topologies have been proposed those have very good read SNM and write noise margin and capability to operate at low voltages.

#### 1.4.1 Conflicting Device Size Requirements

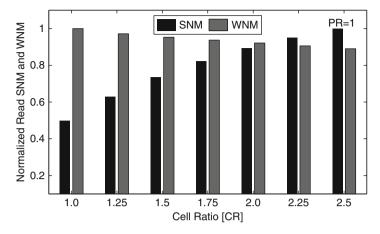

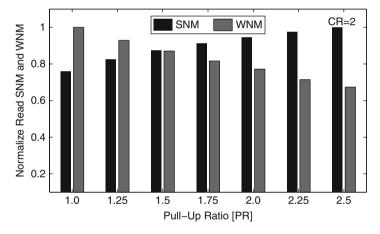

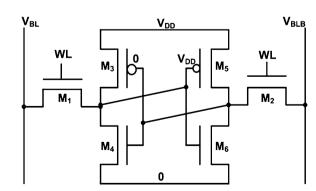

The standard 6T SRAM bitcell design space is continuously narrowing down due to shrinkage in device dimensions, attempting to achieve the high density and high performance objectives of on-chip caches. The SRAM bitcell stability and writeability margins are further degraded by supply voltage scaling. The degradation in margins is mainly due to conflicting read and write requirements of the device size in the 6T bitcell. As both read and write operations are performed via the same pass-gate (NMOS) devices, that is,  $M_1$  and  $M_2$ , as shown in Fig. 1.21. For a better read stability (read SNM), both pull down devices,  $M_4$  and  $M_6$  of the storage inverters must be stronger than the pass-gate devices,  $M_1$  and  $M_2$ . While for write operation the opposite is desirable, that is, pass-gate devices,  $M_1$  and  $M_2$ , must be stronger than pull up devices,  $M_3$  and  $M_5$ , to achieve the better write-ability, that is weak storage inverters and strong pass-gate devices. This conflicting trend is also observed when we simulated the read SNM and write noise margin for different cell ratios ( $\frac{W_4/L_4}{W_1/L_1} = \frac{W_6/L_6}{W_2/L_2}$ ) and pull up ratios ( $\frac{W_3/L_3}{W_1/L_1} = \frac{W_5/L_5}{W_2/L_2}$ ).

Figure 1.15 shows the standard 6T SRAM bitcells' normalized read SNM and

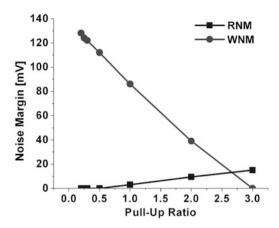

Figure 1.15 shows the standard 6T SRAM bitcells' normalized read SNM and WNM measured for different cell ratio (CR), while the pull-up ratio is kept constant (PR = 1). It can be seen from Fig. 1.15 that the SNM is sharply increasing with increase in the cell ratio, while there is a gradual decrease in the WNM. For different pull-up ratio (PR), the normalized read SNM and WNM exhibit the similar trend. For example, there is a sharp decrease in the read SNM and gradual increase in WNM with increasing PR, while CR is kept constant to 2, as shown in Fig. 1.16. In general, for a standard 6T bitcell the PR is kept to 1 while the CR is varied from 1.25 to 2.5 for a functional bitcell, in order to have a minimum sized bitcell for high density SRAM arrays. Therefore, in high density and high performance standard 6T SRAM bitcell, the recommended value for CR and PR are 2 and 1, respectively.

To achieve sufficient bitcell margins in the nano-meter regime, with optimum device size, choosing the right bitcell topology is vital to ease the difficulties encountered in the fabrication process in high density SRAM arrays. Many design techniques have been proposed to ensure sufficient margins, such as de-coupling of read and write operations by modifying the bitcell topology. For example, in

Fig. 1.15 Normalized read SNM and Write Noise Margin (WNM) of a standard 6T SRAM bitcell for different cell ratio (CR), while the pull-up ratio (PR) is fixed to 1

**Fig. 1.16** Normalized read SNM and Write Noise Margin (WNM) of a standard 6T SRAM bitcell for different pull up ratio (PR), while the cell ratio (CR) is fixed to 2

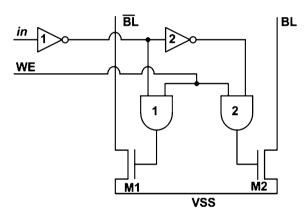

an 8T SRAM bitcell topology [23–25, 103], as shown in Fig. 1.25, two transistors were added to create an isolated read-port or read-buffer. The isolated read-port mechanism offers a static-noise-margin-free read operation. In these topologies read and write operations were performed via separate pass-gate devices, thus two are entirely isolated. It avoids the conflicting requirement of sizing the pass-gate devices, which exist in the standard 6T bitcell to achieve a delicate balance between read stability and write-ability. Hence, it widens the bitcell optimization space to a large extent by ensuring sufficient bitcell margins.

#### 1.4.2 Process Variation

However, aggressive scaling of CMOS technology presents a number of distinct challenges for embedded memory fabrics. For instance, smaller feature sizes imply a greater impact of process and design variability, including random threshold voltage  $(V_{TH})$  variations, originating from the fluctuation in number of dopants and polygate edge roughness [75, 104]. The process and design variability leads to a greater loss of parametric yield with respect to SRAM bitcell noise margins and bitcell read currents when a large number of devices are integrated into a single die. Predictions in [10] suggest the variability will limit the voltage scaling because of degradation in the SNM and write margin. Furthermore, increase in device mismatch that accompanies geometrical scaling may cause data destruction at normal  $V_{DD}$  [19]. Therefore, a sufficiently large read Static Noise Margin (SNM) and Write-Noise Margin (WNM) in a bitcell are needed to handle the tremendous loss of parametric yield.

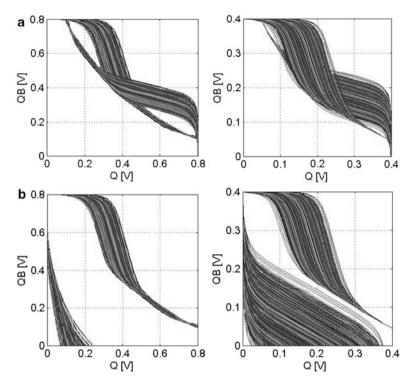

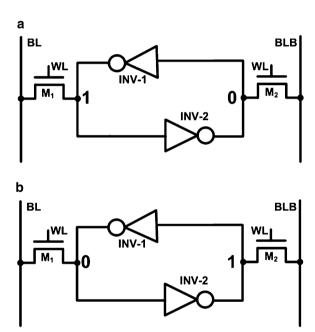

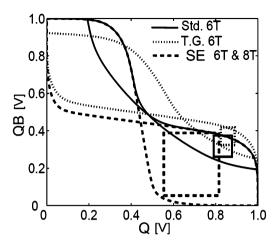

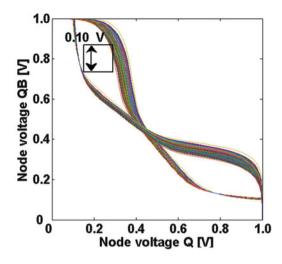

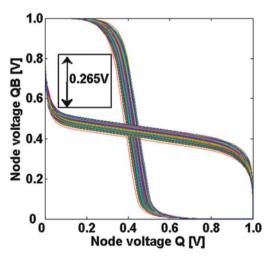

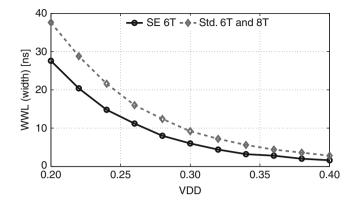

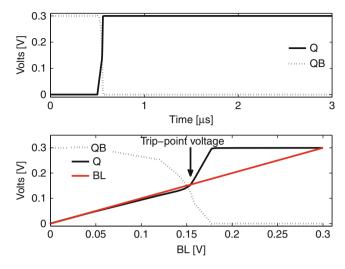

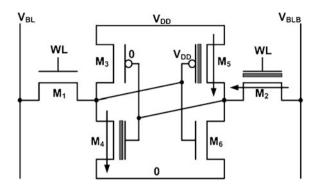

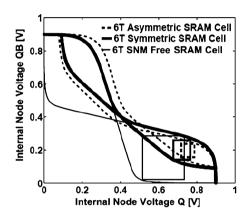

The stability of a 6T SRAM bitcell under process variation can be verified by examining its butterfly curve obtained by voltage transfer characteristics (VTCs) and inverses voltage transfer characteristics (VTCs $^{-1}$ ). The input–output voltage relations from Q to QB and from QB to Q are plotted on the same set of axes, assuming that bitlines and wordlines are biased properly, as shown in Fig. 1.17a, b. During read, three roots of intersection are desired, representing bistability of a SRAM cell. While during write, only one root of intersection is desired in order to flip the bitcell deterministically to one of the two data states, as set by the bitline polarity. The effect of process variation on SRAM read and write stability is evident from Fig. 1.17a, b. Reducing  $V_{DD}$  from 0.8 to 0.4 V in the simulation of an SRAM bitcell using 32-nm predictive technology files reveals a dramatic degradation in read and write butterfly curves as result poor read and write noise margins.

# 1.4.3 Bitline Leakage Current

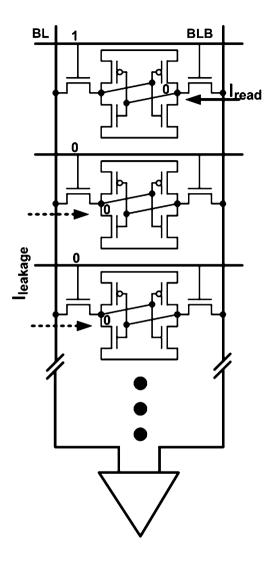

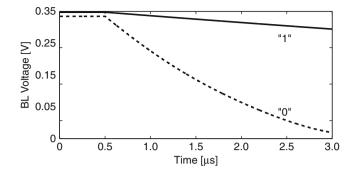

During the read access when the wordline is activated and access devices are enabled, the bitcell read-current,  $I_{read}$ , is the current sunk from the precharged bitline (BLB) (Fig. 1.18) connected to the bitcell node (Q) holding '0' via access device (M<sub>2</sub>), as shown in Fig. 1.21. At lower operating voltages,  $I_{read}$  is significantly reduced due to lower gate-drive voltage, which implies that the read access time increases substantially. This is undesirable from a performance point of view, but even more importantly it affects the ability to correctly sense the data.

The reduced read-current ( $I_{read}$ ) and increased aggregate leakage current from the unaccessed bitcells connected to the same bitlines can make conventional data sensing impractical. The reduced  $I_{read}$  and increased aggregate leakage current also restrict the number of bitcells per bitline and makes the SRAM array less effecient. Generally, in standard 6T SRAM bitcell differential sense-amplifier is used for detecting a small droop on one of the bitlines, BL or BLB, differentially with respect to the other bitline during the read cycle. A small droop in the BL or BLB is

**Fig. 1.17** Read and write stability examination under process variation. (a) Statistical butterfly curves simulated with intra-die variation at the nominal process corner in 32 nm technology node for read operation at  $V_{DD}=0.8$  and  $V_{DD}=0.4$  V. (b) Statistical butterfly curves simulated with intra-die variation at the nominal process corner in 32 nm technology node for write operation operation at  $V_{DD}=0.8$  and  $V_{DD}=0.4$  V

mainly due to the  $I_{read}$ , while other bitline is expected to dynamically remain high. However, the aggregate leakage currents on this other bitline depend on the fact that the data stored in the unaccessed bitcell may also be sunk to this bitline, and this makes the differential sensing difficult. Furthermore, if the aggregate leakage currents exceed the  $I_{read}$  than there may be an erroneous read operation. Figure 1.18 shows the worst-case bitline leakage current scenario where the data in all of the unaccessed bitcells is such that the aggregate leakage current should nominally be high, so that the droop in voltage in both the bitlines is indistinguishable.

#### 1.4.4 Partial Write Disturbance

The read Static Noise Margin (SNM) problem due to a raise in potential of the node voltage holding '0' is well understood in standard 6T SRAM bitcells. However, the stability problems also arise during a write operation to an unselected column,

**Fig. 1.18** Schematic diagram of a column with a standard 6T SRAM bitcell showing the I<sub>read</sub> and aggregate leakage currents in the worst-case scenario

when the wordline is activated while both bitlines are precharged to  $V_{DD}$ , which is a situation that produces equivalent bias conditions to a read operation. The read stability problem is eliminated by adding a read-port or providing separate read and write ports, such as, an 8T SRAM bitcell at the cost of increased area overhead. While the only true method to eliminate bitcell disturbance during such a partial write operation or partial write disturbance (PWD) is that it requires the column select functionality within the array to be disallowed. The PWD problem is explained in detail in Chap. 2.

In dual-port (1-read/1-write) SRAM bitcells, the simultaneous read and write operations and PWD further exacerbate the stability problems. Therefore, it requires modifications in the SRAM array organization. This modification is just as

Fig. 1.19 An interleaved SRAM array structure

important as the bitcell itself. Such array-level changes are necessary to achieve the full stability and scaling benefits of an 8T SRAM bitcell, such as, SNM free operation and improved WAM, and it is shown how they are tightly related to the device feature sizes.

#### 1.4.5 Soft Errors

Soft errors (or single-event-upsets) can also corrupt the data in SRAM cells due to radiation. When neutron from space or alpha particles from packaging materials penetrates a silicon wafer, they generate charge particles that perturbs the active (data storage) nodes of a memory cell causing to flip. Thus, failure rate increases with reduction in supply voltage due to reduction in stored charged on the internal data storage nodes. These soft errors can be addressed by providing the error correcting codes which requires redundant SRAM cells in each word. The error correcting codes in SRAM add latency to both write access (for encoding) and read access (for detection and correction). Redundancy goes significantly high if the number of errors corrected and detected is more than 1 bit. Therefore, multibit errors caused by soft error phenomena can be avoided by interleaving multiple words onto same physical row [100].

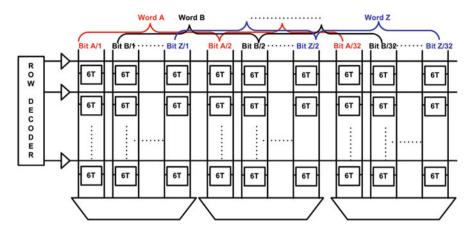

Figure 1.19 shows a conventional interleaved SRAM array structure, where each bit of Z words is laid-out contiguously in a row. To read/write a particular accessed word, the corresponding word-line is activated by the row decoder. Since all bitcells in a row share the same word-line, all the words bitcells are activated simultaneously by the word-line drivers. Accordingly, all the bit-lines for an accessed word are connected to the sense-amplifiers or write-drivers by the column multiplexors. For instance, to read an accessed word B from the first row, remaining words are also activated by the first word-line, hence, these words are referred as

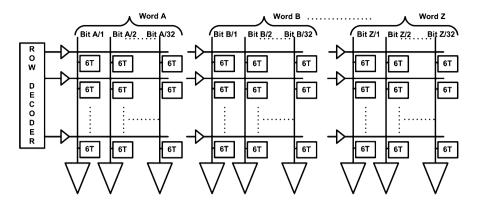

Fig. 1.20 A non-interleaved SRAM array structure for isolated read-port bitcells

half-selected words. These half-selected words are susceptible to read-destructive failure and poor read SNM conditions. The similar problems also exist during write operation in half-selected words, referred as Partial Write Disturbance (PWD). However, the use of read-buffer (isolated read-port) bitcell topologies eliminates the poor read SNM condition during the read access but PWD problem remain exist.

In particularly, half-selected or PWD poses a critical limitation to the low-voltage or energy constrained SRAM bitcell designs. Therefore, a viable alternative (non-interleaved) mainly suitable for isolated read-port bitcells, is shown in Fig. 1.20. The non-interleaved SRAM array structure requires extra hardware and more complex layouts. For example, each word has its own word-line drivers. However, it eliminates half-selection condition during both read and write operations.

# 1.5 SRAM Bitcell Topologies

Standard 6T SRAM bitcell topology as shown in Fig. 1.21 has been widely used in the implementation of cache memory in high performance microprocessors and onchip caches in SoC products. Recently, several SRAM bitcell topologies that have been proposed to achieve different objectives such as minimum bitcell area, low static and dynamic power dissipation, improved performance and better parametric yield in terms of SNM and WAM. However, other techniques such as boosting the supply voltage, read and write assist circuitries in SRAMs have also been proposed to achieve more stable data retention during read operations [53, 66]. The prime concern in SRAM bitcell design is a trade-off among these design metrics. For example, in sub-threshold SRAMs, noise margin (robustness) is the key design parameter and not speed [111,112]. Therefore, on the basis of their robustness these bitcell topologies are broadly divided into two categories: (1) non-isolated read-port SRAM bitcell topologies (less robust), and (2) isolated read-port SRAM bitcell topologies (highly robust).

Fig. 1.21 Schematic diagram of a standard six-transistor (6T) SRAM bitcell

#### 1.5.1 Non-isolated Read-Port SRAM Bitcell Topologies

This category of bitcell topologies are less robust because of their poor read SNM. Both read and write operations in these bitcells are performed via same pass-gate device(s) or in other words read and write ports are non-isolated. The main implication behind this kind of arrangement is tuning of bitcell ratio ( $\beta$ ) to achieve the non-destructive read (sufficient read SNM, atleast 10-15% of  $V_{DD}$ ) and successful write operations (enough WAM) simultaneously. As both the operations are conflicting in nature, hence, properly sized devices are highly desirable. A classical example of this category is a standard 6T SRAM bitcell, as shown in Fig. 1.21, where, both read and write operations are performed via pass gate devices,  $M_1$  and  $M_2$ . Some of the recent developments in this category are as follows:

#### 1.5.1.1 Five-Transistor (5T) SRAM Bitcell Topology

A high density low leakage five-transistor (5T) SRAM bitcell, as shown in Fig. 1.22 [20], has only one bitline and both read and write operations are performed via single pass-gate device  $M_1$ . Writing of '1' or '0' into the 5T bitcell is performed by driving the bitline to  $V_{DD}$  or  $V_{SS}$  respectively, while the wordline (WL) is asserted at  $V_{DD}$ . Sufficient WAM and read-SNM of the bitcell are ensured by cleverly sizing the transistors. This design has 15–21% smaller area for different processes, 75% lower bitline leakage, and a read/write performance comparable to standard 6T bitcell. Major drawbacks of this design are: poor static noise margins (SNM and WNM) and an on-chip DC–DC converter to generate a pre-charge voltage  $V_{PC}$  for bitline. A non-destructive read operation requires a pre-charge voltage  $V_{PC}$ , where  $V_{SS} < V_{PC} < V_{DD}$ . This is in contrast to the conventional 6T SRAM bitlines, which are precharged at  $V_{DD}$  before a read and write operation. The possible bitline pre-charge

Fig. 1.22 Schematic diagram of a high density low leakage five-transistor (5T) SRAM bitcell [20]

voltage  $V_{PC}$  levels (340–860 mV worst case). Therefore, in this work, a  $V_{PC}$  of 600 mV has been chosen as the bitline pre-charge voltage level for a 0.18  $\mu$ m CMOS Technology.

#### 1.5.1.2 Transmission Gate Based Six-Transistor (6T) SRAM Bitcell

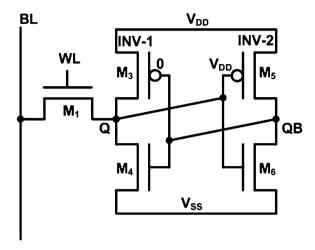

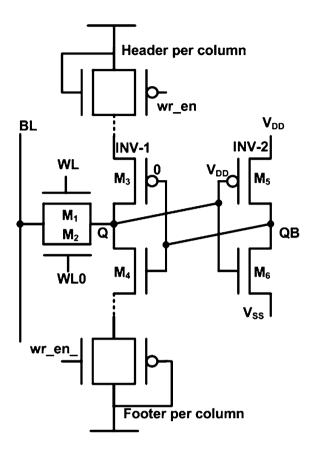

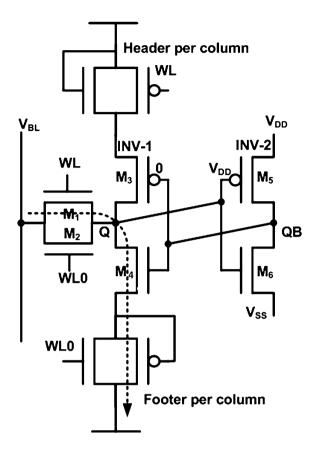

In this design [120] a transmission gate (TG) is used for accessing and transferring the data during read and write cycle via single ended bitline (data line). Employing a TG for reading from and writing into a memory bitcell is dangerous because it conducts perfectly for '0' and '1' in both the directions. In other words, a read cycle can easily flip the bitcell content, because of direct and strong intervention of readcurrent to data storage node O, as shown Fig. 1.23. Hence, the use of TG drastically reduces the read SNM, to even worse than the standard 6T SRAM bitcell for an isoarea topology. In TG 6T bitcell, all the devices have to be sized too large to achieve adequate read SNM, making the bitcell size more than twice the standard 6T bitcell, thus defeating the benefits of technology scaling. The write-ability of the bitcell is ensured by sharing a header and footer per column. However, sharing a header and footer per column will affect the stability of the other (non-accessed) bitcells connected to the same bitline during the write cycle. Because at the onset of a writecycle (when signal wr\_en\_ is activated), the footer will slow down the re-generative action of all the bitcells (or cross-coupled inverters) those sharing the same column for improving the write-ability of an accessed bitcell. The measurement results from a 2 Kb SRAM test-chip fabricated in 0.13 µm bulk CMOS show a 64% energy saving as compared to a multiplexor (MUX) based memory [111]. While this bitcell topology occupies more than 42% of area overhead as compared to standard 6T bitcell that fails to operate below 720 mV but it manages to operate at sub-200 mV  $V_{DD}$ . Another major drawback with this design is that the increased leakage current from the bitline (BL) limits the number of bitcells per bitline to 16.

Fig. 1.23 Schematic diagram of a transmission gate based access six-transistor (TG 6T) SRAM bitcell topology [120]

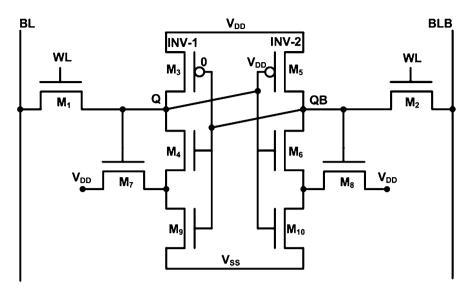

#### 1.5.1.3 Ten-Transistor (10T) Schmitt Trigger SRAM Bitcell

Schmitt Trigger (ST) based 10-transistor SRAM bitcell topology, as shown in Fig. 1.24 [63] focuses on making the inverter pair – a basic unit of the bitcell – robust. Inverter characteristics were improved by using a modified Schmitt trigger configuration. This modified configuration is used to form the inverter pair of the bitcell. It increases or decreases the switching threshold voltage of an inverter depending on the direction of the input transition, hence, providing an enhanced ideal inverter characteristic, which effectively augments the read and hold SNMs. As a result, better read stability and write-ability in the 10T ST bitcell for subthreshold operation that comes with almost double the area overhead, as compare to standard 6T bitcell. Read and hold SNM of this design are  $1.56 \times$  and  $2.3 \times$  better than the standard 6T SRAM bitcell at  $V_{DD} = 0.4 \, \text{V}$ , respectively. More power saving in this design at lower  $V_{DD}$ , approximately 18% and 50% saving in leakage and dynamic power, respectively. These results are based on 130 nm process.

24 1 Introduction to SRAM

Fig. 1.24 Schematic diagram of a Schmitt Trigger based ten-transistor (10T) SRAM bitcell topology [63]

## 1.5.2 Isolated Read-Port SRAM Bitcell Topologies

The isolated read-port SRAM bitcell topologies also known as read-SNM free SRAM bitcell topologies have recently attracted lot of attention [18, 23–25, 73, 101, 103, 108, 111], specifically for lower supply voltage  $V_{DD}$  or sub-threshold operation. Reduction in supply voltage  $V_{DD}$  drastically reduces the SRAM bitcell noise margins and increases susceptibility to process variation. Therefore, researchers believe that it is necessary to move from standard six-transistor (6T) to eighttransistor (8T) or ten-transistor (10T) register file (1-read/1-write) type of bitcells topologies, to cope with poor noise margins or process variability problems when chips operate at lower voltages. Increasing the number of transistors to provide a separate read-port will yield extra silicon overhead and inability of scaling the SRAM bitcell for future generations. In read-SNM-free SRAM bitcells, both read and write operations are performed via separate pass-gate devices, while in the standard 6T bitcell the same pass-gate devices are used for both read and write operations. Hence, optimization of the devices size in read-SNM free SRAM bitcells is easier for a target performance and stability parameters. Mostly cited SRAM bitcell topologies base on isolated read-port are as follows.

#### 1.5.2.1 Eight-Transistor (8T) SRAM Bitcell Topology

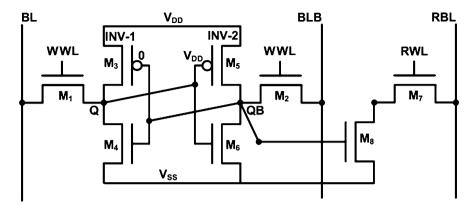

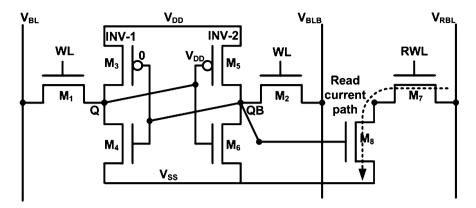

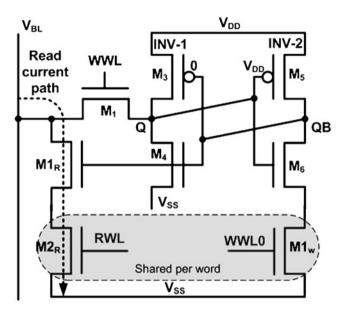

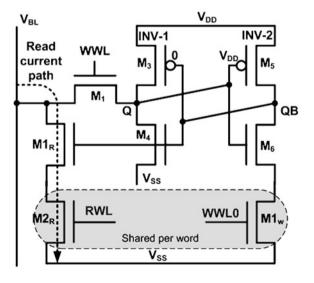

Figure 1.25 shows the read SNM free 8T bitcell [23, 25, 101, 103, 108], a register file type of SRAM bitcell topology, which has separate read and write ports.

Fig. 1.25 Schematic diagram of an isolated read-port (or read SNM free) eight-transistor (8T) SRAM bitcell topology [23]

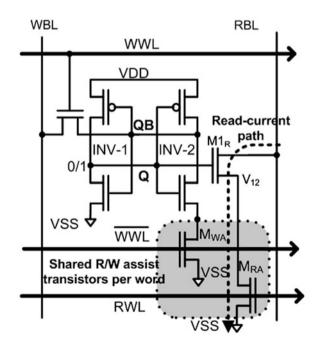

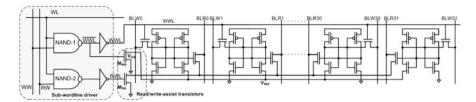

These separate read and write ports are controlled by separate read (RWL) and write (WWL) wordlines and used for accessing the bitcell during read and write cycles, respectively. In 8T bitcell topology, read and write operations of a standard 6T SRAM bitcell shown in Fig. 1.21 are de-coupled by creating an isolated readport or read buffer (comprised of two transistors, M<sub>7</sub> and M<sub>8</sub>). De-coupling of read and write operations yields a non-destructive read operation or SNM-free read stability. The interdependence between stability and read-current is overcome, while dependence between density and read-current remains there. An additional leakage current path is introduced by the separate read-port which increases the leakage current as compared to standard 6T bitcell. Therefore, an increased area overhead and leakage power make this design rather unattractive, since leakage power is a critical SRAM design metric, particularly for highly energy constrained applications.

The read bitline leakage current problem in the 8T bitcell is similar to the problem in the standard 6T bitcell, except that the leakage currents from the unaccessed bitcells and from the accessed bitcell affect the same node, RBL. So, the leakage currents can pull down RBL regardless of the accessed bitcells state. In [108] the bitline leakage current from the un-accessed bitcells is managed by adding a buffer-footer, shared by the all bitcells in that word.

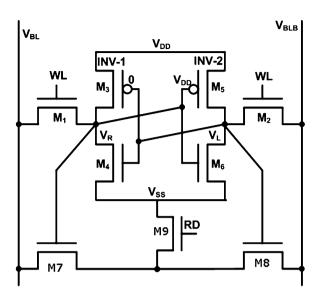

#### 1.5.2.2 Nine-Transistor (9T) SRAM Bitcell Topology

Standard 6T bitcell along with three extra transistors were employed in nine-transistor (9T) SRAM bitcell [73], to bypass read-current from the data storage nodes, as shown in Fig. 1.26. This arrangement yields a non-destructive read operation or SNM-free read stability. Results based on 65 nm process reveals that the read SNM is approximately 2× better than the standard 6T SRAM bitcell.

26 1 Introduction to SRAM

Fig. 1.26 Schematic diagram of an isolated read-port nine-transistor (9T) SRAM bitcell topology [73]

It also claims the leakage power saving of about 23% better than the standard 6T SRAM cell. However, it leads to 38% extra area overhead and a complex layout. Thin cell layout structure does not fit in this design and introduces jogs in the poly.

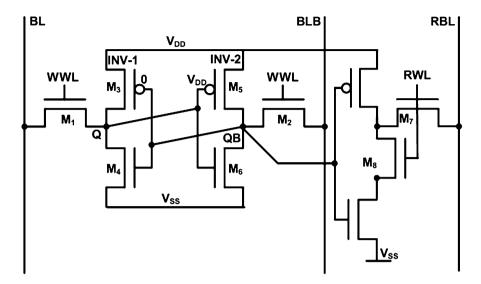

#### 1.5.2.3 Ten-Transistor (10T) SRAM Bitcell Topology

In the 10T bitcell as shown in Fig. 1.27 [18], a separate read-port comprised of 4-transistors was used, while write access mechanism and basic data storage unit are similar to standard 6T bitcell. This bitcell also offers the same benefits as the 8T bitcell, such as a non-destructive read operation and ability to operate at ultra low voltages. But the 8T bitcell does not addresses the problem of read bitline leakage current, which degrades the ability to read data correctly. In particularly, the problem with the isolated read-port 8T cell is analogous to that with the standard (non-isolated read-port) 6T bitcell discussed. The only difference here is that the leakage currents from the un-accessed bitcells sharing the same read bit-line, RBL, affect the same node as the read-current from the accessed bitcell. As a result, the aggregated leakage current, which depends on the data stored in all of the unaccessed bitcells, can pull-down RBL even if the accessed bitcell based on its stored value should not do so. This problem is referred as an erroneous read. This design has good performance at lower  $V_{DD}$ . For example, at 400 mV it can operate at 475 kHz with small power consumption of 3.28 uW. It also has good reliability, that is, it can operate without read error at 27°C and 320 mV, while it can have 256 bitcells per bitline.

The erroneous read problem caused by the bitline leakage current from the unaccessed bitcells is managed by this 10T bitcell by providing two extra transistors

Fig. 1.27 Ultra-low voltage subthreshold ten-transistor (10T) SRAM bitcell topology [18]

in the read-port. These additional transistors help to cut-off the leakage current path from RBL when RWL is low and makes it independent of the data storage nodes content. In [58] the Reverse Short Channel Effect (RSCE) in subthreshold region was utilized to improve the write-ability and data-dependent bitline leakage current. The RSCE reduces the  $V_{TH}$  and exponentially increases the device current. Therefore, in this design, access devices utilize the RSCE to increase the write-ability. However, the RSCE would not be effective and may lead to a poor read-stability if the same access devices are used for read operation.

However, this list is not complete and there are several other potential bitcell topologies exist in the literature some of them are from [4, 44, 84, 103, 113]. In non-isolated read-port bitcell designs a non-destructive read or a successful write operation is ensured by either increasing the bitcell size or an additional circuitry or both. However, isolated read-port SRAM bitcell topologies also lead to extra area overhead but yield higher read SNM and supply voltage scaling for low power applications. Hence, a bitcell topology that yields the benefit of higher read SNM and supply voltage scaling for subthreshold operation with minimum area overhead is highly desirable.

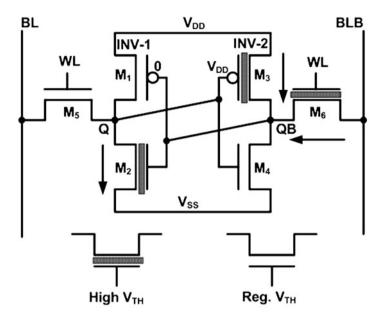

# 1.5.3 Low-Leakage Asymmetric SRAM Bitcell

Standard 6T SRAM bitcell use a symmetric configuration of six transistors with identical leakage and threshold voltage ( $V_{TH}$ ) characteristics. Reduction in leakage can be achieved by using higher  $V_{TH}$  transistors, however, employing all the high

28 1 Introduction to SRAM

Fig. 1.28 Basic asymmetric six-transistor (6T) SRAM bitcell for low-leakage current when holding a '0'. High  $V_{TH}$  transistors are employed where leakage dissipation is higher

$V_{TH}$  transistors will degrade the bitcell performance significantly and even up to an unacceptable level. Dual- $V_{TH}$  technology leads to a difference of approximately  $10\times$  between the leakage current of high  $V_{TH}$  and regular  $V_{TH}$  transistors. The use of dual- $V_{TH}$  technology introduces asymmetry in the SRAM bitcell design because of different threshold transistors are employed. Therefore, SRAM bitcells in which leakage is reduced by employing dual- $V_{TH}$  technology are called low-leakage asymmetric SRAM bitcells. Leakage current can also be reduced by increasing the length of a transistor, but it increases the area of the transistor at least 100-fold. Therefore, dual- $V_{TH}$  technology based SRAM bitcells have good potential of saving leakage power. These bitcells exhibit asymmetric leakage and access behaviour [5, 8].

In low-leakage asymmetric SRAM bitcells, selected transistors are "weakened", or in other words  $V_{TH}$  of selected transistors is raised to reduce the leakage current, however, it can also be achieved by appropriate sizing of the transistors when the bitcell is storing a zero. In order to identify the leaky transistors, most of the bits in caches are zeros for both instruction and data streams fact is exploited. It has been shown that this behaviour persists for a variety of programs under different assumptions about the cache sizes, organization and instruction set architecture [86]. Therefore, "0" storing state is considered and weaken the only transistors necessary to drastically reduce the leakage current. In general bitcell spend most of time in the inactive state. In this state, most of the leakage is dissipated by the transistors that are in off state and that have a voltage difference across their drain and source terminals. When the bitcell storing a "0", as shown in Fig. 1.28, the leaky transistors

1.6 Summary 29

are  $M_2$ ,  $M_3$  and  $M_6$ , therefore, these transistors are made of high threshold voltage. Similarly, if the bitcell was storing a "1", then transistors  $M_1$ ,  $M_4$  and  $M_5$  would dissipate leakage power.

In this asymmetric bitcell, as shown in Fig. 1.28, read access time is degraded due to  $M_2$ 's and  $M_6$ 's higher threshold voltage which causes bitline discharge time longer. The HSPICE simulated results of this asymmetric SRAM bitcell based on 130 nm process exhibit the same leakage as the regular threshold voltage bitcell when holding a logic "1", when it holding a logic "0" leakage current is reduced by  $70\times$ . Therefore, there are many possible combinations to form a asymmetric SRAM bitcell keeping other parameters in mind such as saving in leakage power, stability and performance.

#### 1.6 Summary

The importance of Static Random Access Memory (SRAM) in different processors and system-on-chip (SoC) products has fuelled the need of innovation in this area. The impact of CMOS technology scaling reduces the stability and noise margins of conventional SRAM design, as a result, alternate SRAM designs need to explore for the future technology generations. Study of different SRAM bitcells showed that the isolated read-port SRAM bitcells have better read stability and process variation tolerance as compared to non-isolated read-port SRAM bitcells. However, complex layout and extra silicon area overhead are the major limiting factor in the isolated read-port SRAM bitcells. Apart from SRAM bitcell topologies, SRAM array architectures are equally responsible for overall performance and reliability of a cache module. It is showed that the non-interleaved array architecture is more favourable for the isolated read-port SRAM bitcells and it helps in sharing the peripheral circuitries as well as minimizes the partial write disturbance.

# **Chapter 2 Design Metrics of SRAM Bitcell**

#### 2.1 Standard 6T SRAM Bitcell: An Overview

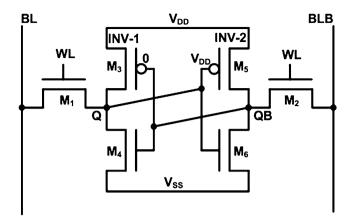

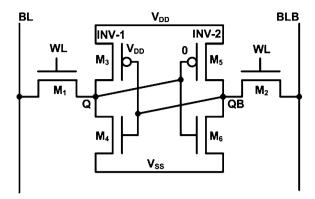

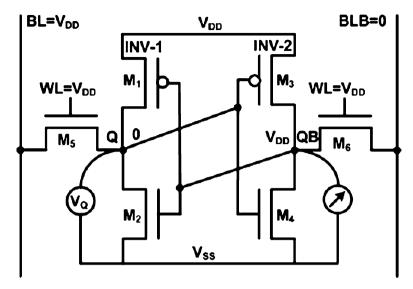

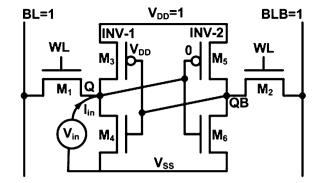

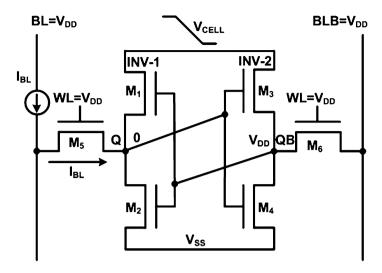

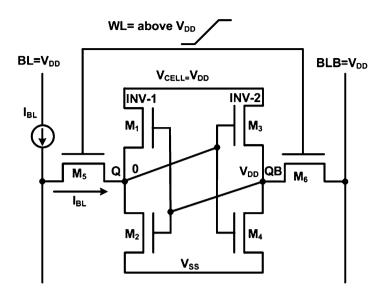

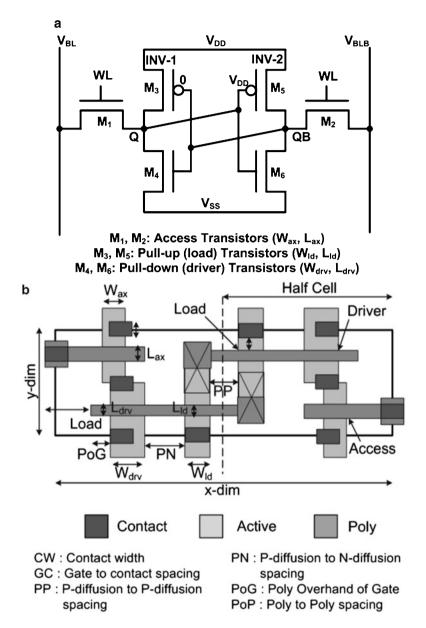

This section gives a brief overview of the standard six-transistor (6T) SRAM bitcell and its operation. A standard 6T SRAM bitcell consists of two identical CMOS inverters (INV-1 and INV-2) connected in a positive feedback loop. It forms a basic unit, that is, a flip-flop or latch to create a bi-stable circuit allowing the storage of one-bit of information, either '1' or '0'. The internal nodes (Q and QB) of the bitcell always contain complementary values, as shown in Fig. 2.1. The crosscoupled inverter pair itself consists of two PMOS pull-up devices (M<sub>3</sub> and M<sub>5</sub>) and two NMOS pull-down devices (M<sub>4</sub> and M<sub>6</sub>). Two NMOS pass-gate or access devices  $(M_1 \text{ and } M_2)$ , which are controlled by the wordline (WL), serve as switches between the inverter pair and the complementary pair of bitlines (BL, BLB) also called datalines, used to read in or write to the bitcell, as shown in Fig. 2.1. The data in SRAM bitcell is stored as long as the power is maintained to the bitcell. The cross coupled inverter pair can be in one of the two stable states of an SRAM bitcell, which corresponds to the data stored '1' and '0', as shown in Fig. 2.2a, b, respectively. The basic operations of a bitcell as a storage device are reading or writing new data to the bitcell.

The read and write operations in a standard 6T SRAM bitcell are performed in the following ways.

# 2.1.1 Read Operation

Without loss of generality, it is assumed that the internal data storage nodes Q and QB are at '0' and '1', respectively, which correspond to Fig. 2.2b. To read the bitcell contents, the following sequence of steps are performed:

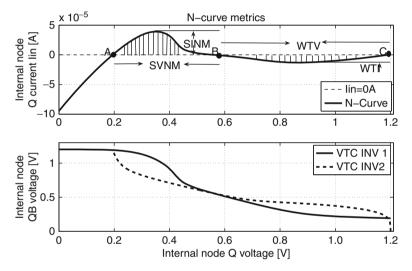

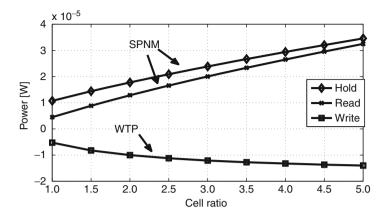

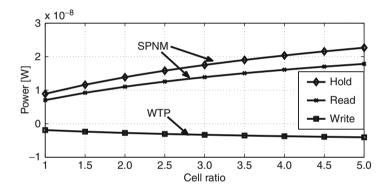

Fig. 2.1 Schematic diagram of a standard 6T SRAM bitcell. Internal data storage node Q at '0' and QB at '1'

Fig. 2.2 Standard 6T SRAM bitcell under different stable states. (a) SRAM bitcell '1' stored. (b) SRAM bitcell '0' stored

- Conventionally to read a bitcell, the bitlines (BL and BLB) are precharged to the supply voltage (V<sub>DD</sub>). In some SRAM designs these bitlines are precharged to intermediate level of 0 and V<sub>DD</sub>.

- The wordline (WL) is asserted to high.

- Rise the WL from '0' to '1', result, one of the bitcell sides (node) stores the logical '0'; that side of the bitline is discharged through the pass-gate and pull-down transistors. In standard 6T, as shown in Fig. 2.1, devices M<sub>1</sub> and M<sub>4</sub> discharges the precharged bitlines BL.

- If BLB goes to low (or discharges), then the bitcell holds a logic '1' value, which correspond to Fig. 2.2a.

- If BL goes to low (or discharges), then the bitcell holds a logic '0' value, which correspond to Fig. 2.2b.

- Depending upon whether the bitline BL or BLB is discharged, the bitcell is read as a logical '1' or '0'. A sense amplifier converts the differential signal exists on BL and BLB to a logic-level output.

- De-assert the wordline (WL) back to 0.

During a read operation, the internal node (say Q) of the bitcell that holds a logical '0' will pull its bitline (BL) low through the pass-gate transistor,  $M_1$  and pull-down transistor,  $M_4$ . It is important that the low internal node (Q) should not rise above the trip-point (switching threshold voltage) of the inverter INV-2, as shown in Fig. 2.1, to avoid a destructive read operation. A destructive read operation can be prevented by ensuring a large enough bitcell ratio  $(\beta)$ , in other words, pull-down transistors ( $M_4$  and  $M_6$ ) must be stronger than the access transistors ( $M_1$  and  $M_2$ ). For a symmetric bitcell, bitcell ratio  $(\beta)$  is defined as:

$$\beta = \frac{W_4/L_4}{W_1/L_1} = \frac{W_6/L_6}{W_2/L_2} \tag{2.1}$$

In general, the bitcell ratio can be varied from 1.25 to 2.5 depending on the target application and desired static noise margin (SNM). A larger bitcell ratio makes the bitcell robust and provides higher SNM and read current  $I_{read}$  (and hence – the speed), at the expense of increased silicon overhead and leakage current. A smaller bitcell ratio, whilst maintaining an adequate speed and noise margin, makes the bitcell compact for a high density cache design but more vulnerable to process variation induced failures.

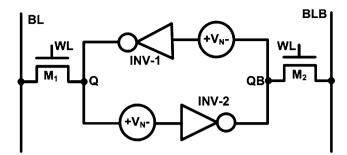

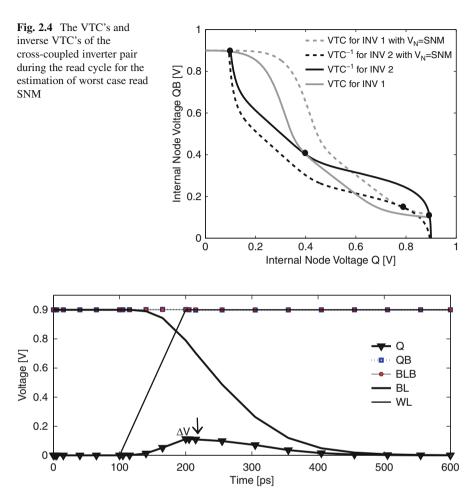

#### 2.1.2 Read SNM Measurement

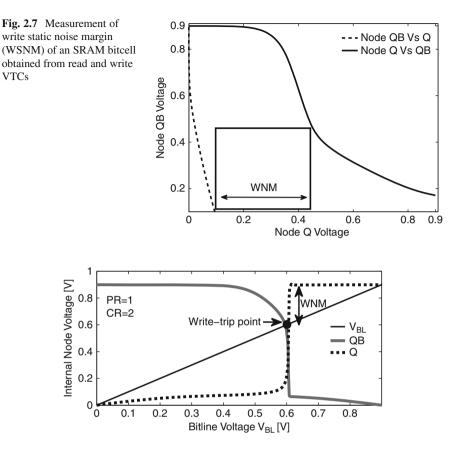

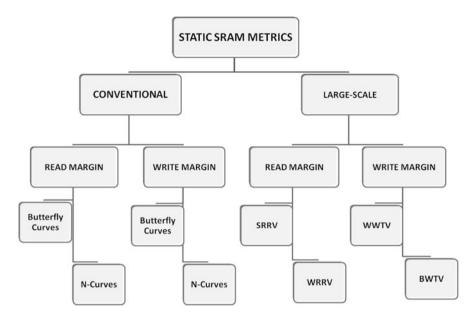

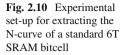

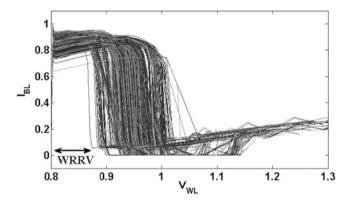

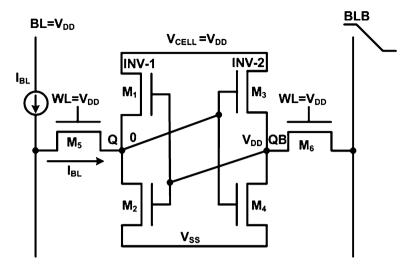

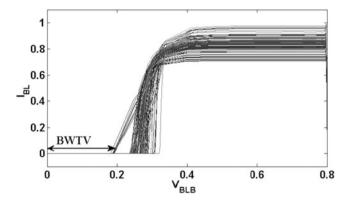

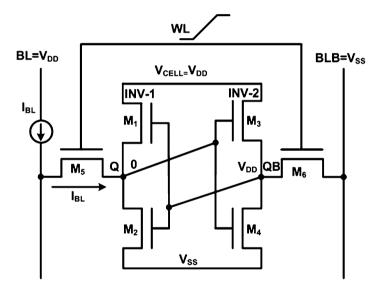

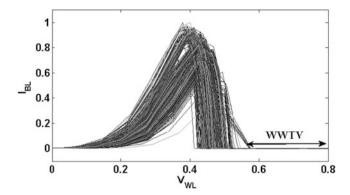

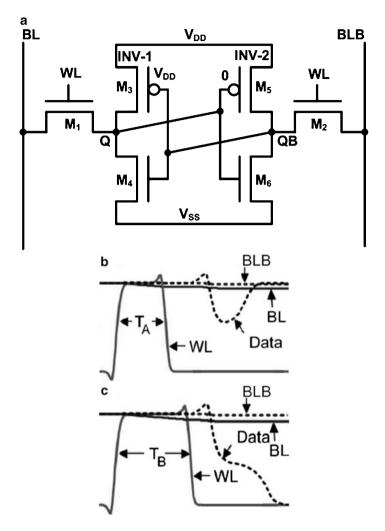

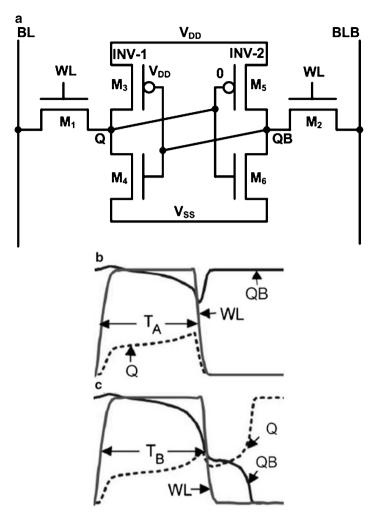

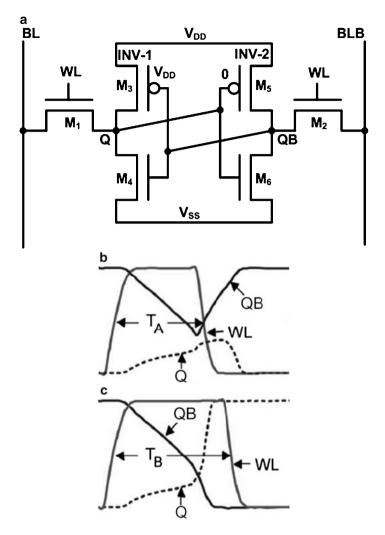

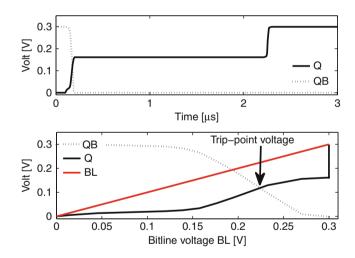

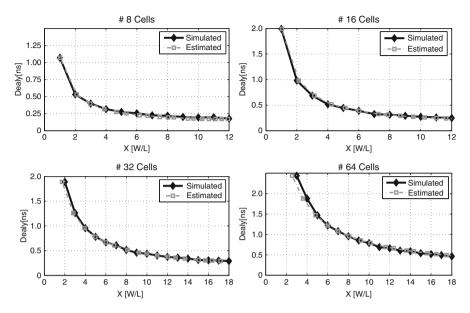

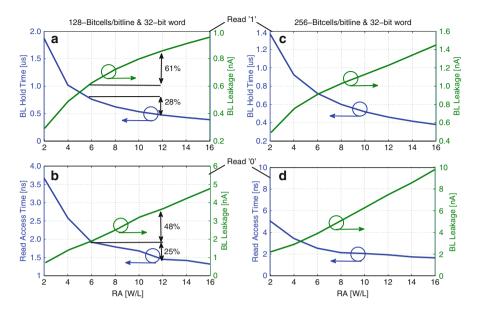

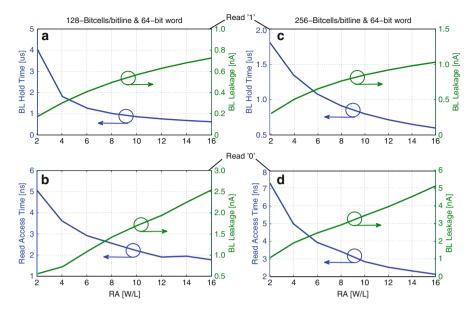

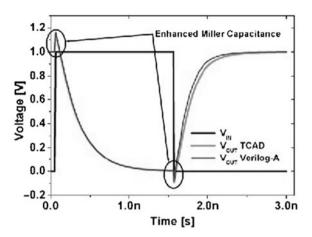

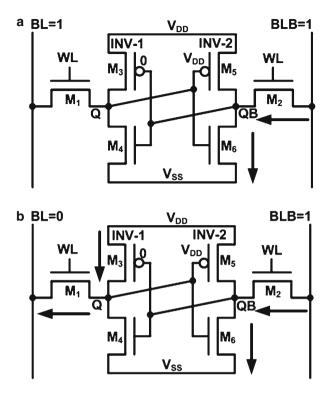

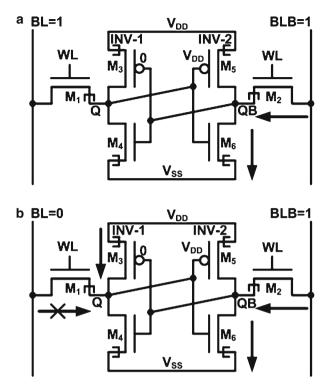

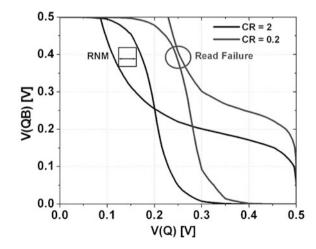

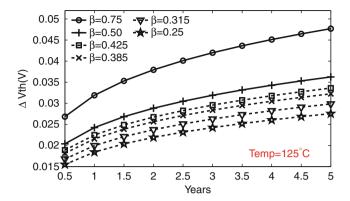

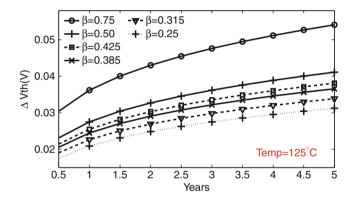

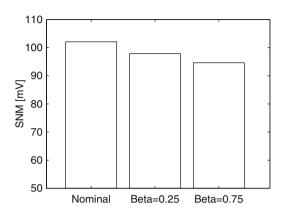

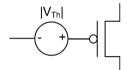

The best measure to quantify the stability of an SRAM bitcell during the read cycle and in hold state is the Static Noise Margin (SNM). The SNM is defined as the maximum amount of DC noise ( $V_N$ ) that can be tolerated by the cross-coupled inverter pair such that the bitcell retains its data [94]. The read SNM is extracted from the read voltage transfer characteristics (VTC). The read VTC can be measured by sweeping the voltage at the data storage node Q (or QB) with both bitlines (BL, BLB) and wordline (WL) biased at  $V_{DD}$  while monitoring the node voltage at QB (or Q).