### The RTL-Level SDC Timing Exception Verification Ecosystem

ChienLin Huang, MediaTek Evan Yang, Synopsys

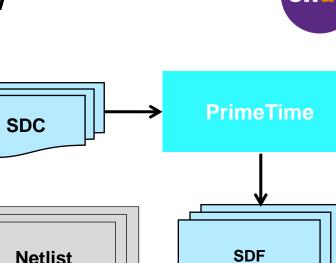

### **Traditional Gate Level Simulation Flow**

- Many chip makers do gate level simulations (GLS) in addition to RTL simulations, static and formal verification

- Designers rely on GLS to catch chip-killing bugs that other tools like static timing analysis (STA), assertion-based verification (ABV), static verification and emulation can't catch

- GLS netlist debug is cumbersome

- Becomes active only in the very late stages of the design process when the netlist and standard delay format (SDF) files are available

2

VCS

### **Existing SDC Verification Approaches**

Need a fast and comprehensive solution that can verify SDC intent early in the design cycle

- Gate-level simulations with full timing (SDF)

- Late in the development cycle (too close to tape-out)

- Huge, slow and high debug effort

- Often run only a test subset leading to low coverage

### Formal/Static methods

- Great when they work testbench-less & exhaustive

- Typically exhibit capacity limitations and may require a complete environment (i.e., firmware?)

- May lead to inconclusive results (or require inordinate amount of time)

- QoR issues with noise

### • Proprietary RTL coding schemes (macros, assertions, …) for simulation

- Ad-hoc, non-standard and difficult to implement (instrumentation point)

- May degrade performance

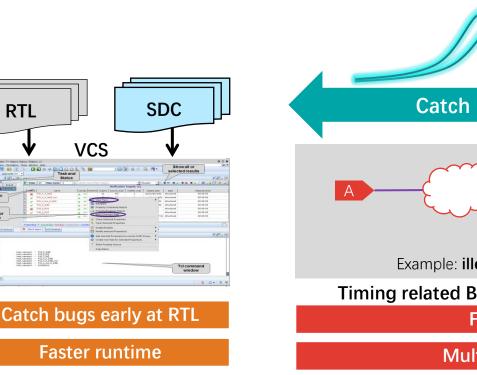

### SDC Aware Verification in VCS

**VCS-SDC** feature

RTL

Tron, cerunal Coon, related Coon, related

Simulation

RTL

High coverage

Leverage Verdi debug

Verify SDC at RTL stage -> increase 10X test coverage -> change simulation time from week to days

sn

4

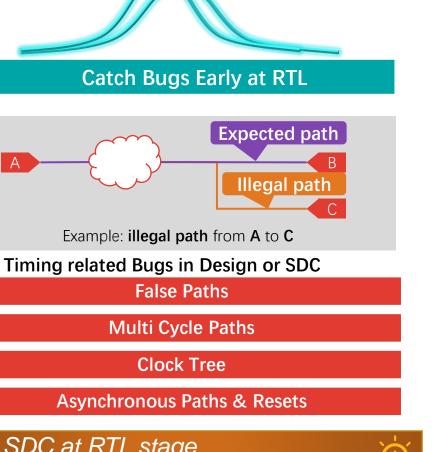

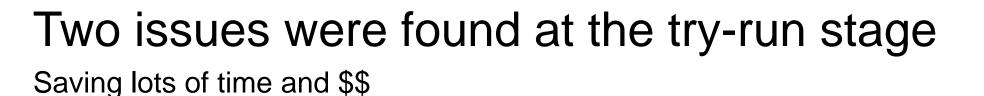

Case1: CDC Reconvergence

• Case2: False path Reconvergence

VCS-SDC can insert different delays on different paths to trigger the design issue to make simulation failed.

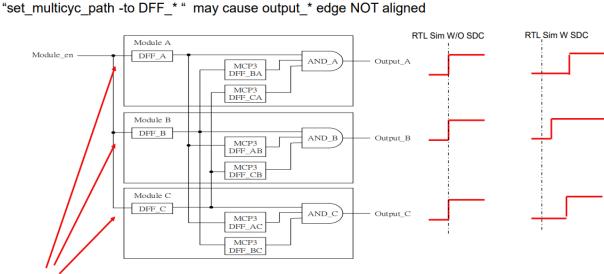

"set false path -to FP DFF\*" causes different delays and make FSM hanging

VCS-SDC can insert different delays on different paths to trigger the design issue to make simulation failed.

### Debug Fail pattern

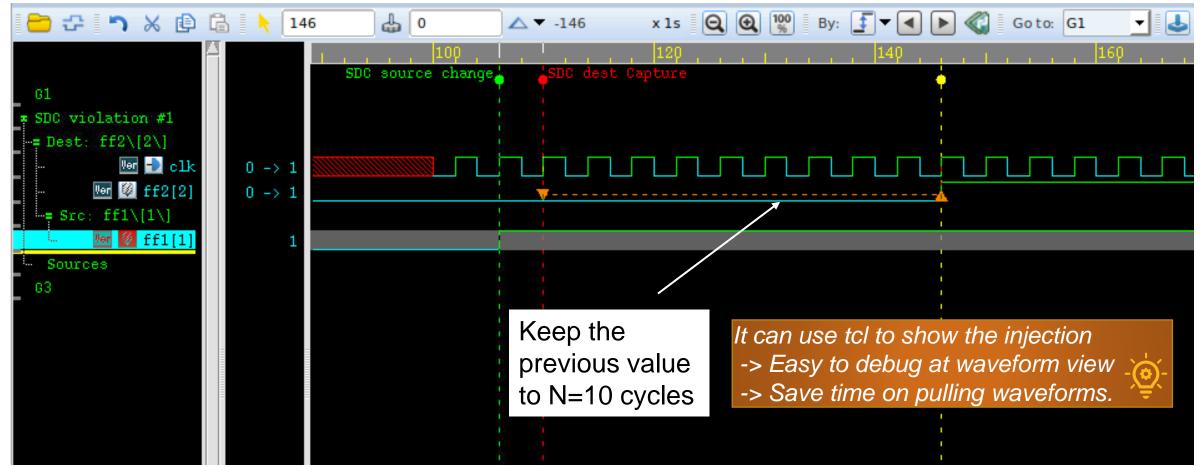

Verdi inject marker and DUTRCA feature: Inject marker

• set\_multicycle\_path 10 – from ff1\* -to ff2\*

6

sn

## Debug Fail pattern

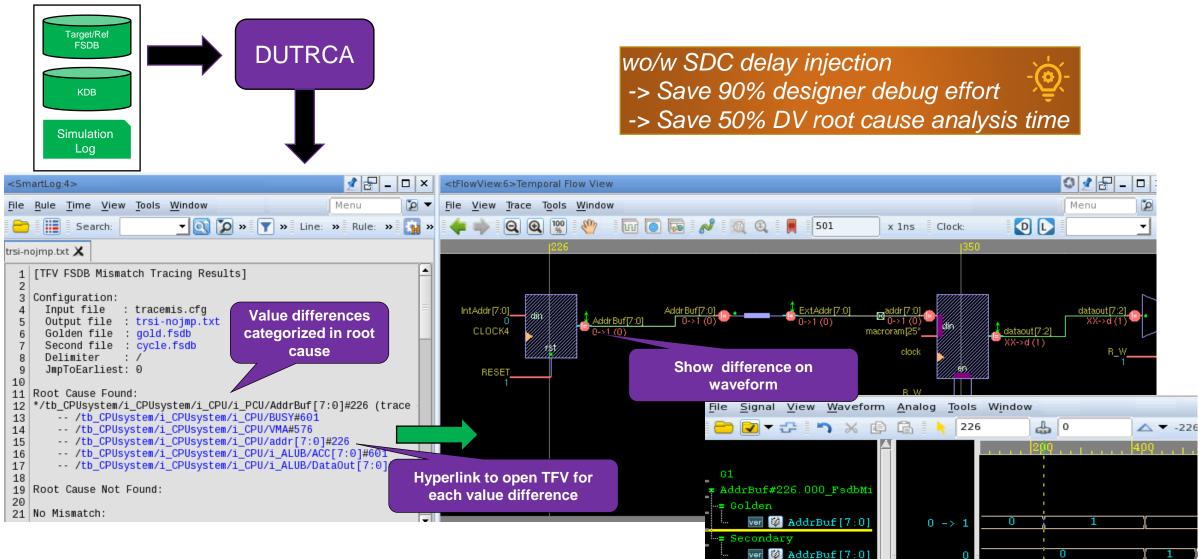

Verdi inject marker and DUTRCA feature: DUTRCA

Sil

#### **Review the VCS-SDC simulation log** SNU MCPRCA feature: Bins view **RTL code in nTrace** 2 2 1 · BB · • DC OOL 3 SDC **Further** Design Command Debug RTL **RDA MCPRCA** VCS Verdi GUI (Violation Binning) (with SDC) Logs in SmartLog Violation Simulation Report Log Violations Waveform in nWave 💽 🕞 🗣 Recommend Debug Index: 1 Violation Time: 230 Q Q 👻 97 [ • 4 🗈 🗳 6010 61 🔹 🛓 Type Specifier: [MCP] Signal(TO): testbench.mult.ff2[1] Clock: testbench.mult.clk (testcase/test.sdc:2) Signal(FROM): testbench.mult.ff1 Clock: testbench.mult.clk (testcase/test.sdc:2) Group and analyze sdc simulation log Observed Delay Cycle: 1 -> Saved 90% of the time spent on SDC error classification Expected Delay Cycle: 10 SDC Command Type: set multicycle path (testcase/test.sdc:3) 8

## Review the VCS-SDC simulation log

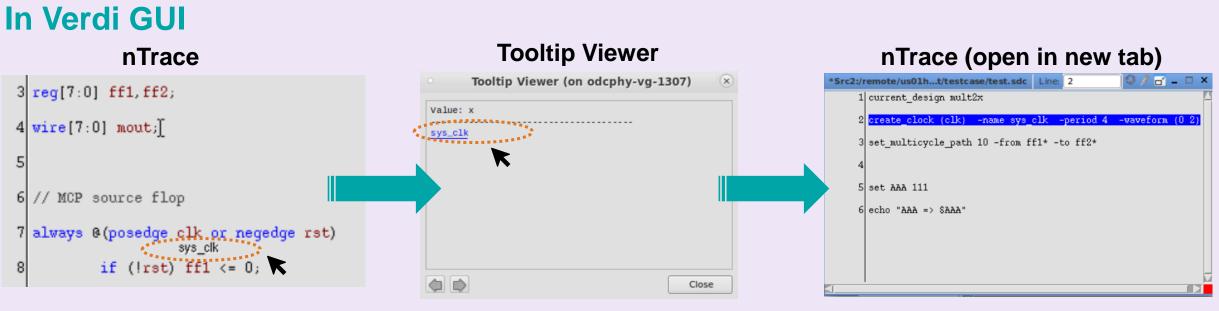

MCPRCA feature: SDC annotation in nTrace

1. Press "shift" to open tool tip viewer

- 2. Click hyperlink to show SDC in Tooltip

- 3. The sdc command is shown in nTrace

All SDC information can be annotated -> Very helpful for debugging -> Easy to trace the clock

## Review the VCS-SDC coverage

URG Coverage feature

- MCP Command:

- Set\_multicycle\_path from ff2\* to ff5\*

- Totally, there are four MCP paths covered by the MCP command

- 4-level signoff criterion (From coarse to fine)

| Hierarchy Modules Groups Asserts SDC Statistics Tests |                                                             |      |      |           |        |       |        |          |           |

|-------------------------------------------------------|-------------------------------------------------------------|------|------|-----------|--------|-------|--------|----------|-----------|

| *                                                     |                                                             |      |      |           |        |       |        |          |           |

| Name                                                  | Δ                                                           | Line | Туре | Status    | Score  | Total | Active | Inactive | Violating |

| ÷                                                     | ./Source/urg_SDC/mult_des_cov.sdc                           |      |      |           | 0.00%  | 6 4   | C      | 0 0      | 4         |

|                                                       | MCP (./Source/urg_SDC/mult_des_cov.sdc:4) -from ff1 -to ff2 | 4    | MCP  | VIOLATING | 12.50% | 8     | ]      | 6        | 1         |

|                                                       | MCP (./Source/urg_SDC/mult_des_cov.sdc:5) -from ff1to ff2   | 5    | MCP  | VIOLATING | 12.50% | 8     | 1      | 6        | i 1       |

|                                                       | MCP (./Source/urg_SDC/mult_des_cov.sdc:10) -from b1 -to b3  | 10   | MCP  | VIOLATING | 50.00% | 5 12  | 6      | i 4      | 2         |

| I                                                     | MCP (./Source/urg_SDC/mult_des_cov.sdc:11) -from b2 -to b3  | 11   | MCP  | VIOLATING | 41.67% | 5 12  | 5      | i 4      | 3         |

Four coverage model levels available -> Reuse urg coverage system -> An indicator of SDC verification level

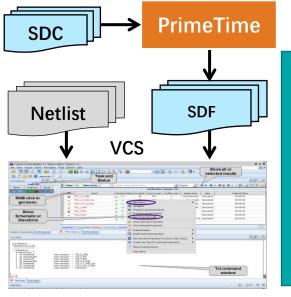

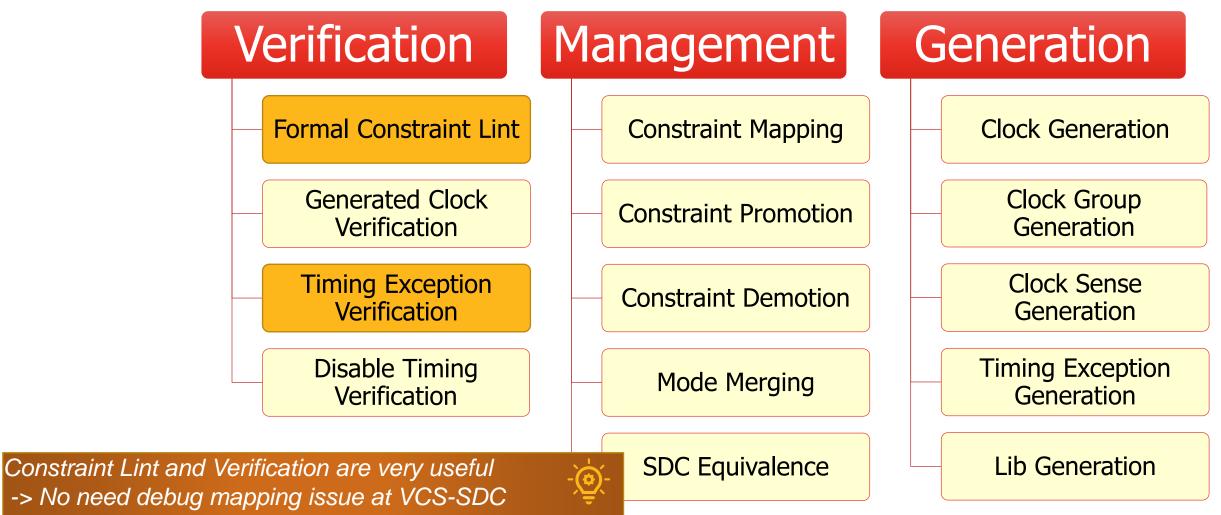

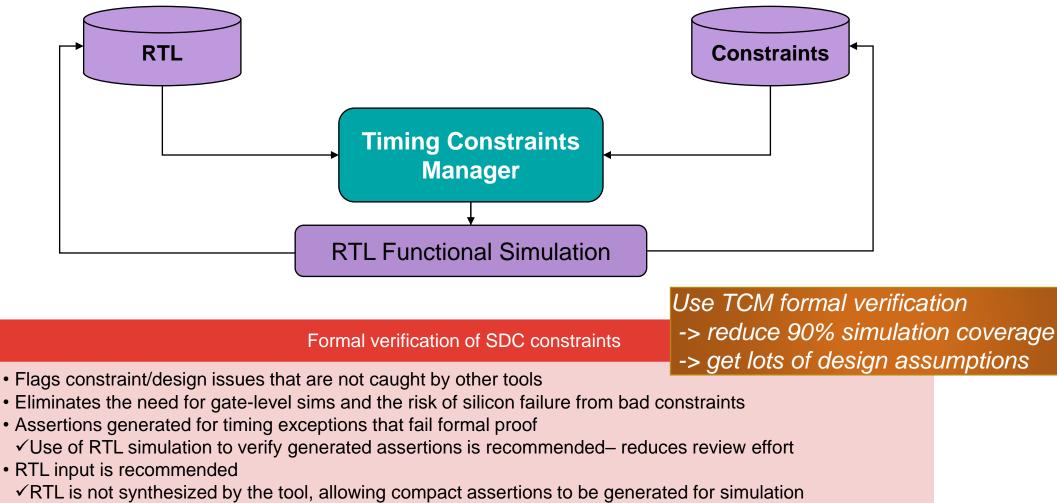

**Timing Constraints Management System**

TCM SDC verification feature

-> VCS-SDC becomes a means for TCM SDC verification

snuc

## Timing Constraints Management System

**TCM SDC Verification Feature**

Refocus maps gate-level signoff constraints to RTL

sn

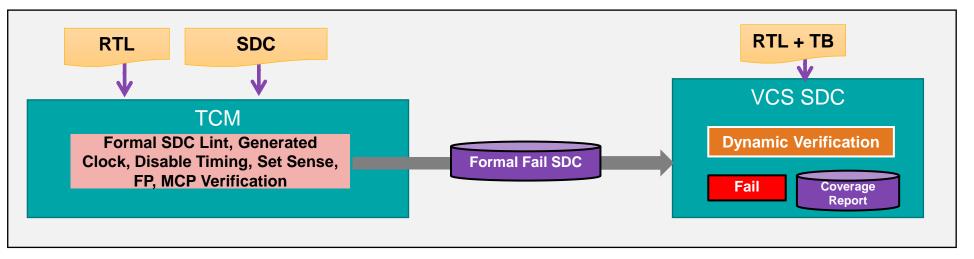

### TCM + VCS-SDC

= Timing Exception Verification Ecosystem

An early stage of SDC verification 'Solution' 'Solution' 'Solution' 'Solution' 'Solution' 'Solution' 'Solution' -> Caught design/SDC bugs at the RTL stage -> Save 90% DE and DV effort

Best in Class Technology for Formal + Simulation Based Verification of SDC constraints

- Complete formal verification of all SDC constraints using TCM

- Timing-exceptions that fail formal proof are provided as input to VCS SDC

- ✓ Large majority of timing exceptions are proven formally with minimal user intervention

- ✓Knowledge of static nets on a design is key to high formal pass percentage

- Fast, dynamic path sensitization-based, verification of formal failures in RTL simulation

- ✓ Native SDC support in simulation is more powerful and easier to manage than assertions

- ✓ Ease of debug and MCP/FP specific coverage

### Conclusions

- VCS-SDC is a VCS feature that can model post-simulation behavior, allowing users to use more patterns at the RTL stage to increase confidence in SDC verification.

- DUTRCA and MCPRCA, as part of the VCS-SDC toolchain, can significantly reduce the effort required to debug failures caused by VCS-SDC injected delays.

- The URG-based SDC coverage system provides a familiar coverage interface, enabling users to review and waive, as well as choose different levels of coverage models to control the amount of coverage.

- The TCM SDC Lint feature can greatly reduce the effort needed to debug SDC mapping in VCS-SDC, and also saves DV engineers from spending time learning SDC syntax-related knowledge.

- The TCM SDC verification feature can effectively increase the coverage rate and efficiently reduce the pattern count required by VCS-SDC.

- Through the combination of TCM and VCS-SDC features, Synopsys provides a very powerful means of SDC verification at the RTL stage, allowing us to significantly reduce the risk of SDC bugs within limited time and manpower.

# THANK YOU

Our Technology, Your Innovation<sup>™</sup>