# Accelerated Serial DFT SOC Scan Validation using ZeBu Emulator

Ashish Tiwari Chokkam Bharath Shivasharanapp Biradar Rakesh Singh (Synopsys)

Samsung Semiconductor India Research Bangalore, Karnataka, India

## AGENDA

- Problem Statement

- Proposed work and methodology

- Results

- Scope for Improvement

- Conclusion

### **Problem Statement**

- SOC Scan Serial simulation for all the patterns can not be done due to the huge simulation run times and huge compute resources requirement.

- The full set Scan Serial simulation can be performed using the Zebu emulator.

- The SOCs of size 69M and 60M gates have been verified on zebu within hours.

# Case study

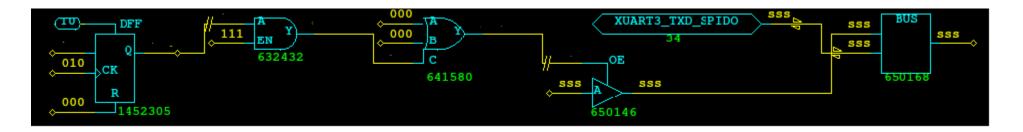

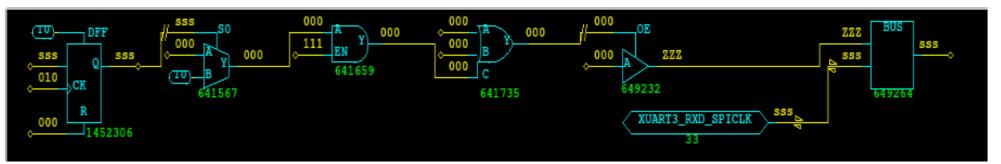

We have run the playback simulations for TD 200 patterns. After Post silicon it was failing on 232 pattern

OE controllability issue on SCAN IN pad

#### PASS Case:

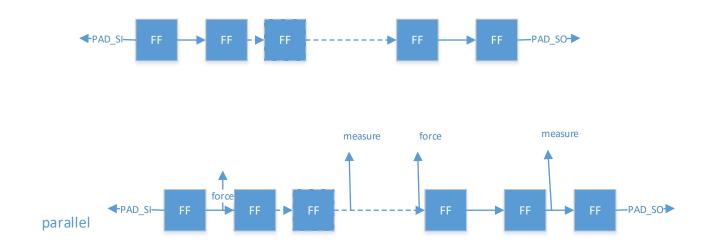

## Proposed work and methodology

SAMSUNG

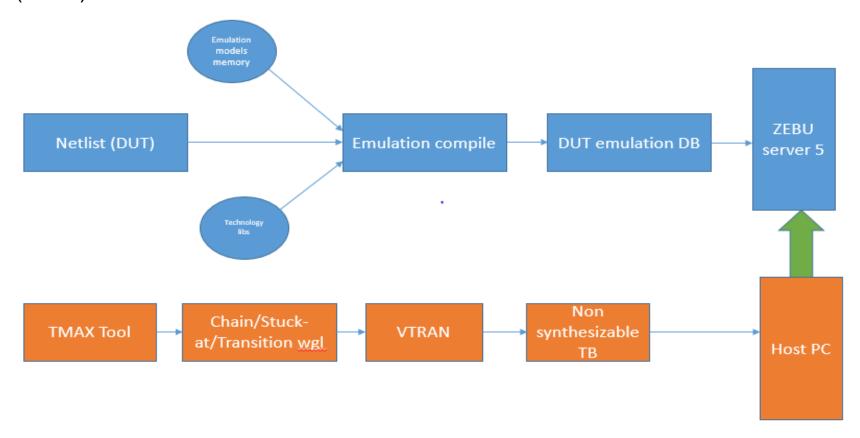

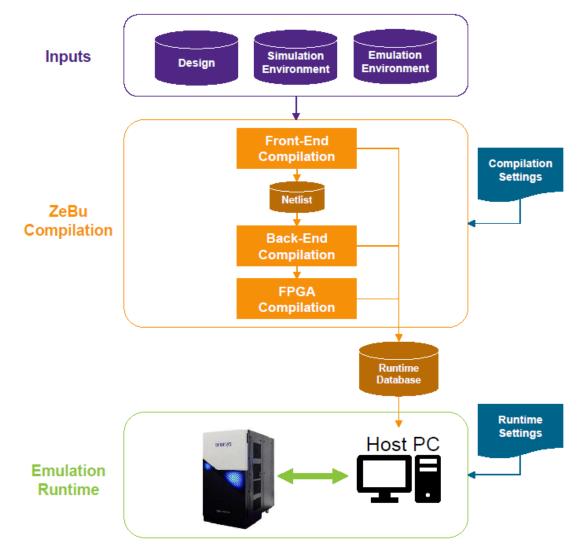

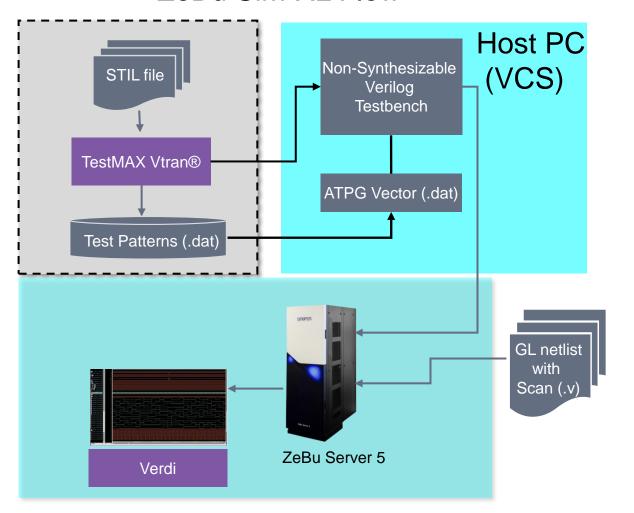

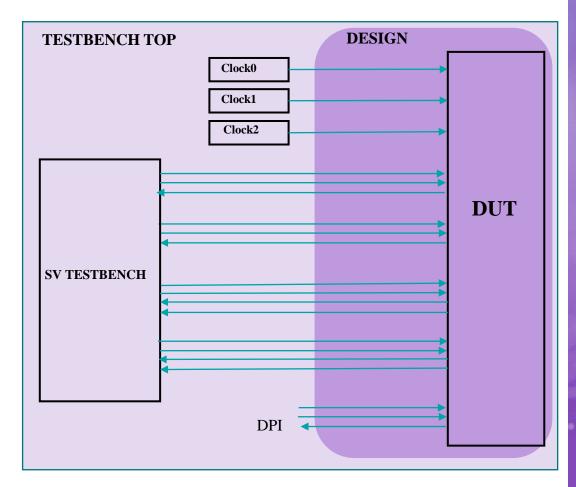

Simxl flow: It provides an incremental approach to bringing up a working simulation environment into an emulation environment. The approach starts with a signal-based communication mechanism between SW (VCS) and HW (ZeBu).

# **Execution Approach**

# **Execution Approach**

#### ZeBu Sim-XL Flow

### Technical Challenges

- SAMSUNG

- snug

- Migration from simulation to emulation.

- Emulation models.

- Debug: ZTDB to FSDB

- Optimization on post pnr netlist.

- PLL models.

- Timing simulations.

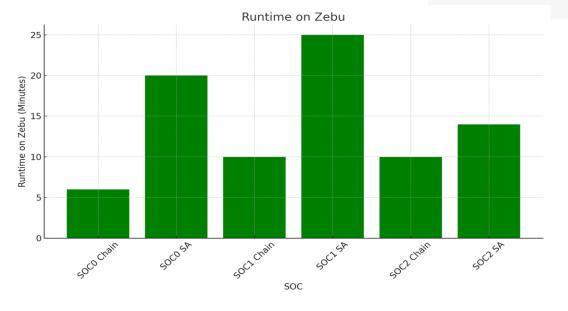

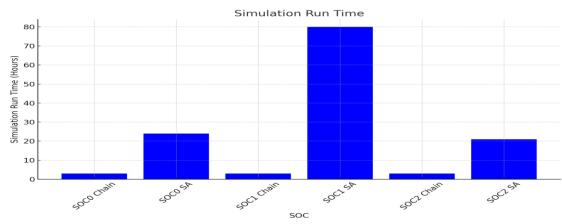

# Comparison of runtime for Simulation and Emulation

| soc        | Simulation<br>Run time      | Runtime on zebu          |

|------------|-----------------------------|--------------------------|

| SOC0 Chain | 7 chain pattern -> 3Hours   | 6min                     |

| SOC0 SA    | 200 pattern - > 24 Hours    | 10k pattern -<br>> 20min |

| SOC1 Chain | 7 pattern -> 3Hours         | 10min                    |

| SOC1 SA    | 200 pattern - > 80 Hours    | 10k pattern -<br>> 25min |

| SOC2 Chain | 7 pattern -> 3<br>Hours     | 10min                    |

| SOC2 SA    | 200 pattern -<br>> 21 Hours | 2k pattern -><br>14min   |

Months to Minutes

### Scope for Improvement

- In the Zebu-Simxl flow, Design under Test is mapped to hardware and the TB will run on the software. There is scope to make the synthesizable TB and map it to hardware.

- Currently the Design is partitioned and we are mapping each design to the hardware. Zebu should provide ways to map the complete design in one go.

#### Conclusion

**SAMSUNG**

Achieved 50 to 100x gain when simulating the complete serial scan pattern set in emulator over GLS.

• The experimental results show that for 3 clusters, the chain pattern, complete stuck-at ATPG WGL format pattern set of 10K can be simulated in emulator within hours.