### **Power Precision** Elevating IC Integrity with Power Replay

Subbash K P Ayan Datta Abhishek Gupta Western Digital Viswanath Daita Synopsys

### Introduction

VLSI design is progressing towards **Ultra Deep Sub-Micron technology** (UDSM) nodes to achieve higher level of performance, improved power efficiency and small form factor area.

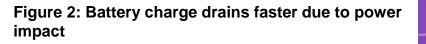

- Lower technology nodes trend (Figure 1) shows a major challenge on **power** which directly impacts the **battery life** and energy consumption of the System On-Chip(SOC) device.

- Accurate power modeling during chip design allows designers to identify and mitigate power-related issues early in the design phase.

- Helps in optimizing power usage without compromising on performance, ensuring cost-effective and robust designs.

- The major challenge is obtaining the accurate power numbers which is always late in the project cycle.

- So, This presentation covers about how PowerReplay steps in and uses **left shift approach** in closing the design with signoff accuracy.

Figure 1: Technology scaling trend data

# **Conventional methods and Challenges**

# **Conventional methods**

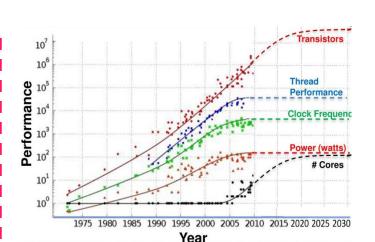

#### **Gate-Level Simulation**:

- Involves running full simulations on the synthesized gate-level netlist using realistic test vectors.

- **Limitation**: Time-consuming and requires considerable computational resources, making frequent analysis impractical.

#### **Vectorless Estimation**:

- Uses probabilistic models to estimate switching activity and hence power consumption.

- **Limitation**: Potential for significant inaccuracies as actual conditions can differ markedly from estimated models.

### Challenges

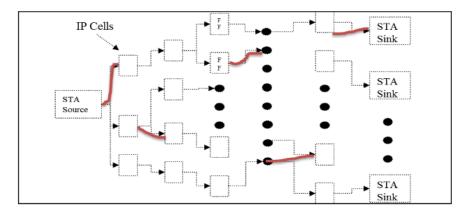

• **Delayed availability of Gate-Level FSDB:** Late availability of gate-level FSDB complicates SOC Integrity checks and delays final sign-offs.

- Late findings of Power Issues: Discovery of power issues during GLS simulation can impact project schedule.

- **Complexity of Modern Semiconductor Designs:** The intricate nature of contemporary designs increases the complexity of power simulations, potentially leading to longer runtimes as more detailed analyses are required to ensure accuracy.

- Accuracy in Dynamic Power Estimation: High accuracy in power estimation is crucial for making informed decisions during design iterations. Inaccuracies can lead to multiple design revisions, impacting the physical design closure and delaying the overall project timeline.

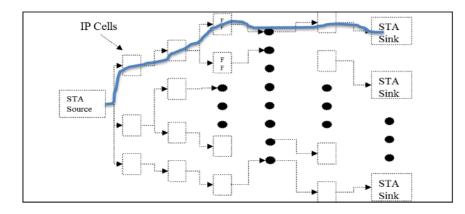

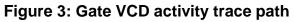

Figure 4: Vectorless implementation with random gate selection

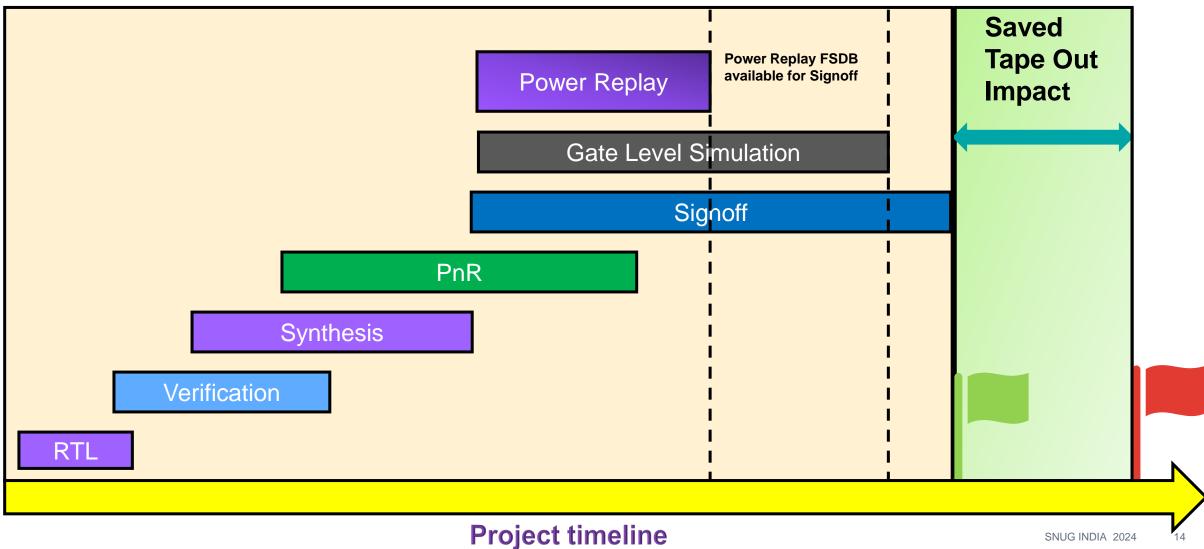

### **GLS Simulation Impact**

#### **Project timeline**

# **PowerReplay Flow**

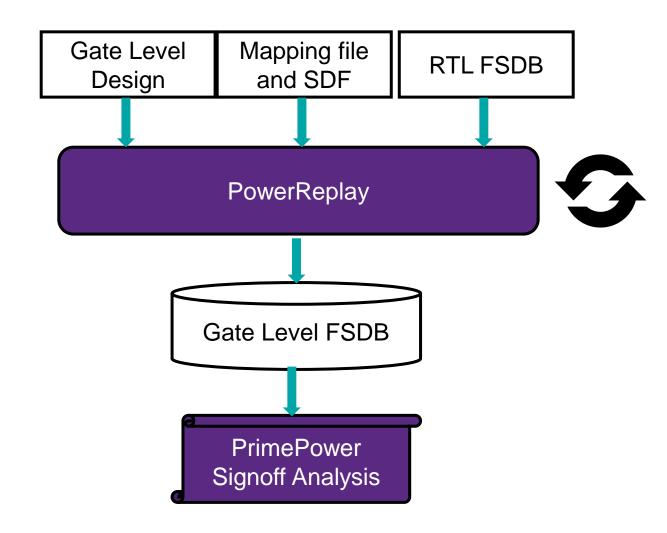

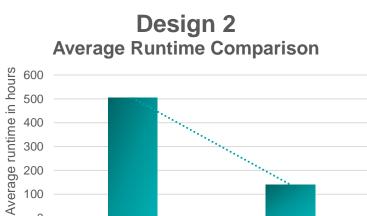

### PowerReplay Flow

| 1. RTL-Gate Mapping                    |

|----------------------------------------|

| <br>Using Good coverage RTL to Netlist |

| mapping.                               |

#### 2. Replay Simulation

- Used RTL FSDB (from VCS or 3<sup>rd</sup> Party)

- Specify sim. windows & design scope

- Auto-generate Gate-level TB

- Leverage SDF from STA.

- Generate Gate-level FSDB

#### 3. Power Analysis

Provide FSDB to PrimePower for Power analysis

9

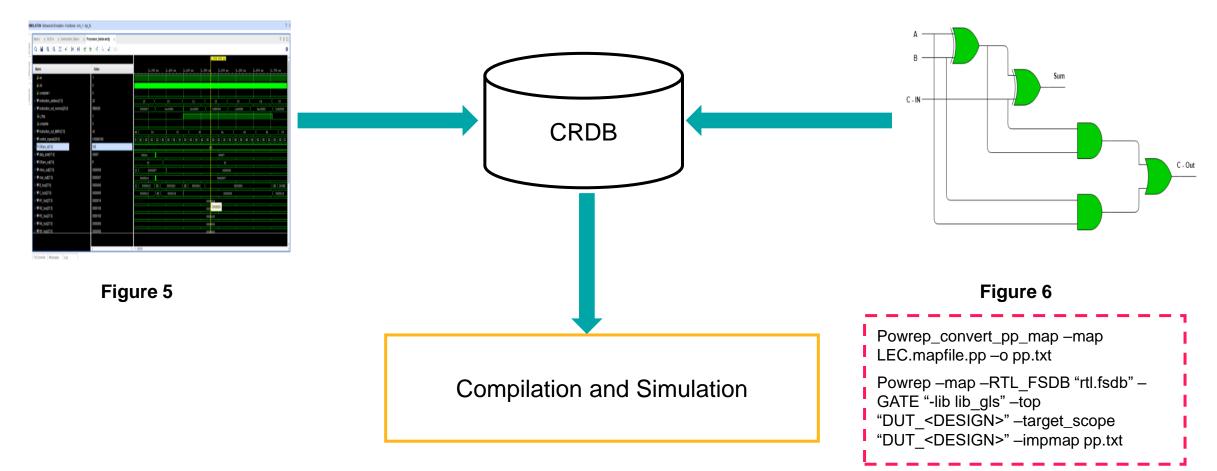

# PowerReplay Flow – Mapping feature

**Gate level Netlist**

\*Figure 5 image reference from Linkedin \*Figure 6 image reference from geeksforgeeks

**RTL FSDB**

### Sample Wi\_config file

- set FSDB = Design.fsdb (RTL FSDB)

- set Scope = tb.DUT.Design

- set Map = gls\_mapping.txt

- set Simulation\_Compile\_script = vcs\_wi\_compile.rc (Contains the VCS Gate Level Compile Command)

- set Simulation\_Run\_script = vcs\_wi\_run.rc (Contains the VCS Gate Level Run Command)

- set Checking\_Rule = +mapping\_quality

- set Begin\_Time = <BEGIN\_TIME>

- set End\_Time = <END\_TIME>

- set Time\_Unit = ns

- set SDF = Design.sdf

### **PrimePower Template**

- set\_host\_options -max\_cores

- restore\_session <SESSION\_PATH>

- set power\_enable\_analysis true

- set power\_analysis\_mode time\_based

- read\_fsdb -strip\_path <SCOPE\_PATH> -time {Begin time End time} <GATE\_LEVEL\_FSDB>

- update\_power

- report\_power -nosplit

- report\_switching\_power

# Left Shift Approach using PowerReplay

14

Western Digital, snug

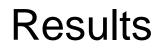

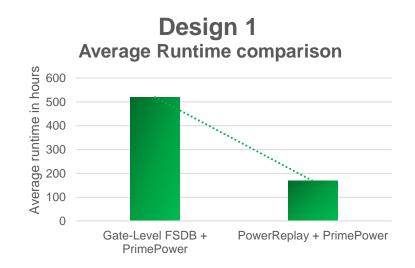

| Designs  | Gate Count | Total Power<br>difference between<br>Gate Level FSDB<br>and PowerReplay<br>FSDB | Peak Power<br>difference between<br>Gate Level FSDB<br>and PowerReplay<br>FSDB |  |

|----------|------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Design 1 | >800K      | ~2%                                                                             | ~14%                                                                           |  |

| Design 2 | >500K      | ~%5.3                                                                           | ~4.4%                                                                          |  |

98% Mapping coverage

0

# **Conclusion & Future Work**

### **Conclusion & Future Work**

#### • Efficiency and Time Savings:

- PowerReplay streamlines the power analysis process, significantly reducing the time from design to verification compared to traditional methods.

- Enables quicker iterations and faster decision-making, leading to shorter project timelines.

- TAT is almost improved by ~50%.

- Enhanced Accuracy:

- Offers more precise power consumption analysis by using real-life scenarios earlier in the design cycle.

- Helps in identifying and mitigating power-related issues well before they become costly to address in later stages.

- Future Work:

- Exploration on Integrated Power Replay feature in PrimePower tool.

- Work with Synopsys team to further improve the correlation between Simulation Gate level FSDB and Power Replay Gate level FSDB.

# THANK YOU

Our Technology, Your Innovation<sup>™</sup>