Enhancing Timing Signoff with Timing Constraint Manager: Case Study for SerDes and PCIe IPs

Synopsys Tutorial

Pawankumar Yendigeri Srini Gaddam Synopsys India Pvt Ltd, India Priyanka Goel Apoorv Srivastava

**SYNOPSYS**°

## Outline

- Timing closure and it challenges with current flows

- Synopsys E2E Constraints Flow

- Case-Study in SerDes MIPI MPHY

- Discussion

- Key Takeaways

- TCM Promotion flow

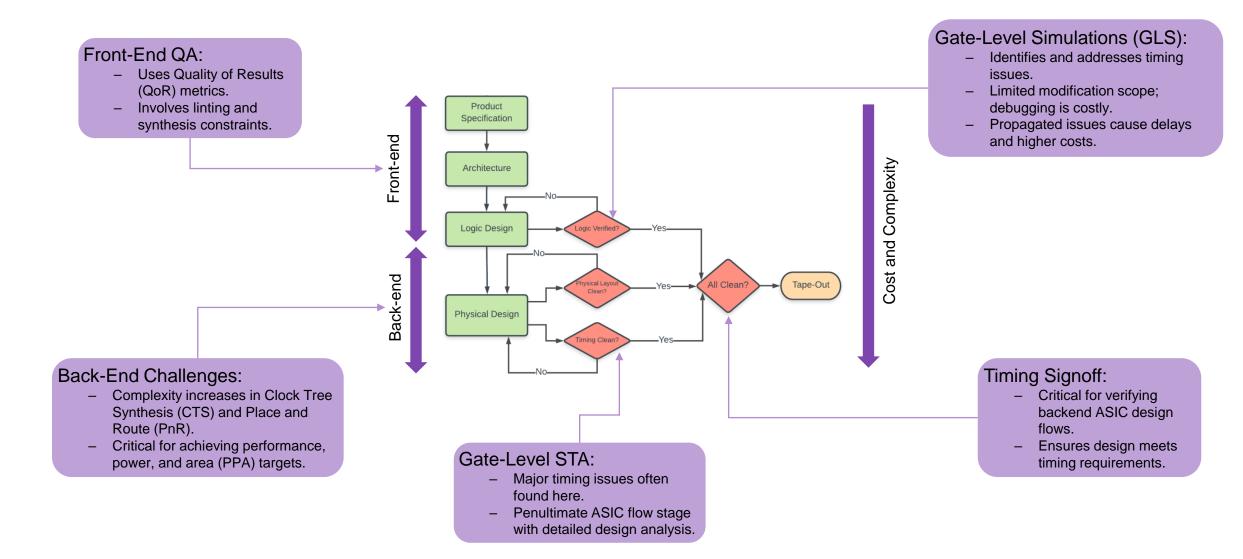

## Timing closure and it challenges with current flows

### **Overview**

**SYNOPSYS**<sup>®</sup>

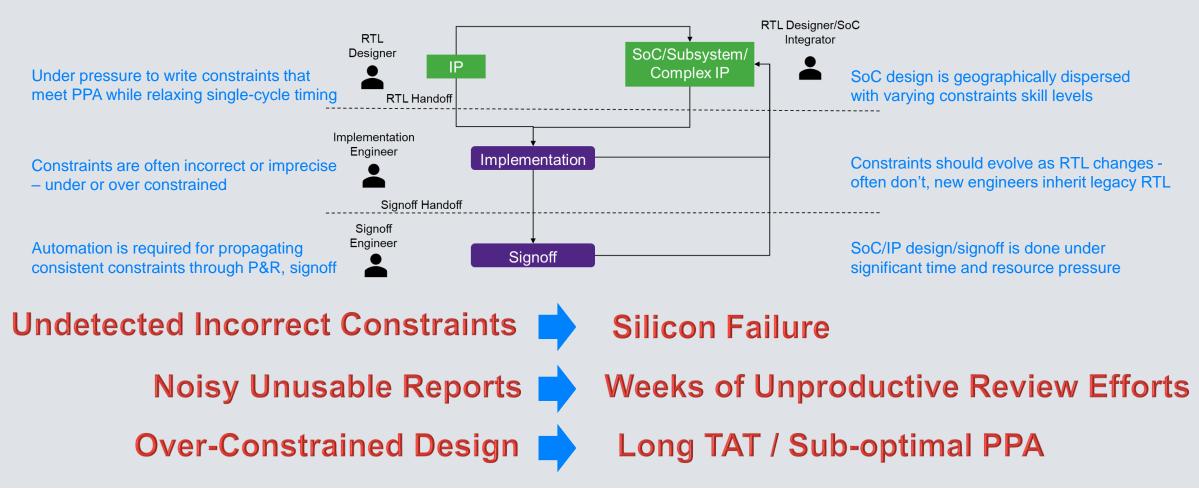

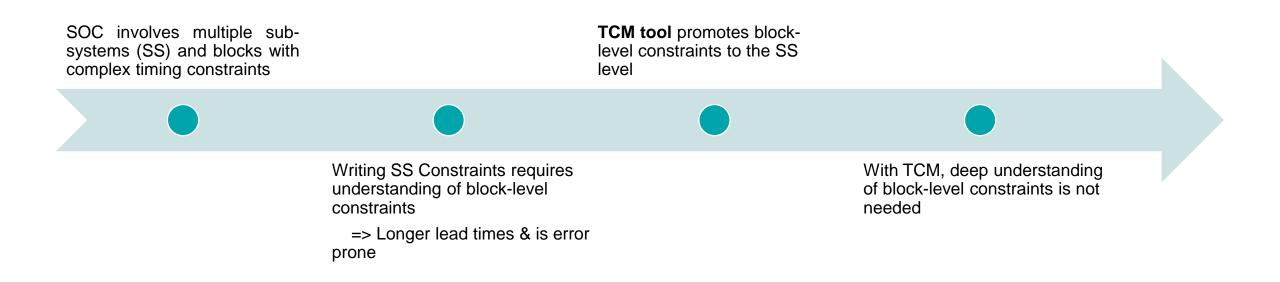

## The Constraints Challenge at Customers

#### SoC Design with External / Internal IP

**SYNOPSYS**°

## **Issues with Timing Closure**

Complex clock tree networks Post CTS Netlist based path checks

High computation Power TAT

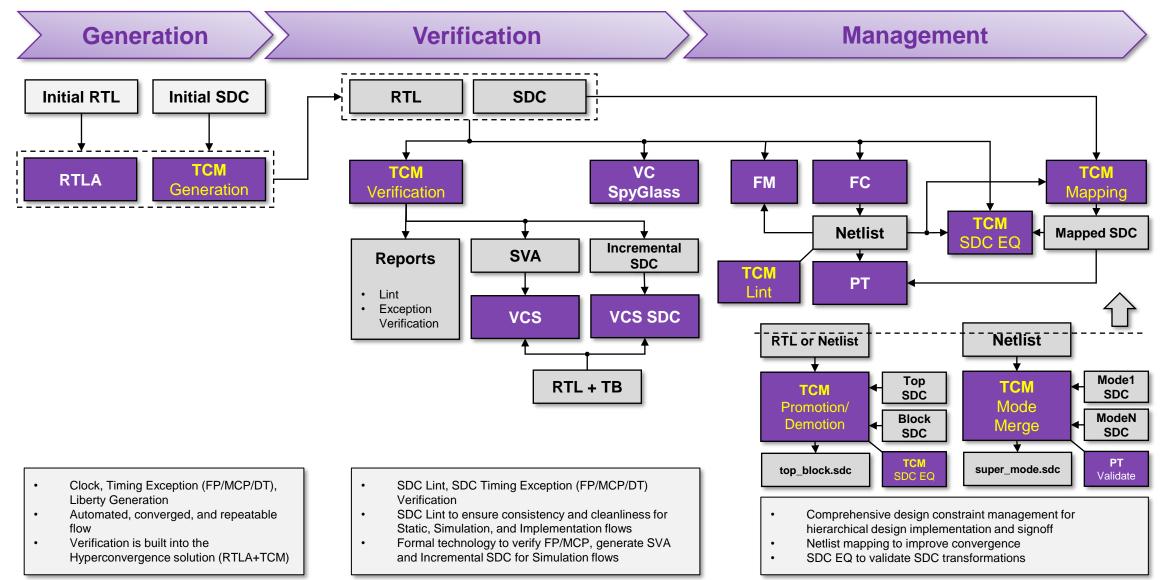

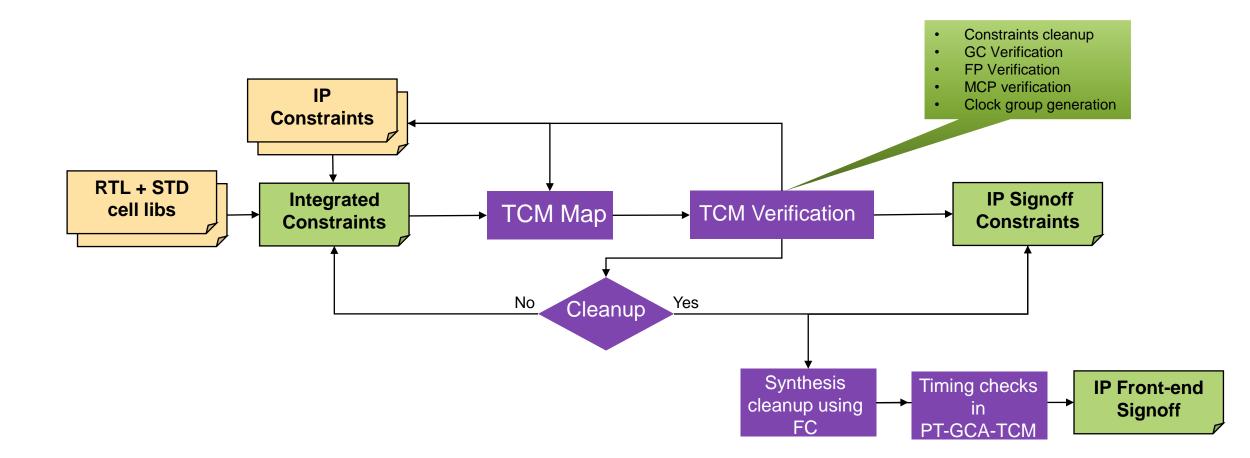

## Synopsys E2E Constraints Flow

## Synopsys E2E Constraints Flow

**SYNOPSYS**<sup>®</sup>

Synopsys Confidential Information

8

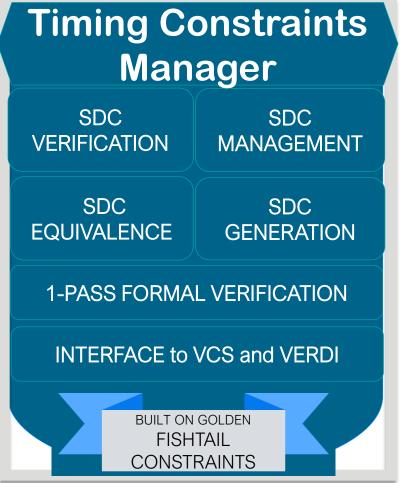

## Synopsys Timing Constraints Manager

Built on FishTail Best-in-Class SDC Constraints Solution

- Comprehensive SDC Timing Constraints Generation, Verification and Management

- Multi-Cycle/False Path Exception Verification with No Noise RTL Designers are provided precise feedback on their SDC bugs

- Comprehensive SDC Management solution Tape-out proven promotion, demotion, mapping solution

#### Automated SDC Generation from RTL

Saves weeks of designer effort and development schedule

Deployed at Top Tier Semi Companies with Production-Proven Tape-outs

## Case-Study SerDes applications

## Case Study

Use of TCM can be extensively tested on applications such as SerDes, where higher number of clock generation and verifications is involved

Majorly high-speed interface IPs like MIPI MPHY, involves high number of clocks and propagated paths that can be majorly benefitted through TCM flow

The MPHY (generic PHY+RMMI) clocking architecture involves more than 50 clock generations based on mode, gears(1 to 5), high speed(PLL) and low speed(PWM) etc.

The exceptions reported are crucial as it contains many constraints that cater to be used for specific configurations in

#### **TCM Deployment Methodology**

snu

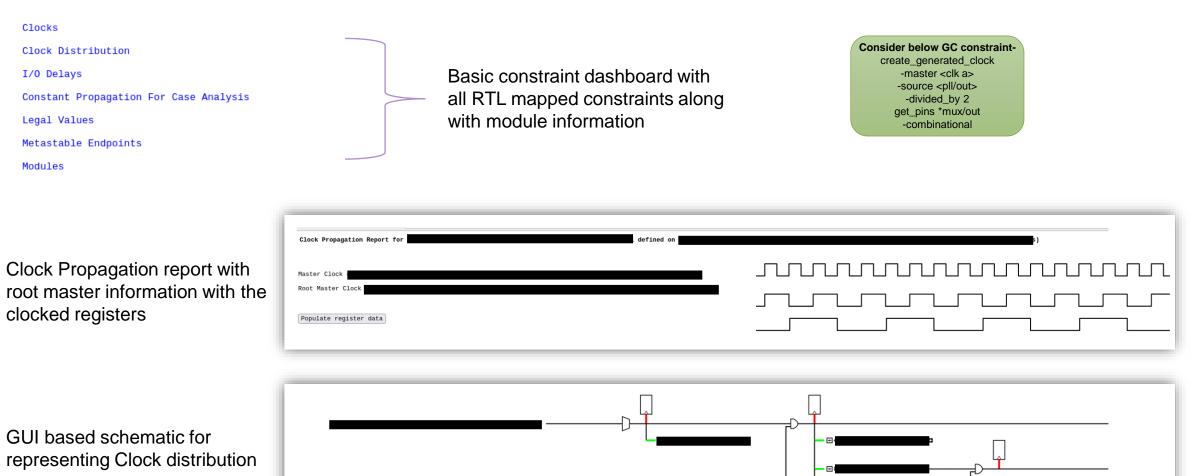

#### **Clock Verification checks - Example**

Design Information (dwc\_mipi\_mphy\_type1\_g5\_2tx\_2rx\_ns)

**SYNOPSYS**<sup>®</sup>

#### **Clock Verification checks** - Example

#### GUI Schematic depicting clock propagation condition

| <nwave:5> /remote//tcm_rt1_verification/verdi/mcp40000008</nwave:5> | 38_1.1.vcd.fsdb |                                                                                                                                                                     | ≀₽_□> |

|---------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <u>File Signal View Waveform Analog Tools Window</u>                |                 |                                                                                                                                                                     |       |

| 😑 🗗 🥱 😹 🕒 🗟 👌 💿 📥 💿                                                 | ▲ ▼ 0           | x 1ps 🕘 🕲 🕎 By: 🛐 🕶 💽 🏹 Goto: G1 💽                                                                                                                                  |       |

|                                                                     |                 | 0, 1, 1, 1, 1, [5001, 1, 1, 1, 1, 000, 1, 1, 1, 1, 500, 1, 1, 1, 12, 000, 1, 1, 1, 13, 500, 1, 1, 1, 13, 500, 1, 1, 1, 14, 000, 1, 1, 1, 14, 500, 1, 1, 1, 15, 000, | 1.1.1 |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 | 1                                                                                                                                                                   |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 | 0 0                                                                                                                                                                 |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 | f                                                                                                                                                                   |       |

|                                                                     |                 |                                                                                                                                                                     |       |

|                                                                     |                 | 0 0 1                                                                                                                                                               |       |

|                                                                     | 177             |                                                                                                                                                                     | 6,500 |

| 1                                                                   |                 |                                                                                                                                                                     |       |

Assertion dumped for verifications of high/low pulse checks for generated clocks

#### False Path Verification checks - Example

False path exception mapped by TCM

#### set\_false\_path -from [get\_clocks clk a] -through [get\_pins -hier "port a port b …"]

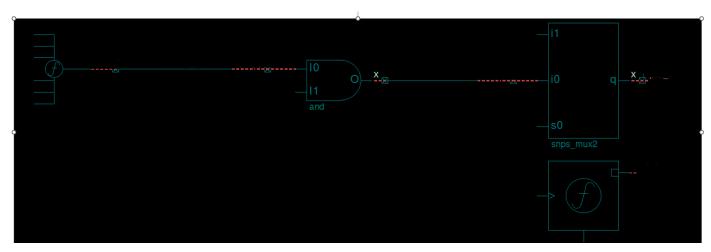

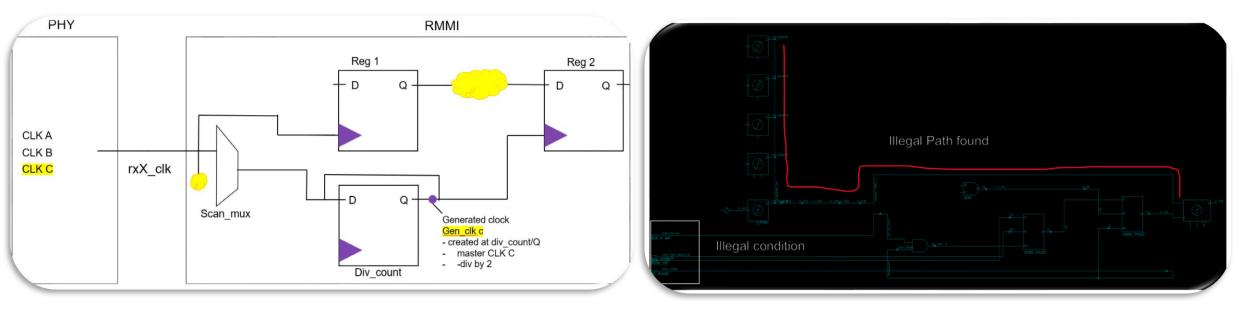

MPHY Rx Clocking architecture Uses CLK C to create Gen\_clk c Verdi based schematic view for assertion generated for false path constraint

#### Implicit timing updates- Example

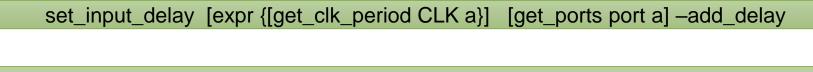

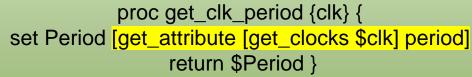

Use of below queries in the constraints causes Synthesis/STA tool to trigger implicit timing update-

- get\_attribute [\*] query

- set\_case\_analysis

- remove\_case\_analysis

- ✤ all\_registers/all\_fanin/all\_fanout

Consider below MPHY example-

This resulted in TCM warning (SDC\_068) in setup as below as it will not query the attribute-

Error: Execution error in SDC on line 'xx' of file 'mphy\_constraints. (SDC-068) >> can't use empty string as operand of "/" >> while executing >> "expr {[get\_clk\_period CLK a}"

>> invoked from within

>> set\_input\_delay [expr {[get\_clk\_period CLK a}] [get\_ports port a] -add\_delay..."

where,

#### **TCM Checks**

sn

| <b>Clock Verification Warnings</b> | Θ    |

|------------------------------------|------|

| Clock Issues                       | 433  |

| IO Issues                          | 3421 |

| Case Analysis Issues               | 1    |

| Exception Issues                   | Θ    |

| Generated | <b>Clock Verification</b> | 100% |

|-----------|---------------------------|------|

| Generated | Clocks                    | 110  |

| Passing   |                           | 19   |

| Failing   |                           | 0    |

| Skipped   |                           | 82   |

| Waived    |                           | 0    |

| False Path Verification | 100% |

|-------------------------|------|

| False Paths             | 35   |

| Passing                 | 0    |

| Failing                 | 0    |

| No Paths                | 30   |

| Skipped                 | 5    |

| Waived                  | 0    |

| Multicycle Path Verification | 100% |

|------------------------------|------|

| Multicycle Paths             | 2    |

| Passing                      | 1    |

| Failing                      | Θ    |

| No Paths                     | 0    |

| Skipped                      | 1    |

| Waived                       | 0    |

#### Message Severity Warnings Waived

| CLK-009         47         0           CLK-010         11         0           CLK-016         4         0           CLK-018         22         0           CLK-027         20         0           CLK-028         313         0           CLK-037         3         0 | CLK-006 | 2   | 13  | 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|---|

| CLK-016         4         0           CLK-018         22         0           CLK-027         20         0           CLK-028         313         0                                                                                                                     | CLK-009 | €X  | 47  | 0 |

| CLK-018         22         0           CLK-027         20         0           CLK-028         313         0                                                                                                                                                           | CLK-010 | Xa  | 11  | 0 |

| CLK-027         20         0           CLK-028         313         0                                                                                                                                                                                                  | CLK-016 | eX. | 4   | 0 |

| CLK-028 313 0                                                                                                                                                                                                                                                         | CLK-018 |     | 22  | 0 |

|                                                                                                                                                                                                                                                                       | CLK-027 |     | 20  | 0 |

| CLK-037 💂 3 0                                                                                                                                                                                                                                                         | CLK-028 |     | 313 | 0 |

|                                                                                                                                                                                                                                                                       | CLK-037 | ex. | 3   | 0 |

Clock warnings

| Classification         | Exception<br>Count | Path<br>Count |      |       |

|------------------------|--------------------|---------------|------|-------|

|                        |                    | Pass          | Fail | Total |

| PASS                   | Θ                  | 0             | Θ    | 0     |

| PARTIAL FAIL           | 2                  | 108           | 448  | 556   |

| FAIL                   | 4                  | 0             | 4008 | 4008  |

| NO PATHS               | 29                 | 0             | Θ    | 0     |

| SKIPPED (Async Clocks) | Θ                  | 0             | Θ    | 0     |

| SKIPPED (I/O Paths)    | 0                  | 0             | Θ    | 0     |

| SKIPPED (Internal)     | Θ                  | 0             | Θ    | 0     |

| SKIPPED (Hold FP)      | Θ                  | 0             | Θ    | 0     |

| SKIPPED (Duplicate)    | Θ                  | 0             | Θ    | 0     |

| SKIPPED (User)         | Θ                  | 0             | Θ    | 0     |

| WAIVED                 | 0                  | 0             | Θ    | 0     |

| WAIVED BY TOOL         | Θ                  | 0             | Θ    | 0     |

| Total                  | 35                 | 108           | 4456 | 4564  |

False path checks

| Message Type         | Warnings | Waived |

|----------------------|----------|--------|

| Clock Issues         | 624      | 0      |

| IO Issues            | 703      | 0      |

| Case Analysis Issues | 1        | 1      |

| Exception Issues     | Θ        | 0      |

#### Constraint warnings

| Classification          | Exception<br>Count | Path<br>Count |      |       |

|-------------------------|--------------------|---------------|------|-------|

|                         |                    | Pass          | Fail | Total |

| PASS                    | 0                  | 0             | 0    | 0     |

| PARTIAL FAIL            | Θ                  | 0             | 0    | 0     |

| FAIL (Incorrect Shift)  | Θ                  | 0             | 0    | 0     |

| FAIL                    | Θ                  | 0             | 0    | 0     |

| NO PATHS                | Θ                  | 0             | 0    | 0     |

| SKIPPED (Async Clocks)  | Θ                  | 0             | 0    | 0     |

| SKIPPED (I/O Paths)     | 1                  | 0             | 0    | 0     |

| SKIPPED (Internal)      | Θ                  | 0             | 0    | 0     |

| PASS (Hold < Setup)     | 1                  | 0             | 0    | 0     |

| SKIPPED (No Relaxation) | 0                  | 0             | 0    | 0     |

| SKIPPED (Duplicate)     | Θ                  | 0             | 0    | 0     |

| SKIPPED (User)          | Θ                  | 0             | 0    | 0     |

| WAIVED                  | 0                  | 0             | 0    | 0     |

| WAIVED BY TOOL          | 0                  | 0             | 0    | 0     |

| Total                   | 2                  | 0             | 0    | Θ     |

Multi-cycle path checks

#### After cleanup

| © 2024 Synopsys, Inc. | 18 |

|-----------------------|----|

|-----------------------|----|

| Early-stage detection          | <ul> <li>As TCM requires only RTL as a part of design input, it proves<br/>to be beneficial in tracking and debugging constraint issues at<br/>initial stages of ASIC flow</li> </ul> |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rigorous constraints<br>checks | <ul> <li>The rules involved in TCM are categorical in addressing issues<br/>related to clock domain crossing, clock relationships, io delays<br/>for design ports etc.</li> </ul>     |

| Timing<br>Optimisation         | <ul> <li>TCM helps getting rid of constraints that cause implicit timing<br/>updates that result in long source time for constraints during<br/>Back-end flows</li> </ul>             |

| Runtime                        | <ul> <li>As TCM does not involve any requirement of synthesis-based<br/>netlist setup, the QA time is much lower than any other<br/>constraint management tool</li> </ul>             |

| Promotion                      | <ul> <li>Issues related to adaptation of constraints in the upper layer in<br/>IP integration can be tracked in early stages using TCM<br/>promotion flow</li> </ul>                  |

| Less noise in GLS<br>setup     | <ul> <li>Cleanup of GLS will be quicker, since the simulation-based<br/>setup in TCM mimics the issues that can be seen in the GLS<br/>setup</li> </ul>                               |

Guidelines and Best Practices for Subsystem Constraints Development with TCM Promotion Tool

Apoorv Srivastava, Priyanka Goel, Akanksha Jat, Naveen Battu Synopsys

#### Agenda

- TCM Constraints Promotion Flow

- The Value Proposition

- The Flow

- Steps (Unix Commands for TCM Constraints development flow)

- Why Top SDC if we are promoting?

- Insights from Case Study of PCIe6 Subsystem

- Overview of Pilot Project

- Tool Behavior

- Guidelines

- Conclusion: Pros/Cons

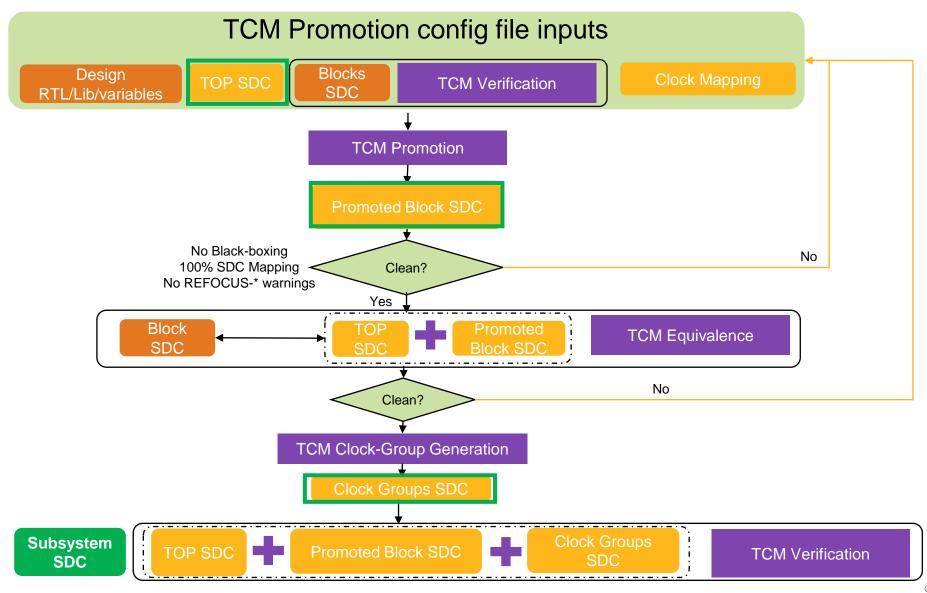

## TCM Constraints Promotion Flow

#### **The Value Proposition**

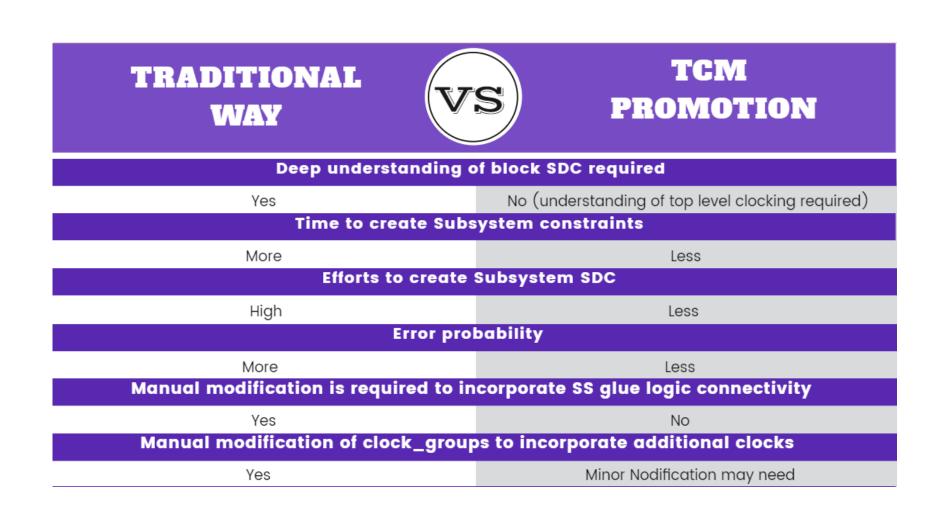

In this presentation, we will share our experience of using TCM Constraints promotion for a PCIe6 Subsystem consisting of Synopsys PCIe6 Controller and Synopsys PCIe6 PHY

## The Flow

#### Steps (Unix Commands for TCM Constraints development flow)

- –Unix %> <source> tcm

- \_Unix %> create\_fishtail\_scripts-config rtl\_constraint\_promotion.cfg

- –Unix %> cd <fishtail\_rtl\_constraint\_promotion>/constraint\_promotion

- –Unix %>./promote\_constraints

- –Unix %> output : promoted.sdc

- –Unix %> view\_fishtail\_result–verdi

- –Unix %> cd ../equivalence\_checking

- –Unix %>./check\_equivalence

- –Unix %> view\_fishtail\_result–verdi

- –Unix %> cd ../clock\_group\_generation

- –Unix %>./generate\_clock\_groups

- –Unix %> output : clock\_groups.sdc

#### **Steps (Unix Commands for TCM Verification)**

- –Unix %> create\_fishtail\_scripts -config rtl\_verification.cfg

- –Unix %> cd ./<tcm\_verification>/setup

- –Unix %>./map\_sdc\_and\_check\_setup

- –Unix %> view\_fishtail\_result–Verdi

### Why Top SDC if we are promoting ?

• Top-level clocks, timing exceptions and IO constraints are required to be defined

```

#Top level SDC

#TOP level clocks

create clock \

-period 9.0 \

{ phy0 pmd jtag tck } \

-name phy0 pmd jtag tck i \

-add

create clock \

-period 9.0 \

name vi phy0 pmd jtag tck i

create clock \

-waveform { 0 2.0 } \

-period 4.000 \

{ apb pclk } \

-name apb pclk

#Top level timing exceptions

set clock groups 🔪

-asynchronous \

-name all phy functional clks from different sources top clks \

-group { apb pclk } \

-group { phy0 pmd jtag tck i vi phy0 pmd jtag tck i }

set input delay \

2.2 \

-clock { vi phy0 pmd jtag tck i } \

{ phy0 pmd jtag tms } \

-max

set false path \

-through { u pcie ctrl top 0/u pcie core/u DWC pcie native core/u DWC pcie core/u cdm/cfg tc vc map[*] }

```

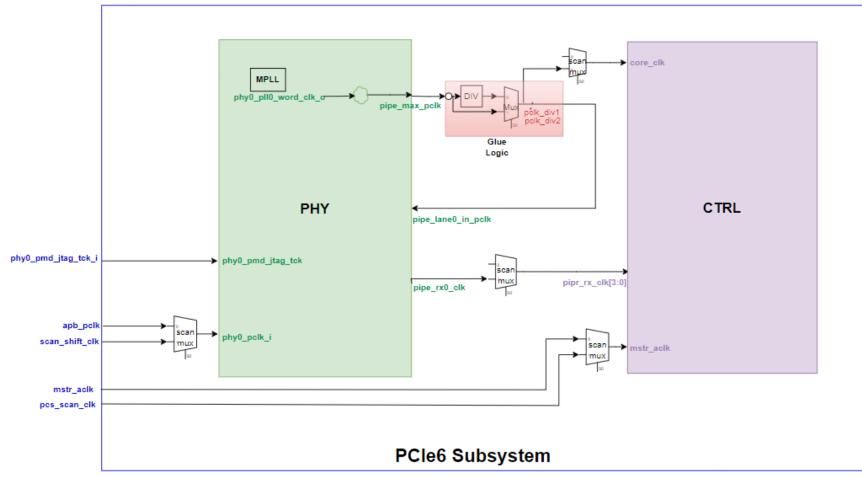

## Insights from Case Study of PCIe6 Subsystem

#### **Overview of Pilot Project**

Block Diagram of PCIe6 Subsystem (with clocking)

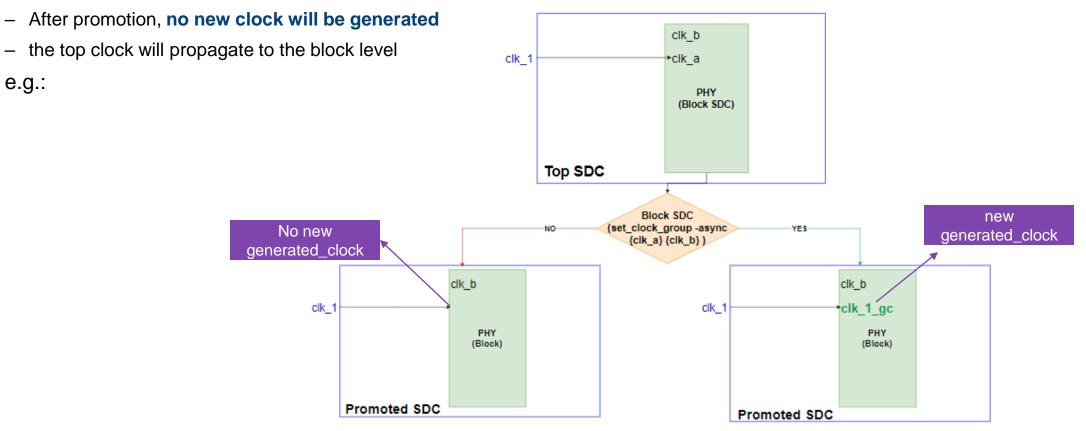

#### **Tool Behavior**

• TB1: If, timing exception is not defined on a clock in block SDC

TB2: Output delay at the block level will be promoted w.r.t. top clocks if there is a direct connection between the mapped block clock to the top clock

#### **Guidelines:1/8**

- G1: Block SDC should be passed through a **constraint's quality check** using the TCM verification tool

- Otherwise, any weakness at block level SDC will get promoted to Subsystem SDC

- e.g.

Warning: There is a timed asynchronous clock crossing but one or more paths for this clock crossing do not have a max delay constraint. (CLK-038)

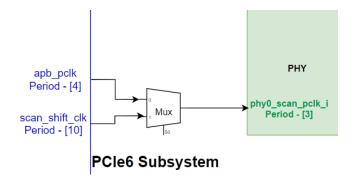

#### **Guidelines:2/8**

- G2: Top-level clocks propagating to the block-level clock ports should match their period/name for tool default clock mapping

- Otherwise, the tool will do a random mapping with a single clock and report a warning

Warning: The period of the top-level clock is different from the block-level clock that it is mapped to. (REFOCUS-070)

- The mapping can be overridden by user-defined clock mapping

e.g.:

|           | CLOCK NAME       | PERIOD |

|-----------|------------------|--------|

| Top Clock | apb_pclk         | 4      |

| Top Clock | scan_shift_clk   | 10     |

| PHY Clock | phy0_scan_pclk_i | 3      |

• Tool Clock Mapping from TCM GUI looks like

| Instance                 | Block Clock      | Definition Pin | Propagated Top-Level Clocks | Mapped Top-level Clock | User Defined Clock Mapping                     |

|--------------------------|------------------|----------------|-----------------------------|------------------------|------------------------------------------------|

| u_pcie_phy_top/pcie_pipe | phy0_scan_pclk_i | phy0_pclk_i    | apb_pclk<br>scan_shift_clk  | apb_pclk               | scan_shift_clk<br>phy0_scan_pclk_i<br>apb_pclk |

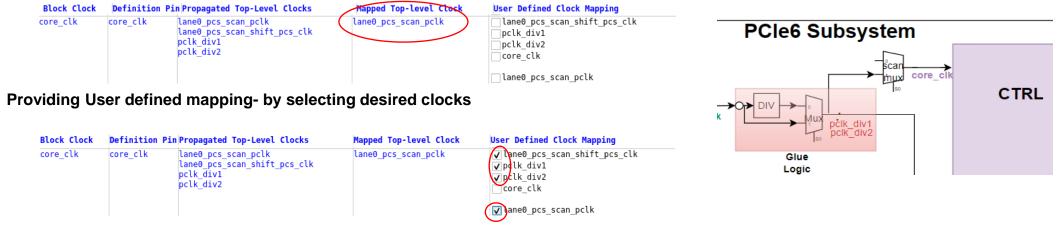

#### **Guidelines:3/8**

- G3: If multiple clocks need to map to block-level clock, user-defined clock mapping is required

- Otherwise, the tool will do a random mapping with a single clock and report a warning

Warning: Multiple top-level clocks propagate to a block-level clock. All but one of them are dropped. (REFOCUS-064)

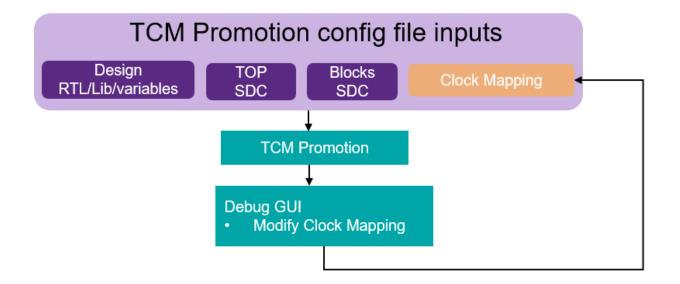

- After the first iteration of TCM Promotion, this file is dumped from the tool, modified, and provided as input to the promotion flow

#### **Guidelines:3/8**

#### **Clock Mapping**

•

• Tool Clock Mapping from TCM GUI looks like

• Dumped File – clock\_mapping.tcl

map\_top\_clock\_to\_block\_clock -block\_clock core\_clk\_ug -top\_clock { lane0\_pcs\_scan\_pclk lane0\_pcs\_scan\_shift\_pcs\_clk pclk\_div1 pclk\_div2 } -pin u\_pcie\_ctrl\_top\_0/u\_pcie\_core/core\_clk\_ug

User-defined Clock Mapping

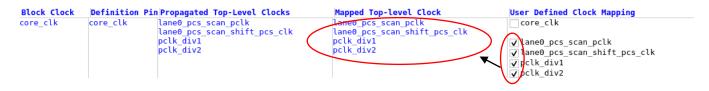

#### **Guidelines:4/8**

- G4: In Top SDC, clock\_group should be defined with clock\_group\_name

- The tool can remove the top clock group after promotion, if required and create a new clock group with updated clock relationship

- e.g. a clock async with all other clocks at the top level

clk1

clk2

After promotion it should be synchronous with its generated clock and asynchronous with all other clocks.

Subsystem SDC = Top SDC + Promoted SDC

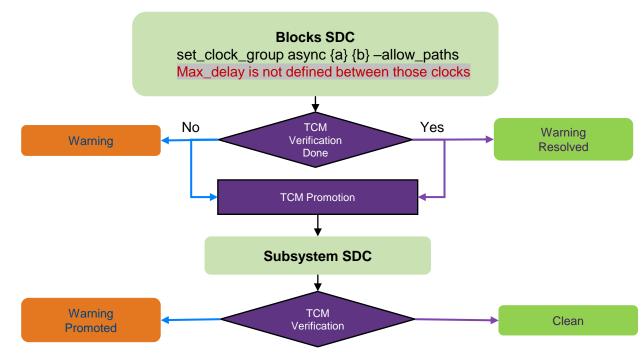

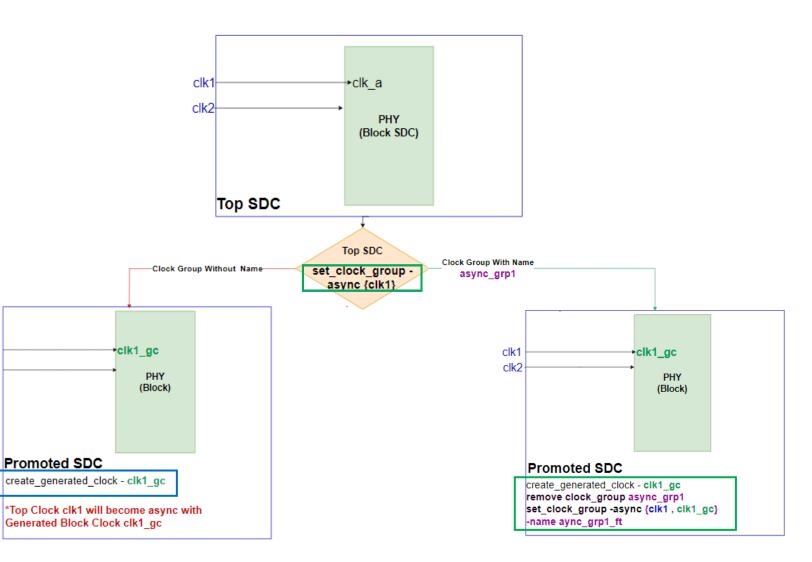

#### **Guidelines:5/8**

- G5: Set TCM variable create\_async\_clock\_group 1 in TCM config file

- It creates an async clock group that specifies

- That clocks created in different blocks being promoted are async to each other and top-level clocks

- If create\_async\_clock\_group is 0, the tool will report a warning in TCM verif for missing clock group

- Warning: There is an asynchronous clock group <sup>clk1</sup> between clock 'clk\_a' and clock 'clk\_b' but their master clocks 'clk1' and 'clk\_b' are missing this constraint. (CLK-026)

Subsystem SDC = Top SDC + Promoted SDC

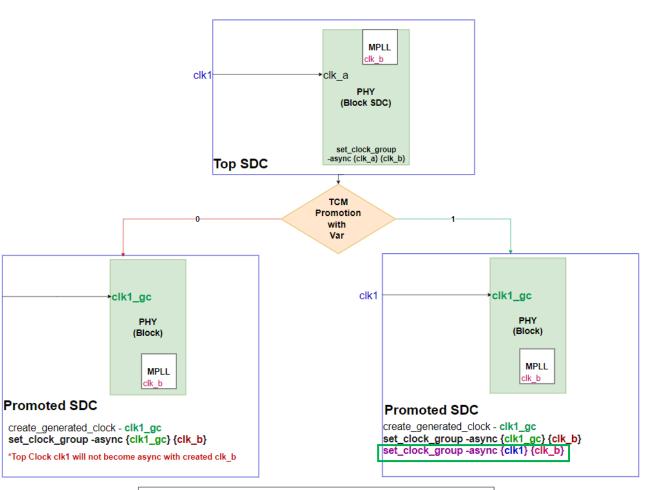

#### **Guidelines:6/8**

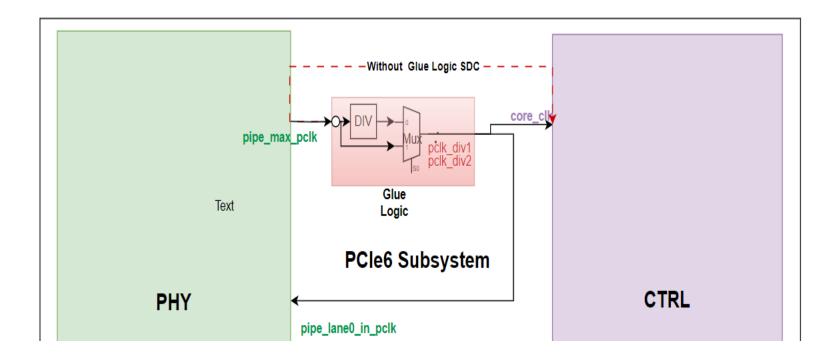

G6: The SDC should be provided for a block in Subsystem glue logic that has a clock-shaping circuit (divider) e.g.:

In our PCIe6 Subsystem, the CLKRST block has a divider that connects the PHY output max\_pclk to the CTRL input core\_clk Glue Logic (CLKRST) SDC is provided along with PHY and CTRL for constraint promotion

#### **Guidelines:7/8**

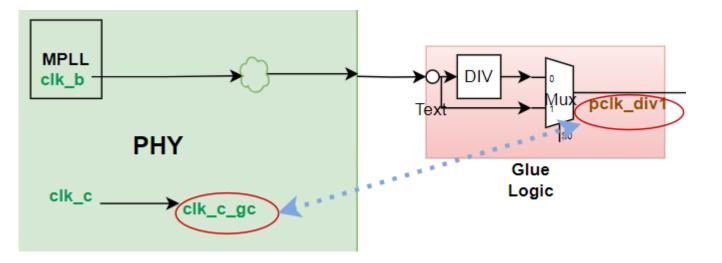

#### • G7: Run Clock Group Generation after TCM promotion

- Some of clock grouping is already handled in promotion flow

- Few clock grouping were missing which will be added by clock group generation step

- In absence of it, TCM verif will report below warning

Warning: There is an asynchronous clock group between master clocks **clk\_b** and **clk\_c** but generated clocks **plck\_div1**' and **clk\_c\_gc'** are missing this constraint. (CLK-023)

- With Clock\_Group\_Generation:

- New async clock\_groups created by clock\_group\_generation between the clocks present in different blocks

#### **Guidelines:8/8**

#### Run TCM verification after Promotion at Subsystem SDC- it can highlight important issues

- G8: If at the block level, some clock\_group is defined between clocks e.g. asynchronous

- After promotion those promoted clocks become logically\_exclusive by design

- Then the promotion tool will not change clock group from async to logically\_exclusive

- TCM verification tool report the warning

Warning: Clocks are logically exclusive but they have not been specified as such. (CLK-022)

– e.g.

\_

- After Promotion CTRL Block Level Logical exclusive {pclk\_div2} {pclk\_div1} async {clk\_a} {clk\_b} Async {pclk\_div2\_gc} {pclk\_div1\_gc} CTRL PHY CLKRST CTRL clk\_a pclk div2 pclk\_div2\_gc Mux pclk div1 clk b pclk\_div1\_gc clk1 PCIe6 Subsystem

- Manual modification (Logical Exclusive {pclk\_div2\_gc} {pclk\_div1\_gc} in promoted constraints is required to take care of such a scenario based on design

#### How are the promoted constraints checked ?

#### TCM Equivalence is run to ensure promoted SDC is aligned with block SDC

# TCM Verification is run on Subsystem SDC (Top SDC + Promoted SDC + Clock Group SDC) to check the quality of constraints

## Conclusion

#### Conclusion : Pros/Cons

# Q&A

Our Technology, **Your** Innovation<sup>™</sup>

**SYNOPSYS**°

2024 Synopsys, Inc

# THANK YOU

#### Other collaborators-

Utkarsh Pandharkar Prabhat Yadav Naveen Battu Our Technology, **Your** Innovation<sup>™</sup>

**SYNOPSYS**°

2024 Synopsys, Inc.