Efficiency Unleashed: Signoff Abstract Model's (SAM) Resource Mastery, Guaranteed QoR and Turbocharged TAT in Static Multi Voltage Verification (SMVV) space

Shauvik Panda Abhijeet Kumar Mugdha D Alurkar Intel India Pvt. Ltd.

- Introduction

- Traditional Static LP Verification Challenges

- What is SAM Model?

- Retention Principle

- Incremental Features of SAM

- SAM Execution Model

- QoR Flow

- Result

- Conclusion

- Acknowledgement

# Traditional Static LP verification Challenges

- As Design sizes grow and advanced power-aware architectures become prevalent, it is crucial to implement early and efficient Static Multi Voltage Verification (SMVV) as a part of convergence and signoff.

- LP checker tool will perform comprehensive SMVV for UPF correctness & implemented power-intent later in • the design flow.

- Traditional SMVV follows 2 approaches:

- Full Flat Flow

- Full Low Power (LP) coverage.

- High resource requirement.

- High Turn Around Time (TAT).

- Black Box Flow

- Lesser TAT and resource requirement.

- Less coverage.

- LP information lost.

Need a robust solution overcoming TAT and resource upshift while maintaining LP coverage intact. SNUG INDIA 2024 3

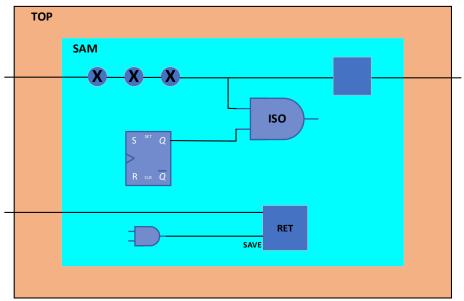

## What is SAM Model?

- snug

- Signoff Abstract Model (SAM) is a leaner retained model created out of original netlist taking into consideration the UPF constructs.

- The main retention logic principle it follows "starting from all Primary Input (PI)/Primary Output (PO) traverses forward/backward, goes through all buffers, inverters, power management cells and stop at first cell/operator which is not part of the aforementioned elements".

- The model goes in hand with flat UPF.

## **Retention Principle**

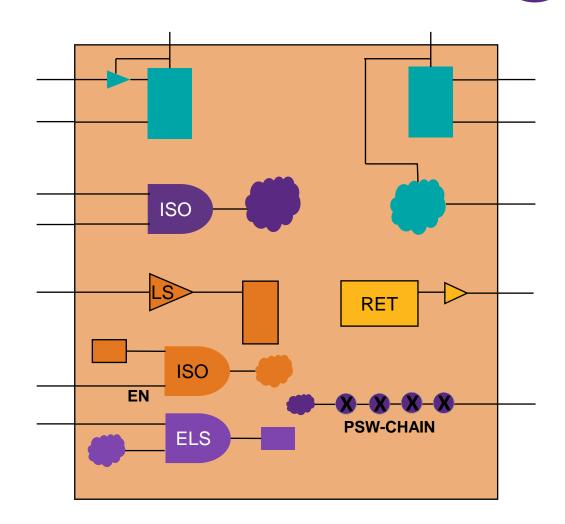

PI & PO connected cells

All supply nets connected to retained PG pins

2

3

4

ISO cells connected to PI/PO

LS cells connected to PI/PO

5

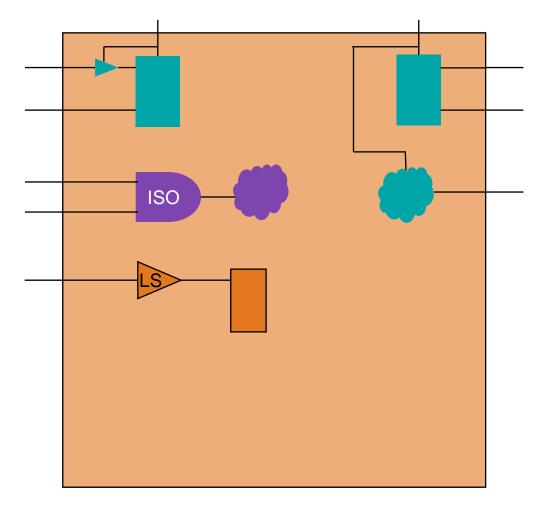

## Retention Principle (Contd.)

Retention cells connected to PI/PO

LP cells control pin connected to PI/PO

Full crossover path of all input of LP Cells if any connected to PI/PO

5

6

7

Full Power switch chain if any input/output connected to PI/PO

6

snu

#### **Incremental SAM Updates**

- Single Go Execution-

- Normal LP Execution with SAM generation.

- o Unaltered Block QoR.

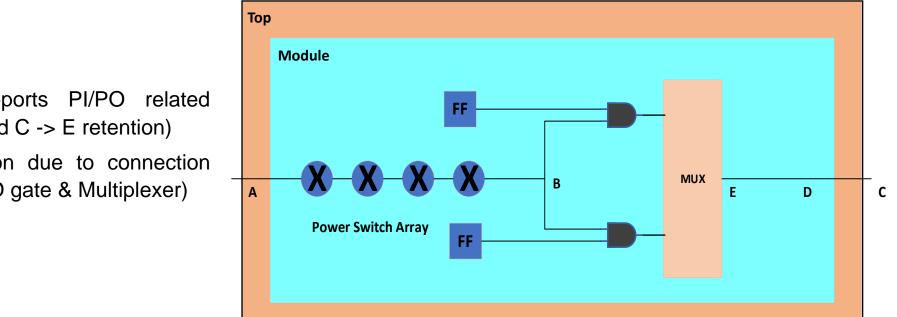

- Power Switch Retention-

- Retention principle supports PI/PO related connection. (e.g. A->B and C -> E retention)

- Update to more retention due to connection validation. (e.g. Flop, AND gate & Multiplexer)

7

## Incremental SAM Updates (Contd.)

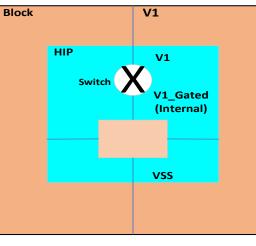

- Support for Virtual Supplies-

- $\circ~$  Virtual supplies present in PST.

- $\circ~$  PST merging requires these definitions preserved.

Create\_supply\_net V1\_Gated

Connect\_supply\_net V1\_Gataed -ports HIP/V1\_Gated

Add\_port\_State .. V1\_Gated ..

Create\_pst .. -supplies { .. V1\_Gated ..}

- Extra Logic Retention

- $\circ~$  Extra retention for control signals.

- $\circ~$  Control and driving logic preserved.

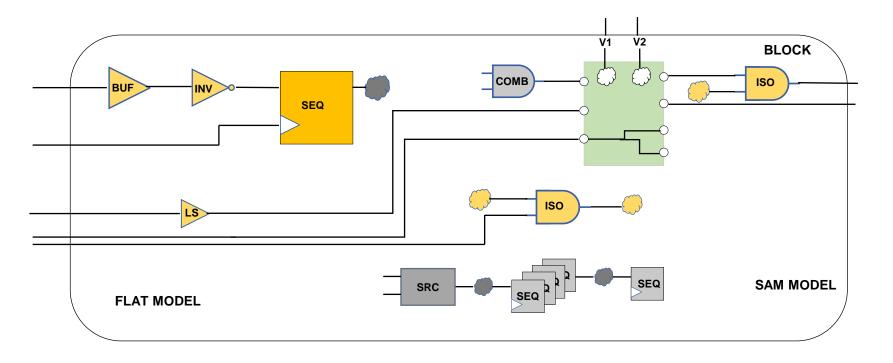

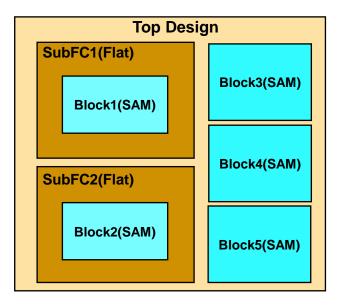

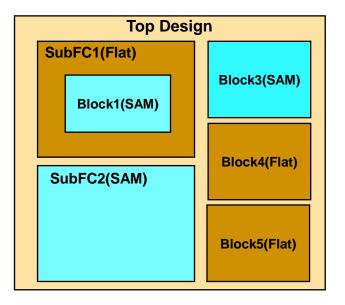

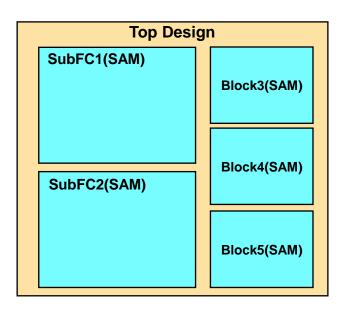

#### SAM Execution Model

- SAM models can be used in different versatile combinations as per design need.

- Best execution model will always be All blocks are used as SAM in design.

9

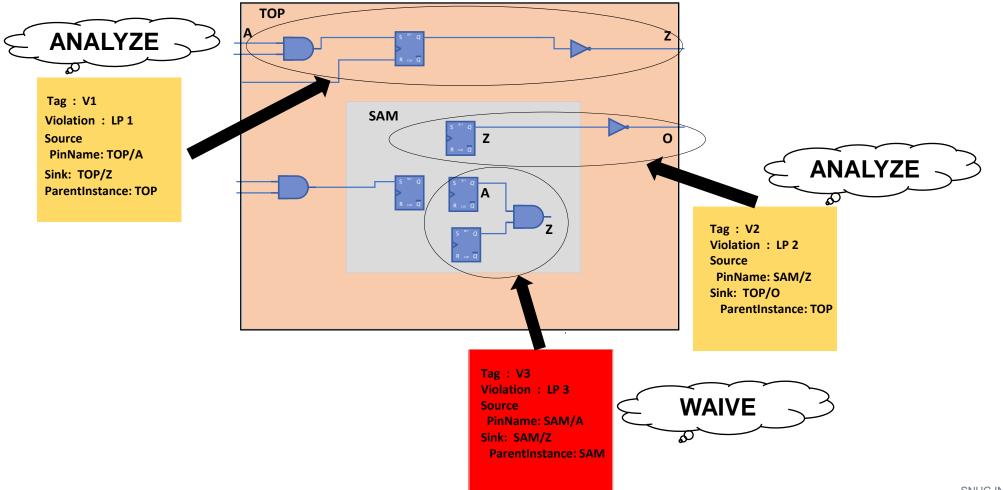

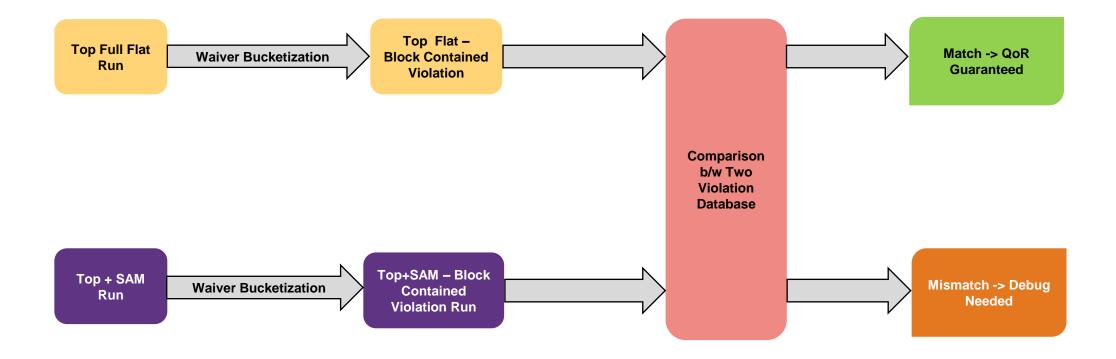

## QoR Flow

#### • Subtractive QoR flow

- Waiving pure block contained issues.

## QoR Flow (Contd.)

Paranoia checks can perform comparing with full flat run.

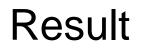

#### **Runtime Comparison**

**Memory Comparison**

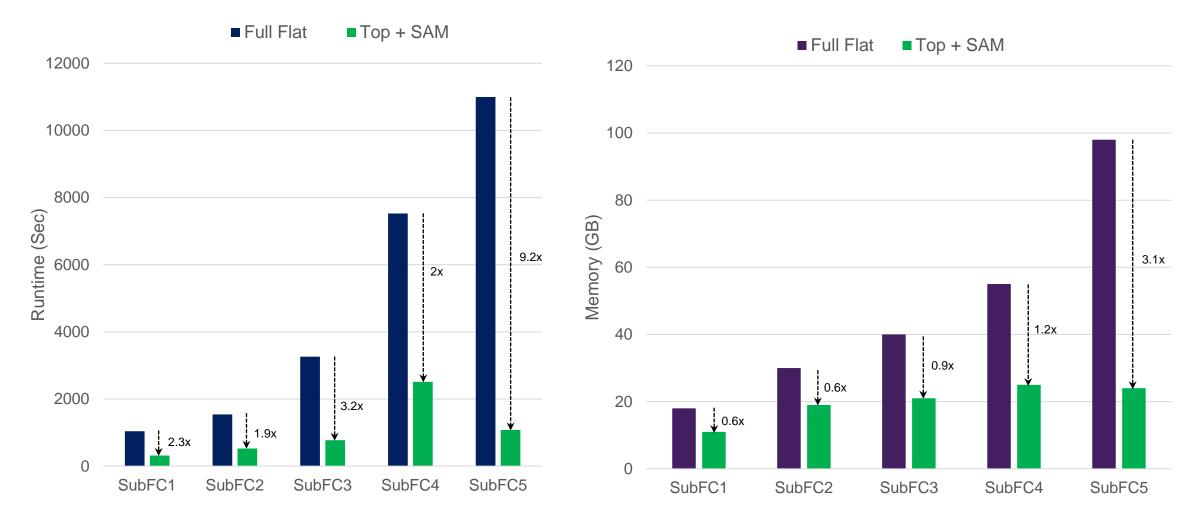

| Design     | Full Flat<br>Runtime<br>(Hrs) | Top + SAM<br>Runtime<br>(Hrs) | Benefit           | Full Flat<br>Memory<br>(GB) | Top + SAM<br>Memory<br>(GB) | Benefit           |

|------------|-------------------------------|-------------------------------|-------------------|-----------------------------|-----------------------------|-------------------|

| FC Design1 | 94.8                          | 10.1                          | <mark>9.39</mark> | 351                         | 98                          | <mark>3.58</mark> |

| FC Design2 | 114                           | 11.45                         | <mark>9.95</mark> | 412                         | 101                         | 4.07              |

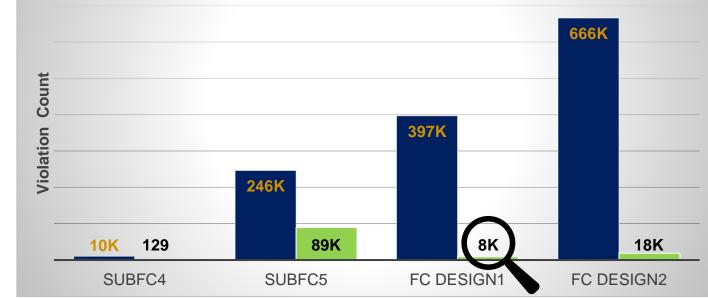

#### **Violation Comparison**

Full Flat Top + SAM

Runtime benefit : 3 to 10x

Memory resource benefit : 1.5 to 4x

Debug cycle reduced ~30% due to removal of block contained violations

#### Conclusion

- The Donut netlist model created by SAM offers both runtime improvement and resource reduction, making it most efficient static LP verification method.

- Guaranteed QoR with a shorter debug cycle accelerates the static LP convergence goals.

- Recommended methodology for all future multi-billion gates design.

- Working with vendor on-

□ On the fly identification and generation of SAM.

□ Further lighter, faster version of SAM.

# THANK YOU

Our Technology, Your Innovation™