## Taking SDC Constraints to the Next Level with Timing Constraints Manager

Dustin Peterson Robert Bosch GmBH (ME/EIS3)

# Taking SDC Constraints to the Next Level with TCM

#### 1. Problem:

Why are constraints an issue for flat timing signoff in hierarchical designs?

#### 2. Solution without TCM:

What was the custom solution for constraint promotion to top-level?

#### 3. Solution with TCM:

Implementation of TCM-based constraint promotion flow in RadarSoC

#### 4. Results:

Benefits and drawbacks of custom flow vs. TCM

#### 1. Problem Why are constraints an issue for flat timing signoff in hierarchical designs?

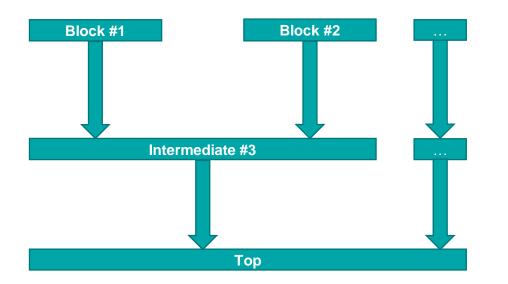

## **Timing Signoff of Hierarchical Designs**

This talk focuses on hierarchical designs, i.e. when a chip is comprised of multiple individually hardened blocks, sub blocks and macros.

- How to signoff hierarchical designs safely to reach quality for Automotive products?

- Our Vehicle: GF 22FDX-based RadarSoC<sup>12</sup>

<sup>1</sup> P. Ritter et al., "A Fully Integrated 78 GHz Automotive Radar System-an-Chip in 22nm FD-SOI CMOS," 2020 17th European Radar Conference (EuRAD), Utrecht, Netherlands, 2021, pp. 57-60, doi: 10.1109/EuRAD48048.2021.00026

<sup>2</sup> https://www.all-electronics.de/markt/globalfoundries-und-boschentwickeln-automotive-radar-technologie.html

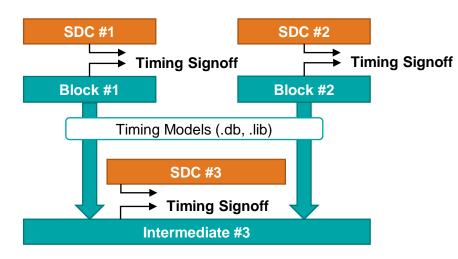

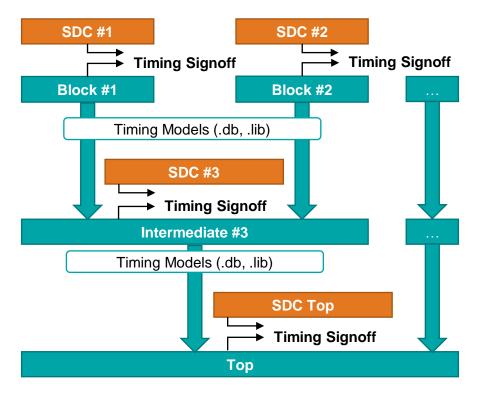

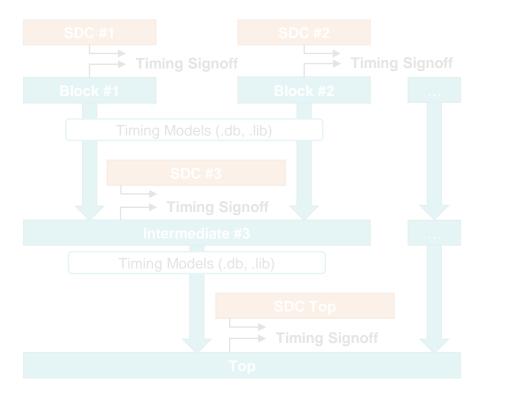

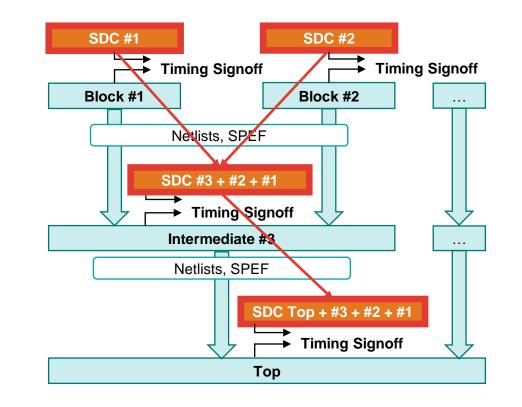

## **Hierarchical Timing Signoff**

- Each block signed off individually with block-level SDC.

- Top signoff: ETMs and top-level SDC

## **Hierarchical Timing Signoff**

- Each block signed off individually with block-level SDC.

- Top signoff: ETMs and top-level SDC

sn

## **Hierarchical Timing Signoff**

- Each block signed off individually with block-level SDC.

- Top signoff: ETMs and top-level SDC

- Benefits:

- Lower runtimes.

- Block-level constraints to be ignored mostly

- Drawbacks:

- Applicable only for coarse nodes with neglectable crosstalk impacts!

- For larger technology nodes reasonable signoff approach!

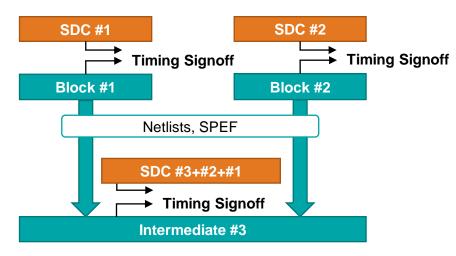

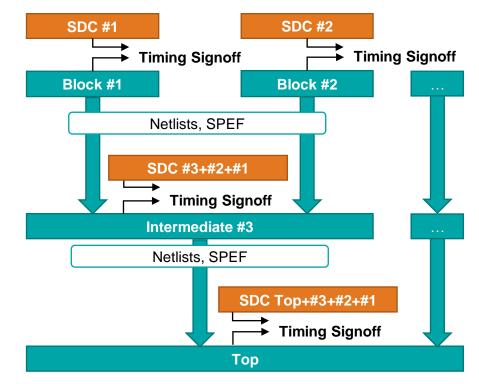

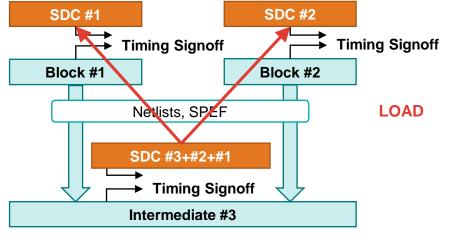

## Flat Timing Signoff

- Each block signed off individually with block-level SDC.

- Top signoff: Netlists and <u>all</u> SDCs

## Flat Timing Signoff

- Benefits:

- Most accurate signoff:

- Modeling of clock crosstalk effects on block-level reg2reg timing.

- Modeling of arrival curves from top- to block-level could also unveil noise violations.

- Drawbacks:

- Larger runtimes.

- Block-level constraints need to be promoted to top-level (clock grouping, exceptions, case settings, ...)

- Indispensable for smaller technology nodes like for our 22nm case

- Each block signed off individually with block-level SDC.

- Top signoff: Netlists and <u>all</u> SDCs

9

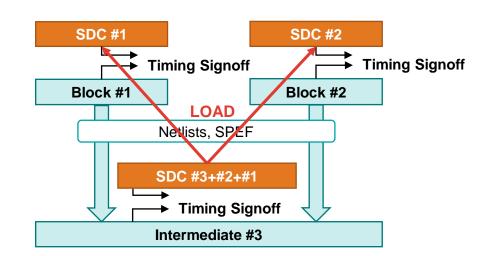

## Constraints in Hier. vs. Flat Timing Analysis

Each block is a "blackbox" so no need for block-level constraints at top-level signoff.

#### **Hierarchical STA**

We need block-level constraints for toplevel signoff – how do we achieve that?

Flat STA

# How do we take SDC constraints to the next level?

#### 2. Solution without TCM Custom solution for constraint promotion to top-level

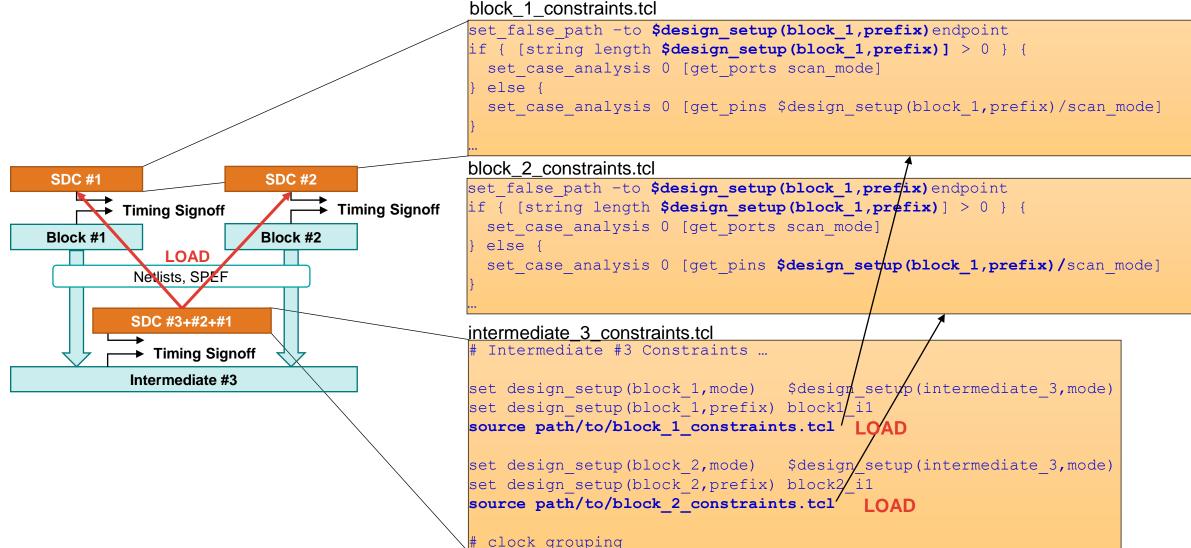

#### **Tcl-based Constraining**

snug

- One main Tcl constraints file per block.

- Constraints used for block- and top-level signoff!

- Definition of pseudo Tcl API to define:

- Instance prefix of block-level

\$design\_setup(<block>,prefix) <path/to/instance/>

- Timing mode of block-level \$design\_setup(<block>\_3,mode) <mode\_name>

- Clock mapping from block-level to top-level clocks

\$design\_setup(<block>, clock\_map) [list

<block\_level\_clock\_1> <top\_level\_clock\_1> ...

<block\_level\_clock\_n> <top\_level\_clock\_n>]

- Top-level Tcl constraints file loads block-level Tcl constraints files

## **Tcl-based Constraining**

## Pros and Cons of Tcl Constraining

- Changes can be implemented fast

- Supports full set of constraints (also non-SDC)

- High effort for integration of 3rd party IPs

- Error-proneness increases

- Wildcarding in Tcl constraints dangerous and runtime-intense

- Clock grouping needs to be redone individually on each level

- Quality of Constraints for Safety (ISO26262)

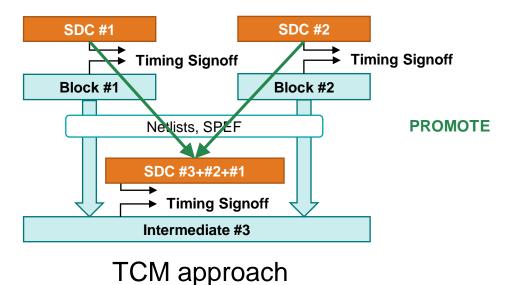

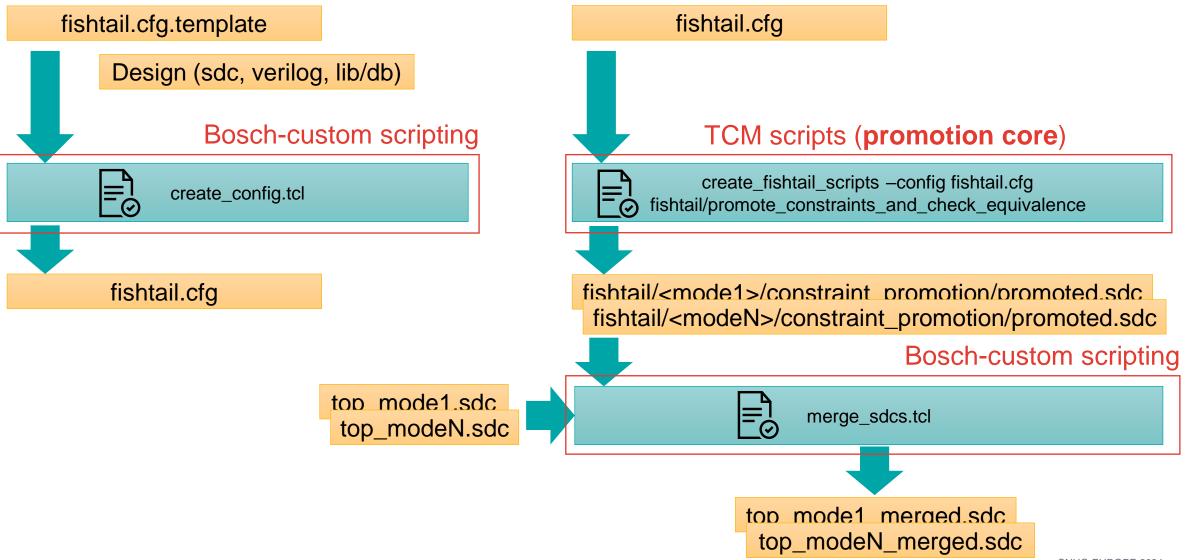

#### 3. Solution with TCM Implementation of TCM-based constraint promotion flow in RadarSoC

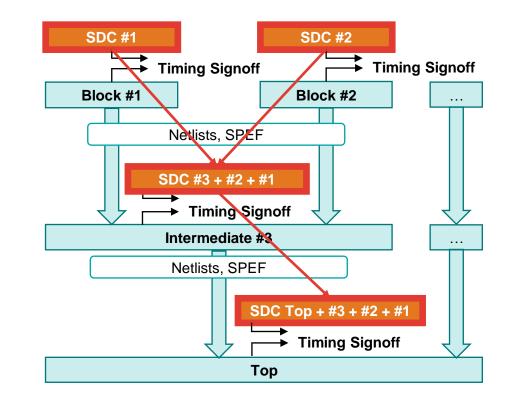

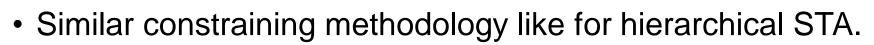

Constraining Methodology

- Block constraints are written individually without any preparation for integration.

- Intermediate- and top-level constraints are also written in the same way.

- For flat STA TCM is taking the netlists and SDCs of all blocks and promotes them to the top-level context, i.e. we end up with a merged static SDC.

Custom Tcl approach

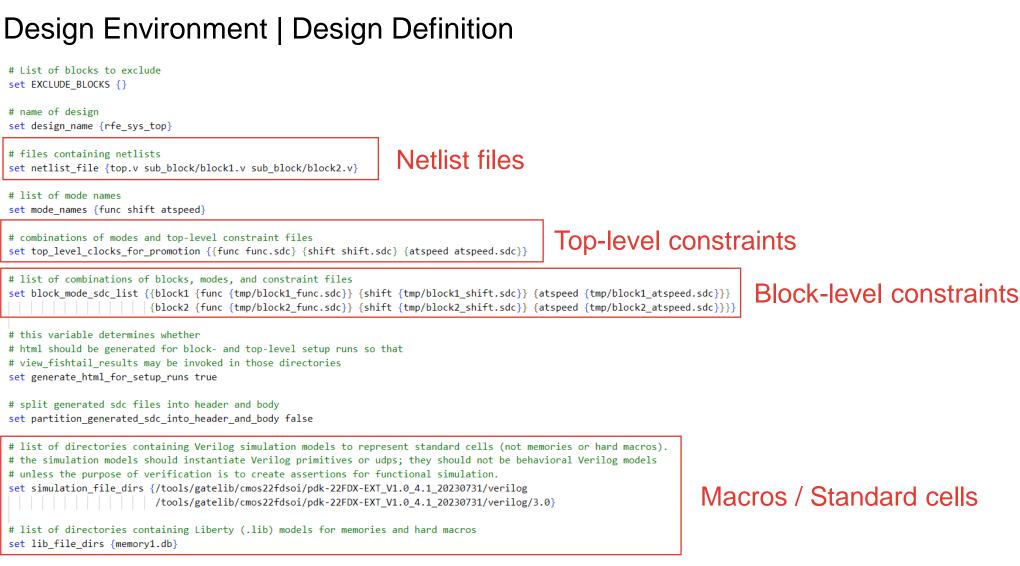

Design Environment

- Definition of designs and sub designs

- Verilog files

- Constraint modes

- Constraint files (SDC, non-SDC) per mode

- Liberty/DB files for macros and standard cells

- Configuration of promotion

- Force pushing constraints to leaf pins instead of hierarchical pins?

- What to do with block-internal clocks that are not promoting to a block's interface?

- Do you want to promote case analysis settings?

- Threshold for matching clock periods

Equivalence Check

Configuration

## **TCM Basics**

# tcl variable definition overrides

#### Design Environment | Promotion Configuration

set variable\_definitions { "## Mapping Variables" "#set case analysis sequential propagation 0; # determines whether constants propagate thru sequential "set move hier pins to leaf pins 0; "#..." "## Constraint Promotion Variables" "set clock mapping period threshold 5; "set create async clock groups 1; "set create clocks on hier pins 0; "set keep unpropagated clocks 1; "set promote case analysis 1; "set promote clock attributes 0; # when 1, clock groups and clock-to-clock false paths are "set promote clock groups 1; "set promote interface exceptions 1; # when 1, exceptions that are specified on primary input: "## Equivalence Checking Variables" "#set compare clock uncertainty 0; "#set compare internal timing 1; "#set compare io timing 1; "#set optimism threshold 0.1; "#set pessimism threshold 0.1; "set report path timing requirement 1;

# in mapping, promotion, and demotion runs, write constra

Promotion # tolerance value (as a percentage) for whether a warning Configuration # create an async clock group that specifies that clocks # when 0, if a divide-by 1 generated clock cannot be move # in promote-without-push, preserve create clock command: # when 0, block-level set case analysis commands are igna # when 0, set clock latency and set clock uncertainty cor

# when 1, clock uncertainty and clock latency are conside # when 0, during top-vs-block equivalence checking, do no # when 0, during top-vs-block equivalence checking, only # minimum optimism difference in timing requirement for ; # minimum pessimism difference in timing requirement for # compare both endpoints and paths during equivalence che

Mapping Configuration

#### SNUG EUROPE 2024 21

#### **TCM Basics**

**Promotion Flow**

- Update prefixes of objects accordingly. set\_false\_path -from

[get\_ports scan\_enable]

Set\_false\_path -through [get\_pins

path/to/instance\_1/scan\_enable]

- Remove non-applicable constraints (e.g. I/O delays)

- Promote case settings, min/max delays, data checks, ...

- Special handling of clocks, see next slide

- Check for:

- case conflicts

- clock period matches

- . . .

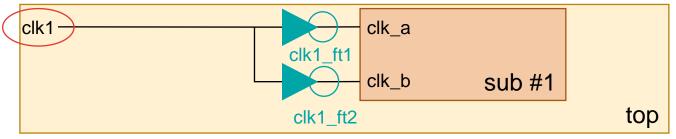

Promotion Flow | Clock handling

- Root clocks at block interfaces are replaced by generated clocks

- For each clock input, a generated clock is generated on the leaf driver:

- Please note: Clock mapping between block and top is configurable!

Promotion Flow | Clock handling

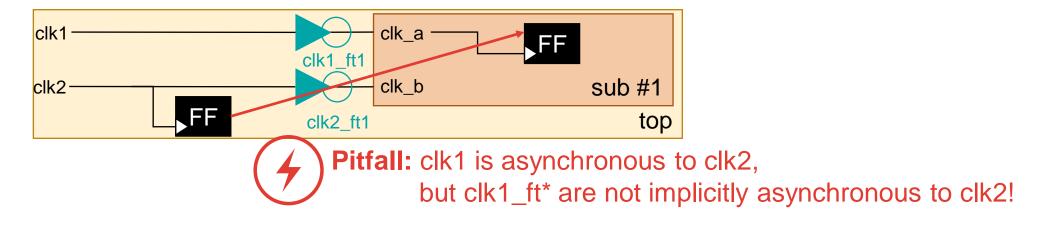

• Paths from root or block-level clocks to asynchronous block-level clocks of other blocks is not implicitly set to false:

• TCM supports runtime-intense second promotion run for further clock group investigation to put a false path also on those crossing paths. (not default)

## Flow Implementation

### **Promotion Results**

|                                                                                                     | RH7[414] ls `pwd`                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                     |                                                                                                                     |    |

|                                                                                                     | fishtail/func/constraint_promotion:                                                                                 |    |

| be used for debugging                                                                               | design.rdb design_setup_issues.html HTML Report                                                                     |    |

|                                                                                                     | promoted.sdc refocus interactive.tcl the constrain                                                                  | nt |

| Promoted                                                                                            | refocus_mem.log report_setup_issues.log* promotion                                                                  |    |

| Constraints                                                                                         | report setup issues.tcl rmodules.rpt.gz                                                                             |    |

|                                                                                                     |                                                                                                                     |    |

| # SDC file generated by FishTail Refocus                                                            | version U-2022.12-SP3                                                                                               |    |

| <pre>set_units -time ns set remove_extraneous_combinational_clock # set_case_analysis on //tr</pre> | ks 1 Promoted constraints file<br>documents origin of each<br>constraint<br>mp/mode func 0.tcl line 26 for instance |    |

| <pre>set_case_analysis \     1 \</pre>                                                              |                                                                                                                     |    |

| {                                                                                                   | }                                                                                                                   |    |

| <pre># set_case_analysis on</pre>                                                                   |                                                                                                                     |    |

| set_case_analysis \<br>0 \                                                                          | <pre>mp/mode_func_0.tcl line 38 for instance</pre>                                                                  |    |

snug

#### HTML Reports

| Design | Setup | Summary | for | rfe_ | _sys_ | top |

|--------|-------|---------|-----|------|-------|-----|

|--------|-------|---------|-----|------|-------|-----|

Design Information

Constraint Mapping

Clock Mapping

Promoted Constraints

Issues

Total Runtime: 1:23:02

Memory Usage: 42.1 gB

**HTML** Reports

| Design Setup Summary for rfe_sys_top |                                |

|--------------------------------------|--------------------------------|

| Design Information                   | Constra                        |

| Constraint Mapping                   | Mapped Constrai                |

| Clock Mapping                        | Name                           |

| Dromotod Constraints                 | Unapplied                      |

| Promoted Constraints                 | create_clock                   |

| Issues                               | create_clock (v                |

|                                      | create_generate                |

| Total Runtime: 1:23:02               | group_path<br>set_case_analys: |

|                                      | set_clock_group                |

| Memory Usage: 42.1 gB                | set_disable_tim                |

|                                      | <br>set_dont_touch             |

|                                      | set_false_path                 |

|                                      | set_false_path                 |

|                                      | set_max_delay                  |

|                                      | set_min_delay                  |

|                                      |                                |

#### **Constraint Mapping Reports**

| Name                                   | Mapped | Unmapped | Waived |

|----------------------------------------|--------|----------|--------|

| Unapplied                              | 0      | 1        | 0      |

| create_clock                           | 7      | Θ        | 0      |

| create_clock (virtual)                 | 1      | Θ        | Θ      |

| create_generated_clock                 | 21     | 0        | Θ      |

| group_path                             | 12     | 0        | 0      |

| set_case_analysis                      | 726    | 0        | Θ      |

| set_clock_groups                       | 1      | 0        | 0      |

| set_disable_timing                     | 5012   | 0        | 0      |

| set_dont_touch                         | Θ      | 403      | 0      |

| set_false_path                         | 21     | 0        | 0      |

| set_false_path (hold)                  | 3      | 0        | 0      |

| set_max_delay                          | 2      | 0        | 0      |

| set_min_delay                          | 1      | 0        | 0      |

| <u>_</u>                               | 4      | 0        | 0      |

| <pre>set_multicycle_path (setup)</pre> | 4      | 0        | 0      |

| set_sense                              | 53     | Θ        | 0      |

#### **HTML** Reports

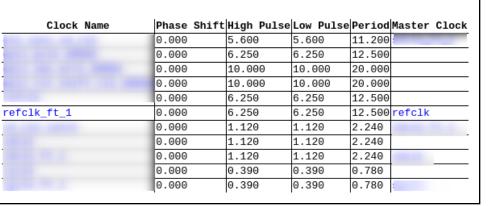

#### **Clock Mapping Reports**

Clock Report for Module rfe\_sys\_cpll

| Clock Name                        | Phase Shift | High Pulse | Low Pulse | Period | Master Clock |

|-----------------------------------|-------------|------------|-----------|--------|--------------|

| and some one offer                | 0.000       | 5.600      | 5.600     | 11.200 |              |

|                                   | 0.000       | 6.250      | 6.250     | 12.500 |              |

| AND THE OWNER OF THE OWNER        | 0.000       | 10.000     | 10.000    | 20.000 |              |

| AND THE REAL PROPERTY AND ADDRESS | 0.000       | 10.000     | 10.000    | 20.000 |              |

|                                   | 0.000       | 6.250      | 6.250     | 12.500 |              |

| refclk_ft_1                       | 0.000       | 6.250      | 6.250     | 12.500 | refclk       |

| a can see a                       | 0.000       | 1.120      | 1.120     | 2.240  |              |

|                                   | 0.000       | 1.120      | 1.120     | 2.240  | -            |

|                                   | 0.000       | 1.120      | 1.120     | 2.240  |              |

|                                   | 0.000       | 0.390      | 0.390     | 0.780  |              |

|                                   | 0.000       | 0.390      | 0.390     | 0.780  | :            |

#### Design Setup Summary for rfe\_sys\_top

Design Information

Constraint Mapping

Clock Mapping

Promoted Constraints

Issues

Total Runtime: 1:23:02

Memory Usage: 42.1 gB

#### Constraint Mapping Reports

| Name                                   | Mapped | Unmapped | Waived |

|----------------------------------------|--------|----------|--------|

| Unapplied                              | Θ      | 1        | 0      |

| create_clock                           | 7      | 0        | 0      |

| create_clock (virtual)                 | 1      | 0        | 0      |

| create_generated_clock                 | 21     | 0        | 0      |

| group_path                             | 12     | 0        | 0      |

| set_case_analysis                      | 726    | 0        | Θ      |

| set_clock_groups                       | 1      | Θ        | Θ      |

| set_disable_timing                     | 5012   | 0        | Θ      |

| set_dont_touch                         | Θ      | 403      | Θ      |

| set_false_path                         | 21     | Θ        | Θ      |

| set_false_path (hold)                  | 3      | Θ        | 0      |

| set_max_delay                          | 2      | 0        | 0      |

| set_min_delay                          | 1      | Θ        | 0      |

| <pre>set_multicycle_path (hold)</pre>  | 4      | 0        | 0      |

| <pre>set_multicycle_path (setup)</pre> | 4      | 0        | 0      |

| set_sense                              | 53     | 0        | 0      |

**HTML** Reports

#### **Clock Mapping Reports**

Clock Report for Module rfe\_sys\_cpll

Design Setup Summary for rfe\_sys\_top

Design Information

Constraint Mapping

Clock Mapping

Promoted Constraints

Issues

Total Runtime: 1:23:02

Memory Usage: 42.1 gB

#### Constraint Mapping Reports

| Mapped Constraints for modu            | ule    |          | (instan | ce         |                | )       |                                        |                             |

|----------------------------------------|--------|----------|---------|------------|----------------|---------|----------------------------------------|-----------------------------|

| Name                                   | Маррес | Unmapped | Waived  |            |                |         |                                        | Ionning Edita               |

| Jnapplied                              | Θ      | 1        | 0       |            |                |         |                                        | lapping Edito               |

| create_clock                           | 7      | 0        | 0       |            |                |         |                                        |                             |

| create_clock (virtual)                 | 1      | 0        | 0       | Clock Mapp | ing for        |         |                                        |                             |

| create_generated_clock                 | 21     | 0        | 0       |            |                |         |                                        |                             |

| group_path                             | 12     | Θ        | 0       | Apply all  | tool clock map | opings  |                                        |                             |

| set_case_analysis                      | 726    | 0        | 0       |            |                |         |                                        |                             |

| set_clock_groups                       | 1      | 0        | 0       | Reset all  | tool clock map | pings   |                                        |                             |

| set_disable_timing                     | 5012   | Θ        | Θ       |            |                |         |                                        |                             |

| set_dont_touch                         | Θ      | 403      | 0       |            |                |         |                                        |                             |

| set_false_path                         | 21     | 0        | 0       |            |                |         | Top-Level Clocks Mapped Top-level Cloc | kUser Defined Clock Mapping |

| set_false_path (hold)                  | 3      | 0        | 0       | blc_clk    | blc_clk        | clk_rfe | clk_rfe                                | ✓ blc_clk                   |

| set_max_delay                          | 2      | 0        | 0       |            |                |         |                                        | □clk_rfe                    |

| set_min_delay                          | 1      | 0        | 0       |            |                | I       | I                                      | CIK_FI6                     |

| <pre>set_multicycle_path (hold)</pre>  | 4      | Θ        | 0       |            |                |         |                                        |                             |

| <pre>set_multicycle_path (setup)</pre> | ) 4    | Θ        | 0       |            |                |         |                                        |                             |

|                                        | 53     | Θ        | 0       |            |                |         |                                        |                             |

#### HTML Issue Overview

| Setup Issues                            |                        |

|-----------------------------------------|------------------------|

| Issues                                  | Severity Message Count |

| Parser Issues                           |                        |

| Design Issues                           |                        |

| Design object does not exist. (RTL-002) | 492                    |

| Module has no definition (RTL-004)      | 32                     |

| Setup | Issues |

|-------|--------|

Issues

SDC Issues

Exception Issues

**Promotion Issues**

| RTL-004 (32 messages) |                                |

|-----------------------|--------------------------------|

| Warning: Module '     | ' has no definition. (RTL-004) |

| Warning: Module '     | ' has no definition. (RTL-004) |

| Warning: Module '     | ' has no definition. (RTL-004) |

#### **HTML Issue Overview**

| SDC Issues                                 |                        |

|--------------------------------------------|------------------------|

| SDC Issues                                 | Severity Message Count |

| SDC command could not be applied. (SDC-038 | 406                    |

| The command is not supported. (SDC-059)    | 538                    |

| Issues           |

|------------------|

|                  |

| Setup Issues     |

| SDC Issues       |

| Exception Issues |

| Promotion Issues |

| SDC-038 (405 messages)                                                                                            |          |             |

|-------------------------------------------------------------------------------------------------------------------|----------|-------------|

| Warning: SDC command 'set_dont_touch [get_lib_cells {     on line 594 of file     could not be applied. (SDC-038) | ] false' | /design.tcl |

| Warning: SDC command 'set_dont_touch [get_lib_cells {     on line 595 of file     could not be applied. (SDC-038) | ] false' | /design.tcl |

**HTML Issue Overview**

|                                   | Exception Issues                                                                                                                                                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | Exception Issues       Severity Message Court         Exception refers to many pins. Unless this exception is supported by the logic on the design, consider waiving it from verification. (SDC-010)       2 |

| Issues                            |                                                                                                                                                                                                              |

|                                   |                                                                                                                                                                                                              |

| Setup Issues                      |                                                                                                                                                                                                              |

| SDC Issues                        | SDC-010 (1 message)                                                                                                                                                                                          |

| Exception Issues Promotion Issues | Warning: Exception 'set false path -through {                                                                                                                                                                |

| FI 0110 C 1011 1 550 65           | } on line 3506' refers to 194898 pins. Unlest this exception is supported by the logic on the design, consider waiving it from verification. (SDC-010)                                                       |

## snug

## **Promotion Reports**

**HTML Issue Overview**

|                  | Promotion Issues                                                                                                                           |                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Issues           | Promotion Issues<br>Multiple top-level clocks propagate to a block-level clock. All but one of them are dropped. (REFOCUS-064)             | Severity Message Count |

|                  | The period of the top-level clock is different from the block-level clock that it is mapped to. (REFOCUS-070                               | ) 2                    |

| Setup Issues     |                                                                                                                                            |                        |

| SDC Issues       |                                                                                                                                            |                        |

| Exception Issues | REFOCUS-064 (1 message)                                                                                                                    | ۵ 🔒 🕲                  |

| Promotion Issues | Warning: Multiple top-level clocks propagate to clock ' defined on insta<br>' of block ' '. The following top-level clock<br>(REFOCUS-064) |                        |

#### 4. Results Benefits and drawbacks of custom flow vs. TCM

#### Results

- Application of TCM in the latest Bosch RadarSoC tapeout

- GlobalFoundries 22FDX technology

- ~10 million leaf cells in total (combo, sequential, memories)

- ~40 root clocks, ~100 generated clocks in TCM-generated constraints

- Multiple AMS macros with nested digital blocks (individually hardened)

- Complex 3rd party IP integration

- 3 modes @ 40 corners (120 timing scenarios to signoff)

- Constraint promotion is run automatically within AMS macro preparation and at the end of top-level synthesis subsequently.

- ~5h total promotion runtime for top-level

- ~2h total promotion runtime for largest AMS block

- ~7h worst-case runtime when fixing a constraint in an AMS sub block

- Results

- Manual Review of promoted.sdc for critical items:

- set\_max\_delay –from/-to from block was neither promoted with –through nor with –probe (non-SDC) so it would split data paths which could be wrong.

- set\_max\_transition/set\_max\_capacitance –force was ignored, but did not show up in ignored commands.

- No further major issues found.

- Validation with TCM:

- Reviewing all reported issues and promotion/mapping reports.

No severe issues found.

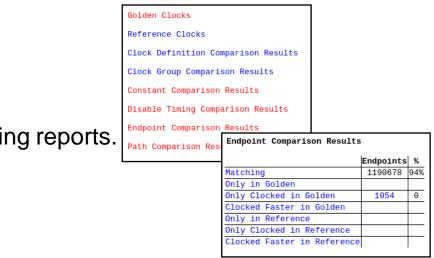

- Equivalence check reports of TCM

- Validation with GCA:

- Lots of waivable errors caused by promoted constraints (incomplete clock grouping,...)

- Pitfalls

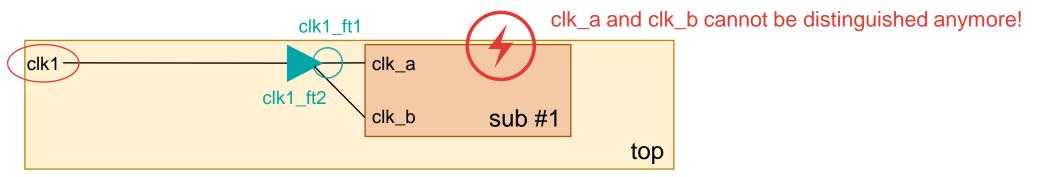

- Need for an individual driver on each clock input caused issues:

- Missing individual drivers on test clocks were found late in the flow, promotion based on synthesis netlist

was not feasible anymore as it broke the clock propagation in Primetime.

- Workaround: Doing promotion based on layout netlist as we had individual drivers there.

- Each generated clock maps to one top-level clock could be an issue to cover timing scenarios properly.

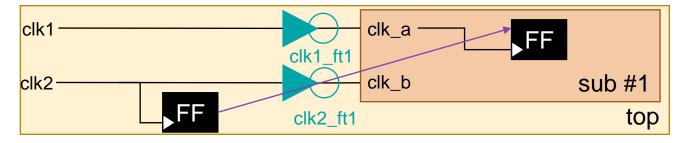

#### Pitfalls

- False timing violations because of paths between top- and block-level clocks:

- Even though clk1/clk2 are defined logically exclusive as well as clk\_a/clk\_b and clk1\_ft1/clk2\_ft1 there is for safety reasons no implicit logical exclusivity between clk1 and clk2\_ft1!

- TCM supports runtime-intense second promotion run for further clock group investigation

- Alternative: Use TCM output as baseline and add false paths / clock groups as needed

- In Radar SoC we used a mixture of both:

The second promotion run covered most of the issues, the rest was fixed by a patch script.

## **Benefits and Drawbacks**

TCM vs. Custom Tcl-based Constraining

- Benefits of TCM:

- Safer approach, generated SDCs can be reviewed.

- No impact on block-level hardening, proper work split between block-level and top-level impl.

- Enables 3rd party IP integration.

- Drawbacks of TCM:

- Design requirements (individual drivers)

- Runtime significantly higher, debugging turnaround times usually higher

- TCM is a blackbox tool, while for Tcl it's WYSIWYG (ignoring script side effects)

- set\_max\_cap/trans were just ignored...

- Benefits of Tcl-based Constraining:

- Faster turnaround times when ramping up and debugging flat constraints

- Adaption of one Tcl line in a sub block does not cause multiple runtime-intense promotion steps.

- Not necessarily causes design requirements such as explicit buffers on clock inputs

- Number of generated clocks needed is lower

- Drawbacks of Tcl-based Constraining:

- Script side effects in dynamic interpretation

- No isolated block-level constraint development

- Need for use of many wildcards.

- 3rd party IP integration difficult

## THANK YOU

YOUR INNOVATION YOUR COMMUNITY