# Multi Chip Simulation of Battery Management System with Synopsys Virtualizer Studio

Frank Poppen, Ralph Görgen, Manfred Thanner NXP Semiconductor Germany GmbH Hamburg and Munich, Germany https://www.nxp.com

### ABSTRACT

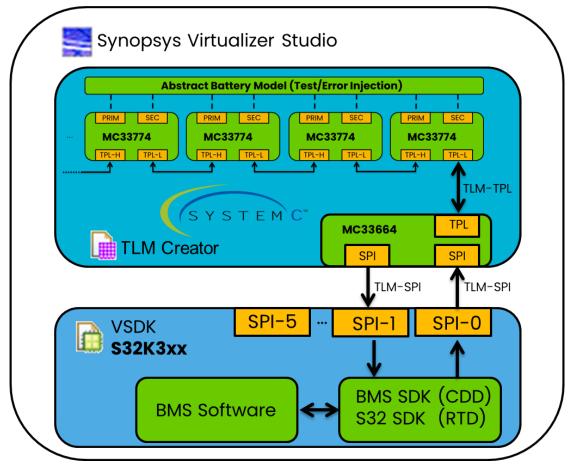

This work describes the virtual integration and usage of a complete multi-chip battery management system (BMS) in an extensible Synopsys Virtualizer Studio Development Kit (VSDK). The full system simulation (FSS) consists of a microcontroller unit (MCU) S32K3xx with serial peripheral interface (SPI), gateway (GTW) MC33664 to transport protocol link (TPL), daisy chain of battery cell controllers (BCC) MC33774 as parts of a cell monitoring unit (CMU) and simplified battery cell models. Such a FSS is an enabler for early development and evaluation of BMS complex device drivers (CDD) in a safety critical automotive open system architecture (AUTOSAR) environment. Especially the aspects of safety require the completeness of the model in all main functions. The work denotes the virtual integration process, obstacles that needed to be overcome and use of the FSS.

# **Table of Contents**

| 1. Introduction                                   | 3   |

|---------------------------------------------------|-----|

| 2. High Voltage Battery Management System         | 4   |

| 3. Full System Simulation Setup                   | 6   |

| 4. Identifying and Fixing an Issue with TLM-SPI   | 9   |

| 5. Oberserving Complete SW Stack Execution on FSS | .11 |

| 6. Conclusions and Future Work                    | .15 |

| 7. Glossary                                       | .16 |

| 8. References                                     | .17 |

# Table of Figures

| Figure 1. Shift Left with Hardware/Software Co-Design                                                            |

|------------------------------------------------------------------------------------------------------------------|

| Figure 2. Integrated into an electric car: battery pack of several modules4                                      |

| Figure 3. System Solution of a High Voltage Battery Management System5                                           |

| Figure 4. Balancing Cells for Optimal Charging and Discharging of a Battery Pack                                 |

| Figure 5. Complete Software Stack of BMS Reference Application                                                   |

| Figure 6. Full System Simulation Setup with Model of S32K3xx, MC33664 and MC337747                               |

| Figure 7. TLM Model of SPI to TPL Gateway MC336648                                                               |

| Figure 8. Instantiating BCC in VSDK and Connecting SPI-TLM Network9                                              |

| Figure 9. TPL Data Field Alignment: 64-, 80-, 96- or 112-bit Frame for One or up to Four Data Values transmitted |

| Figure 10. Description of the Continuous Select Flag                                                             |

| Figure 11. Configuring RTD and CDD Software with EB tresos and Compiling with S32 Design Studio                  |

| Figure 12. Loadnig Executable .elf File on Simulated MCU. Images Ttab of VP Config (vpcfg)12                     |

| Figure 13. Attaching Lauterbach TRACE32 Debugger to Simulated Core 0 of Simulated MCU13                          |

| Figure 14. Browsing BCC's Software Configured Hardware Registers14                                               |

| Figure 15.Vpcfg Analyses Tracing Device Enumeration Value Changes in CMU over Time15                             |

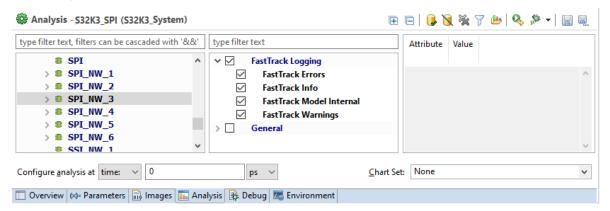

| Figure 16. Enabling FastTrack Logging on SPI Network for Versatily Messages on Interface Status.                 |

### 1. Introduction

The development of today's automotive microelectronic systems is a demanding challenge. On one hand, there is the high complexity of the systems and the high degree of interaction inside and between them. On the other hand, there are strong requirements for instance on functional safety, reliability, bill of material (BOM<sup>1</sup>), and time to market. Our work here is about a multi-chip automotive battery management system (BMS) consisting of a microcontroller unit (MCU), a gateway (GTW) and a chain of battery cell controllers (BCC) assembled in a cell monitoring unit (CMU). The BMS supervises the voltage and temperature of lithium-ion cells in automotive batteries through highly accurate measurements in a high-voltage environment including requirements such as functional safety, power consumption, and reliability. The possibility of catching fire in the battery of an electric vehicle is rated as an automotive safety integrity level (ASIL) D hazard i.e., the BMS needs to support ASIL D requirements in an ASIL D environment. Furthermore, the system's BCCs are directly mounted to the battery modules and supplied by the battery, meaning that they are permanently powered. Consequently, the ICs power consumption needs to be very low to avoid discharge of the cells. Additionally, this means that the IC cannot be powered off and restarted in case of a failure. In [1] we describe our method to close the gap between the architecture description in SysML and a BCC virtual prototype. As stated there, this allows us to use the architecture definition not only for the virtual prototype but also for a starting point for RTL design and integration as a common source of truth. At the time, the flow concentrated on structure only. In the meantime, we continued our approach by adding functional behavior towards a more complete functional BCC model. But such single component model, even though quite complex in its own internal structure, is just a small part of the system that we need to make saver and more secure. For pre silicon evaluation we had to bring together several stakeholders of different business lines for a complete virtualized BMS in one full system simulation (FSS).

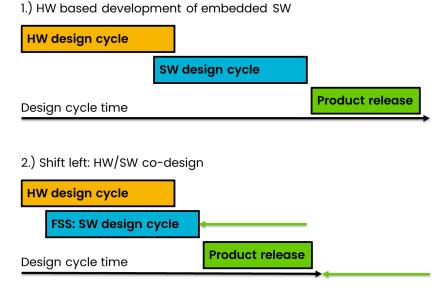

Figure 1. Shift Left with Hardware/Software Co-Design.

The FSS is part of our shift left approach (compare with Figure 1) of moving software development, testing, quality, and safety evaluation early in the development process before we expect first silicon to be available. As with any embedded software, the traditional development and evaluation of the complete software stack of a BMS is originally hardware based and requires the availability and setup

<sup>&</sup>lt;sup>1</sup> Please refer to Chapter 7. which holds an extensive Glossary.

of several physical components which are usually not available until very late in the design cycle of a new product. As soon as they are available, it becomes a time-consuming task to bring up a yet untested software on complex hardware equipment which generally does not come with visible and fully controllable behavior. Also, with physical components it becomes rather tedious to test multiple configurations as permutations of HW setups with changing number and type of components. Such setups' costs can go up very high for each system. A FSS setup on the other hand can be changed by a simple adaptation of parameters and a restart. RTL simulation is no solution for early software development known as hardware/software co-design. Its execution performance is not sufficient for live software debugging sessions. So, our objective was to create a showcase which proofs that FSS enables the required shift left in early software development.

In the following Chapter 2. an example of a high-voltage battery management system (HVBMS) is examined from a bird's eye view. The knowledge transfer on the topic in this paper is not that deep, but sufficient to be able to understand what we had to accomplish for our FSS setup documented in Chapter 3. In the process we came across an anomaly that involved the simulated SPI communication. It prevented us from communicating SPI data streams of arbitrary bit length. Chapter 4. provides the story on how NXP and Synopsys worked together to understand and fix the issue. Once the FSS was complete we were able to run a full software stack. Chapter 5. depicts what that looks like and what significant use can be drawn from it. The paper closes with our conclusions and future work in Chapter 6. followed by a glossary in Chapter 7. and references in Chapter 8.

## 2. High Voltage Battery Management System

When we talk about electric vehicles (EV), the first thing that comes to mind is an electric powered car with a battery. In general, however, scooters, motorcycles, buses, trucks, trains and even boats or airplanes can also be designed as EVs. For some applications as in trains, but also buses and trucks, it is an option to draw power from an extravehicular source like overhead contact wires. While this offers a nearly unlimited traveling range it at the same time confines the freedom of mobility severely to limited available infrastructure of electrified tracks and roads. The circumstances are inverted when we have a look at the situation where the EV carries its own source of limited power with it. We can think of fuel that is converted into electric energy by fuel cells or combustion engines as in hybrid cars. Or, as it is in the scope of this paper, we put our emphasis on in-vehicle batteries that come in as many configurations as there are use case scenarios imaginable. In other words, there is no one size fits all BMS solution. The chemistry today is typically good for battery cells at around 3 to 5 V each that are interconnected in parallel for higher currents and in series for higher voltage. This way battery packs are created as low as 14V or high voltages of 800V and more. Unfortunately, the chemistry reacts very sensitively to leaving the range of specified parameters.

Figure 2. Integrated into an electric car: battery pack of several modules.

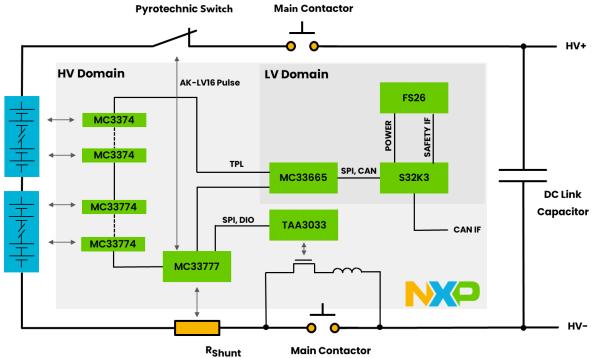

NXP offers full system solutions for HVBMS with complete chip sets. They are fully compliant to ASIL D safety requirements and the technical features include outstanding flexibility. Please refer to the following Figure 3 as one of many possible BMS setups.

Figure 3. System Solution of a High Voltage Battery Management System

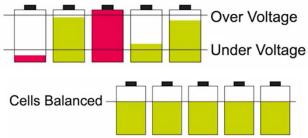

A HVBMS typically consists of three different modules. The first is a battery management unit (BMU) and its MCU which is the brain of the BMS. It makes measurement decisions, implements mechanisms of protection, and communicates with the main vehicle unit. It calculates the State of Charge (SoC) as the battery's current capacity. It is an important factor to know, how many more kilometers an EV can go before it needs to reach a charging point. Another key performance indicator (KPI) of a battery is the State of Health (SoH). It offers feedback on a battery's general health and life expectancy in comparison of the present capacity and its initial capacity after production. The second module is the cell monitoring unit (CMU) which hosts a chain of BCCs that measure cells' voltages and temperatures. It balances the cells to guarantee maximum capacity on charging the pack as otherwise the cell that first reaches over voltage (OV) would prevent further charging of other cells, while under voltage (UV) of a cell would prevent further discharge of the battery pack (refer to Figure 4).

Figure 4. Balancing Cells for Optimal Charging and Discharging of a Battery Pack.

The battery junction box (BJB) is the third module and measures the battery pack's current, the pyrotechnic switch's and contactors' high voltages and the isolation between the battery and the vehicle's chassis. If the current from the battery becomes too large due to a dramatic event, the BJB

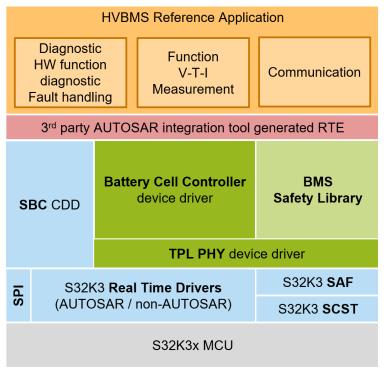

fires the pyrotechnic switch that uses a small explosive very like an airbag or seatbelt tensioner to physically cut of power supply as last resort safety measurement. A safety critical feature that should not engage unintentionally. During power on, a precharge mechanism protects the main contactor from welding together due to too high inrush currents by initially charging the car's battery attached capacitors at a limited current. BJB and CMU operate in the high voltage (HV) domain which must be isolated from the low voltage (LV) domain where the BMU resides. TPL stands for NXP's Transport Protocol Link to establish communication between high voltage BMS components. It is a communication bus that offers electrical isolation with speeds of typically 2.0 Mbps. A single BCC can handle up to 18 cells with 5 Volts in series which sums up to 90 Volts [4]. Electric cars typically rely on batteries with more cells in series going up to 400 or even 800 Volts. A daisy chain of connected BCCs that monitors such cell configurations needs to be electrically decoupled through TPL. The physical connection of communication interfaces like SPI, UART, CAN or others are not an option for such a use-case without destroying the devices. The BMU makes use of a GTW to translate between the MCU's SPI and the TPL. The MCU executes the BMU's software to control everything with real time drivers (RTD) for these communication peripherals and complex device drivers (CDD) to configure and operate the BCCs of the CMU. Figure 5 illustrates the complexity of the software stack, which is based on the AUTOSAR standard.

Figure 5. Complete Software Stack of BMS Reference Application

In the following Chapter 3. we describe how we created an FSS of the described BMS but leaving out the BJB for the moment.

## 3. Full System Simulation Setup

We started with two main parts. A Synopsys VSDK of NXP's S32K3xx MCU and a BCC architectural model as we describe in [1]. The first can execute a compiled binary of any software that would also run on the real processor. Unlike a simple instruction set simulator (ISS) it includes a complete hardware perspective with registers and peripherals (GPT, UART, CAN, SPI). It is only the MCU that executes BMS software. The BCC itself is software-free but requires its configuration registers initialized by the CDD running on the MCU. Also, the MCU must read and process measuring values

from the BCC's result registers. Our SysML generated SystemC architectural model of the BCC already implements all registers together with read and write accesses. Being SystemC, we made use of Synopsys TLM creator tool to set up a BCC TLM component. Please refer to Figure 6 to understand the full system setup which is still missing the BJB as introduced in Chapter 2., an enhancement for future work.

Figure 6. Full System Simulation Setup with Model of S32K3xx, MC33664 and MC33774.

Our original architectural model of the BCC [1] comes with an interface to a python script API. The execution of test python scripts triggers the call and creation of TLM transport methods with proper payloads for our TPL communication abstraction (TLM-TPL). This enables us to configure register values of the BCC and read out measured values from a BCC standalone SystemC test-environment executing specialized python-testcases.

Just like the physical device, the simulated S32k3xx of the VSDK comes with several SPI interfaces implemented through Synopsys proprietary TLM-SPI socket<sup>2</sup>. We required a gateway from Synopsys TLM-SPI to NXP TLM-TPL and connect the two models. This required communication gateway is not just an artefact of simulation, but a needed functionality in the physical world, too. For this purpose, NXP offers a physical GTW device named "MC33664: Isolated Network High-Speed Transceiver" [5] or "MC33665: General Purpose BMS Communication TPL Transceiver and CAN FD Gateway" [6]. which needs to become part of the FSS to make it complete. Synopsys offers a helpful tutorial lab on how to design a SPI Controller Model [2]. This tutorial was the perfect implementation start for a

<sup>&</sup>lt;sup>2</sup> tlm\_ft\_spi\_device\_socket

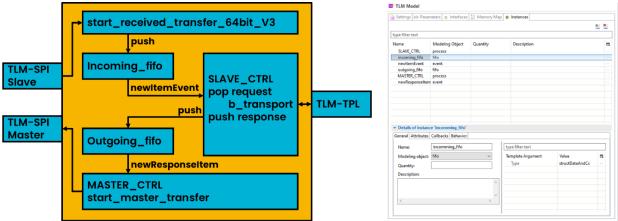

behavioral model of the required gateway as depicted in Figure 7. While the left part of the figure shows the architecture of the MC33664 model, the right part visualizes a screenshot of the TLM creator tool.

Figure 7. TLM Model of SPI to TPL Gateway MC33664

The gateway is equipped with one SPI Slave interface for request commands and one SPI Master interface for respective responses. In the TLM creator graphical usage interface (GUI) both interfaces are created in the tab "Interfaces". Other instances are added to the model in the tab "Instances". The "Details of instance ..." tab leads to callbacks for SystemC code sections to fill in the behavior of e.g. the processes "SLAVE\_CTRL" and "MASTER\_CTRL". Referring to [2] should make it quite clear how this works in all detail.

TLM creator also comes with the option of importing existing SystemC TLM Models. Being an TLM based model, it seemed obvious to use this feature to pull the architectural model of the BCC into the FSS. As stated in [1], the model is autogenerated from SysML leading to a highly structured SystemC code with many .cpp- and .h-files to import. We did not expect it to be promising to draw all of this in as one enormous chunk. Instead, we decided to achieve this in a controlled semi-manual step by step approach making use of the Synopsys Visualizer Studio python API. Whenever we were satisfied with what part of the BCC we imported last, we continued to extend the python script as outlined below for the next section of code to add. Defining approximately 300 path- and filenames by hand in the TLM creator GUI would otherwise have been a very tedious endeavor. Especially knowing that we would want to start from scratch whenever we did not like the outcome of the previous import. Outline of Synopsys Virtualizer Studio python script to setup/modify an existing TLM project:

```

# Path to BCC_REPOSITORY

bcc_repo = '<*path*>'

# Finding the correct project with name

projs = tlmcreator.get_tlm_projects()

for i in projs:

if (i.get_eclipse_project_name() == "<*proj*>"):

proj = i

bs = proj.get_build_specification()

bc = bs.get_configurations()[0]

# Adding compiler flags to the project

cxxFlags.append('<*flag_1*>')

cxxFlags.append('<*flag_2*>')

bc.set_cxx_flags(cxxFlags)

# Adding include information to the project

```

```

includePath.append(bcc_repo + '<*/path/SLMODEL/inc1*>')

...

includePath.append(bcc_repo + '<*/path/SLMODEL/inc90*>')

bc.set_include_path(includePath)

# Adding source information to the project

sources = []

sources.append(bcc_repo + '<*/path/SLMODEL/src/source1.cpp*>')

...

sources.append(bcc_repo + '<*/path/SLMODEL/src/source180.cpp*>')

bc.set_sources(sources)

proj.save()

```

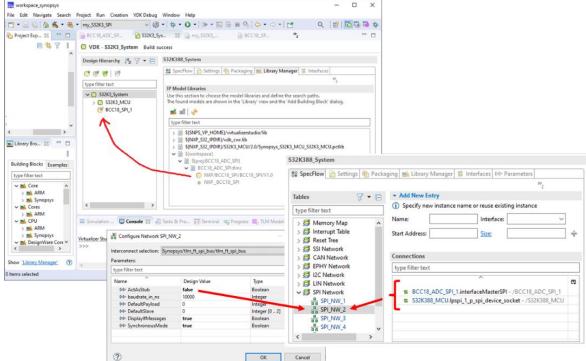

After import and compile of our GTW plus BCC chain model, the TLM component is accessible via the Synopsys Virtualizer Studio Library Manager. The new component can be dragged and dropped into the VSDK S32K3\_System as seen in Figure 8 top left. To connect the SPI sockets, one selects the SpecFlow tab and finds the proper SPI Networks (middle right). With originally only the MCU model attached to the network, it is configured as "stub" to cope with the missing communication partner. To enable transmission of TLM messages the "*ActAsStub*" flag needs to be set to false (bottom left). The FSS we created is a scalable model of a complete CMU with a configurable number of BCC instances attached as one TPL daisy chain (compare with Figure 6). TLM creator offers the concept of TLM model parameters which we used to make SPI IDs, use case selection and number of BCC instances configurable.

Figure 8. Instantiating BCC in VSDK and Connecting SPI-TLM Network.

### 4. Identifying and Fixing an Issue with TLM-SPI

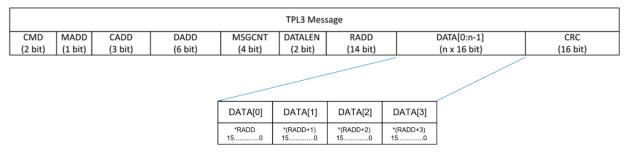

In the process of setting up the FSS as documented in Chapter 3. we came across an issue that involved the behavior of TLM-SPI communication. In the real world and the simulation, the MCU is coupled to the CMU via a GTW which serves as gateway between SPI and TPL. The bit length of a

message frame is encoded inside the data itself and can have a length of 64, 80, 96 or 112 bits (refer to Figure 9).

Figure 9. TPL Data Field Alignment: 64-, 80-, 96- or 112-bit Frame for One or up to Four Data Values transmitted.

The transmitted bits through the GTW are a one-by-one copy of a frame from SPI to TPL and vice versa. When we think of how this would be abstracted with TLM-SPI one might expect that the MCU's simulated SPI interface would create a single TLM-SPI message containing the complete frame in its payload. But a TLM-SPI message can carry only a max of 64 bit, one unsigned long long. The reader is referred to the documentation [3] for all details: "*bits - Number of valid data bits to be transmitted in the SPI payload. It can set from 0 to 64.*". The following shows the method's receive signature.

```

received_transfer_64bit_V3(

unsigned long long data,

unsigned bit_length,

bool continuous_select

)

```

Instead, the simulated MCU sends several SPI-TLM for one message frame. The software real time device driver (RTD) handling the SPI interface is configurable in such a way, that the "*SpiDataWidth*" can be set between 1 to 64 bits. Meaningful values are 8, 16, 32 or 64 bits only. We decided to configure a value of 16-bit lengths. The simulated MCU of the VSDK is modeled to such accuracy that it then creates one TLM message for every 16 bits of data. This makes good sense as the BCC's registers are 16-bit word based and we can interpret the length of a message with respect to that as 4, 5, 6, or 7 words of 16 bit. But how can the GTW model know if the 5<sup>th</sup> word is still part of the current message frame received or already a new one? We could have implemented it in the way that we interpret the "*DATALEN*" information inside the TLM messages received so far (compare with Figure 9). But that would be inappropriate for two reasons. Firstly, semantic bitwise interpretation of the data in the payload would break the level of abstraction. The reason to use TLM is exactly to abstract away such detail of communication. Secondly, this would add functionality to the GTW model that is not there in the physical device. The GTW does not interpret the data it is sending from SPI to TPL and vice versa. Consequently, the model should not do this either.

The way to go here is to make use of the flag "*continuous select*" as to be seen from the method signature above. The Synopsys Virtuallizer Studio documentation [3] gives the following information (Figure 10).

#### 2.4.3.1.19 set\_continuous\_select

#### Description

Sets the continuous select bit in the payload. This can be used to indicate if successive payloads have the Chip-Select continuously enabled or not.

0 signifies that Chip-Select signal gets de-asserted after this frame whereas 1 signifies that Chip-Select pin remains asserted after this frame.

...

#### 2.4.6.1 Examples

Continuous select feature:

To send 64 bits of data in a single job of SPI, when only 16 bits of data can be sent by the SPI device at a time (that is, in a single payload), the continuous select flag is set as follows:

```

1st Tx payload: Continuous Select = 1 (start of Tx)

```

2nd Tx payload: Continuous Select = 1

3rd Tx payload: Continuous Select = 1

4th Tx payload: Continuous Select = 0 (end of Tx)

However, to send only a single payload (of, say, 16 bits), set the continuous select flag as follows: 1st Tx payload: Continuous Select = 0 (start and end of Tx)

| 1 <sup>st</sup> TX |  |

|--------------------|--|

|                    |  |

Figure 10. Description of the Continuous Select Flag.

We implemented the GTW model to collect SPI-TLM messages to the point when the continuous select flag would become '0' before creating one single TPL-TLM payload and calling the b\_transport of the BCC model. The GTW model would issue an error if less than four or more than seven SPI-TLM messages are received. Unfortunately, this approach was not successful right away. We would see cases where the continuous select flag is faulty. The cause of this erroneous behavior could have been the RTD software running on the simulated MCU, our newly created model of the GTW or the simulated SPI of the VSDK. We started an extensive analysis to find the cause for this. Our special thanks go to the Synopsys team who took the effort to help us track down the issue to the MCU's SPI interface implementation. A fix for the S32K3xx VSDK was delivered by Synopsys within three working days and the FSS setup became operational.

### 5. Observing Complete SW Stack Execution on FSS

Looking back at Figure 5 gives some impression on the complexity of BMS software and that its development and safety validation testing is a tedious task that takes a significant amount of effort and time to complete. We are happy to report that the FSS we created in the previous chapters is accurate to the point where it can execute the complete software stack and enables a significant shift left in our product development cycle. In the following we want to document the look and feel of a simulation run and pre silicon software debugging session.

Simulation and real device operate on the same *.elf* file as executable. Meaning, that the same compiler and compiler setup is used for both cases. Our setup is based on Elektrobit (EB) Tresos as microcontroller abstraction layer (MCAL) for an AUTOSAR workflow. It generates the RTD and CDD source code configuration files of which the BMS application makes use of. The design and compilation environment for that is S32 Design Studio (S32DS) [7]. Figure 11 shows the GUIs of the two tools. The screenshot of EB Tresos symbolizes the configuration of the SPI RTD with 16 bit data

width (mentioned in previous chapter 4.), while the one of S32DS depicts the generated *.elf* file after successful compile of the project.

|                                                  |                                                                                                           | Elle Edit Search Project Window Help                                                                                                                  | •   \$ • \$ •   \$ • \$ •   \$ • \$   \$                          |                       |                            | Quick Access                       |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------|----------------------------|------------------------------------|

|                                                  |                                                                                                           |                                                                                                                                                       | • [ \$ • \$ •   \$ ] • \$ ] • ] [V5.0 ]                           |                       |                            |                                    |

|                                                  |                                                                                                           | D                                                                                                                                                     |                                                                   |                       |                            | Quick Access                       |

|                                                  |                                                                                                           | Project Explorer 23 E 10                                                                                                                              | 😤 Spi (Spi) 💠                                                     | 2 0                   | 1 Workflows 22 @ 5         | debar 📟                            |

|                                                  |                                                                                                           | <ul> <li>Spi_HalfDuplexTransfer_S32K388</li> <li>Ø someId (CORTEXM, S32K300)</li> </ul>                                                               | SpiChannel                                                        | e o 🗄                 | No workflow selected.      | 0 02 00                            |

|                                                  |                                                                                                           | <ul> <li>S BaseNXP (V4.0.0, AS4.7.0)</li> <li>S Bcc_774a (V1.0.1, AS4.7.0)</li> <li>S Bms_common (V1.0.1, AS4.7.0)</li> </ul>                         | Name 🔄 SpiChannel_0                                               |                       | No workflow select         | ed.                                |

|                                                  | CD01/eclipse/plugins/Spi_TS_T40034M4000R0/examples/EBT/S32K38                                             | <ul> <li>Bms_TPL3_SL_E2E (V1.0.1, AS4.7.0)</li> <li>Dem (V4.0.0, AS4.7.0)</li> </ul>                                                                  | General                                                           |                       |                            |                                    |

| Elle Edit Source Refactor Navigate Search Projec | t Configiolis Sun Window Belp                                                                             | > 10 Dio (V4.0.0, AS4.7.0)                                                                                                                            |                                                                   | ^                     |                            |                                    |

|                                                  | POID(4)GIMINE-0-0-19-                                                                                     | > 1 EcuC (V4.0.0, AS4.7.0)<br>> 1 Gpt (V4.0.0, AS4.7.0)                                                                                               | <b>BpiChannelld</b>                                               | € 0 v                 |                            |                                    |

| 09.71                                            | main.c 12 🕞 Makefile 🕞 project_parameters.mk<br>17 // SPECIFICATION :                                     | <ul> <li>         McI (V4.0.0, AS4.7.0)     </li> <li>         Mcu (V4.0.0, AS4.7.0)     </li> <li>         Phy_664 (V1.0.1, AS4.7.0)     </li> </ul> | SpiChannelType                                                    | <u>ي</u> ا (8 ~       |                            |                                    |

| Lou_ip_crig.d                                    | 18 // PURPOSE :<br>19 // KEYWORDS :<br>20 // AUTHOR : Frank Poppen, Balph Goergen                         | <ul> <li>Se Platform (V4.0.0, AS4.7.0)</li> <li>Se Port (V4.0.0, AS4.7.0)</li> </ul>                                                                  | SpiDataWidth (1 -> 64)                                            | 16     1              | -                          |                                    |

| Lcu_lp_Hw_Access.o                               | 21 //<br>22 // COPVRIGHT MESSAGE                                                                          | <ul> <li>Resource (V4.0.0, AS4.7.0)</li> <li>Spi (V4.0.0, AS4.7.0)</li> </ul>                                                                         | SpiDefaut@uta                                                     | 6 T                   | No description availa      | ble.                               |

| Tco"ib"ud'a                                      | 23 //<br>24 // NOP Semiconductors confidential and propriets                                              | P Spi                                                                                                                                                 | SpiEbMaxLength (1 -> 1048576)                                     | 1000                  |                            |                                    |

| Ecu_lp_irq.o                                     | 25 //                                                                                                     | > 😂 config                                                                                                                                            | a state of the state of the state                                 |                       |                            |                                    |

|                                                  | 26 // NXP Semiconductors Germany GmbH<br>27 // Beiersdorfstrasse 20.                                      | eutput                                                                                                                                                | SpitbNBuffers (1 -> 65535)                                        | iii 1                 |                            |                                    |

|                                                  | 20 // 22529 Hamburg, Genmany                                                                              | > 🦢 systemmod                                                                                                                                         | SpiTransferStart                                                  | MSB ~                 |                            |                                    |

| E Lou la VS 0 PRefa a                            | 29 //                                                                                                     | < >                                                                                                                                                   | age many states                                                   | QI MSB V              |                            |                                    |

|                                                  | 30 // All rights are reserved. Reproduction in who<br>31 // prohibited without the written consent of the | 9: Outline 12                                                                                                                                         | E SpiChannelHalfDuplexDirection                                   | HALF DUPLEX TRANSMIT  |                            |                                    |

|                                                  | 31 // prohibited without the written consent of the                                                       |                                                                                                                                                       | as spectarine survey to record                                    | HAD DOPLES TRANSMIT   |                            |                                    |

|                                                  | 33                                                                                                        | SpiMaxJob:0                                                                                                                                           |                                                                   |                       |                            |                                    |

| Lpspi_lp_lrg.o                                   | 34 #ifdefcplusplus                                                                                        | G SpiMaxSequence:0                                                                                                                                    | Default                                                           |                       |                            |                                    |

|                                                  | 35 extern <sup>CC</sup> (<br>36 Bendif                                                                    | SpiChannel     SpiChannel 0                                                                                                                           | Error Log 11 Problems View Assarch                                |                       | Properties 12              | <b>13</b> 7 9                      |

| Epspilip_vs_0_vBctg.o                            | 36 Bendif<br>37                                                                                           | SpiChannelldt0                                                                                                                                        |                                                                   | 0 0 1 2 1 1 0 1 - U 1 | Properties 2.5             |                                    |

|                                                  | 38                                                                                                        | SpiChannelType:EB                                                                                                                                     | Last 0 entries (up to 100) warnings, errors (filtered out: infos) |                       | Properties for SpiChan     | nelld                              |

|                                                  | 398 /************************************                                                                 | SpiDataWidth:16                                                                                                                                       | Message                                                           |                       |                            |                                    |

|                                                  | 48 * INCLUDE<br>41 * 1) system and project includes                                                       | SpiDefaultData:1                                                                                                                                      |                                                                   |                       | Description                | SPI Channel ID, used as            |

| C. PARAMELICIA                                   | 42 * 2) needed interfaces from external units                                                             | SpiEbMaxLength: 1000                                                                                                                                  |                                                                   |                       | Information                | parameter in SPI API<br>functions. |

| ing main.map                                     | 43 * 3) internal and external interfaces from this                                                        | SpilbNBuffers 1                                                                                                                                       |                                                                   |                       | Problems                   | an account.                        |

|                                                  | 44 ************************************                                                                   | SpillransferStart:MSB                                                                                                                                 |                                                                   |                       | PostBuildVariantConditions |                                    |

|                                                  | 45 #include "Ncu.h"<br>46 #include "Spi.h"                                                                | SpiChannelHalfDuplexDire                                                                                                                              |                                                                   |                       |                            |                                    |

|                                                  | 47 #include "Platform.h"                                                                                  | SpiChannelEcucPartitionRe                                                                                                                             |                                                                   |                       | Comments                   |                                    |

| mcu_bem_wwwppend                                 | 48 #include "Port.h"                                                                                      | SpiChannel 1                                                                                                                                          |                                                                   |                       | CustomAttributes           |                                    |

| Mcu_Dem_Wrapper.o                                | 49 /*                                                                                                     | < >>                                                                                                                                                  | <                                                                 | >                     |                            |                                    |

| Mcu_lpw.d                                        | 50 #include "COD Phy 664.h"                                                                               | Configuration: Spi, Module: Spi, TS, T40D34M400R                                                                                                      | 0. Project: Spi HalfDuplexTransfer S32K388                        |                       |                            |                                    |

| Mcu_lpw.o                                        | C C C C C C C C C C C C C C C C C C C                                                                     |                                                                                                                                                       |                                                                   |                       |                            |                                    |

| Mcu_VS_0_PBcfg.d                                 |                                                                                                           | and a second second                                                                                                                                   |                                                                   |                       |                            |                                    |

|                                                  | Problems 🔄 Tasks 📮 Console 🔯 🥅 Properties                                                                 | * • • • <u>M</u>                                                                                                                                      |                                                                   |                       |                            |                                    |

|                                                  | T Build Console [SW32K388_RTD_4.4_R21-11_4.0.0_CD01]                                                      |                                                                                                                                                       |                                                                   |                       |                            |                                    |

| Mcu.o ct.                                        | /nxp/s32ds.3.5/s32ds/build_tools/gcc_v10.2/gcc-10.2-                                                      |                                                                                                                                                       |                                                                   |                       |                            |                                    |

|                                                  | /nxp/s32ds.3.5/s32ds/build_tools/gcc_v10.2/gcc-10.2-                                                      | arm32-eabi/bin//lib/gcc/arm-none-eab                                                                                                                  | 1/10.2.0////arm-none-ei                                           |                       |                            |                                    |

| Mpu_M7_lp_Cfg.o                                  | :51:15 Build Finished. 0 errors, 0 warnings. (took 5                                                      | s (920ms)                                                                                                                                             |                                                                   |                       |                            |                                    |

|                                                  | servers owned renamed. a errors, a mernings. (cook 5                                                      |                                                                                                                                                       |                                                                   |                       |                            |                                    |

| Mpu_M7_lp.o                                      |                                                                                                           |                                                                                                                                                       | ~                                                                 |                       |                            |                                    |

| < > <                                            |                                                                                                           |                                                                                                                                                       | >                                                                 |                       |                            |                                    |

Figure 11. Configuring RTD and CDD Software with EB tresos and Compiling with S32 Design Studio

Synopsys Virtualizer Studio makes use of a VP configuration concept that comes in the form of vpcfgfiles. Selecting the "*Images*" tab gives the option to go for the above compiled executable for a simulation run.

| 🗟 S32K3_SPI.vpcfg 🛛 🕅                |                 |                           |        |               | - 0   |

|--------------------------------------|-----------------|---------------------------|--------|---------------|-------|

| Images - S32K3_SPI (S32K3_System)    |                 | 🔕 🎣 🖗 😓   🕀 🕞   🍪 🎘 🕶   🔚 |        |               |       |

| type filter text, filters can be cas | caded with '&&' |                           |        |               |       |

| Parameter                            | File            |                           | Offset | Load Type     | Ad. ^ |

| (x)= image_pa                        | th              |                           |        |               |       |

| V # CPU_SS                           |                 |                           |        |               |       |

| ✓ ♦ ImageInfo                        |                 |                           |        |               | 1     |

| ✓ (×)= initial_image                 |                 |                           |        |               |       |

| aid                                  | /out/main.elf   |                           | 0x0    | Image+Symbols |       |

| ✓ # Security_Device                  | _GPRs           |                           |        |               |       |

| ✓ # HSE_B                            |                 |                           |        |               |       |

| ✓ # HSE_CM7_                         | 0               |                           |        |               |       |

| · · A Impacinfe                      |                 |                           |        |               | ~     |

| <                                    |                 |                           |        |               | >     |

Figure 12. Loading Executable .elf File on Simulated MCU. Images Ttab of VP Config (vpcfg).

The simulation starts with a click on the play button and stops right before the first processor command executes. This halt is different from that one of a physical processor. A CPU can be stopped by a debugger, but the environment cannot. In a real hardware setup, the debugger would halt but GTW, BCC and all the world's physics around it would still be running. When the simulation stops, the simulated time itself stops. The concept of time itself halts.

A debugger can attach to the simulated MCU, or rather to any of the four cores that it provides. In our case we connect the Lauterbach TRACE32 debugger to core 0 of the simulated K3xx processor as shown in Figure 13 top part. Here we can apply break points or do anything else that debugging allows us to do, step through the code, add watchpoints, etc. (bottom part of Figure 13).

| nch Simulation using Executable<br>ach from Simulation<br>tart Simulation<br>ume Simulation<br>nfigure Analysis<br>play Charts<br>w Parameters | F8<br>Ctrl+Shift+A                                                                               | ny_S32K3_SPI.vpcfg 🛛 🔀<br>Images<br>e filter text, filters can be cascaded with                                                                          |                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tart Simulation<br>ume Simulation<br>nfigure Analysis<br>play Charts                                                                           |                                                                                                  | Images                                                                                                                                                   |                                                                                                                                                                                                                        |

| ume Simulation<br>nfigure Analysis<br>play Charts                                                                                              |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

| nfigure Analysis<br>play Charts                                                                                                                |                                                                                                  | e filter text filters can be cascaded with                                                                                                               |                                                                                                                                                                                                                        |

| play Charts                                                                                                                                    | Ctrl+Shift+A                                                                                     | e filter text, filters can be caseaded with                                                                                                              | '8x8x'                                                                                                                                                                                                                 |

|                                                                                                                                                |                                                                                                  | rameter                                                                                                                                                  | File                                                                                                                                                                                                                   |

| w Parameters                                                                                                                                   | Ctrl+Shift+D                                                                                     | # S32K3_System                                                                                                                                           |                                                                                                                                                                                                                        |

|                                                                                                                                                | Ctrl+Shift+P                                                                                     | ✓ # S32K3_MCU                                                                                                                                            |                                                                                                                                                                                                                        |

| nch Source Code Debugger                                                                                                                       |                                                                                                  | ✓ # Periphs                                                                                                                                              |                                                                                                                                                                                                                        |

|                                                                                                                                                |                                                                                                  | ✓ # VP9D                                                                                                                                                 |                                                                                                                                                                                                                        |

| p Simulation                                                                                                                                   | Ctrl+F2                                                                                          | v                                                                                                                                                        |                                                                                                                                                                                                                        |

| Simulation                                                                                                                                     |                                                                                                  | -1                                                                                                                                                       |                                                                                                                                                                                                                        |

| ar Debug Session State                                                                                                                         |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

| en Simulation Results                                                                                                                          |                                                                                                  | (x)= image_out                                                                                                                                           |                                                                                                                                                                                                                        |

|                                                                                                                                                |                                                                                                  | (×)= image_path                                                                                                                                          |                                                                                                                                                                                                                        |

| -                                                                                                                                              |                                                                                                  | ✓ # CPU_SS                                                                                                                                               |                                                                                                                                                                                                                        |

| are coverage neport                                                                                                                            |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

| p into Source Code                                                                                                                             |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

| Create Checkpoint                                                                                                                              |                                                                                                  | _                                                                                                                                                        |                                                                                                                                                                                                                        |

| tore Checkpoint                                                                                                                                |                                                                                                  | ✓ # HSE_B                                                                                                                                                |                                                                                                                                                                                                                        |

| ·                                                                                                                                              |                                                                                                  | 1105 OH7 0                                                                                                                                               |                                                                                                                                                                                                                        |

|                                                                                                                                                |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

| Systems                                                                                                                                        | >                                                                                                |                                                                                                                                                          |                                                                                                                                                                                                                        |

|                                                                                                                                                |                                                                                                  |                                                                                                                                                          | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                |

|                                                                                                                                                |                                                                                                  |                                                                                                                                                          | Debug S32K3_System.S32K3_MCU.CPU_SS.CLUSTER_1                                                                                                                                                                          |

|                                                                                                                                                |                                                                                                  | winIDEA >                                                                                                                                                | Debug S32K3_System.S32K3_MCU.CPU_SS.CLUSTER_2                                                                                                                                                                          |

|                                                                                                                                                |                                                                                                  | (x)= EEPROM_Image                                                                                                                                        | Debug S32K3_System.S32K3_MCU.CPU_SS.CLUSTER_3                                                                                                                                                                          |

|                                                                                                                                                |                                                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                        |

|                                                                                                                                                |                                                                                                  | (x)= SecureRegister_0_Imag                                                                                                                               | Debug S32K3_System.S32K3_MCU.Security_Device_GPRs.HSE_B.HSE_CM7_0                                                                                                                                                      |

|                                                                                                                                                |                                                                                                  | (×)= SecureRegister_0_Imag<br>(×)= SecureRegister_1_Imag<br>(×)= SecureRegister_2_Imag                                                                   | Standalone Start-Un                                                                                                                                                                                                    |

| a<br>a<br>a<br>a<br>t                                                                                                                          | n Simulation Results<br>iage Search Paths for Results<br>ite Coverage Report<br>into Source Code | r Debug Session State n Simulation Results lage Search Paths for Results tet Coverage Report into Source Code tet Checkpoint ore Checkpoint hth Debugger | r Debug Session State<br>n Simulation Results<br>lage Search Paths for Results<br>tet Coverage Report<br>into Source Code<br>into Source Code<br>ite Checkpoint<br>ore Checkpoint<br>ch Debugger<br>Systems<br>Systems |

Figure 13. Attaching Lauterbach TRACE32 Debugger to Simulated Core 0 of Simulated MCU.

Additionally, a virtual platform gives full visibility to the state of the simulated HW. Figure 14 and Figure 15 depict the introspection potential that gives us full observability and traceability of all BCC's configuration registers content. The use of Synopsys proprietary SystemC Modeling Library (SCML) in the model is required to have this feature available in Synopsys Virtualizer Studio. Our model generation flow of [1] automatically makes use of the library to instantiate all model's registers and bitfields. SCML source code is available and SCML based models can run standalone without Synopsys tools. Still, we consider this proprietary dependency a drawback. SCML is not an open standard, and we currently are evaluating other options that help us to keep single vendor dependencies at a minimum.

The first step in the startup of a BMS with several BCC devices in a TPL daisy chain (CMU) is enumeration. After power on, all BCC's system communication configuration register's bitfield device address (DADD) contains the value zero. Such an unconfigured device acts on any message that it receives, independently of the DADD in a TPL message. Firstly, the device must be awakened, though. Any activity on the TPL bus does this e.g., a NOP. A second message during initialization of the BMS software stack is a TPL write command to the SYS\_COM register address (RADD) with the proper enumeration value. After enumeration it will only respond to such messages that match with its configured DADD. Otherwise, the message is sent further down the chain. The following pseudo code

```

gives the idea off this.

```

```

for devNum=1 to 5 do (

nopTPL(DADD=0);

writeTPL(DADD=0, RADD=0x0001, val=devNum);

devNumCheck=readTPL(DADD=devNum, RADD=0x0001);

if devNumCheck == devNum -> OK

else NOK

)

```

The proper initialization is directly observable in Synopsys Virtualizer Studio as shown in Figure 14. Just to point out one of the many features, the tool's Analysis enables a timely tracing of values. In Figure 15 one can nicely see how enumeration ripples down the TPL chain.

| odules filter, * for wild cards on full p | ath members filter                                                |       |      |                                         |

|-------------------------------------------|-------------------------------------------------------------------|-------|------|-----------------------------------------|

| 2K3_System/BCC18_SPI_1/bcc18_dc/          |                                                                   |       |      |                                         |

|                                           | ^ Item                                                            | Start | End  | Value                                   |

|                                           |                                                                   | Start | LIIU | value                                   |

| >                                         | m_System_Control_Registers                                        | -     | -    | 0x0000                                  |

|                                           | - m_SYS_CFG_CRC                                                   | -     | -    |                                         |

|                                           | m_SYS_COM_CFG m_SYS_COM_CFG_DADD                                  | -     | -    | 0x0202<br>0x2                           |

|                                           |                                                                   | -     | -    | 0x2                                     |

| >                                         | m_SYS_COM_CFG_CADD<br>m_SYS_COM_CFG_BUSFW                         | -     | -    | 0x0                                     |

|                                           | m_SYS_COM_CFG_NUMNODES                                            | -     | -    | 0x0                                     |

| >                                         | > - m_SYS_COM_TO_CFG                                              | -     | -    | 0x001e                                  |

| >                                         | > m_SYS_COM_IO_CFG                                                | -     | -    | 0x001e                                  |

|                                           | > m_SYS_CYC_WAKEUP_CFG                                            | -     | -    | 0x1400                                  |

|                                           | > - m_SYS_TPL_CFG                                                 | -     | -    | 0x0000                                  |

|                                           | > - m_SYS_CYC_MODE_CFG                                            | -     | -    | 0x0010                                  |

| system_ctrl                               | > m_SYS_CLK_SYNC_CTRL                                             | -     | -    | 0x0000                                  |

| top_dft                                   | > m_SYS_DBG_CTRL                                                  | -     | -    | 0x0000                                  |

| ✓ ■ bcc_1                                 | > m_SYS_VERSION                                                   | -     | -    | 0x0000                                  |

| 🗸 🔳 impl                                  | > m_SYS_UID_LOW                                                   | -     | -    | 0x0000                                  |

|                                           | > m_SYS_UID_MID                                                   | -     | -    | 0x0000                                  |

|                                           | > m_SYS_UID_HIGH                                                  | -     | -    | 0x0000                                  |

|                                           | > m_SYS_PROD_VER                                                  | -     | -    | 0x0000                                  |

| > •                                       | > m_SYS_SYNC_CFG                                                  | -     | -    | 0x0100                                  |

|                                           | > m_srs_sric_cro                                                  | -     | -    | 0x0000                                  |

| > • •                                     | > m_SYS_DLY_L                                                     | -     | -    | 0x0000                                  |

|                                           | > m_SYS_DLY_H                                                     | -     | -    | 0x0000                                  |

| •                                         | > m_SYS_SYNC_CTRL                                                 | -     | -    | 0x0000                                  |

| •                                         | > m_SYS_R2R_MEAS                                                  | -     | -    | 0x0000                                  |

|                                           | > m_SYS_SYNC_DEBUG0                                               | -     | -    | 0x0000                                  |

| > •                                       | > - m_SYS_SYNC_DEBUG1                                             | -     | -    | 0x0000                                  |

| > •                                       | or reg_bus_slv_pi                                                 | -     | -    | <n a=""></n>                            |

| • ———— {                                  | cik_pi                                                            | -     | -    | <n a=""></n>                            |

| > 0                                       | <pre>&gt; init_ack_pi</pre>                                       | -     | -    | 0x00000000                              |

| > 🗉 🔤                                     | mcu_if_select_pi                                                  |       | -    | 020000000000000000000000000000000000000 |

| • • • • • • • • • • • • • • • • • • •     | por_pi                                                            |       | _    | 0x00000000                              |

|                                           | <pre>poi_pi prim_meas_rdy_pi</pre>                                | -     | -    | 0x00000000                              |

|                                           | <pre>&gt; sleep_ack_pi</pre>                                      | -     | -    | 0x00000000                              |