Comprehensive IP Verification using Hybrid Way (simulation and formal) : User Experience

Nikhil Tambekar, Verification Specialist Nokia Solutions and Networks Oy, Finland

2

### Agenda

- Introduction

- IP verification requirements

- IP verification challenges and risks

- Proposed partitioning

- VC Formal APPs

- Regression management

- Traceability using VPlanner

- Results

- Suggestions for enhancements

- Conclusion

### Introduction, IP Verification Challenges

### SNUG EUROPE 2024

### Introduction

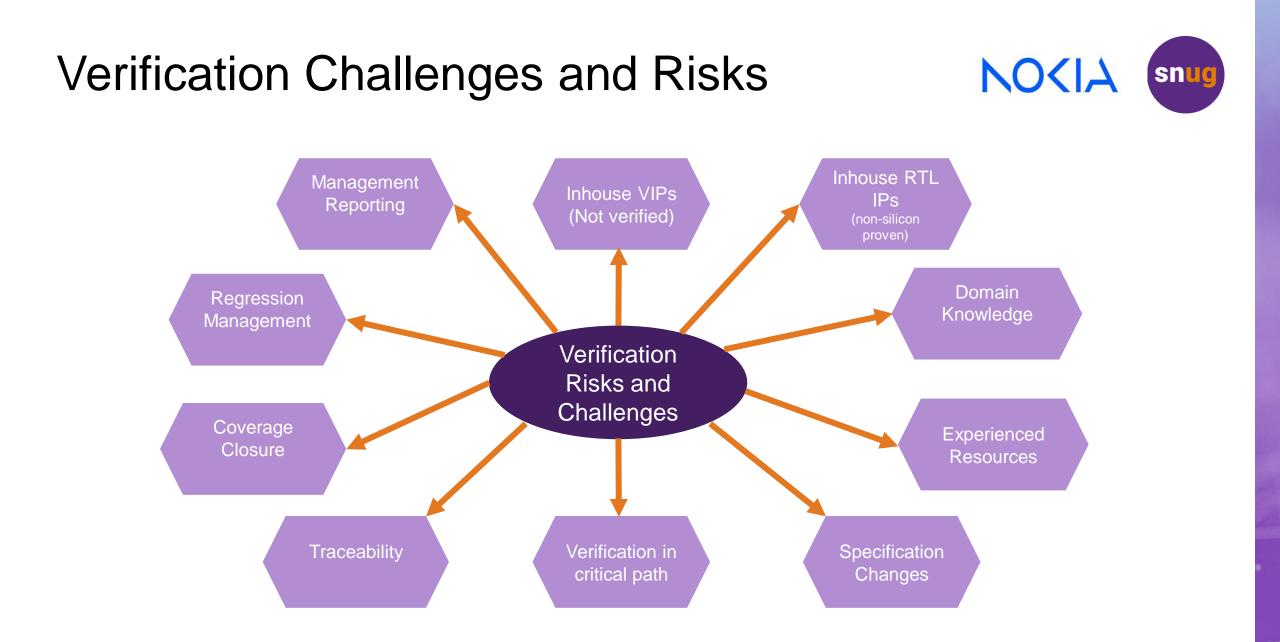

- Increased Complexity of SOCs

- Verification Challenges

- Configurable IPs

- First pass silicon and Time to market

- Simulation based verification methodology is matured

- Time to explore Formal for exhaustive verification

Combination of Formal Verification and Simulation improves quality

### **IP** Verification Requirements

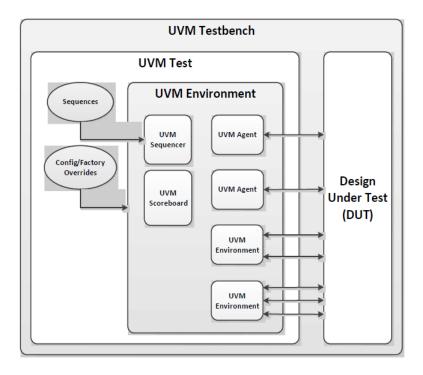

Testbench reusability and maintainability All functional features verified Use case or System Scenario verification (Domain Specific) Crosses of functionality with configurations Micro-architecture and interface protocol checking Code and Functional Coverage should be 100% achieved Traceability between feature requirements to coverage

Reference: Accelera UVM User guide 1.2

6

# **Proposed Solution**

### **Proposed Solution**

Divide-and-Conquer

Formal Techniques for micro-architecture verification

Simulations for use-case and system verification

Execution Manager based regression

YAML config + templates = Regression configurations

Jenkins CI for automation

Reporting

- VPlanner for test plan development

- Requirement to coverage mapping

- Single document for status reporting and tracking

Coverage Signoff

- VPlanner and regression result back annotation

- Merging simulation and formal coverages

- Define organization specific coverage metric

8

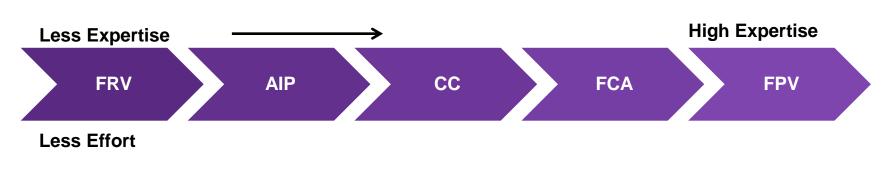

## Formal Verification Made Easy

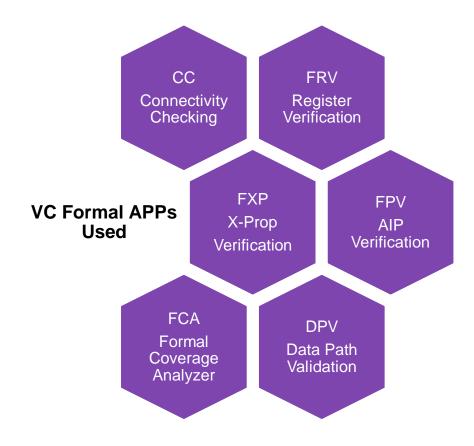

VC Formal APP Based Verification

• CC

- Top Level connectivity check

• FRV

- Register field attributes check

• FXP

- Catches X Prop issues at RTL level

- FPV-AIP

- AMBA Assertion IPs (AXI4, AXI stream, AXI4\_lite)

- Data Path Validation

- Mathematical blocks, C/C++ reference models

- Formal Coverage Analyzer

- Improves Coverage closure with auto exclusions

9

### **Benefits of Formal Verification APPs**

- Exhaustive verification using formal techniques

- Easy and fast VC Formal APP setup

- Can be used without expert level formal verification knowledge

- No dependency on testbench

- Speed up the setup using automation

- Easy failure analysis using counter example

- Used for small RTL blocks

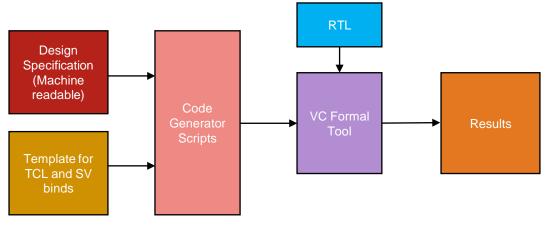

Automation setup for VC Formal Run

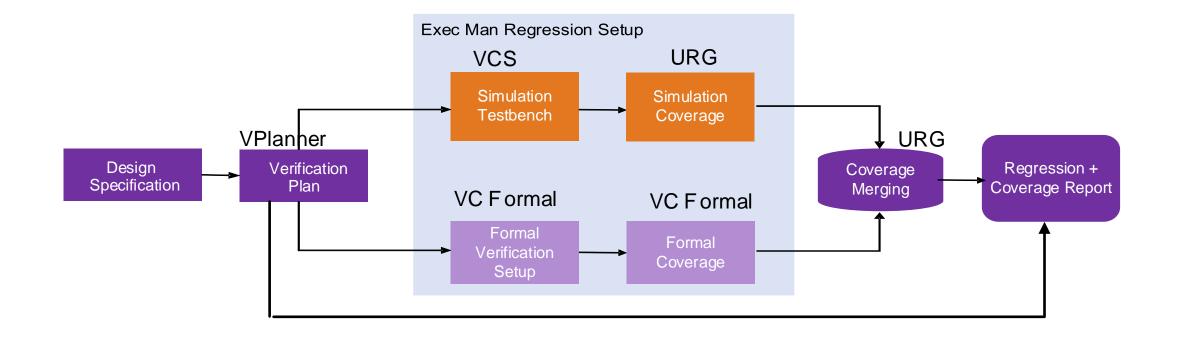

### **Verification Setup**

- Identify features for simulation and formal in the plan

- Reuse compilation: VCS and VC Formal

- Merge simulation and formal Coverage

- V Planner for back-annotation of results

- Unified Coverage report for analysis

### Regression management and Traceability

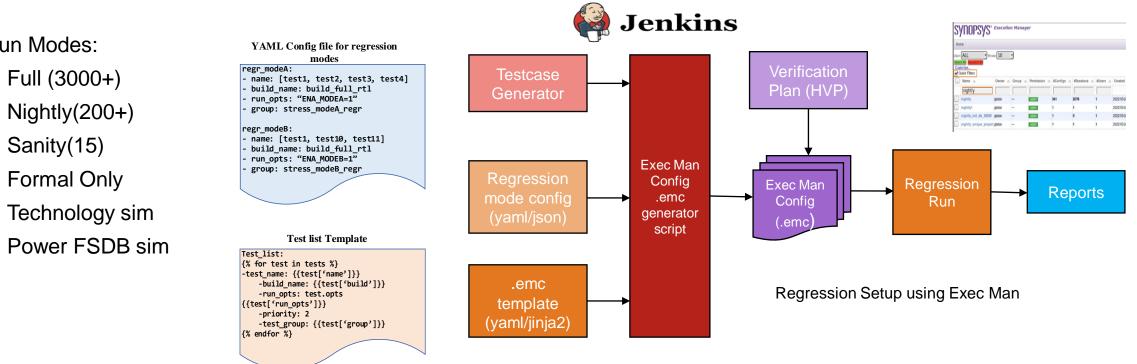

### **Regression Setup Automation**

- Automation of regression setup using Jenkins ٠

- YAML based regression modes •

Run Modes:

Full (3000+)

Sanity(15)

•

Exec man does Coverage merging, HVP ٠ annotation

- snug

- Enabled Simulation and formal builds

- Sequential VC Formal run using Jenkins Pipeline

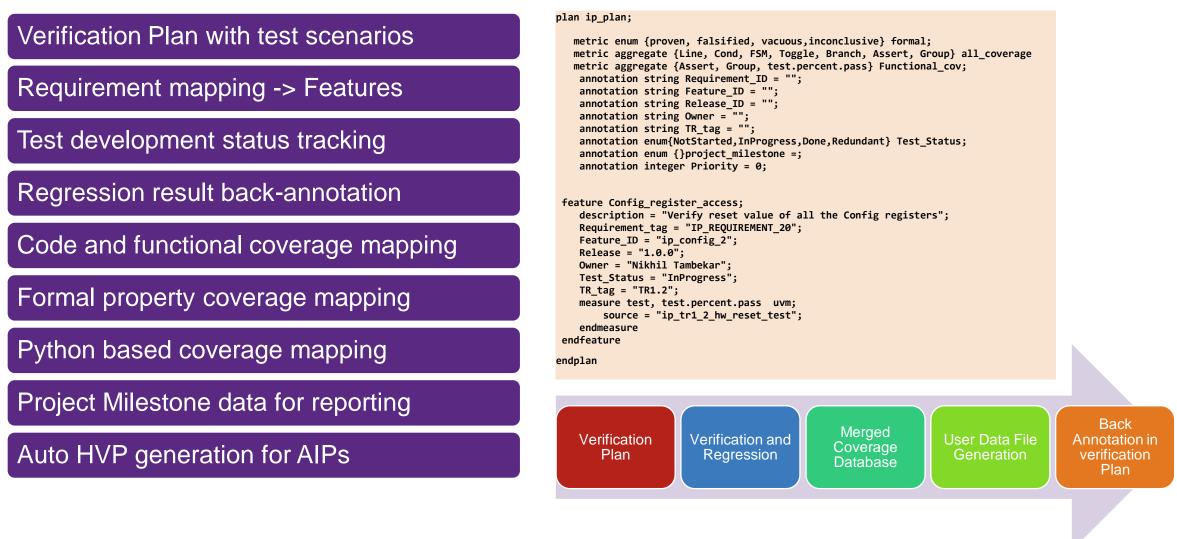

### Verification Planner for traceability

NOCIA snug

Requirement to coverage completion

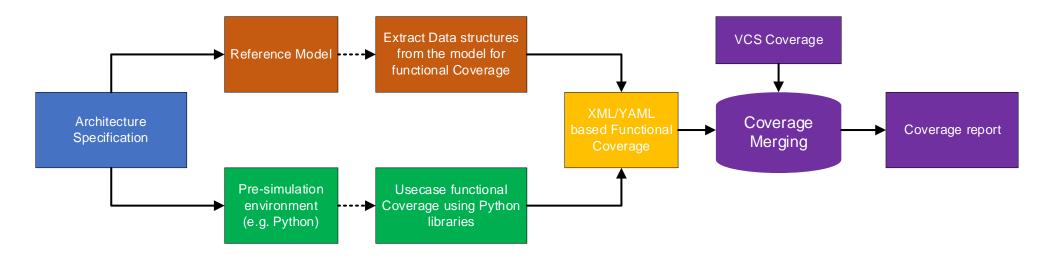

### Functional Coverage outside SV

- Use case scenario coverage is important for completeness

- Some features are difficult to extract in IP level testbench

- E.g. Computation graphs, end to end usecase scenarios etc

- Coverage extraction outside the System Verilog testbench

- Use reference model for coverage data structure generation

- Python based cover groups from test generation environment

- Map the usecase coverage in VPlanner

### **Results and Conclusion**

### Results

- Critical bugs found using formal verification

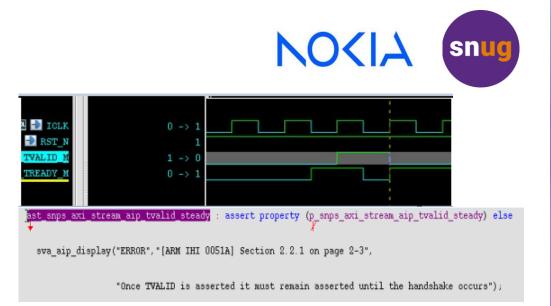

- [AIP] AXI stream protocol bugs (tvalid-tready handshake, access errors)

- [FPV] Architecture Spec vs RTL Endianness issues

- [FPV] Architecture Spec vs RTL mismatch in decoding logic

- Formal techniques improve IP quality and early bug finding

- Single document (HVP Plan) for status reporting

- · Saved bandwidth used for domain specific Usecase verification and debug

- Faster coverage closure and frame-work scalable for other IPs

- Traceability achieved for verification completion signoff

- Significant Efficiency improvement with automation

Verification team achieved all the project milestones on time with high quality deliverables

Handshake bug using AIP AXI stream APP

### Future Improvements

- Encourage third party coverage database merging

- More support is needed for UCIS or user-friendly APIs for coverage database manipulation

- Open-source libraries for verification

- Improvements in Execution Manager tool

- Support for running only failing tests

- Improving coverage merging efficiency

- More exhaustive testing for the VCS and VC Formal coverage merging and interoperability

- VC Formal elaboration logs are not self-explanatory, needs AE's assistance

- YAML/JSON based configuration option for handling tool command line arguments

### Conclusion

- Simulation is necessary for Use cases and System scenarios

- Formal verification for micro-architectural features

- Automation in Regression management

- Single document VPlanner for reporting

- Combination of Simulation and Formal techniques gives best results

Thanks to Jukka Heikkila, Patrick Blestel and Toni Rastio for Technical Support

# THANK YOU

YOUR INNOVATION YOUR COMMUNITY