# Comprehensive Verification and Performance Analysis of HBM3 Memory Subsystem

Ankitkumar Patel - Annapurna Labs (AWS) Co-authored by Gaurav Chugh & Heena Mathur - Synopsys

2

# Agenda

- Objectives

- HBM3 (High Bandwidth Memory) Subsystem Architecture

- Verification Requirements

- Memory Subsystem Performance Analysis

- Conclusion

- Comprehensive Verification of HBM3 Memory Subsystem

- Signoff with different JEDEC and Memory Vendor Configurations

- Performance Analysis sign off

- Coverage Closure

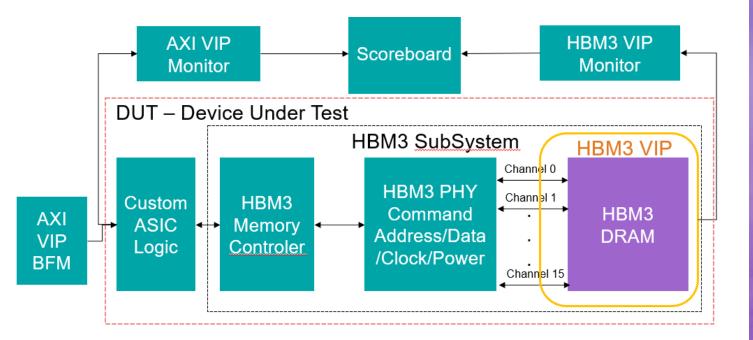

# HBM3 Subsystem Architecture

# HBM3 Subsystem Architecture

- 16 Channels 32 Pseudo Channel

- DRAM Capacity

4/8/16/24/32/64 GB

- Different Data Rates

4800Mbps, 5600Mbps & 6400Mbps

- BW Requirement

25.6GBps

- HBM3 Key Features

Training (DWORD, CA & Periodic Phase) IEEE Repairs

Bank Group & Refresh Management

- End-to-End Data integrity check between AXI Interface & HBM3 DRAM Interface

- Protocol Compliance Checks at AXI & HBM3 Interface with AXI & HBM3 VIP Monitor

- HBM3 & AXI VIP Synopsys

# **Verification Requirements**

### **Verification Requirements**

Requirements

**Solutions**

#### Scalability from subsystem to SoC Reuse SV & UVM Env at SoC testbench Scalability from HBM3 to next HBM3 VIP Supports backward compatibility as well as future generation of HBM generation of HBM without need of testbench changes Configurability for different JEDEC & HBM3 VIP supports Different Vendor Catalog load during run time • memory vendor datasheets without need for recompilation or TB changes Robust set of protocol & timing Leverage exhaustive protocol and timing checks from HBM3 VIP checks Leverage HBM3 VIP Performance Metrices (Bandwidth, Page Hooks for analyzing performance hit/miss, Irregular page accesses, Unoptimized command spacing) Used HBM3 VIP callbacks to implement Custom Performance data at HBM3 Interface Monitor for monitoring custom workload traffic

### Verification Requirements

RequirementsSolutionsError injection capability to test end<br/>to end Interrupt flow• 1 or 2 bit ECC Error, Sev error, etcSimulation speed-up requirements• Bypass Training<br/>• Backdoor Mode Register Settings

End-to-end data integrity between

AXI Interface to HBM3 Interface

Custom scoreboard implemented by leveraging Synopsys AXI & HBM3 VIP callbacks

•

Coverage model for verification signoff

Gate-level simulation

• HBM Subsystem - DW & CA training with Write & Read Traffic

Leverage HBM3 VIP comprehensive coverage model

Ease of debug capabilities

- Transaction log, Synopsys Verdi

Protocol Analyzer, Debug Ports, Error Message

- Backdoor HBM3 DRAM initialization with known/random value

- Different Traffic Pattern Analysis

- Write only/Read Only/Write-Read Mix

- Sequential Address Access

- Random Address Access

- Identify Unnecessary bubbles on Command & Data Interface

- HBM Controller/HBM PHY/Custom Wrapper logic

- With large number of write-read transaction flowing through HBM3 DRAM.

- For different row & column commands to identify any bubbles (Idle Cycle) inside HBM Subsystem

- Page open/close policy

- Root Cause analysis of performance Bottlenecks

- Review row & column commands from performance analyzer to identify throughput bottlenecks

- Key Performance Matrices to achieve HBM subsystem performance throughput goals

- Bandwidth

- Page hit/miss ratios

- Irregular page accesses

- Unoptimized command spacing

- Read-Write grouping

- Developed custom performance monitor based on HBM3 VIP callbacks

- Transaction\_started & Transaction\_ended to extract custom throughput requirements for different traffic workloads.

- Auto Test Pass/Fail status based on throughput goal requirements for different traffic pattern

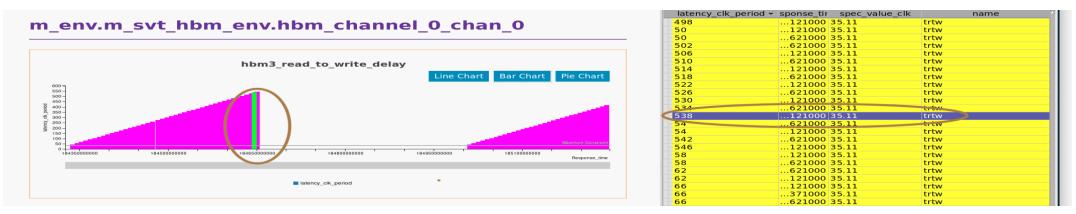

• Performance Analyzer helps to identify any gaps between read to write switching

• Identify gap between write to write for different bank group latency

### Conclusion

- Deliver high quality HBM Memory subsystem RTL to SoC

- Meet desired throughout goals for different traffic workloads

- Exercise HBM Memory subsystem for different Transaction sizes & Address alignments

- HBM Memory subsystem RTL meet JEDEC & Vendor Timing and Protocol compliance

- Meet HBM3 Coverage requirements

#### HBM3 Subsystem Requirements

- 16 Channels 32 Pseudo Channel

- DRAM Capacity 4/8/16/24/32/64 GB

- Different Data Rates 4800Mbps, 5600Mbps & 6400Mbps

- BW Requirement

25.6GBps

- HBM3 Key Features

- Training (DWORD, CA & Periodic Phase) IEEE Repairs

Bank Group & Refresh Management

- End to End Data integrity check between AXI Interface & HBM3 DRAM Interface

- Protocol Compliance Checks at AXI & HBM3 Interface with AXI & HBM3 VIP Monitor

# THANK YOU

YOUR INNOVATION YOUR COMMUNITY