Automated Constraints Promotion Methodology from IP to SoC Designs for Complex Designs

Mallik Devulapalli & Ajay Daga Synopsys

# Agenda

- Addressing the Need for Timing Constraints Promotion

- Overview of Synopsys Timing Constraints Manager

- Case Study SDC Promotion Using Timing Constraints Manager

- Leveraging Early PCIe Gen 6 Sub System Configuration

- Getting a Jumpstart on SDC Promotion Using Fusion QIKs

- Results on Early PCIe Gen 6 Design

- Conclusion

- Q & A

# Addressing the Need for Timing Constraints Promotion Before Synthesis Overview of Synopsys Timing Constraints Manager

### **Bottom-up Hierarchical Design Integration**

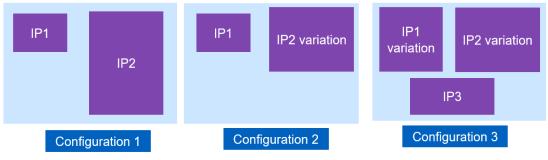

What is sub-system integration?

- SoCs involve integration of several sub-systems

- Ex. Interface IPs: PCI Express (PCIe) or USB

- Computing IPs: Micro-processors or Graphics processors

- Communication IPs: Modems

Timing constraints at individual IPs are well-defined and exercised

- Timing constraints take various shapes when IPs are put together to form subsystem

- Number of computing units may change

- Different number of clocks, different interface standards

- Higher or lower bandwidth for IP variations

- May demand different bus dimensions

- Clocks, exceptions need to be manually rethought and verified

### Timing constraints don't exist for newer configurations and require manual effort

4

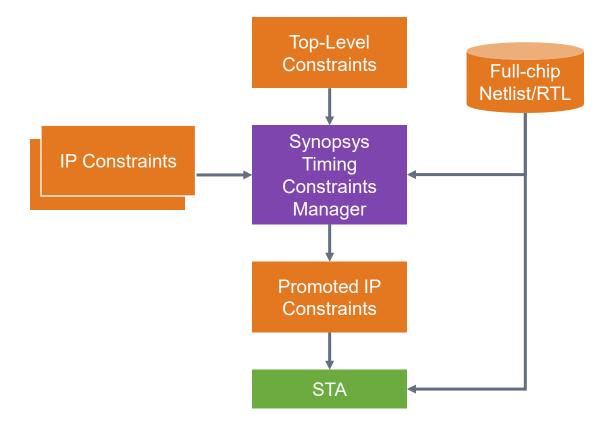

# Synopsys Timing Constraints Manager (TCM)

Built on FishTail's Best-in-Class SDC Constraints Solution

- Comprehensive SDC Timing Constraints Generation, Verification and Management

- SDC Verification with No Noise

- SDC Signoff at RTL handoff using proprietary formal & assertion technology

- Automated, Accurate SDC Promotion

- Saves weeks and eliminates bugs from manual reuse of IP constraints in SoCs

- Automated SDC Generation from RTL

- Improves designer productivity and design PPA

| <b>90% Reduction</b><br>in Designer SDC<br>Review Effort | Auto SDC Gen/Mgmt.<br>Shortens SoC Execution<br><b>by 6-8 Weeks</b> | Eliminate Silicon<br>Failure from SDC Bugs |

|----------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|

|----------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|

Deployed at top-tier semi companies with production-proven tape-outs

### **TCM Constraint Promotion Flow**

snug

- Promote standalone block-level constraints to chip-level

- Reduces effort and eliminates errors resulting from maintain two versions of the same constraints (for standalone and in-context use)

- Automatically stitches block and top-level clocks

- Preserves user Tcl for timing exceptions

# TCM SDC Promotion Methodology on Early PCIe Gen 6

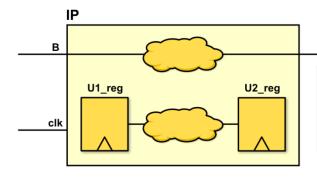

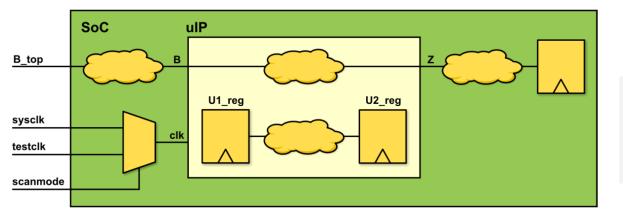

### **Illustration of Constraint Promotion**

# snug

#### SDC for IP

create\_clock clk -period 6 -name clk

set\_false\_path -from [get\_pins -of [get\_cells -hier

-filter full\_name=~\*U1\*] -filter is\_clock\_pin==true]

set\_multicycle\_path -from clk

#### SDC for SoC

create\_clock sysclk -period 6

create\_clock testclk -period 6

set\_case\_analysis 0 scanmode

set\_clock\_groups -async \

-group sysclk -group testclk

Promoted

SDC

current\_instance uIP

set\_false\_path -from [get\_pins -of [get\_cells -hier -filter full\_name=~\*U1\*]

-filter is\_clock\_pin==true]

current\_instance

create\_generated\_clock -divide\_by 1 -master sysclk -name sysclk\_1 uIP/clk

set\_multicycle\_path -from sysclk\_1

set\_clock groups -async -group {sysclk 1} -group {testclk}

### **SDC Promotion Using TCM** Case Study Leveraging Early PCIe Gen 6 Subsystem Configuration

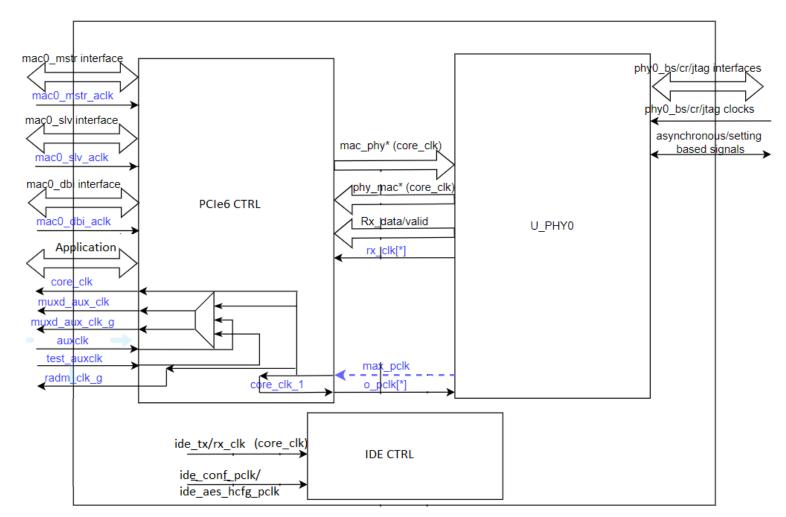

### Design Specifics of PCIe Top SS

Gen6 top SS early release

PCIe controller & IDE controller blocks are implemented as Hard macro

### **Design Specifics - PCIe Gen6 Clock Definitions**

PCIe Ctrl (mac0\_DWS\_pcie\_ctl\_rams)

PHY (dwc\_pcie6\_upcs\_x4\_ns\_x8\_x4x4\_pipe)

max pclk (1 GHz) max\_pclk max\_pclk\_scan (1 GHz) pipe lane0 max pclk lane0 max pclk div1 clksrc0 (1 GHz) lane0 max pclk div2 clksrc0 (500 MHz) lane0 pcs scan max pclk (1 GHz) core clk (1 GHz) lane0 pcs scan shift max pclk (200 MHz) core clk scan (1 GHz) lane0 in pcs clk (1 GHz) pipe lane0 in pclk lane0 pcs scan pclk (500 MHz) o pclk[0] lane0 in pcs clk lpbk rx clk (1 GHz) pipe rx0 clk rx0\_clk rx\_clk\_0 (1 GHz) auxclk test auxclk IDE Ctrl (mac0 ide ctl rams) ide cfg caps clk (1 GHz) ide\_cfg\_caps\_clk Red: PHY clock definitions ide\_rx\_clk ide rx clk (1 GHz) Blue: PCIe Ctrl clock definitions Green: IDE Ctrl clock definitions ide tx clk ide\_tx\_clk (1 GHz)

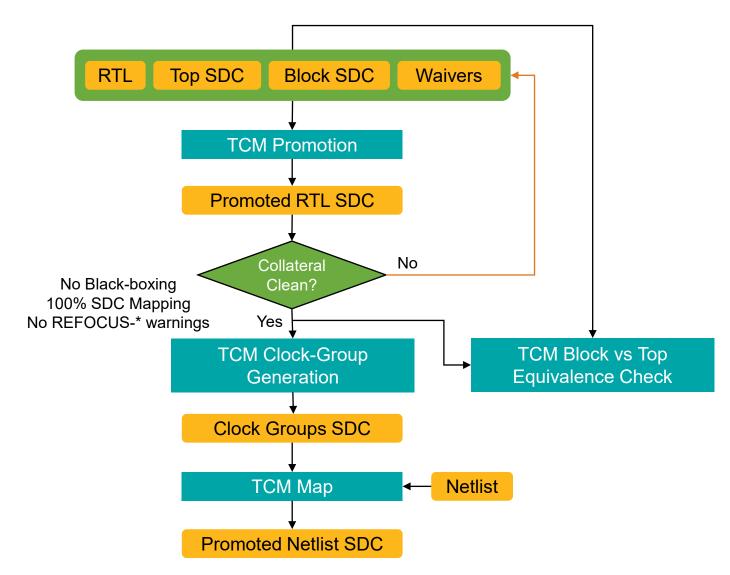

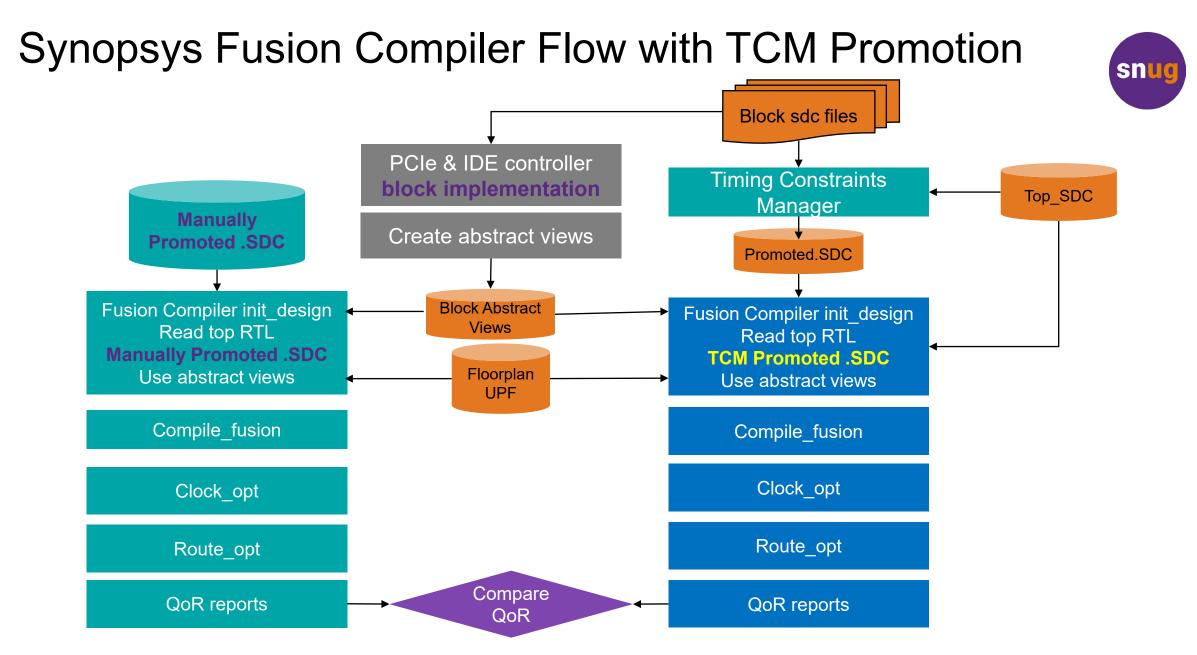

# PCIe Gen 6 TCM Constraints Promotion Flow

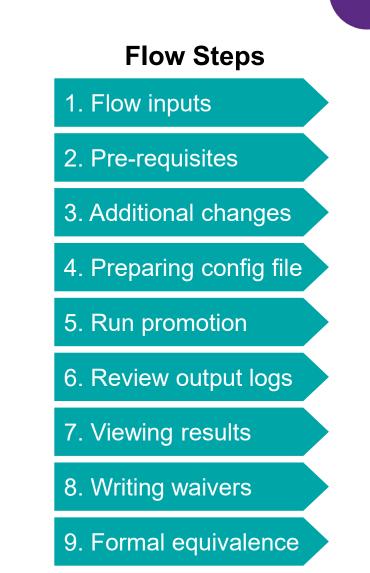

Outline of steps

- Required input collateral for running TCM:

- Full RTL design file list

- Include entire design subsystem which would include IP RTL

- Liberty db files (standard cells and/or memory cells)

- Verilog behavioral models can be used if liberty models are unavailable

- Sub design SDC constraints in Tcl format

- SDC format is acceptable, Tcl is preferred

- Top level clocks file

- Any waiver files provided by IP verification by IP provider

**SNU**

### Prerequisites of TCM Promotion Flow

Applicable to all sub-designs or IP cores

- Ensure all sub designs/IP cores are run through TCM SDC verification flow

- Read Tcl constraints, RTL and perform SDC verification

- Avoid issues faced in promotion flow having origin in the block-level constraints

- Separate training resources are available

- Ensure block-level constraints are signed off

- Example : A clock is not propagating to output of mux, we would not expect it to be promoted

- If a constraint or Tcl structure is not friendly with TCM, user has opportunity to fix it first

- Verilog file lists along with `defines, and necessary variables to resolve RTL

- set verilog\_defines "SYNTHESIS" ;# recommend to add SYNTHESIS to all Synopsys cores

- set verilog\_parameters "rtl\_parameters.cfg"

- set mapping\_include\_files "rtl\_variables.config.tcl"

#### 2. Pre-requisites

### Before Starting TCM Promotion Flow

Applicable to all sub-designs or cores

- Prepare a top-level clocks file

- This file should include

- All primary and virtual clocks used purely at top level

If we expect the clock to connect with promoted clock, it is essential to maintain same clock period

- Generated clocks used purely at top level

- Clock groupings

Any known asynchronous clock relationships

- IO delays, if required at this level

- Treat all IP blocks as a sub-block for constraint promotion flow

- All constraints that need to be promoted should be at block level scope

- Top level contains only instantiation of blocks and some glue logic but not IP blocks

- This approach keeps the constraints space very clean and helps promotion of constraints

3. Additional changes

sn

#### 4. Preparing config file

### **Preparing Configuration Files**

#### Customizing template

- Download template config file and cheat sheet from TCM installation

- Unix %> cp \$FISHTAIL\_HOME/cfs\_config\_files/rtl\_constraint\_promotion.cfg

- Unix %> cp \$FISHTAIL\_HOME/doc/tcm/doc/cheat\_sheets/RTLConstraintPromotionCheatSheet.pdf

- Customize sections in rtl\_constraint\_promotion.cfg (Example)

```

set design_name "pcie6_snps_hardening_dm8sx8_gen6_axi_subsys"

set file list "verilog lists/pcie6 snps hardening dm8sx8 gen6 axi subsys.add mux.lst"

set block list {

mac0_ide_ctl_rams

mac0 DWS pcie ctl rams

dwc pcie6 upcs x4 ns x8 x4x4 pipe

set block sdc files {

tcl constraints/mac0 ide ctl rams.tcl

tcl constraints/mac0 DWS pcie ctl rams.mod.core clk.add scan.tcl

tcl constraints/pcie6 snps hardening dm8sx8 gen6 axi subsys.phy.tcl

set top level clocks for promotion {

tcl constraints/top clocks.tcl

tcl constraints/Uncertainity.tcl

set lib models are dbs true

set lib file dirs {

.. }

```

### **Running Promotion**

#### Customizing template

- After config file is suitably edited, run these commands

- Unix %> create\_fishtail\_scripts -config\_file rtl\_constraint\_promotion.cfg

- Unix %> cd fishtail\_rtl\_constraint\_promotion/constraint\_promotion/

- Unix %> promote\_constraints

- New SDC file promoted.sdc is generated

- Comments indicate which lines of source sdc files were used to promote

```

# SDC file generated by FishTail Refocus version U-2022.12-SP5-1

# From /mac0_ide_ctl_rams.tcl line 13 for instance u_mac_subsys/u_ide_ctl_rams

create_generated_clock -name ide_aes_hcfg_pclk_ft_ide_aes_hcfg_pclk_ft_I_u_ide_ctl_rams -master_clock

ide_aes_hcfg_pclk -add [get_pins { u_mac_subsys/u_ide_ctl_rams/ide_aes_hcfg_pclk }] -source [get_ports {

ide_aes_hcfg_pclk }] -divide_by 1 -combinational

...

set_clock_uncertainty -fall_from [get_clocks { phy0_pll0_word_clk_o }] -rise_to [get_clocks {

phy0_pll0_word_clk_o }] $::fishtail::phy0_pll0_word_clk_o_setup_fall_from_rise_to_uncertainty -setup

...

# Auto-Generated clock group because multiple tool inserted div-1 generated clocks are defined on the same

pin

set_clock_groups -physically_exclusive -group { core_clk_ft_I_u_phy } -group { core_clk_ft_lane0_in_pcs_clk

} -group { core_clk_scan_ft_I_u_phy } -group { core_clk_scan_ft_lane0_pcs_scan_pclk }

set false path -through [get pins { u_mac_subsys/u_pcie_ctl_rams/rx_lane flip_en }]

```

# Verifying Output and Resolving Issues

What to watch out for

- Un-resolved modules: ensure that the hand mapped cells are found

- Constraints that were not parsed due to incompatible tcl

- Example: Don't include implementation tool (like Design Compiler or Fusion Compiler) attributes in tcl constraints

- What to ensure

- The constraint mapping is 100% or close enough

- Look at run\_refocus.log

- Info: Constraint mapping percentage: 99%

- If it is not 100% check what constraints were skipped, and fix the constraints

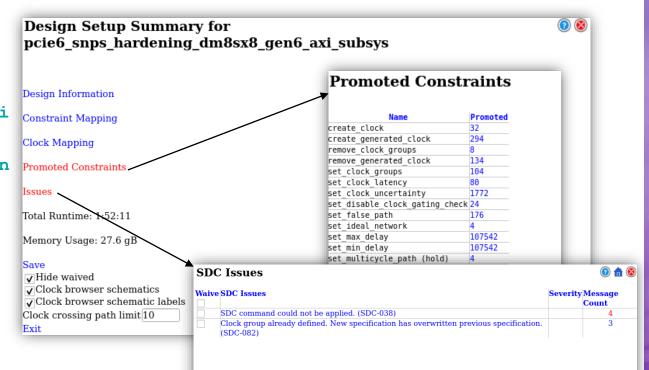

grep skipped run\_refocus.log Info: 0 create\_clock command(s) were skipped Info: 0 create\_clock (virtual) command(s) were skipped Info: 0 create\_generated\_clock command(s) were skipped Info: 0 set\_clock\_groups command(s) were skipped Info: 0 set\_clock\_latency command(s) were skipped Info: 0 set\_clock\_latency command(s) were skipped Info: 0 set\_false\_path command(s) were skipped Info: 0 set\_ideal\_network command(s) were skipped Info: 0 set\_ideal\_network command(s) were skipped Info: 0 set\_max\_delay command(s) were skipped Info: 0 set\_min\_delay command(s) were skipped Info: 0 set\_multicycle\_path (hold) command(s) were skipped Info: 0 set\_multicycle\_path (setup) command(s) were skipped Info: 0 set\_sense command(s) were skipped Info: 32 create\_clock command(s) were written to the output file(s)

Info: 294 create\_generated\_clock command(s) were written to the output file(s)

Info: 134 remove\_generated\_clock command(s) were written to the output file(s)

Info: 104 set\_clock\_groups command(s) were written to the output file(s)

Info: 104 set\_clock\_groups command(s) were written to the output file(s)

Info: 80 set\_clock\_latency command(s) were written to the output file(s)

Info: 1772 set\_clock\_uncertainty command(s) were written to the output file(s)

Info: 24 set\_disable\_clock\_gating\_check command(s) were written to the output file(s)

Info: 176 set\_false\_path command(s) were written to the output file(s)

Info: 107542 set\_max\_delay command(s) were written to the output file(s)

Info: 107542 set\_min\_delay command(s) were written to the output file(s)

Info: 4 set\_multicycle\_path (hold) command(s) were written to the output file(s)

Info: 4 set\_multicycle\_path (setup) command(s) were written to the output file(s)

Info: 58 set sense command(s) were written to the output file(s)

6. Review output logs

### Viewing the Results of the Promotion

Using the graphical user interface

- Bring up the results in UI

- After promotion of clocks is run, browse results and take action to fix anything

- Unix %> module load tcm ; module load verdi

- Unix %> cd

fishtail\_rtl\_constraint\_promotion/constrain

ts\_promotion

- Unix %> view\_fishtail\_results -verdi

- Browse design issues, add any waivers until all issues are resolved

#### 7. Viewing results

Snu

### **Customizing Waivers**

Guidance and refinement with waivers

- Waivers file can be specified in the config for promotion flow

- Example : When the clock in the block should be recognized same as the top level clock

- When multiple clocks arrive from top level at an input on the IP, TCM needs guidance

- Examples:

- Config file rtl\_constraint\_promotion.cfg contains:

```

- set external_waive_tcl_file "my_waive.tcl"

```

#my\_waive.tcl

• •

```

map_top_clock_to_block_clock -instance { u_mac_subsys/u_ide_ctl_rams } -block_clock { ide_aes_hcfg_pclk } -top_clock { ide_aes_hcfg_pclk }

```

```

map_top_clock_to_block_clock -instance { u_mac_subsys/u_pcie_ctl_rams } -block_clock { max_pclk } -top_clock { lane0_max_pclk_div1_clksrc0

lane0_max_pclk_div2_clksrc0 }

```

map\_top\_clock\_to\_block\_clock -instance { u\_mac\_subsys/u\_pcie\_ctl\_rams } -block\_clock {rx\_clk\_0 } -top\_clock { lane0\_phy\_rx\_serdes\_clk lane0\_phy\_rx\_serdes\_clk\_dser\_int\_clk lane0\_rx\_scan\_ms\_clk lane0\_rx\_scan\_shift\_clk lane0\_in\_pcs\_clk\_lpbk\_rx\_clk} map\_top\_clock\_to\_block\_clock -instance { u\_mac\_subsys/u\_pcie\_ctl\_rams } -block\_clock {rx\_clk\_1 } -top\_clock { lane1\_phy\_rx\_serdes\_clk lane1\_phy\_rx\_serdes\_clk\_dser\_int\_clk lane1\_rx\_scan\_ms\_clk lane1\_rx\_scan\_shift\_clk lane1\_in\_pcs\_clk\_lpbk\_rx\_clk}

8. Writing waivers

### Equivalence Checking of Promoted Constraints

Validation of IP vs promoted constraints

- TCM verifies IP constraints (golden) vs promoted constraints (reference)

- After promotion of clocks is run, next step is to run the equivalency check

- Unix %> cd fishtail\_rtl\_constraint\_promotion/equivalence\_checking

- Unix %> check\_equivalence

- This step runs clock groups generation, does formal equivalency check

- What to ensure?

- Endpoint comparison is 100%

- Clock definition comparison is OK

- Path Comparison is 100%

- What next?

- Inspect and debug results

- For mismatches

- Add waivers if needed

| Timing Requirement Comparison       | 08 |

|-------------------------------------|----|

| Golden Clocks                       |    |

| Reference Clocks                    |    |

| Clock Definition Comparison Results |    |

| Clock Group Comparison Results      |    |

| Endpoint Comparison Results         |    |

| Path Comparison Results             |    |

| Save<br>↓<br>Hide waived<br>Exit    |    |

# Getting a Jumpstart on SDC Promotion using Fusion QIKs How can implementation engineers benefit?

### Additional Automation for Ease of Use & PPA

Quickstart Implementation Kit (QIK Flow)

- Easily generate configuration file(s) and customize based on familiar Fusion Compiler RM 2.0 setup

- Verify sub blocks

- Apply waivers (manual analysis)

- Fix any constraints issues

- Run promotion flow

Contact Synopsys to download Fusion Compiler QiK setup for Timing Constraints Manager

# Viewing and Verifying Results on Early PCIe Gen 6 Design

# Results on Early Release of PCIe Gen 6 SS

Timing promotion and Fusion Compiler implementation

- Promotion

- Runtime 5 hrs; Memory 37 GB

- 39 map\_top\_clock\_to\_block\_clock waivers

- Block vs Top Equivalence

- Runtime 2 hrs; Memory 43 GB

- Showed promotion results were correct

- Clock-Group Generation

- Runtime 10 minutes; Memory 36 GB

- 134 clock groups generated

- Netlist Mapping

- Runtime 3 hrs; Memory 15 GB

- 87% mapping; registers optimized out, abstracted models

- Fusion compiler QoR results show similar PPA

- Formal equivalence was established with Synopsys Formality®

- Proves that the design is equivalent

| route_opt                         | WNS(ns)<br>R2R | TNS(ns)<br>R2R |

|-----------------------------------|----------------|----------------|

| FC Baseline<br>(manual promotion) | -0.447 ns      | 377 ns         |

| FC with TCM<br>(TCM flow)         | -0.417 ns      | 345 ns         |

sn

### Conclusion

- Need for solution

- Timing constraints for subsystems/SoCs need to be created through reuse of IP constraints

- Current manual approach is time-consuming, introduces mistakes with manual promotion of constraints

- Synopsys Timing Constraints Manager

- Comprehensive SDC management

- TCM offers flows for SDC verification, Promotion, Demotion, SDC Equivalence among others

- Customer success

- Deployed at top tier semi companies with production-proven tape-outs

- Scalable solution

- Can be targeted to variety of IPs and configurations

- Great turnaround time with integrity in IP constraint reuse

- Cuts the time to solution from weeks to days.

- Fusion Compiler QiK is available to help with productivity

# THANK YOU

YOUR INNOVATION YOUR COMMUNITY