Navigating the Labyrinth: Unravelling Challenges in Analog Circuit Debugging with Synopsys StarRC Parasitic Explorer

Venkat Nachiappan Intel Corporation Senthil Annamalai Synopsys Inc

### Introduction

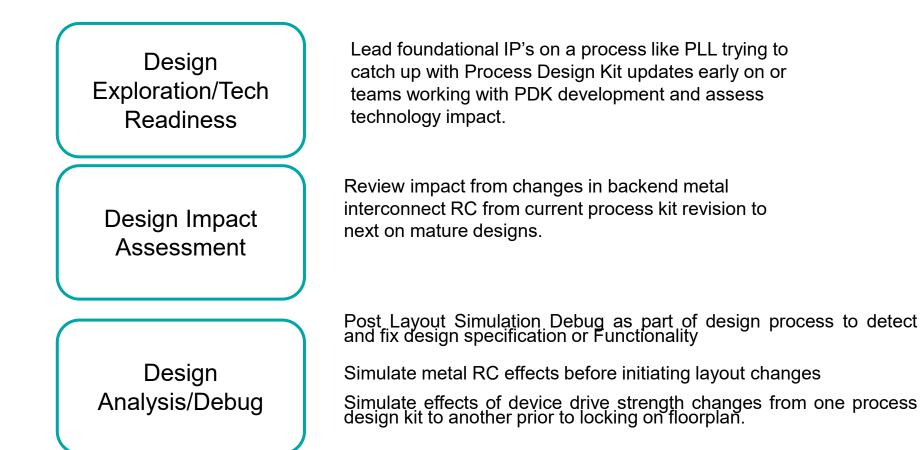

- Traditional methods existing today to assess impact of interconnect resistance and capacitance or examining effects of device sizing and drive strength changes on Analog circuit performance involves a costly design loop.

- This encompasses generating several versions of layout followed by extracting and capturing the parasitics into a Detailed Standard Parasitic Exchange (DSPF) netlist for simulation with an Analog Spice Circuit Simulation Engine downstream. Or other methods involve running simulation iterations in pre-extracted mode that don't capture the design intent accurately or manual intervention of capturing intent directly with ASCII RC netlists which are not efficient and scalable.

- Cover overview for an interconnect scaling and device parameter sizing flow for custom transistor level extraction context aiding designers to perform what-if RC analysis

- The framework aids designers with several different applications like simulating effects of variation in device drive strengths as PDK matures or working through post layout simulation debug prior to committing physical layout changes

- The flow additionally also provides a method to scale interconnect resistance and capacitive effects seamlessly to mimic and simulate effects of Process Design Kit back-end metal RC changes.

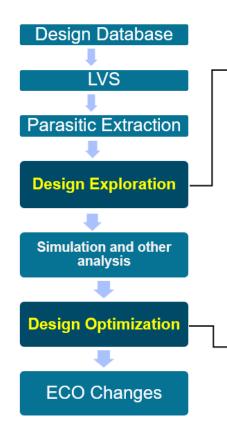

# Where Does "what-if" Fit in the Design Flow

# Parasitic Explorer Flow

# Parasitic Explorer Flow

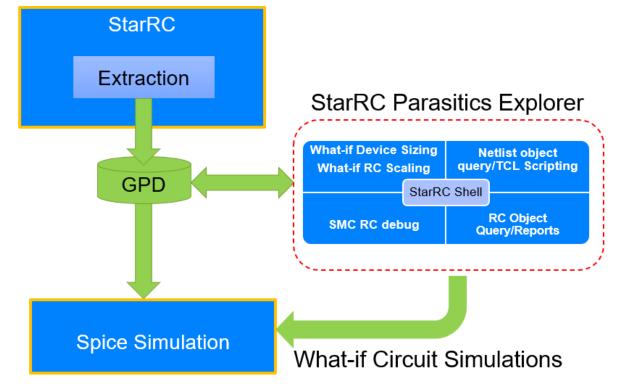

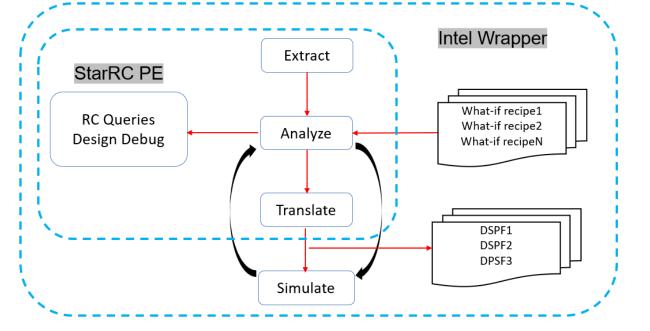

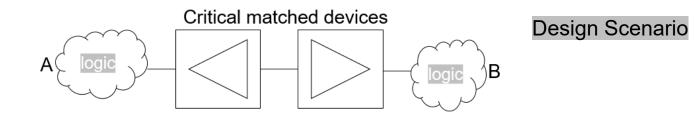

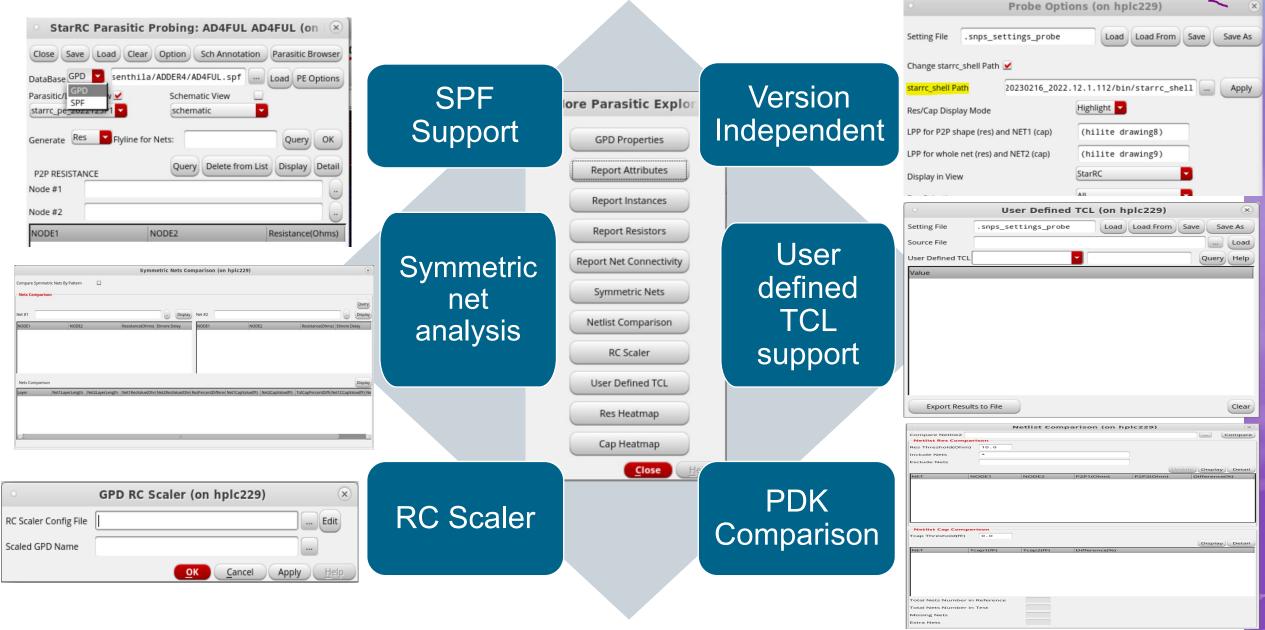

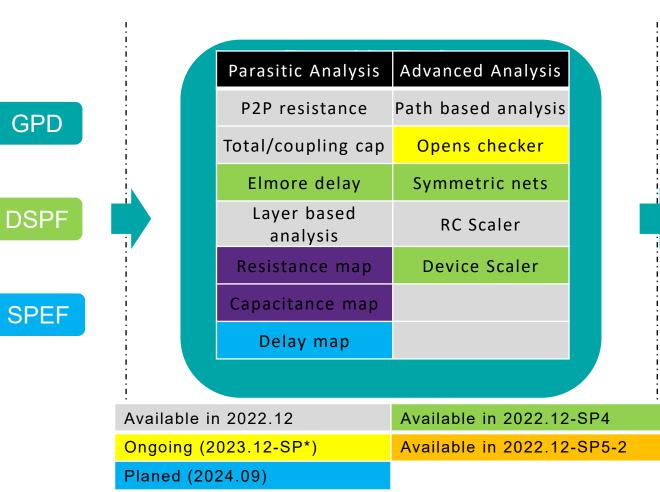

- Synopsys StarRC<sup>™</sup> Parasitic Explorer Flow enables end users to perform various RC debug experiments from a single cockpit in addition to extending the capabilities for performing what-if type simulation experiments

- The primary input source for the flow is a Golden Parasitic Database generated by Synopsys StarRC with specific attributes for giving end users capability to perform the needed RC debug and what-if simulation tasks

- StarRC PE has several extensive capabilities but in this presentation, we will focus on the Interconnect Scaling and Device Parameter sizing aspects feeding downstream spice simulation

- In the context of the Device Sizing and Interconnect Scaling aspects, end users start with an extracted database and iterate over that for the design exploration.

- Physical layout at some level of maturity in the design cycle with LVS'able where end user is able to run Layout versus Schematic Checks followed by extraction and then continue with the analysis depending on what context it is (Tech Readiness, Design Debug, etc).

## Use Models for Design Debug and Exploration

## Gain deeper understanding of design before running expensive post layout simulations

- What is the highest fanout ?

- Do I have devices with appropriate drive strength?

- · What is the Elmore delay of my nets?

- · Can I understand the Xtalk effect on critical signal nets?

## Probe into specific target nets and its drivers receivers to uncover design issues

- · Why is my design not meeting functional spec and PPA targets?

- Can I isolate the bottlenecks in the layout layers causing high R, higher coupling regions,etc?

- How is process migration/technology porting going to impact design functionality and margins?

# Intel What-if Simulation Workflow

TCL Recipe from User

we draw trave, builts escape fall

scale paratice - config gath to scaling reips config files

we draw to escale fall

(Transform in memory)

Spice Polo Simulation

we draw to escale fall

for draw to escale fall

we draw to escale fall

for draw to escale fall

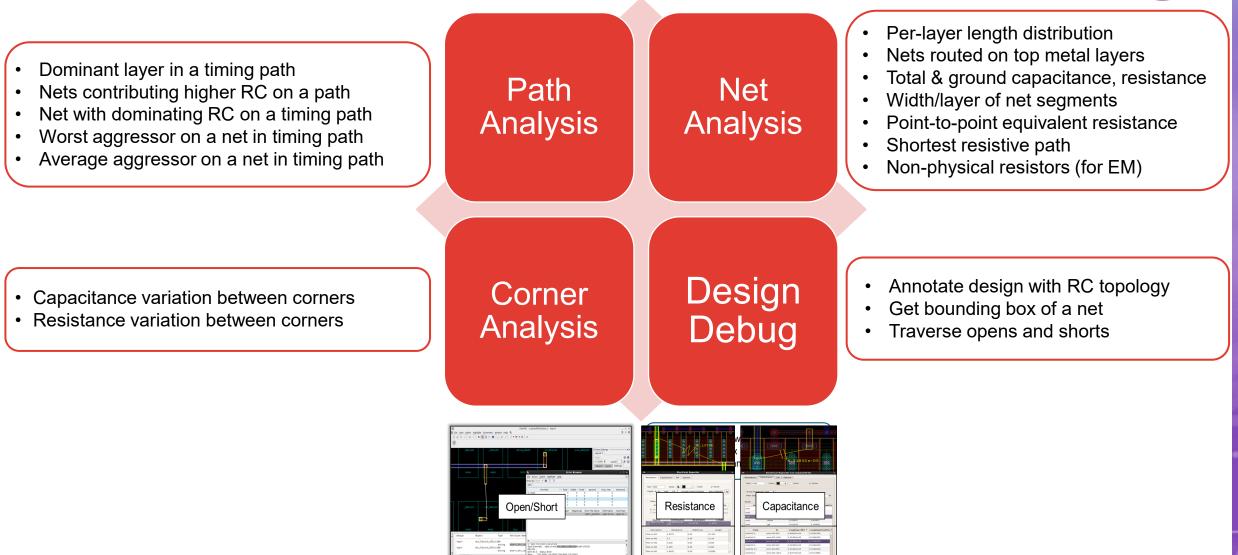

- Flow chart shows the Intel wrapper flow built around Synopsys StarRC Parasitic Explorer.

- The wrapper flow takes in recipes from end user and uses Synopsys StarRC parasitic explorer to transform changes in memory followed by writing out a Detailed Standard Parasitic Format (DSPF) RC netlist for Circuit simulations.

- The flow works to generate scaled DSPF at single temperature and interconnect skew or with StarRC simultaneous multi corner (SMC) mode to generate DSPF's across multiple temperature and interconnect skews.

# Config File Syntax

snug

#### 1. Net Based Controls

- a) -net\_list <net name> -res\_factor <res\_factor> -cc\_factor <cc\_factor> -gc\_factor <gc\_factor> //specify factor to "1" if no scaling is required

- b) -net\_list <net name> -res\_factor <res\_factor2> -cc\_factor <cc\_factor2> -gc\_factor <gc\_factor2>

- c) -net\_list <net name> -from <pin/port/node name> -to <pin/port/node name> -res\_factor <res\_factor> -cc\_factor <cc\_factor> -gc\_factor <gc\_factor>

#### 2. Layer Based Controls

- a) -layer <layer name> -res\_factor <res\_factor> -cc\_factor> -gc\_factor< gc\_factor> //specify factor to "1" if no scaling is required

- b) -net\_list <net name> -layer <layer name> -res\_factor <res\_factor> -cc\_factor> -gc\_factor <gc\_factor> //specify factor to "1" if no scaling is required

#### 3. Width Based Controls

a) -layer <layer name> -target\_width <width> -res\_factor 10

#### 4. Device Sizing Controls

- a) device instance\_name -w new\_w\_data -nf new\_nf\_data -m new\_m\_data -l new\_l

- b) device instance\_name -model new\_model\_name -cellw new\_cellw

#### 5. SMC controls

```

corner_start <temp1_skew1>

-net_list * -layer <layer name> -res_factor 2 -gc_factor 2 -cc_factor 2

corner_end

```

```

corner_start <temp2_skew2>

-net_list * -layer <layer name> -res_factor 2 -gc_factor 2 -cc_factor 2

corner_end

```

```

corner_start <temp3_skew3>

-net_list * -layer <layer name> -res_factor 10 -gc_factor 10 -cc_factor 10

corner_end

```

# Design Usage Cases

# **Design Case 1**

| sn | ug |

|----|----|

|    |    |

#### **Design Scenario Details**

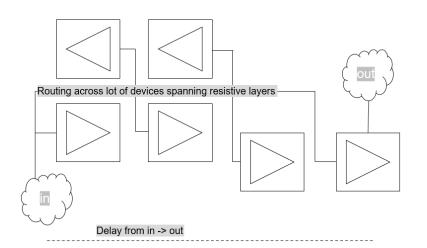

- Case 1 demonstrates Design Exploration examining simulation results from emulating effects of different variants of layout routing topology for a level shifter before locking on floor plan.

- Sweep with different RC scaling recipes on critical nets to assess simulation impact and meet delay specifications across 4 simulation Corners2

- Critical net "NET1" is used for the evaluations with goal of meeting target delay of 1ns. Scope of analysis is to determine if promoting the routing to higher metal layers or widening the metal routing on the lower layers can meet the delay target

- 2 recipes run to show the upper and lower boundaries of the targeted delay margins. Experiments span reducing the overall RC by half (0.5x) in Recipe#1 and reducing the overall RC by 2x in Recipe#2

| Net              | RC Profile                         | RC Scaling Recipe                              |   |

|------------------|------------------------------------|------------------------------------------------|---|

| Critical<br>NET1 | Vary MetalX by<br>2x and VIAX by   | -net_list NET1 -layer METALX<br>res_factor 2   | - |

|                  | 0.5x                               | -net_list NET1 -layer VIAX<br>res_factor 2     | - |

| Critical<br>NET1 | Vary MetalX by<br>0.5x and VIAX by | -net_list NET1 -layer METALX<br>res_factor 0.5 | - |

|                  | 2x                                 | -net_list NET1 -layer VIAX<br>res factor 0.5   | - |

| Recipe 📑 | Туре 💌     | Spec 💌 | Pass/Fail 🛛 💌 | SIM_PVT1 - | SIM_PVT2 🔻 | SIM_PVT3 💌 | SIM_PVT4 💌 |

|----------|------------|--------|---------------|------------|------------|------------|------------|

| Recipe#1 | Delay_Rise | <1ns   | Fail          | 615.2ps    | 774.3ps    | 711p       | 1.205n     |

| Recipe#1 | Delay_Fall | <1ns   | Fail          | 778.4ps    | 1.321ps    | 836.2p     | 891.1p     |

|          |            |        |               |            |            |            |            |

| Recipe#2 | Delay_Rise | <1ns   | Pass          | 451.1p     | 563p       | 715.3p     | 512p       |

| Recipe#2 | Delay_Fall | <1ns   | Pass          | 581p       | 674.1p     | 891.1p     | 609.2p     |

|          |            |        |               |            |            |            |            |

#### Scaling Recipe

Results

#### SNUG SILICON VALLEY 2024 11

# Design Case 2

#### **Design Scenario Details**

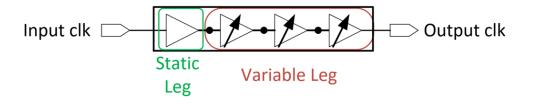

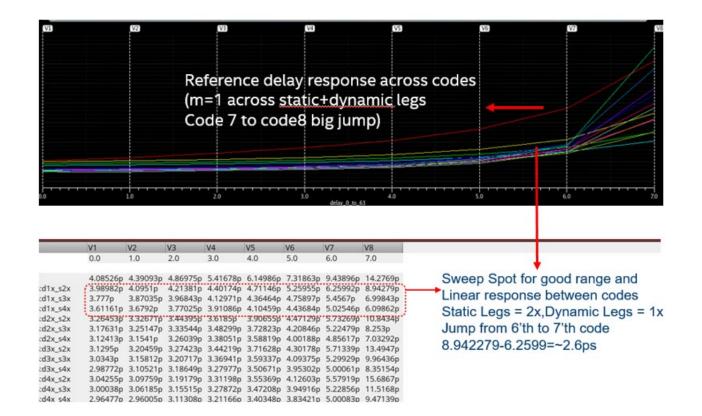

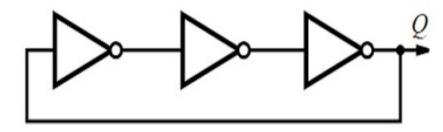

- Case 2 details scenario of Delay Linearization circuit analysis activity to determine optimum ratio of device sizes for achieving linear transitions across codes.

- Sweep device size ratio between groups of devices in the design. Design Scenario

- Static legs always on, dynamic legs controlled through code sweep.

- As codes sweep from 0 to 7 less of the dynamic TX legs are turned on.

- At code 7 only static legs on. Highest delay with no dynamic legs turned on.

- At code 0 all legs (dynamic+static) are on with fastest propagation (smallest delay) device sizes swept across static/dynamic legs and find sweep spot to make delay curve across codes linear with good range.

| Dynamic | Static | Ratio<br>Dynamic<br>static | ofDevice Sizing Recipe<br>to                                        |

|---------|--------|----------------------------|---------------------------------------------------------------------|

| 1x      | 2x     | 1:2                        | -device <dynamic> -m 1<br/>-device <static> -m 2</static></dynamic> |

| 1 x     | 3x     | 1:3                        | -device <dynamic> -m 1<br/>-device <static> -m 2</static></dynamic> |

| 1x      | 4x     | 1:4                        | -device <dynamic> -m 1<br/>-device <static> -m 4</static></dynamic> |

| 2x      | 1x     | 2:1                        | -device <dynamic> -m 2<br/>-device <static> -m 1</static></dynamic> |

#### Scaling Recipe

## **Design Case 2: Results**

#### Results

# **Design Case 3**

41.14

LAYERY PVT4

**Design Scenario**

| Net                | RC Profile       | RC Scaling Recipe                                                         |          |  |

|--------------------|------------------|---------------------------------------------------------------------------|----------|--|

| All nets           | Scale            | -net_list * -layer METALX -res_factor 2                                   |          |  |

|                    | MetalX           | corner_start <125C_tttt>                                                  |          |  |

|                    |                  | -net_list * -layer METALX -res_factor 1.5                                 |          |  |

|                    |                  | corner_end                                                                |          |  |

|                    |                  | corner_start <100C_prcs> Scaling Rec                                      |          |  |

|                    |                  | -net_list * -layer METALX -res_factor 0.5                                 |          |  |

|                    |                  | corner_end                                                                |          |  |

| NA                 | PMOS:NM          | -device NMOS1 -m 2                                                        |          |  |

|                    | OS size<br>ratio | -device PMOS1 -m 4                                                        |          |  |

|                    |                  |                                                                           |          |  |

| Extract Corner 🔽 d | elay % chage 🔽   | delay % chage                                                             |          |  |

| LAYERX_PVT1        | 170.32           |                                                                           |          |  |

| LAYERX_PVT2        | 167.85           |                                                                           |          |  |

| LAYERX_PVT3        | 172.08           | ₩ 170.32 167.85 172.08 168.93                                             |          |  |

| LAYERX_PVT4        | 168.93           | a         170.32         167.85         172.08         168.93           b |          |  |

| LAYERY_PVT1        | 41.29            |                                                                           |          |  |

| LAYERY_PVT2        | 47.24            |                                                                           | Results  |  |

| LAYERY_PVT3        | 44.32            | <b>41.29 47.24 44.32 41.14</b>                                            | ILESUILS |  |

Laver Extract Corne

# snug

- Case 3 examines Tech Readiness Sensitivity Analysis Activity during early process assessment phase. We vary RC to detect which layers are more sensitive to delays across interconnect skews.

- GPD contains 4 sets of corners and when scaled and transformed through parasitic explorer will produce 4 scaled DSPF's for downstream spice simulations.

starrc\_shell> get\_gpd\_corners -gpd ringosc.gpd

125C\_tttt 100C\_tttt 125C\_prcs 100C\_prcs

- Simulation test bench device skews and voltages levels kept same sweeping across the 4 scaled DSPF's. Use model also aids to determine sweep spot for N to P MOS device sizing ratios meeting delay specifications for target frequencies.

- If the PMOS is weaker the sizing ratio sweep can provide guidance for end users to make design choices for meeting target delays at different frequencies.

# Design Case 4

| Design Intent Recipe                                  | Device Sizing Recipe                                   | Delay                           |

|-------------------------------------------------------|--------------------------------------------------------|---------------------------------|

| Recipe#1                                              | -device XIBUF.MXI1* -m 2                               | Original Delay – 356ps          |

| Scale MXI1 and MXI2<br>devices Mult by from 4 to<br>8 | -model ULVT<br>-device XIBUF.MXI2* -m 2<br>-model ULVT | Scaled Delay – 345ps            |

| Recipe#2                                              | -device XIBUF.MXI1 -m 3 -                              | Original Delay – 356ps          |

| Scale MXI1 and MXI2                                   |                                                        | Scaled Delay – 337ps (closer to |

| devices Mult by from 4 to<br>9                        | -device XIBUF/MXI2<br>_NET*-m 2 -model ULVT            | spec)                           |

# snug

- Case 4 design Scenario covers observation of circuit propagation delays as a function of upcoming PDK device model changes and device drive strength variations.

- Delay spec to be met is 340pico seconds between input A and output B shown in the circuit snapshot with critical matched devices are in the middle of the design.

- Input A traverses through the critical matched devices playing a crucial role in controlling delay to output B.

- Device sizing recipe dialed in with the hierarchical device names and multiplier scaling factors.

- Results table explains the recipes.Recipe#1 scales the multiplier on MOS devices from 4 to 8 mimicking the effect of increasing the drive strength 2x. Scaled Delay obtained amounts to 345ps. Recipe# 2 bumps up the multiplier from 4 to 9 obtaining delay of 337ps and closer to meeting the target spec of 340ps.

#### **Recipe and Results**

# **PE Interactive Shell/Virtuoso Integration**

# Interactive Parasitic Design Analysis and Exploration

#### Synopsys StarRC Parasitic Explorer

# Parasitic Explorer – Virtuoso Interface

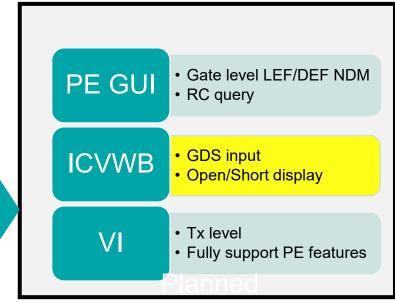

# **Conclusion and Future Plans**

# **Conclusion and Future Plans**

- In this presentation we have demonstrated a new novel capability where-in end users can perform circuit analysis on early or mature designs with shorter turn around times before making progress on design choices.

- The flow described uses the Synopsys StarRC infrastructure and wraps around custom Intel flow creating a user-friendly TCL driven framework. The capability aids analog mixed signal circuit designers to sweep device sizing across PVT's or sweep RC across different PVT's and quickly run circuit simulations to assess impact.

- Future Plans include additional device sizing controls and extend capability to working off a standalone DSPF RC netlist.

# Parasitic Explorer Roadmap

#### **Graphical User Interface**

# THANK YOU

YOUR INNOVATION YOUR COMMUNITY