# Next-Generation Verdi: Overview of the IDE and the Verification Management System

Jens Dickel, Ionut Cirjan, Noam Roth Synopsys Agenda

- Introduction to Next-Generation Verdi

- Synopsys Verdi® Verification Management System with VC Execution Manger

- Verdi Integrated Design Environment (IDE) with Euclide

- Summary + Q&A

# **Introduction to Next-Generation Verdi**

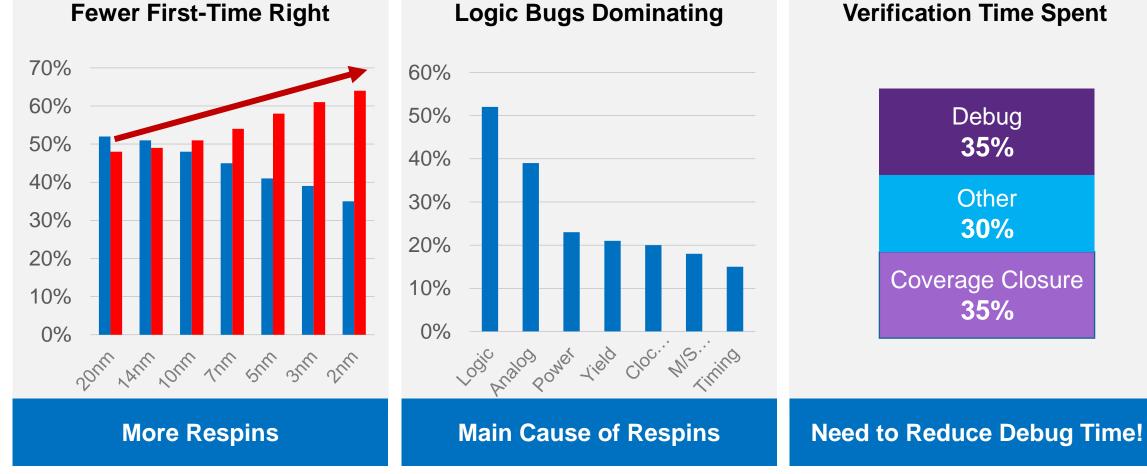

### Impact on Right First-Time Silicon

Source: Wilson Report 2022

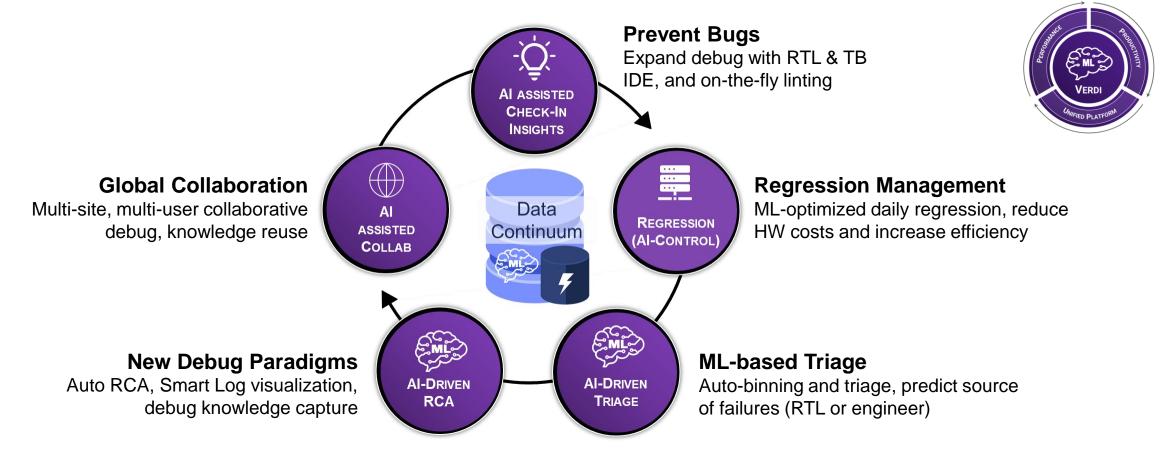

### **AI-Assisted Debug Flow**

Next-Generation Debug: Improves debug productivity up to 10X

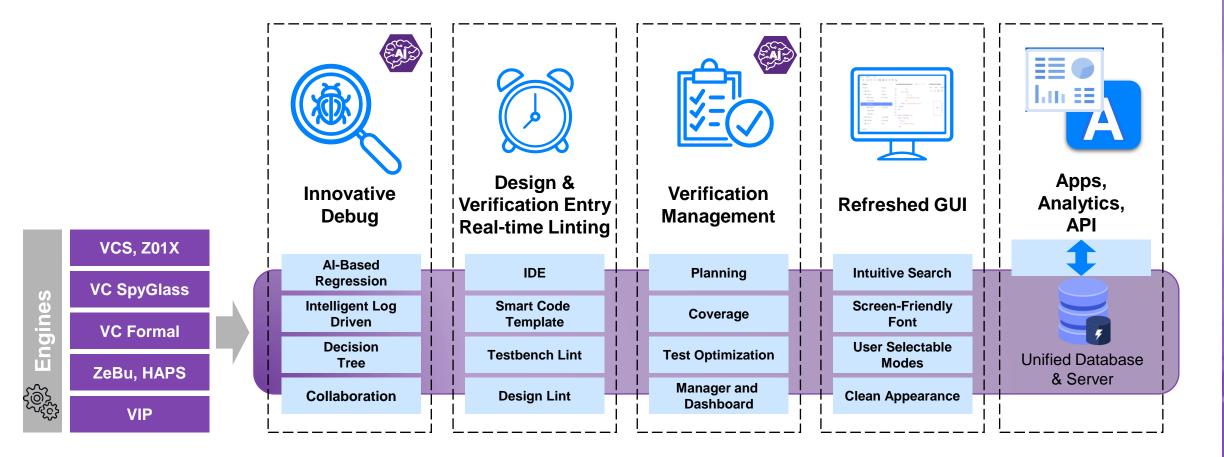

### Introducing Next-Generation Verdi Platform

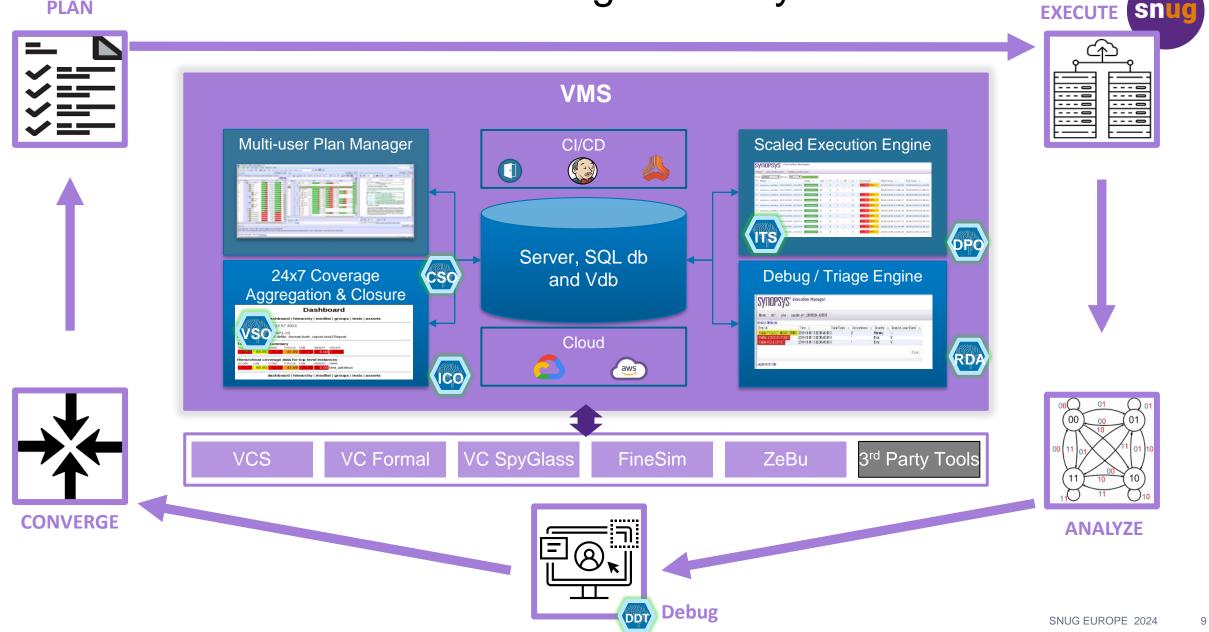

# **Verdi Verification Management System**

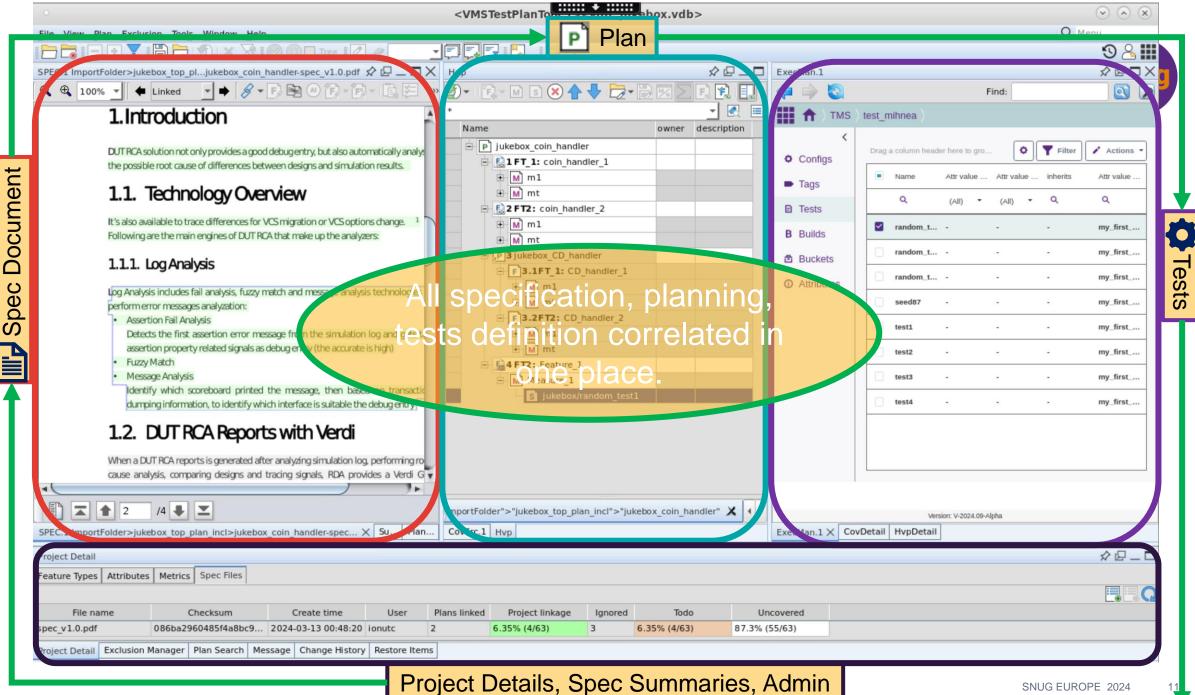

## **Verification Management System**

#### Manager and Dashboard

- Test planning, execution & debug, coverage merge and annotation

- Enables verification data-over-time to be mined for analytics

#### Planner

Coverage

- Multi-user test

scheduling/planning

- Supports change history and restore

- API for automated report generation and updates

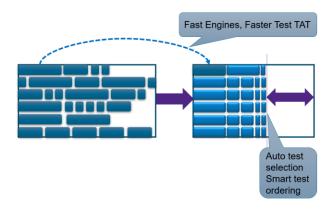

### Runner

- Runs regressions

- Order tests to eliminate

long tail

- Synopsys VCS® engine performance enhancement

- Continuously merges

incoming coverage

- Integrated tagged VDB from ad hoc regression runs

- Can generate moving window merge VDB

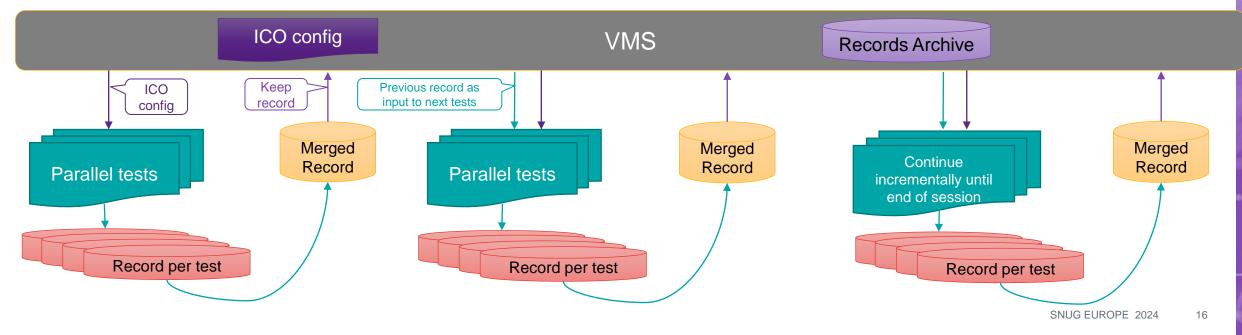

### Verification Management System

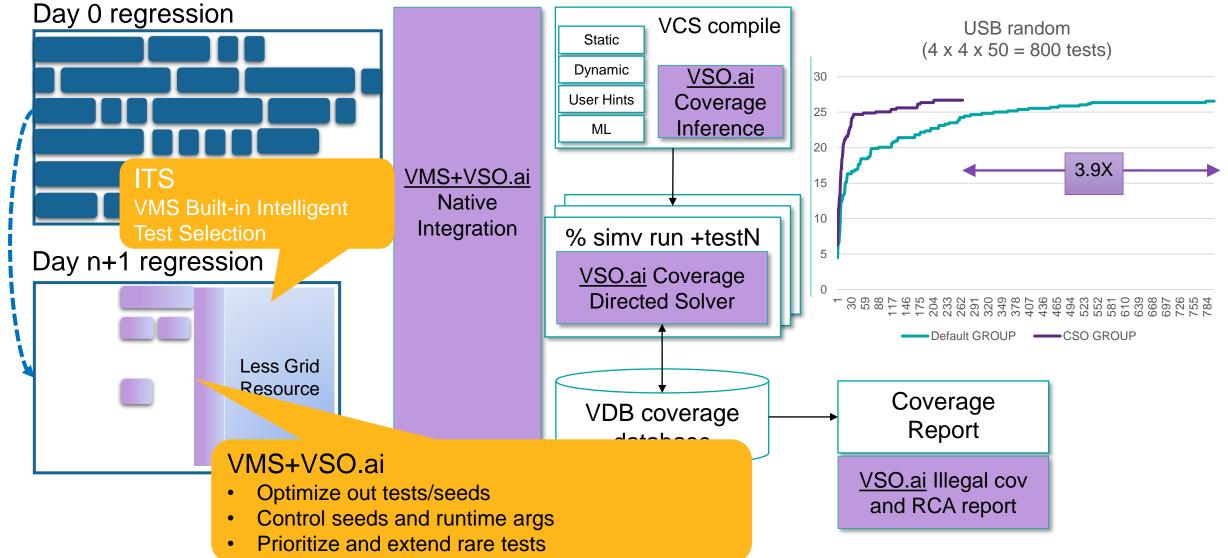

# Optimized Regression with VMS+VSO.ai

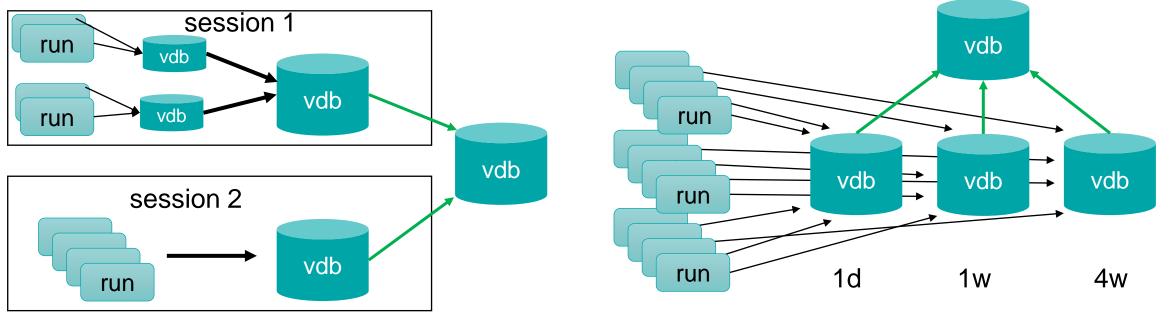

## Standalone aggregation or integrated inside Runner

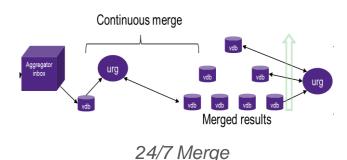

### **Runner Coverage Merging**

- Merges are tied to specific build and runs

- Final merged VDB and session report

- Session VDBs can be combined separately

### **Standalone Coverage Merging**

- VDBs come from multiple builds and runs

- Continuous merge incoming VDBs

- Tree combines results at higher levels

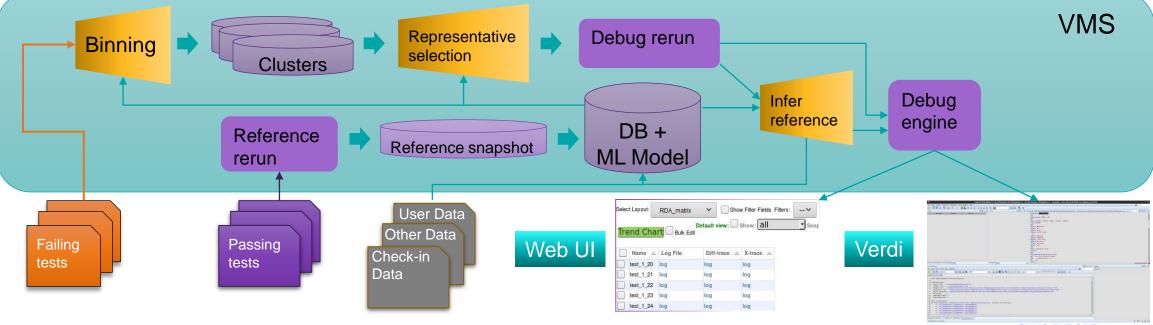

# VMS debug automation

### Native support for debug automation and root cause analysis in regression

### Value Proposition

- Native flow for Binning, Debug, Rerun and Root cause analysis flows

- Open API for custom Binning and Root cause algorithms (e.g. fsdb based, check-in based)

- Open API for DB and ML models

- Reference capture and inference

- Easy enablement in regression flows

#### Flow

٠

- Define Debug engines and policies in easy and generic way in the config file.

- Categorize failing tests into clusters using Error patterns and ML.

- Infer representative tests per cluster for debug.

- Make reference snapshots of predefined passing tests.

- Infer reference snapshot or re-generate it on the spot.

- Run Debug engines as natively embedded step in VMS flow. ٠

- Debug engines results ready at end of the session in web browser UI or Verdi. ٠

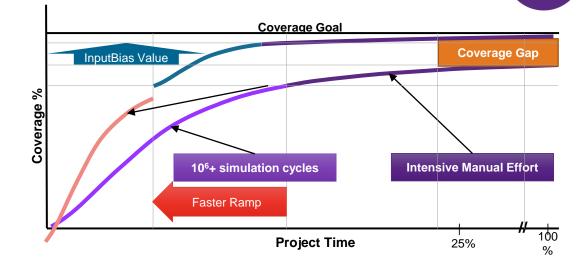

# Native Integration of Intelligent Coverage Optimization (ICO)

Enabling constraints biasing on full regression

- Achieve higher, faster coverage

- Catch more bugs

- Leverage VMS managed infrastructure

- Use simple interface

- Merge server scalable technology

- Run parent session

- Provides consistent debug and retry

- Reports

- Grade results

snuc

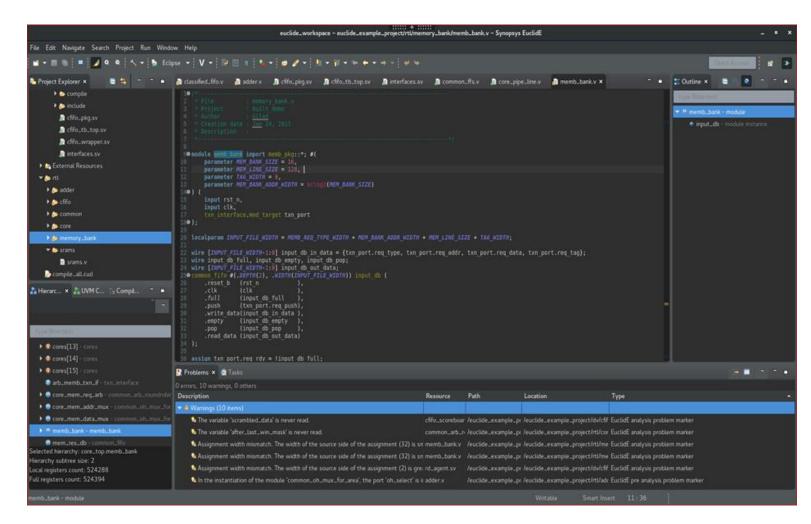

### Euclide Verdi Integrated Design Environment (IDE)

### Euclide IDE

- On-the-fly SVTB linter and design checks

- Content assistance

- Hover information

- Hyperlinks

- Design hierarchy tree

- UVM component hierarchy and more

- Task management

### Euclide IDE

### Advanced Rule Checking as You Type

- High-performance, Highly incremental engine for interactive design and testbench checks

- Complete elaboration, design resolution and pseudo-synthesis even on incomplete code

#### Advanced linter with deeper checks

- Over 1000 rules for RTL and testbench

- Real-time design checks for down-stream EDA tools

- Simulation performance, emulation compliance and synthesis

### Under the hood

| Euclide                                 |                 |                  |  |  |  |  |

|-----------------------------------------|-----------------|------------------|--|--|--|--|

| Design & Testbench Checks               |                 |                  |  |  |  |  |

| Real-time Synthesis and Analysis Engine |                 |                  |  |  |  |  |

| Compilation                             | Elaboration     | Pseudo-synthesis |  |  |  |  |

| RTL & Testbench Methodology             | Error Resilient | Instant Feedback |  |  |  |  |

| Integrated Development Environment      |                 |                  |  |  |  |  |

### Native Integrations and Interoperability

| VCS  | Verdi | VIP              | VC SpyGlass            | VC Formal          |

|------|-------|------------------|------------------------|--------------------|

| ZeBu | HAPS  | RTL<br>Architect | Design<br>Compiler NXT | Fusion<br>Compiler |

### There is also VS Code

| □ ···                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | fg ⊕ ··· ×<br>∨ {} adder module 1<br>··· NUMBER_OF_OPERANDS pa<br>··· MAX OPERAND VALUE para                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <pre>&gt; {} adder module 1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| € man=b*<br> Sfratb<br> -lister<br> Factor<br> Factor<br> Stat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T NUMBER_OF_OPERANDS pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>OPERAND_WIDTH parameter</li> <li>(e) reset_b net</li> <li>(e) clk net</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>(a) pcik net</li> <li>(b) operands full net</li> <li>(c) operands req net</li> <li>(c) operands net</li> <li>(c) operands net</li> <li>(c) flos_empty net</li> <li>(c) flos_data net</li> <li>(c) flos_op net</li> <li>(c) operands_flos generate block</li> <li>(c) operand_flo hierarchical ins</li> <li>(c) operand_st operand_in therarchical ins</li> </ul>                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (e) new operand net<br>() op_dSata_oh_mux hierar 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Filter (e.g. text. **/*.ts Y       P = ^ ×         de(PRE_ANALYSIS_PROBLEM) [Ln 39, Col 83]         ative for including additional fields in Euclide(PRE_ANALYSIS_PROBLEM) [Ln 19, Col 25]         ed to be used instead. Euclide(PARSING_PROBLEM) [Ln 44, Col 4]         b. Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 242, Col 42]         ther the condition is met. Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 242, Col 42]         roject methodology, Euclide(NON_HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 28, Col 7]         er operand and is always 't Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 33, Col 30]         ways 'true', Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 33, Col 63]         26, Col 29] | Tab Size: 4 UTT-8 LF Verilog (2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ati<br>ed<br>the<br>roj<br>er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (PRE_ANALYSIS_PROBLEM) [Ln 39, Col 83]<br>ive for including additional fields in Euclide(PRE_ANALYSIS_PROBLEM) [Ln 19, Col 25]<br>I to be used instead. Euclide(PARSING_PROBLEM) [Ln 242, Col 4]<br>Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 242, Col 42]<br>er the condition is met. Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 242, Col 42]<br>ject methodology. Euclide(NON_HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 24, Col 7]<br>operand and is always 't Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 33, Col 30]<br>ays 'true', Euclide(HIERARCHICAL_ANALYSIS_PROBLEM) [Ln 33, Col 63]<br>6, Col 29] |

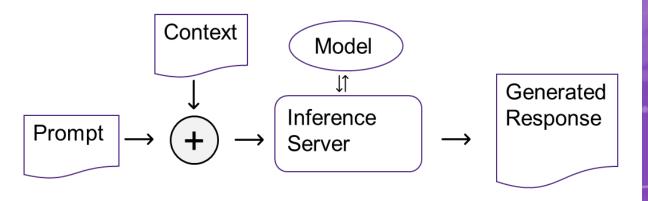

### A look ahead: AI features

| .02<br>.03 /* assert when push and pop are active at the same                                                                                           | e time */                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| .04         .05         AI proposal 0:           .06⊖         AI proposal 1:           .07⊖         AI proposal 1:           .08         AI proposal 2: | <br>/* assert when push and pop are active at the same time */ *                                                                                 |

| Prol                                                                                                                                                    | `ifdef ASSERT_ON<br>wire pw_pop = w_push & w_pop;<br>a1: assert property (@(posedge clk) disable iff<br>(reset) ~pw_pop);<br>`endif // ASSERT_ON |

| Bind                                                                                                                                                    | endmodule                                                                                                                                        |

| Press Ctrl+Space to show Template proposals                                                                                                             | Press 'Tab' from proposal table or click for focus                                                                                               |

- Euclide GenAl client features:

- AI code generation

- Code explainer and documentation generator

- Usage statistics collection

- Compiled project context

- Euclide GenAI backend/model features:

- On-prem LLM specialized in the domain of RTL design and verification

- Clients to easily fine-tune Synopsys model using their data for training

- Evaluation framework to benchmark different models

Summary

• Next-Gen Verdi lets you avoid manual regression debug is tedious

- Automate it with AI and advanced RCA technologies to debug any failing simulations

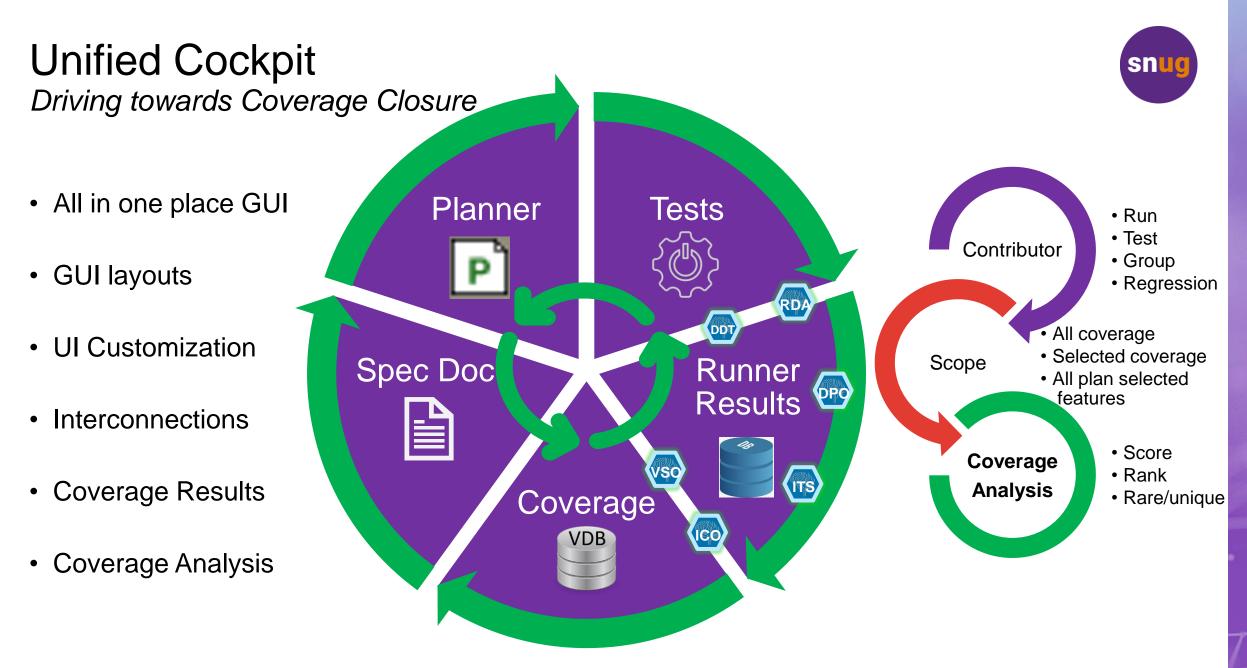

Use VC Execution Manager (VMS) as a Unified Cockpit to create verification plans, manage simulation, gather coverage data and analyze date, optimize regression TAT and achieve faster coverage closure

- Available with Verdi (2023.12)

- Create correct code by construction by using Euclide

- Available with Verdi (2023.12)

# THANK YOU

Our Technology, **Your** Innovation<sup>™</sup>