# Broadening the Horizon – Al-Driven Digital Design Exploration and Implementation

Donnie Chen R&D Engineering, Sr Director Synopsys

## Industry Trends and Challenges

Design talent is on track to face a shortfall of 35% workers by 2030

Growing Design Complexity March To Angstroms 1000x Power Reduction

Multi-Die Design challenges

Semi Talent Shortage

89,000

Demand for US-based design workers in 2030

Demand for workers is expected to rise by ~50% ...

66,000

Supply of US-based design workers in 2030

... While supply will grow by less than 1% annually ...

23,000

Shortage of design workers in 2030, growing by 3,000 per year

... Meaning that demand for design workers will **exceed supply** by nearly 35% in 2030

Demands Significant Increase in Productivity

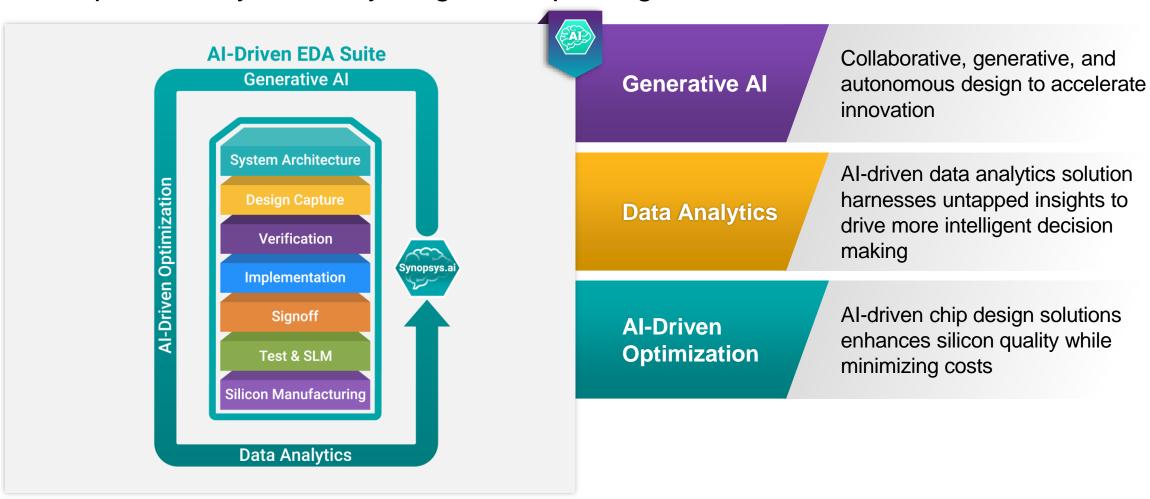

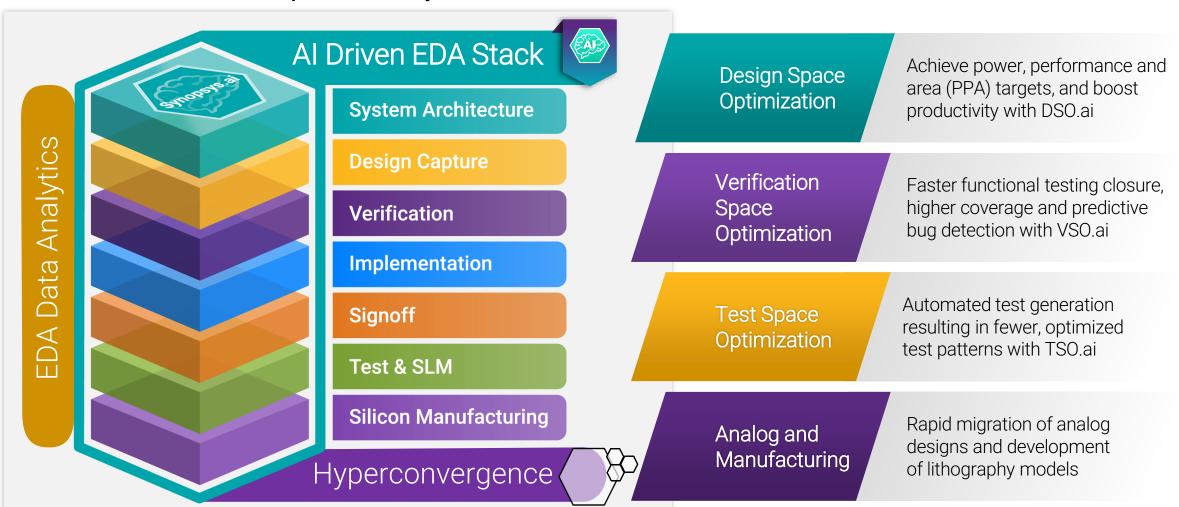

## Synopsys.ai: Industry's First Full-Stack, Al-Driven EDA Suite

Boost productivity for every stage of chip design

## Synopsys.ai: Industry's First Full-Stack, Al-Driven EDA Suite

Delivers unmatched productivity & QoR boost

## Synopsys.ai Copilot

## Key Innovation Areas in Digital Implementation

#### **ADVANCED NODE PPA**

- Seamless new node enablement

- Out-of-the-box PPA entitlement and optimized cost efficiency (PPA-C)

#### **HYPERCONVERGENCE**

- Fastest design throughput with 100+ core scalabilty

- Global RTL-to-GDSII convergence with expanded shift-left optimization

- Native advanced signoff, test, and verification fusion

#### AI / ML-BOOSTED PPA & PRODUCTIVITY

- 2<sup>nd</sup> generation DSO.ai reinforcement learning engine

- Al-guided dynamic implementation flow

- ML-driven predictive flow and big data analytics

#### HIGH PERFORMANCE CORE INITIATIVE

- Boundary-less development with ecosystem team

- Targeted technology innovation and accelerated feature deployment

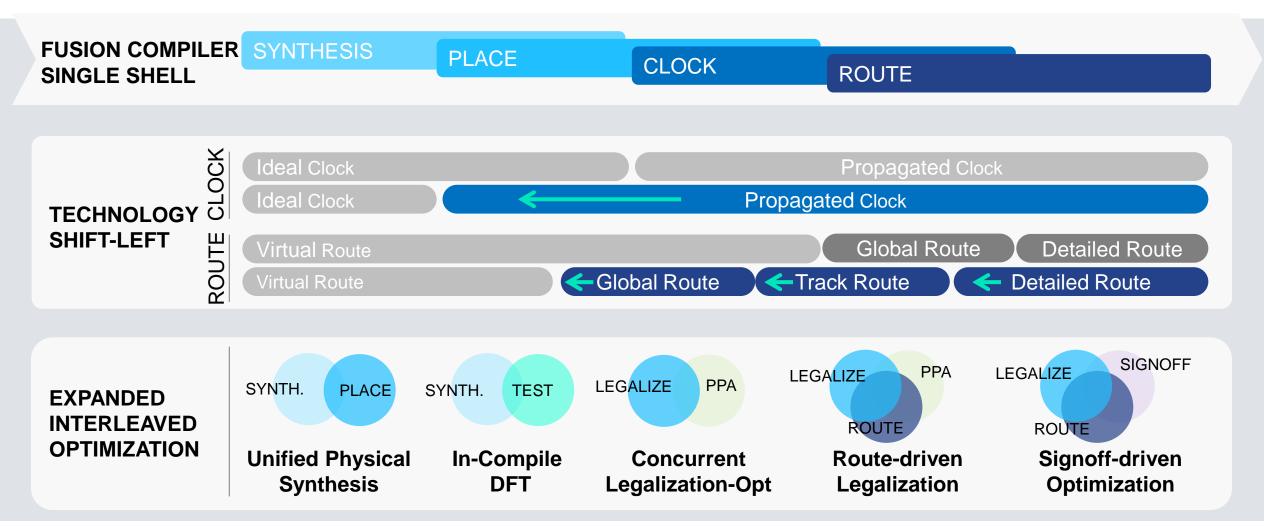

## Endless Opportunities for Hyper-Convergent Flow

Single Shell Enabled Technology Movements

## AI/ML-Driven Productivity

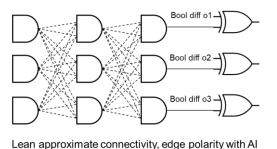

#### **ML-Driven Structuring**

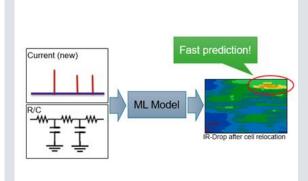

#### ML IR-drop Prediction

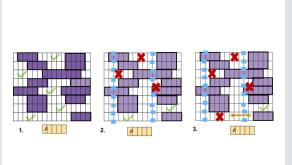

#### ML Legalization & Opt

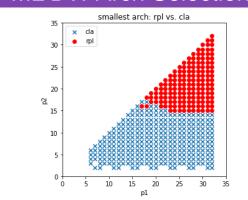

ML DW Arch Selection

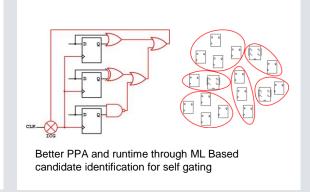

ML Self Gating

Produce exact implementation with BDD/SAT

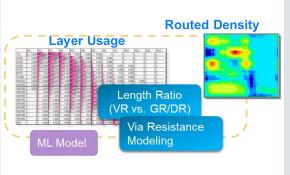

#### ML Pre-route Extraction

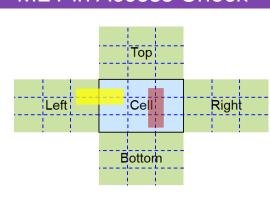

#### ML Pin Access Check

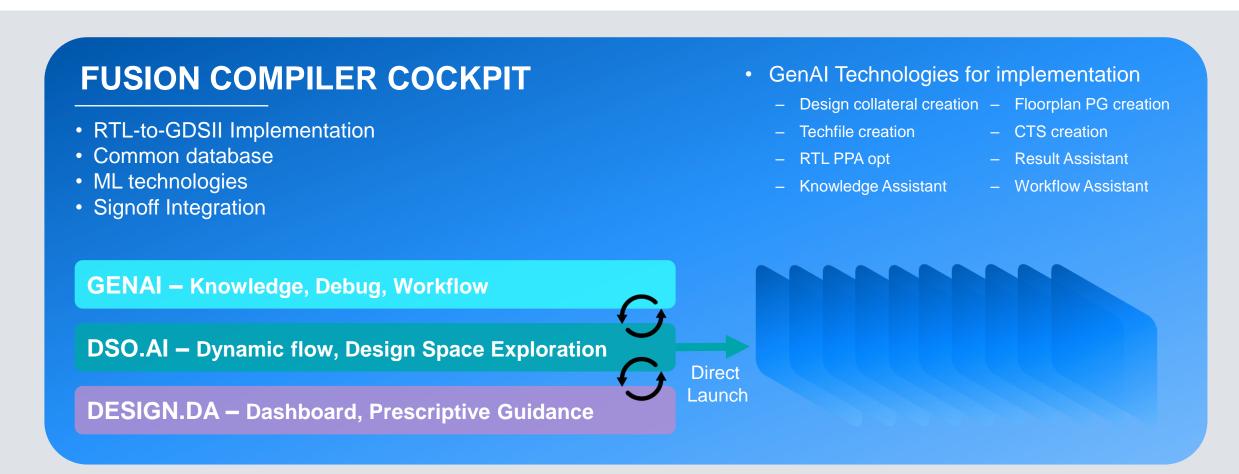

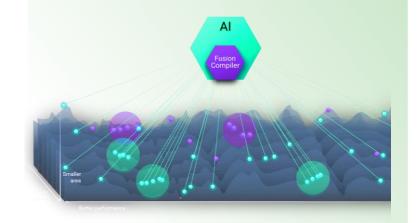

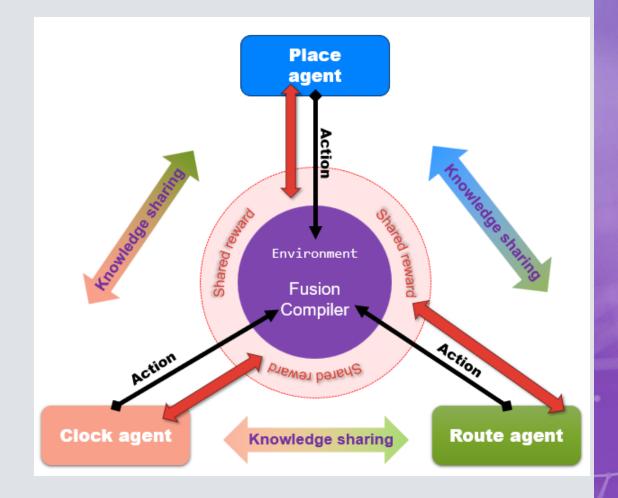

## Al-driven Implementation Platform

Seamless and scalable AI enablement through Fusion Compiler platform

## AI / ML Runtime Acceleration Technologies

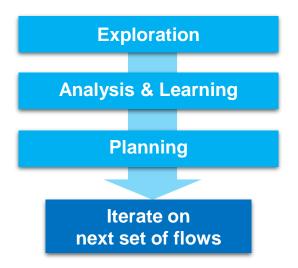

#### **In-Design DSO.ai**

- Learns block-specific behavior at each stage to better configure latter stages

- Dynamically configures sub-flows & engines for next runs & stages

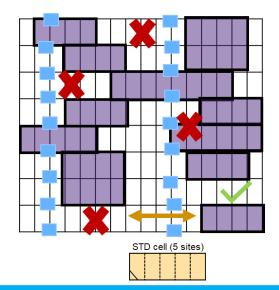

#### ML-Accelerated Concurrent Legalization and Opt

- ML technique to improve picking candidates or locations for optimization

- Adv rules context-aware probability infrastructure and learning model

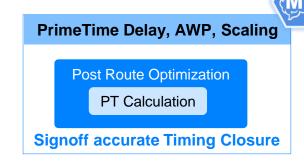

## ML-Accelerated PrimeTime Delay Calculation

- Machine Learning to reduce delay calculation runtime

- Leverage pre-defined model to select worst receiver mode

- Same accuracy as standard PrimeTime Delay Calculation

SYNOPSYS°

## AI-Driven Acceleration Technologies

Flexible multiple objective reinforcement learning (DAC-2022)

Neural network training inspired coarse placement engine (DAC-2019)

Netlist clustering to speed up reward calculation

### 工商時報

COMMERCIAL TIMES

臺大攜手聯發科、至達科技產學研發 超越Google晶片擺置彈性

文謝易晏 2022.05.05

## Al-Driven Productivity Enhancement

#### **Copilot**

Knowledge assistance to answer expert questions

#### **Design Space Exploration**

Al-driven autonomous design optimization

#### **GPU Acceleration**

PPA improvement through placement exploration

## Synopsys.ai Copilot for Next-Level Automation synopsys®

#### Generative AI (LLM) Based EDA Assistants

Knowledge Assistant

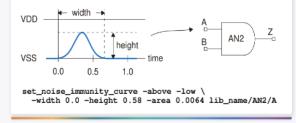

What values can I use to define a custom noise immunity curve?

You can specify the type of noise bump, the coefficient to define the curve and the pin/port to which the curve applies, as in this example:

Answer expert questions

Run Assistant

What is the current state of my timing?

Results from report\_global\_timing show that this design has zero setup violations but 1423 hold violations.

Results from report\_constraints show that the clock group CLK accounts for 786 violations.

Summarize results, suggest next steps

## Answer Expert Question: App Options

How to control max density for doing cell placement?

I found the following documents related to your question:

☐ Controlling the Placement Density ?

♦ DPP > DPP-417 Message ?

Q Resolving and Controlling High Cell Spreading During Congestion Alleviation ?

**Show More**

Based on these documents, here is my response:

To control the maximum density for cell placement, you can use the place.coarse.max\_density application option.

By setting this option to a specific value between 0 and 1, you can control how densely the tool can place cells in the design.

For example, you can set the maximum density value using the following command:

fc\_shell> set\_app\_options -name place.coarse.max\_density -value 0.6

This command will set the maximum density to 0.6, allowing you to control the density of cell placement in the design. Remember that setting a higher value allows cells to clump together more densely, while setting a lower value helps avoid cell clumping.

List all app options related to placement density control

I found the following documents related to your question:

- place.common.pnet\_aware\_density Application Option > Examples ?

- ★ place.common.pnet\_aware\_density Application Option > Examples ?

- ★ place.coarse.max\_density Application Option ?

#### Show More

Based on these documents, here is my response:

- place.coarse.auto\_density\_control

- place.coarse.max\_density

- place.coarse.congestion\_driven\_max\_util

- plan.place.auto\_max\_density

- place.floorplan.density\_aware\_hard\_movebounds

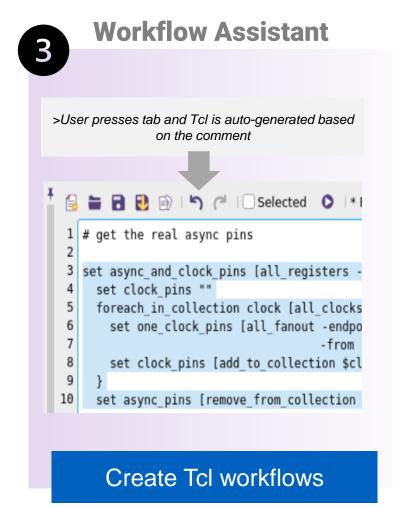

## Tcl Script Assistance

How to change color of register cells?

I found the following documents related to your question:

- \* remove\_colors Command > Options and Arguments (?)

- ★ remove\_colors Command > Options and Arguments ?

- place.legalize.libcell\_based\_color\_shifting Application Option ?

#### **Show More**

Based on these documents, here is my response:

To change the color of register cells, you can use the following script:

```

gui_change_highlight -remove -all_colors

gui_change_highlight -add -color blue -collection [all_registers]

```

This script will remove all existing colors and then highlight all register cells in blue.

How to write tol to traverse all cells?

I found the following documents related to your question:

- Q How Do I Get All the Cells in a Specific Site Row? ?

- □ rpt\_cell Overview ?

- □ rpt\_cell Listing and Output Example ?

#### Show More

Based on these documents, here is my response:

To traverse all cells in a design using Tcl, you can use the following script:

```

set all_cells [get_flat_cells -hierarchical *]

foreach_in_collection cell $all_cells {

set cell_name [get_attribute $cell full_name]

# Perform actions on each cell here

# For example, print the cell name

puts $cell_name

}

```

This script first retrieves all cells in the design using the get\_flat\_cells command and stores them in the all\_cells collection. Then, it iterates over each cell in the collection using the foreach\_in\_collection command, retrieves the full name of the cell, and performs any desired actions on each cell. In this example, it simply prints the name of each cell.

Artificial Intelligence Helps the Entire Team Perform Like Experts

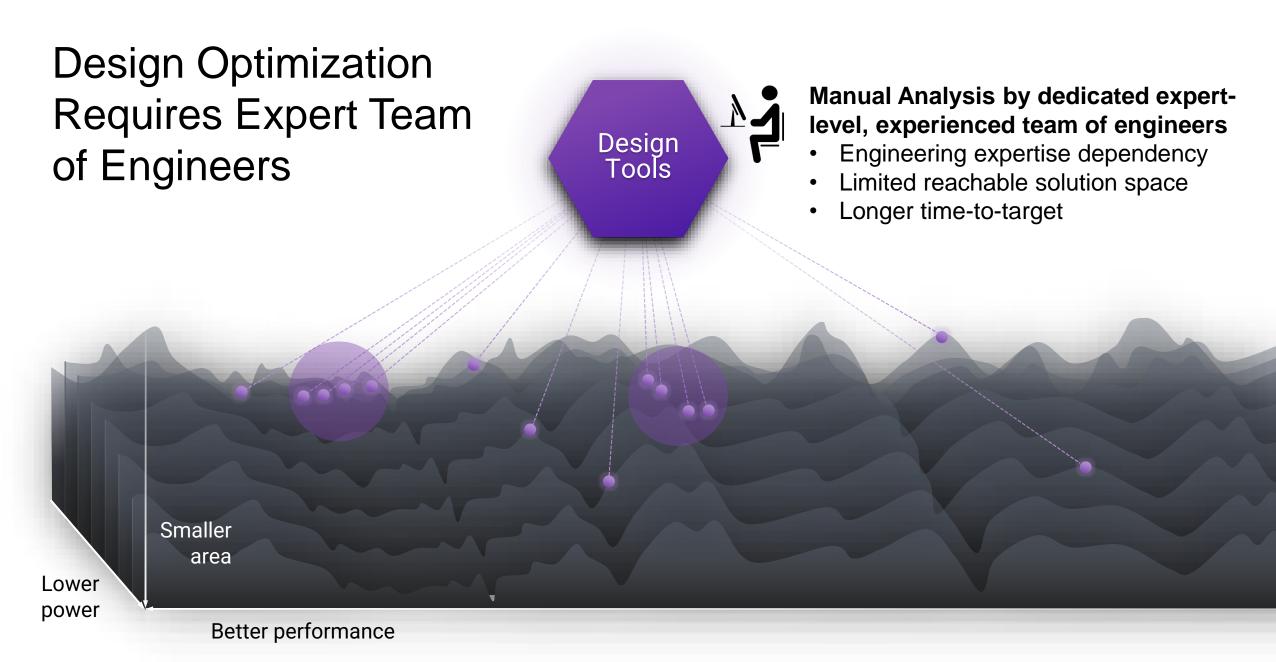

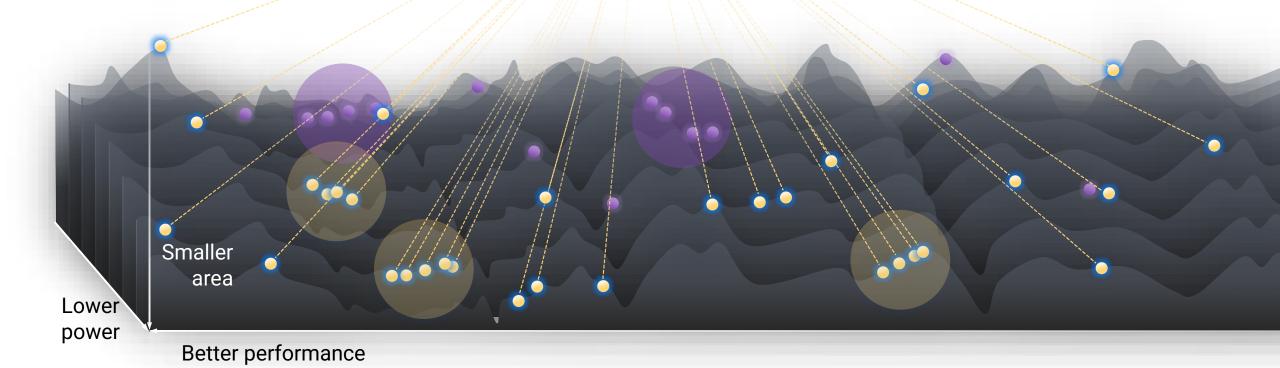

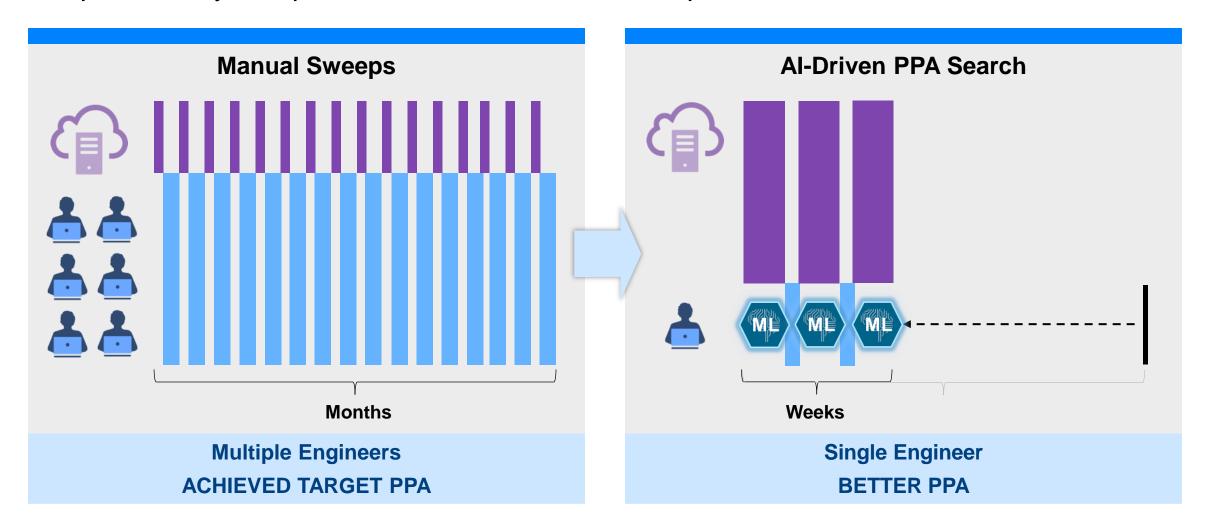

#### **Al-driven Autonomous Design Optimization**

- Minimal Engineering expertise dependency

- Extended reachable solution space

- Shorter time-to-target

## Synopsys DSO.ai — Al-driven Digital Design

World's First Autonomous Design Space Optimization

## Al-Driven Design Space Optimization (DSO)

10X productivity compared to traditional, manual exploration

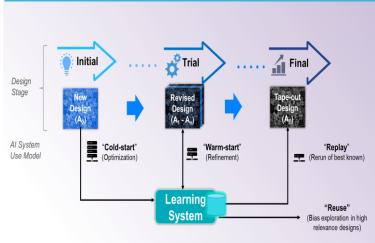

## DSO.ai Use Models in the Implementation Flow

PPA Push, Project Reuse, Early Feasibility

## PPA Push

- Unmatched PPA with Design Space Optimization

- Up to 20% better quality of results

#### Project Reuse

- Learning and reuse on derivative blocks/designs

- 3x reduction in compute resources

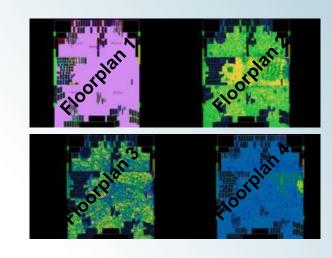

#### Early Feasibility

- Multiple floorplan configuration exploration

- 5x productivity improvement

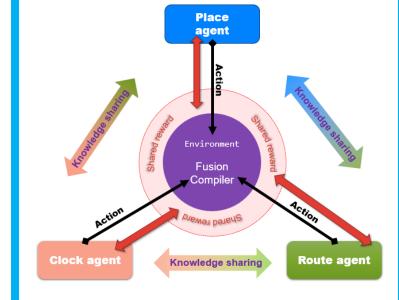

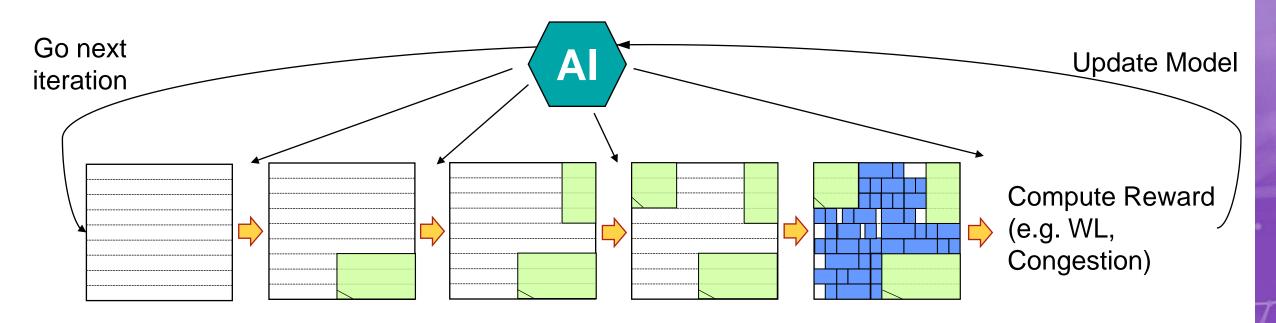

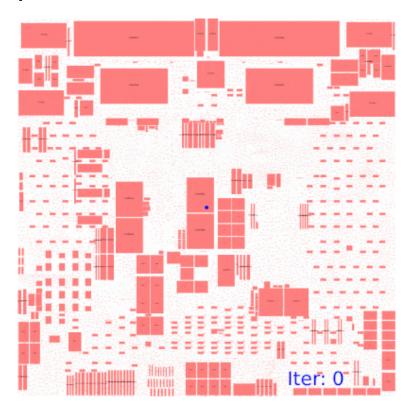

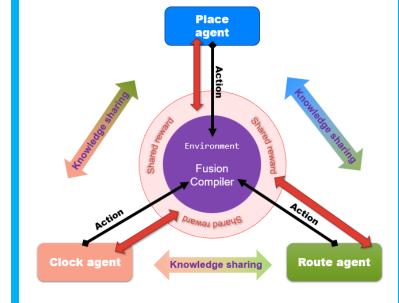

## Al in Floorplanning and Placement

- Reinforcement learning placement

- Intelligent agents take actions to maximize the cumulative reward

- Mirhoseini et al. "A graph placement methodology for fast chip design," Nature 2021

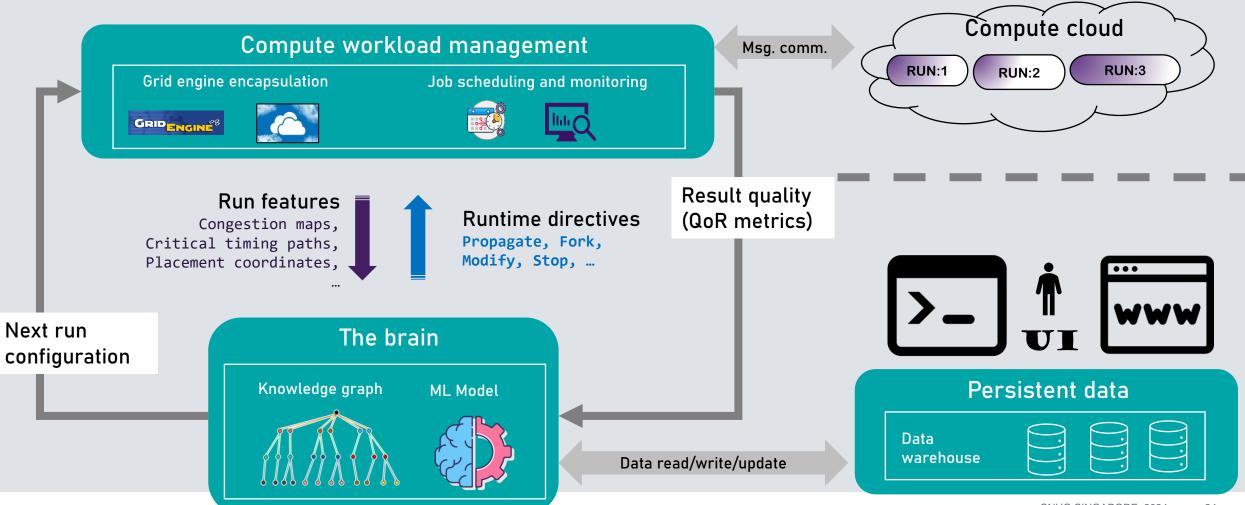

### Architecture

A scalable distributed system with continuous learning

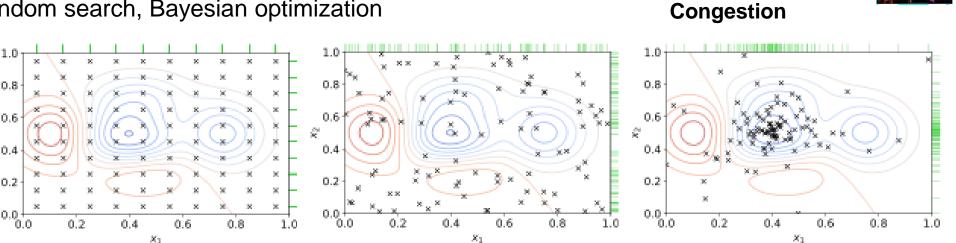

## Hyperparameter Optimization

#### Parameters

- Cell density, utilization, module location, floorplan styles

- Multi-objective efforts (congestion, timing, power)

#### Approaches

- Grid search, random search, Bayesian optimization

**Timing**

https://en.wikipedia.org/wiki/Hyperparameter\_optimization

SYNOPSYS<sup>®</sup>

25

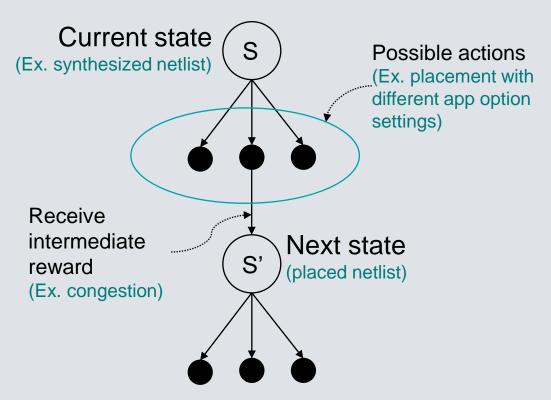

## Reinforcement learning

Specialized RL agents operating at the flow level

### Sequential decision making

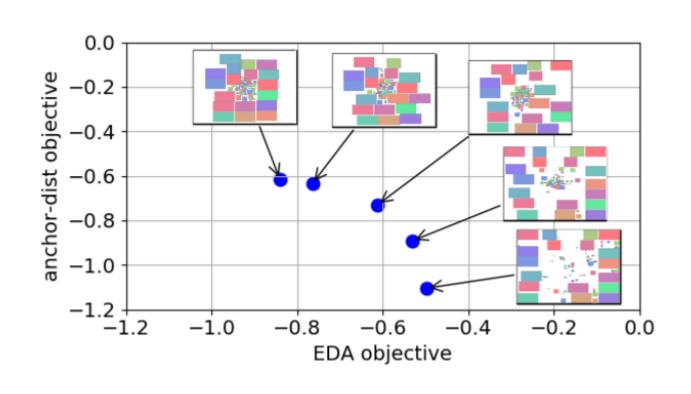

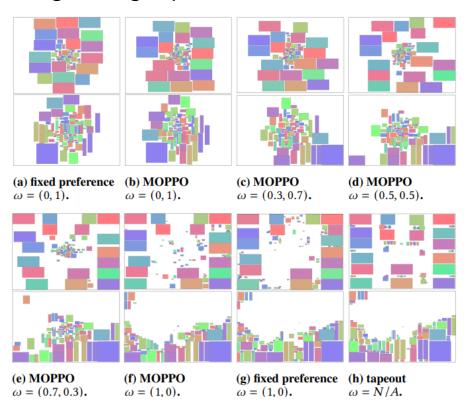

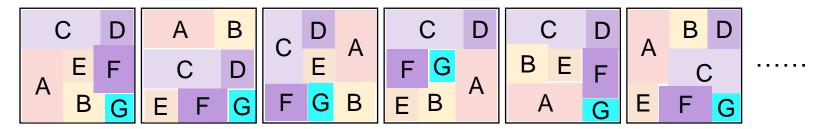

## Flexible Multiple-Objective Reinforcement Learning for Chip Placement (Source: DAC 2022, MediaTek/Maxeda)

- Fixed-weighted models cannot generate the diversity of placement

- Need flexible multiple-objective reinforcement learning using a single pretrained model

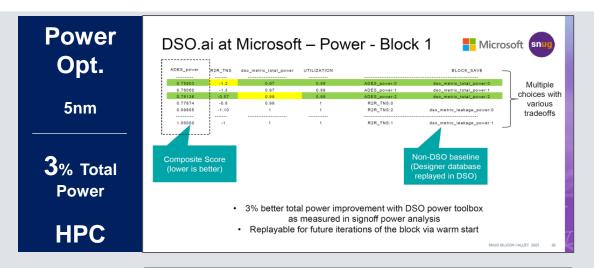

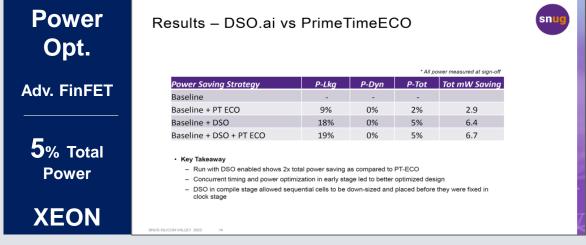

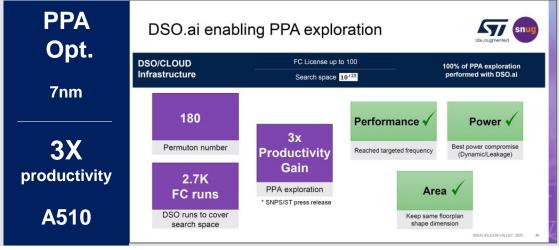

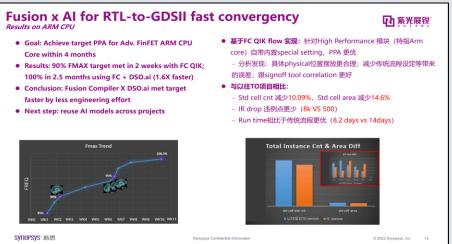

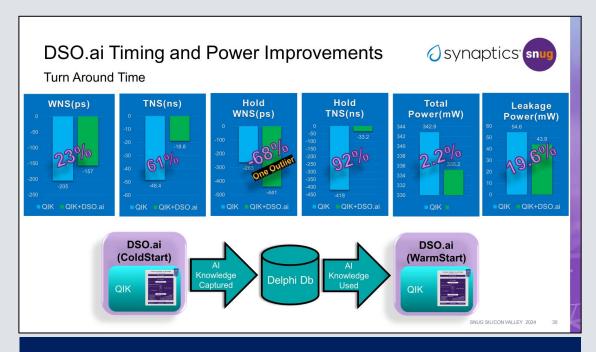

## Customers Share Success with Production Deployment

Results from Al Track, SV SNUG 2023 Proceedings, customer engagements

## Recent Customer Success with Broad Applications

Results from Al Track, SV SNUG 2024 Proceedings

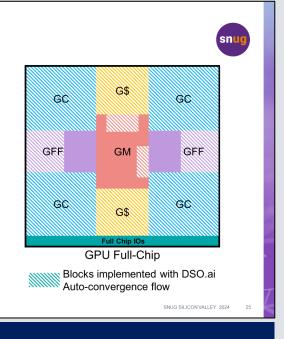

## Results – Setup and Scope • Setup

- Fusion Compiler T-2022.03-SP5\* Build

- DSO.ai U-2022.12-SP5\* Build

- 2-3X higher disk allocation + additional compute resources

- Selected blocks for DSO.ai based optimization

| <b>Unique Blocks</b> | Selected Blocks |

|----------------------|-----------------|

| 8                    | 8               |

| 15                   | 7               |

| 1                    | 1               |

| 27                   | 5               |

|                      | 8               |

- Contribution to Full-chip

- ~75% of the Die-area

- ~80% of the Total Power

GPU Power Opt. ~75% Of Full Chip Die-area

Synopsys ARC CPU Migration 60% Timing; 20% Leakage Improvements

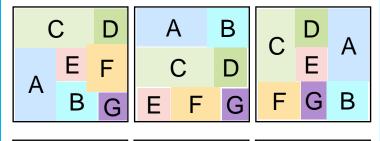

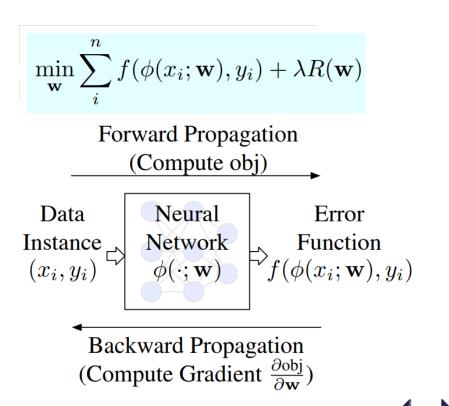

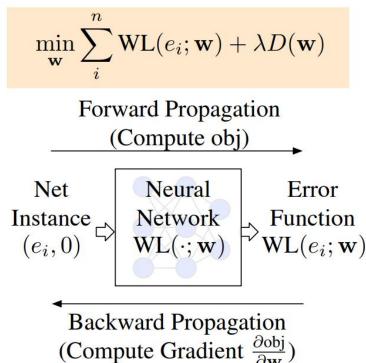

## Analogy between VLSI Placement and NN Training

• Lin et al., DAC 2019; 10x-50x faster for runtime speedup

Train a neural network

Solve a placement

### **GPU-Accelerated AI-Driven Placement**

Expand search space by 15x to 20x with autonomous design space optimization

#### Core placement has more than 10X speedup.

| Design                          | Tech Node<br>(nm)          | Number Of<br>Placeable<br>Standard<br>Cells | I NIIMPER ()T | CPU-driven Placement 16-Cores x86 CPU | GPU-driven<br>Placement<br>NVIDIA A100 80GB | Comparison |

|---------------------------------|----------------------------|---------------------------------------------|---------------|---------------------------------------|---------------------------------------------|------------|

| GPU Streaming<br>Multiprocessor | 3nm Variable<br>Row Height | 1.4M                                        | 20            | 12.5 Minutes                          | 38 secs                                     | 20X        |

| Automotive CPU                  | 12nm                       | 2.9M                                        | 200           | 18.7 Minutes                          | 82 secs                                     | 14X        |

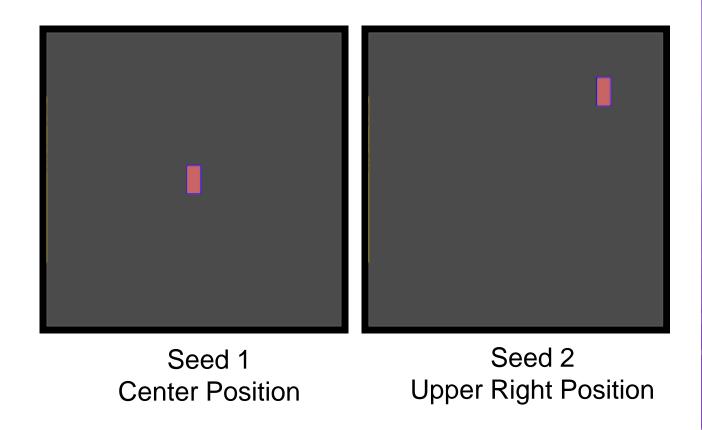

- Explore various module placements by autonomous design space optimization.

- GPU-accelerated placement can explore more placement possibilities in the same runtime.

- Initial seed exploration

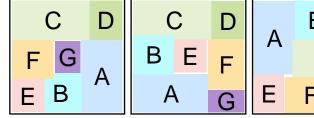

## Placement Exploration

- Source: NVIDIA Technology Blog

- Agnesina et al., ISPD-2023

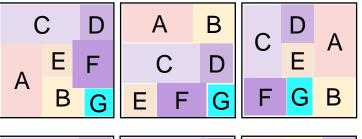

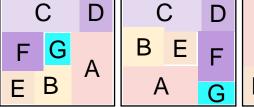

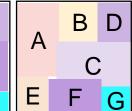

## Placement Exploration

#### Seeds

#### **Placement Results**

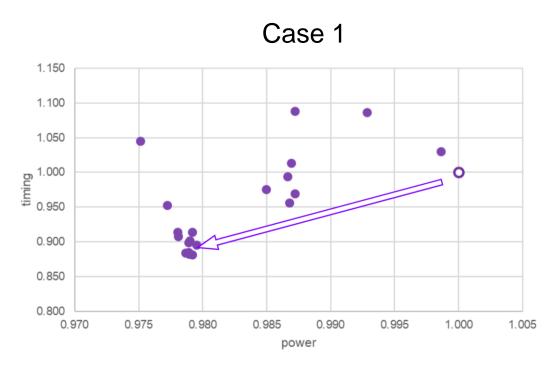

## PPA Improvement through Placement Exploration

Achieved Better Timing and Power

## Recap: Al-Driven Productivity Enhancement

#### Copilot

Knowledge assistance to answer expert questions

#### **Design Space Exploration**

Al-driven autonomous design optimization

#### **GPU Acceleration**

PPA improvement through placement exploration

## Synopsys – Leading the Era of Al-driven Chip Design

2020

Synopsys introduces DSO.ai, world's first Al application for chip design

2021

World productivity record:

10 blocks-9% total pwrONE engineer

2022

Record adoption:

9 of Semi Top-10

100% Better Results

2023

Synopsys.ai

Industry's first Al driven EDA suite – Design, test, verification, manufacturing

DSO.ai named Innovative Product of the Year by EETimes

Wired: World's first **Al-designed** chip design

Al-designed Chips cross

100 Commercial Tapeouts with DSO.ai

Al-designed Chips cross **450 Commercial Tape-outs** with DSO.ai