#### CONFIDENTIAL INFORMATION

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

#### IMPORTANT NOTICE

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

### Agenda

- Challenges at advanced nodes

- Why IC Validator

- Customer case studies

- Technology differentiators

- ESD solution

- License package

## Challenge

## Solution

## Where to Eat?

## Long Cai Fan Queues

## MAXIMISE YOUR CAI PNG ORDER

#### ORDER MOST EXPENSIVE DISH FIRST

Seafood or Fish > Meat > Veggies

#### LINGER WHEN CHOOSING

Keep pointing and you might get more

#### ASK FOR "A LITTLE MORE RICE"

Not "Add Rice"

#### CHOOSE DISHES CLOSE TO EACH OTHER

Make it easier for the person scooping

#### LOOK FOR DISHES THAT'RE RUNNING OUT

Might get everything + something extra!

#### ORDER LESS QUANTIFIABLE DISHES

Sweet & Sour Pork vs a whole Pork Cutlet

or get the economic rice auntie to like you...

## Disappearing Food

## Sharing Bubble Tea??

## Some Other Challenges

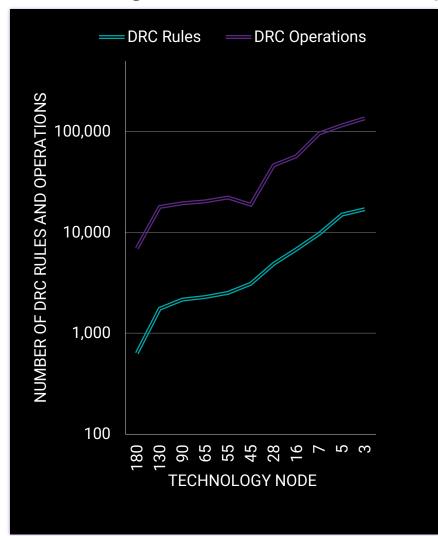

#### Challenges at Advanced Nodes

Increasing Rules Increases Complexity and Runtime

- Multi-day runtimes due to increasing rules, complexity

- Large N3 SoC runtime > 24 hrs with 1000 cores

- Debug is complex and time-consuming

- Require guidance to find root cause of DRC, LVS and Antenna issues

- Extensive hardware compute requirements

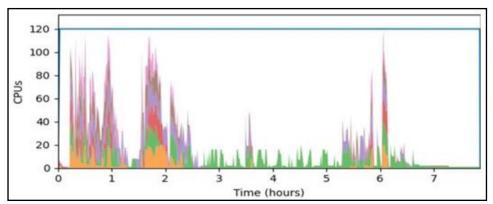

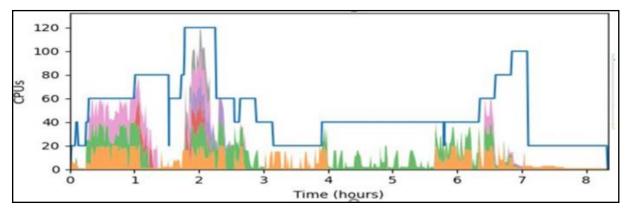

#### Why IC Validator

**Scalability to 4000 Cores**

**Overnight Runtimes**

**40% Compute Savings**

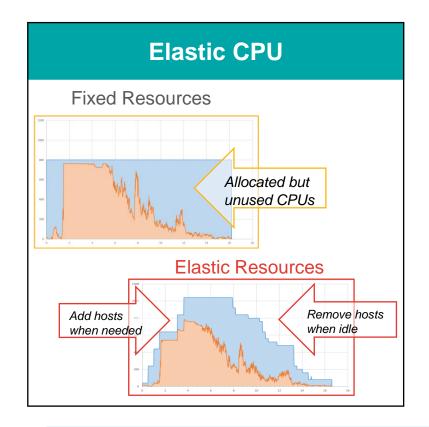

Elastic CPU: Optimized use of compute

Cloud: PPU license model for peak demand

**Explorer DRC & LVS**

Isolate key design weaknesses within hours

2X Faster Debug Convergence

Find root cause of issues quickly to accelerate TAT

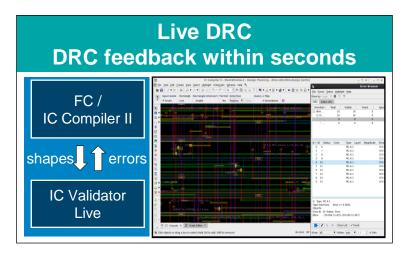

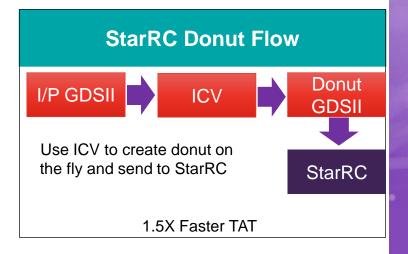

**Fusion**

Signoff DRC/Fill, Live DRC and PGA in FC and StarRC earlystart flow

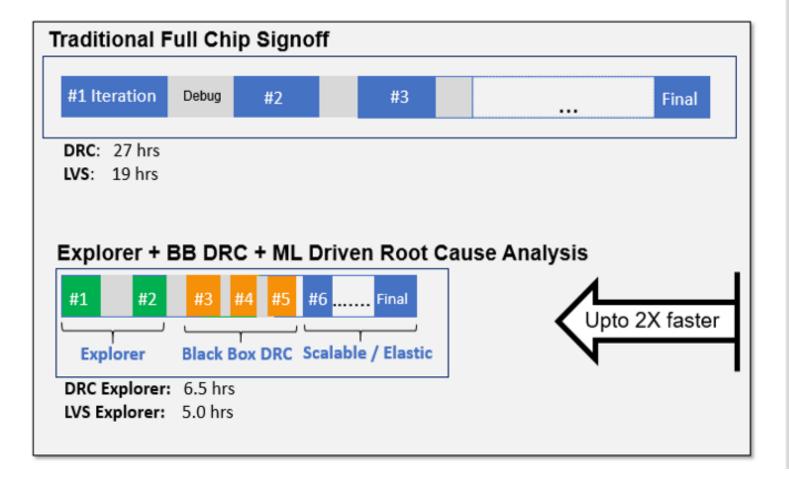

#### 2X Faster with ½ Resources

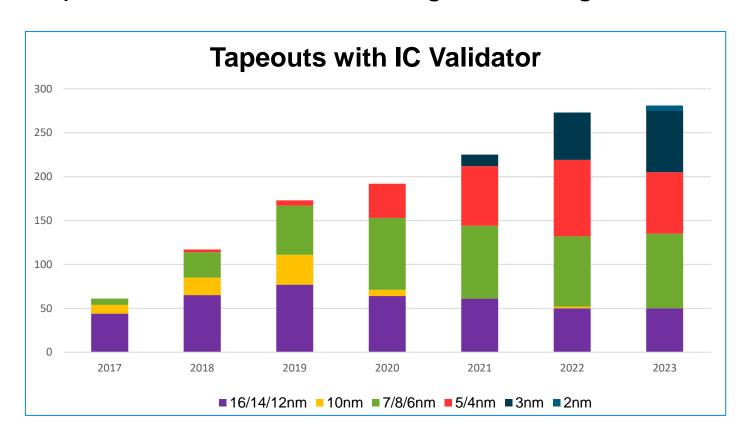

#### IC Validator Signoff Momentum

Source: TSMC OIP, DDTS, SNUG Presentations, Webinar

100+ 3nm

Tapeouts/Testchips

**80+5nm** Tapeouts/Testchips

60+ 12nm

Tapeouts/Testchips

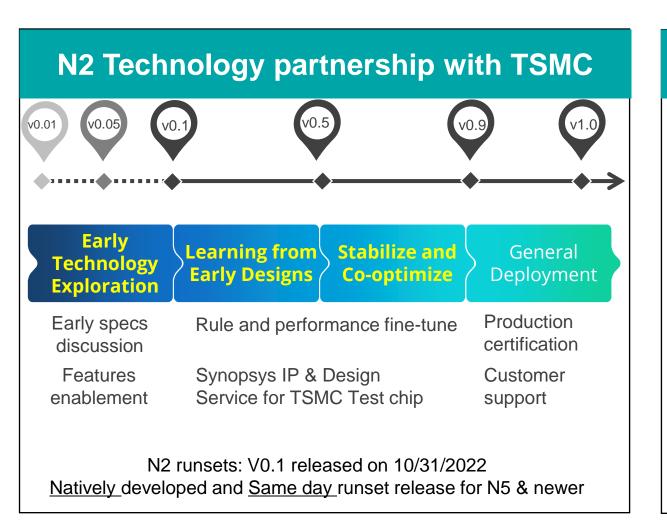

#### Strong Foundry Collaboration

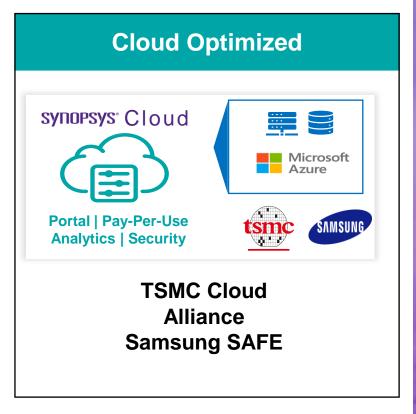

Golden Signoff Certified at TSMC, Samsung, IFS and GF

#### **TSMC** N2 N12 N16 N20 N22 N45/N40 N65/55 Natively developed and Same day runset release for N5 & newer

| Samsung Foundry                                           |         |     |     |      |

|-----------------------------------------------------------|---------|-----|-----|------|

|                                                           | Process | DRC | LVS | Fill |

|                                                           | 14A     |     |     |      |

|                                                           | 2nm     |     |     |      |

|                                                           | 3nm     |     |     |      |

|                                                           | 4nm     |     |     |      |

|                                                           | 5nm     |     |     |      |

|                                                           | 7nm     |     |     |      |

|                                                           | 8nm     |     |     |      |

|                                                           | 10nm    |     |     |      |

|                                                           | 11nm    |     |     |      |

|                                                           | 14nm    |     |     |      |

|                                                           | 18nm    |     |     |      |

|                                                           | 28nm    |     |     | • ,  |

| Multiple 3nm or newer projects signoff using IC Validator |         |     |     |      |

22nm processes

100% Intel process projects signoff with IC Validator

#### TSMC Collaboration Beyond Enablement

#### Tool of choice for TSMC IP team

- Primary DRC / LVS Signoff at DTP

- Foundry tapeouts for pathfinding and IP silicon validation

- TSMC tapeouts 6 at N2 and 24 at N3

- 100+ tapeouts at N3 across all customers

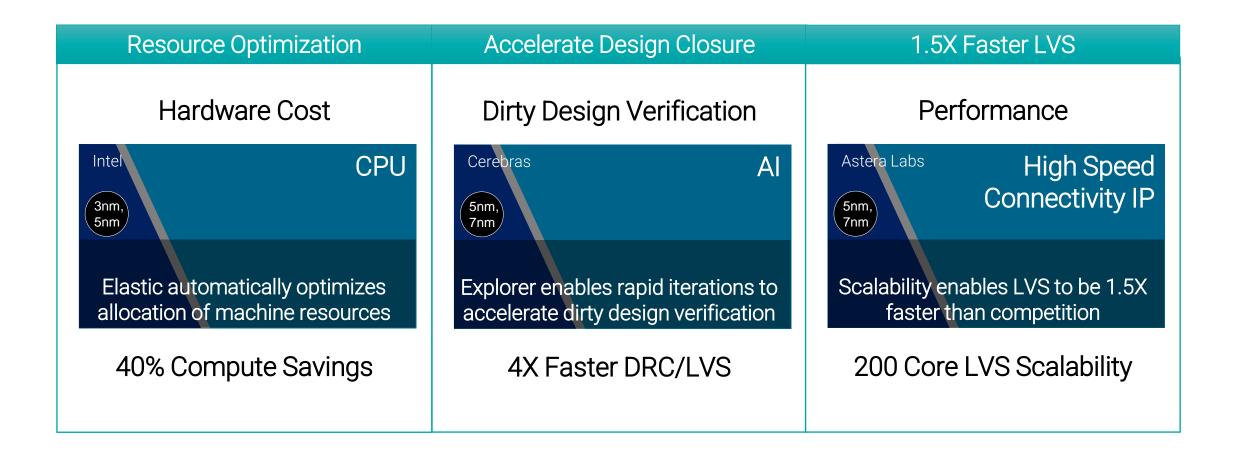

#### Key Signoff ICV Wins

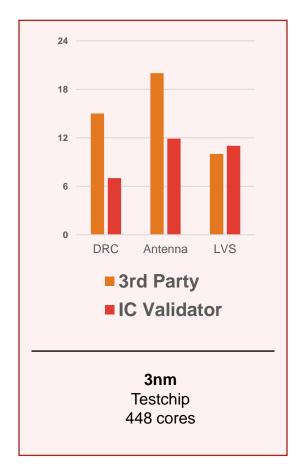

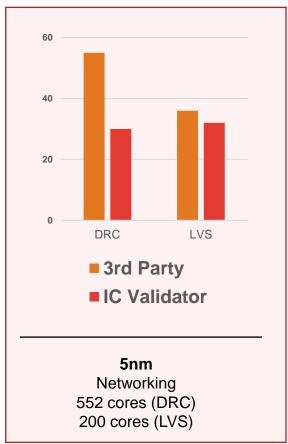

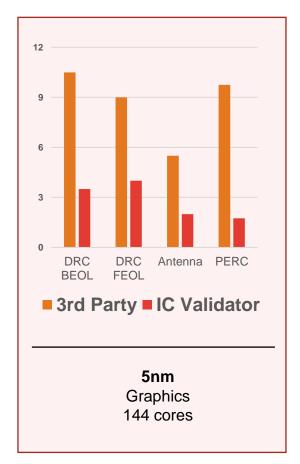

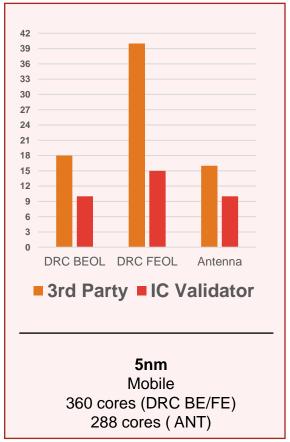

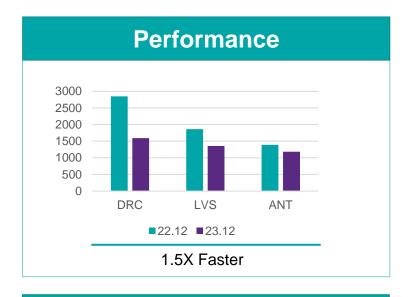

#### Performance Leadership at Advanced Nodes

#### Recent Benchmark data

1.5X faster on DRC, PERC and ANT

#### Scalability Technology Leadership

2X Speed-Up Massive Parallel

Processing

Memory aware

Smart Scheduler

40%

Compute Savings

Eliminate queue time Lower peak license usage 40% Immediate on-dema use for peak

TTR Improvement

#### IC Validator 2023.12 Release Highlights

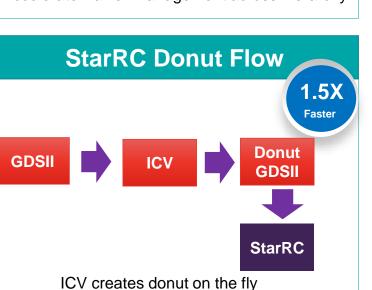

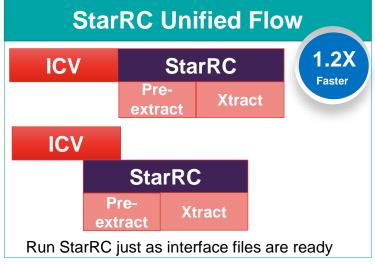

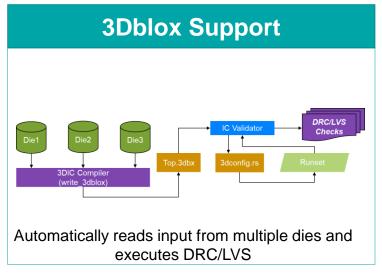

#### Faster Design Convergence with Fusion and StarRC

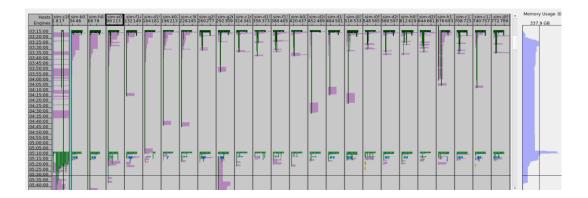

#### Customer Case Study: Peak Memory on N5 Design

**DRC** Default Peak Memory: 4T

After Improvements: 337G

Antenna Default Peak Memory: 4T After Improvements: 200G

10X DRC and 20X Antenna Peak Memory Reduction

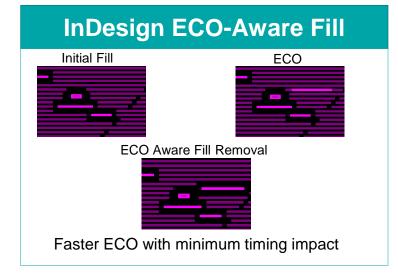

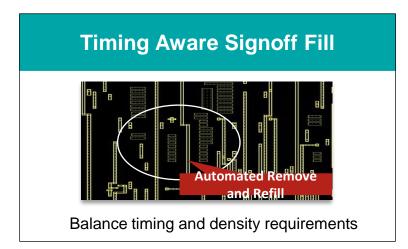

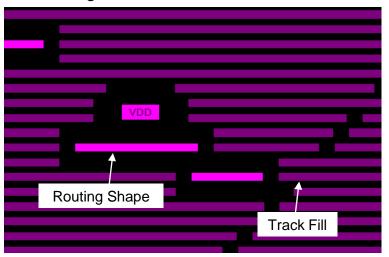

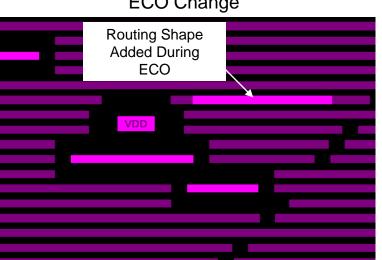

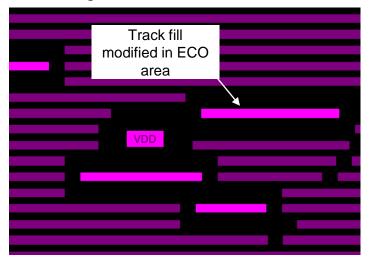

#### InDesign ECO-Aware Fill Removal For DRC Clean Results

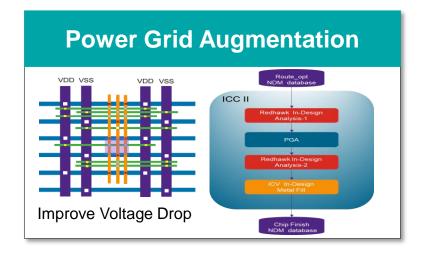

- Automatic track fill removal in ECO areas

- Applicable to normal track fill and power grid augmentation (PGA) flows

- No need to generate DRC error markers with signoff\_check\_drc, check\_routes, or check\_pg\_drc

Design After Initial Track Fill Insertion

ECO Change Routing Shape Added During

Design After ECO Aware Fill Removal

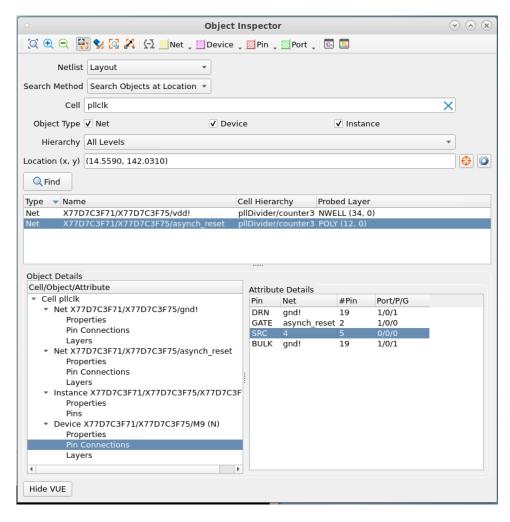

#### LVS VUE Object Inspector

- Direct Access to extracted netlist data for debugging LVS ERC or complex LVS errors

- Probe the layout to get a list of netlist objects located at that point

- Find detailed information about items like pin connections, properties, or layers

- Flexible highlight controls

- Trace Paths through devices

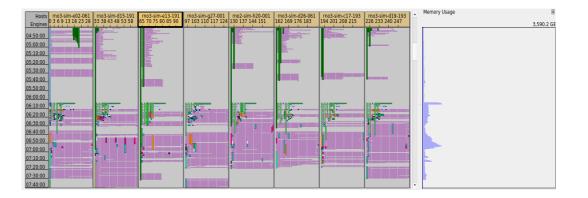

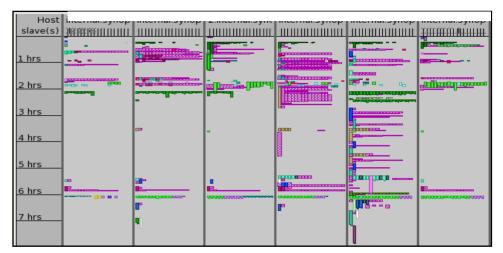

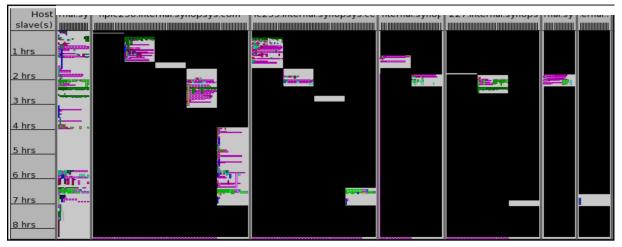

#### Customer Case Study: Elastic CPU for LVS on N5 Design

Normal run: Wall time 7:50Hours

Allocated CPU Hours: 943.7

Elastic run: Wall time 8:20Hours

Allocated CPU Hours: 410

50% resource and license savings with 5% overhead in wall time

#### SYNOPSYS® snug

#### Customer Case Study: 7nm 650 mm<sup>2</sup> design

Rapid verify → fix turns during chip integration

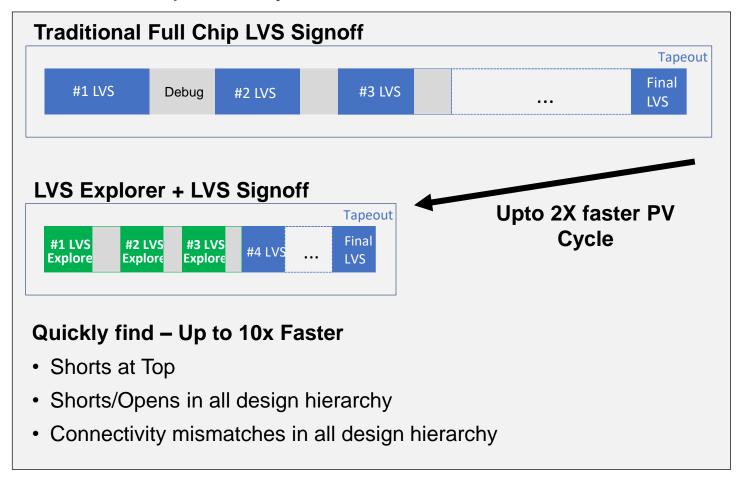

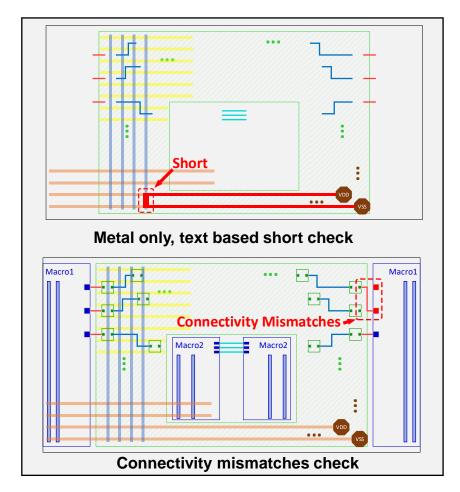

#### LVS Explorer – 4X Faster

- Shorts/Opens at Top and all design hierarchy

- Connectivity mismatches

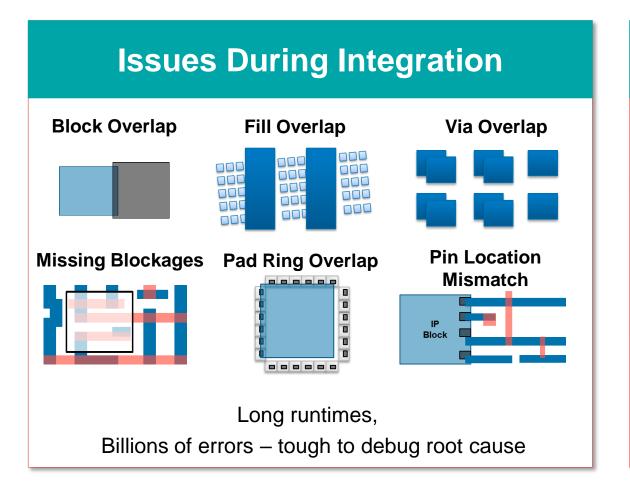

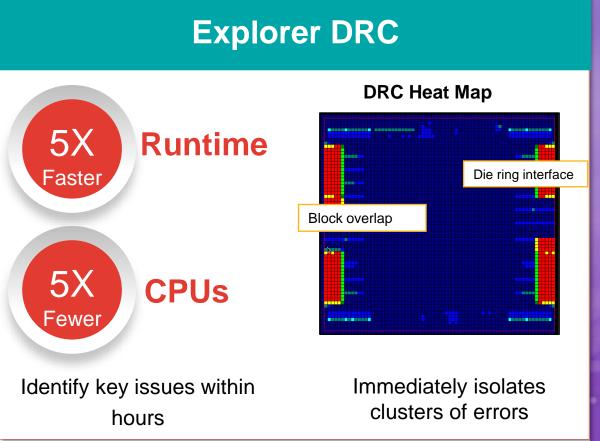

#### DRC Explorer – 4X Faster

- Fill/Block/Via overlaps

- · Pin Location Mismatches

#### Black Box DRC – Decrease Noise

Filter known macro errors

#### **Root Cause Analysis**

Identify structural design issues

#### Scalable / Elastic

Improve compute / license efficiency

#### Explorer DRC Identifies Key Design Issues Within

Howypsive technology for dirty design verification

#### Explorer LVS: 2X Faster LVS Signoff Cycle

Able to do rapid verify → fix turns

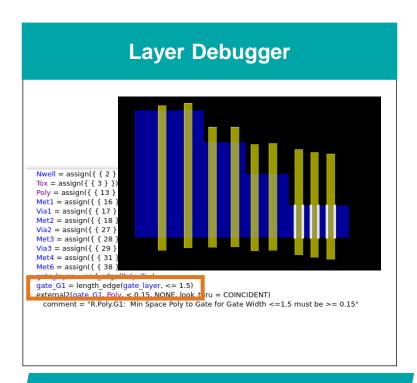

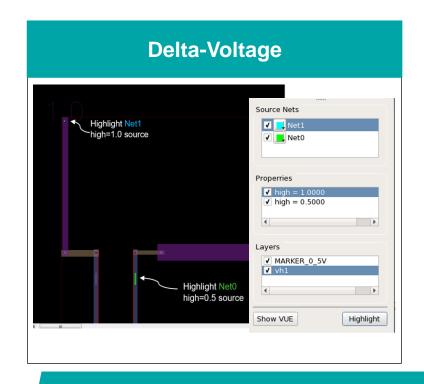

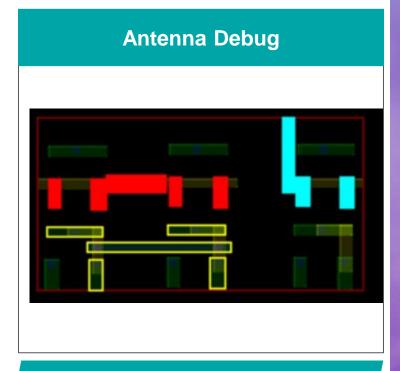

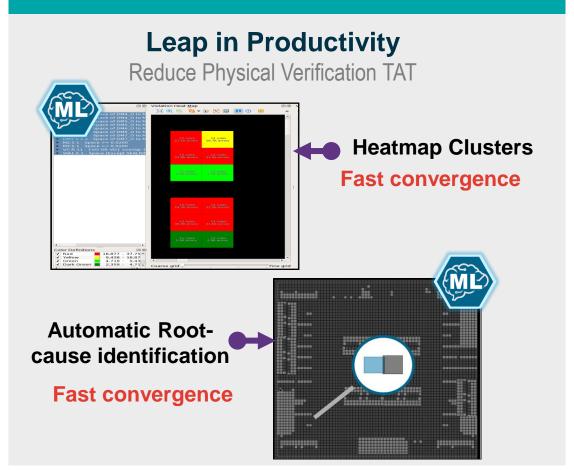

#### Unparalleled Innovations to Accelerate Debug

Highlight intermediate layers out-of-the box to debug complex rules

Highlight entire net with voltage sources for faster debug

Highlight multiple nets for easier debug

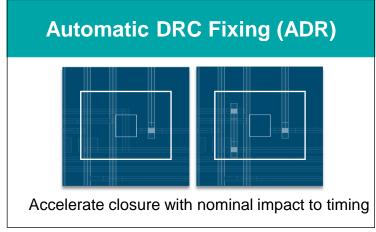

2X Faster PV Convergence

#### Unparalleled Innovations to Accelerate Debug

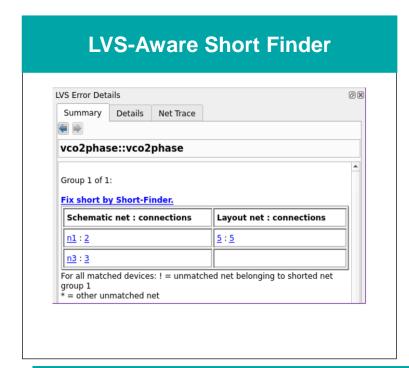

# LVS Short Finder Interactive Short Analysis

Multiple text-shorts debug without rerunning LVS

Fix logical shorts using interactive short finder

Show conflicting metal nets attached to well islands

#### 2X Faster PV Convergence

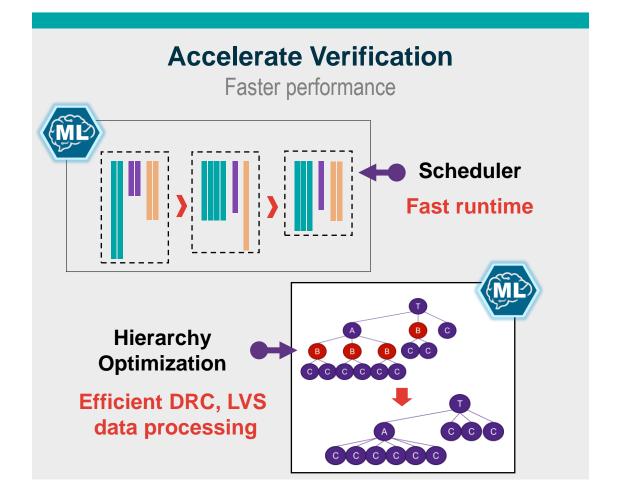

#### Machine Learning Solution

ML-Enhanced Physical Verification

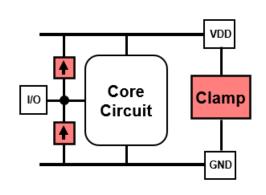

#### **End-to-End ESD Solution**

Technologies from Schematic to Layout

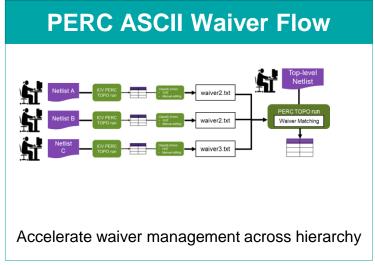

#### **ICV PERC - TOPO**

#### Fully programmable netlist analysis

Recognize and report full ESD network

Foundry Certified

Python programming language

#### ICV PERC - CD/P2P

#### Unmatched full chip performance, 94B Tx

Star-RC golden Extraction

**Foundry Certified**

Silicon Proven on SNPS IP

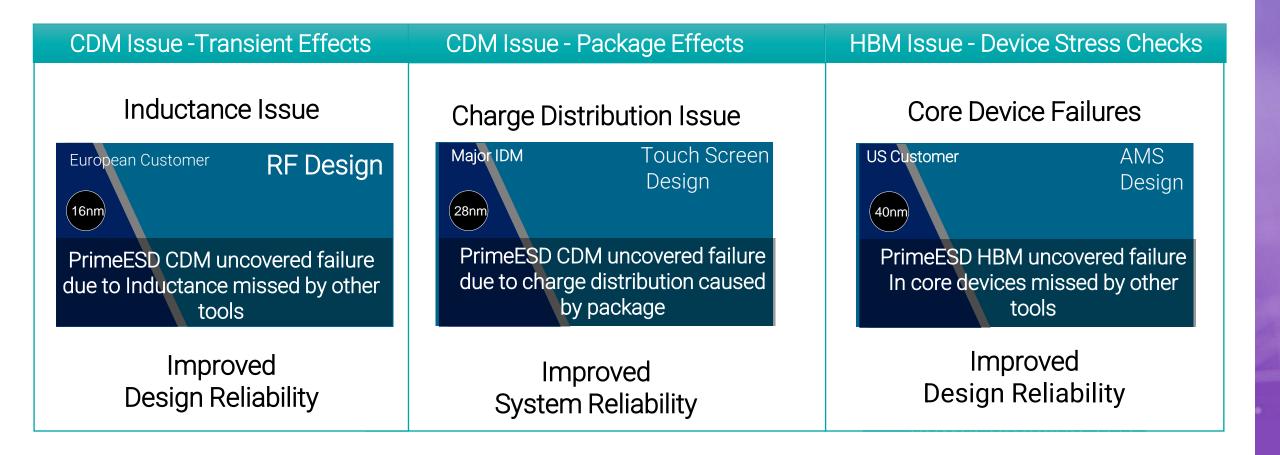

#### **PrimeESD - HBM**

#### **Full chip HBM Analysis**

Finds core device and interconnect failures

Highlights cause of failures

Identifies unused or lightly used ESD Devices

#### **PrimeESD - CDM**

#### **Full chip CDM Analysis**

Supports ESD Device snapback

Charge distribution algorithm supports all design styles

Supports inductance and capacitance

#### **Enabling Designers to Achieve ESD Proof Designs**

#### **Customer Successes**

#### Summary

TSMC Golden Certified, Natively Developed Runsets, 100+ N3 Tapeouts

#### Scalability to 4000 cores

40% compute savings

2X faster debug convergence