### PrimeClosure

### Accelerating ECO Convergence with PrimeClosure Advanced Technologies

Kenneth Hung Senior Manager Synopsys

### **CONFIDENTIAL INFORMATION**

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

## **IMPORTANT NOTICE**

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

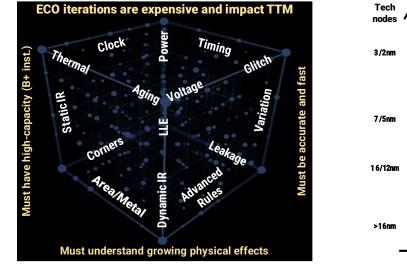

### Advanced Node Challenges Impact ECO Time-to-Results

SYNOPSYS®

Tech

nodes 3/2nm

7/5nm

16/12nm

>16nm

1-2M inst.

Signoff PPA last-mile design closure TAT and iterations have significantly increased

#### Multi-dimensional ECO Problem Space

Advanced Node ECO Requirements Last-mile signoff closure complexity growing exponentially

LMC

Signoff ECO

Signoff ECO

LMC

Signoff ECO

LMC

P&R

P&R

Signoff ECO

Last-Mile Closure

LMC: Last-Mile Closure

**Time-to-Closure**

Signoff accurate subsystem-level / closure required for large SoCs

5-10M inst.

Increased iterations delay product time-to-market and increase project cost

00M-200M inst.

Growth in ECO Design Size

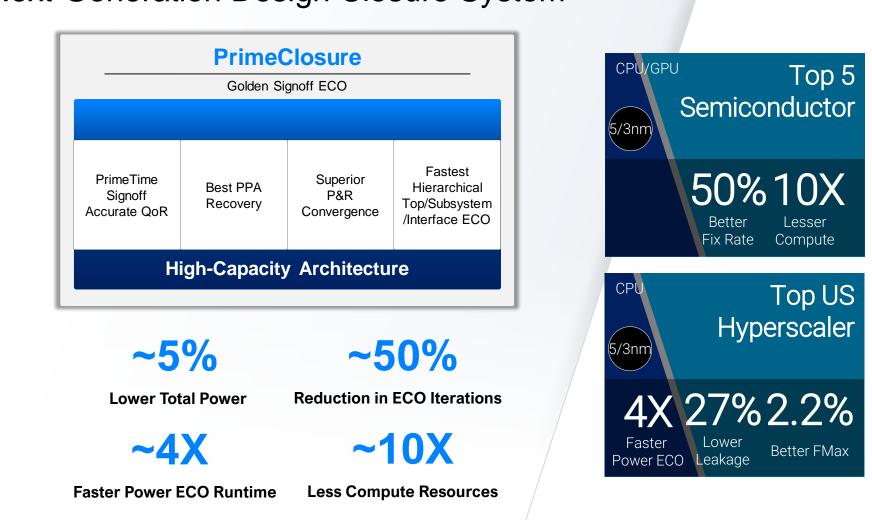

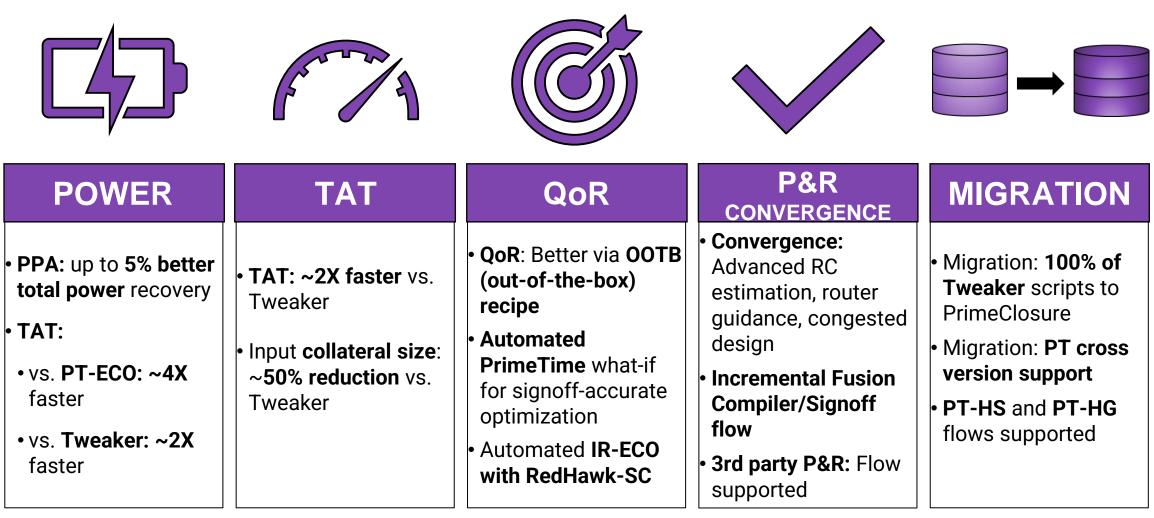

PrimeClosure: Golden Signoff ECO

**Next-Generation Design Closure System**

Top 5

GPU

Faster Lesser Lesser Compute Power ECO Iterations

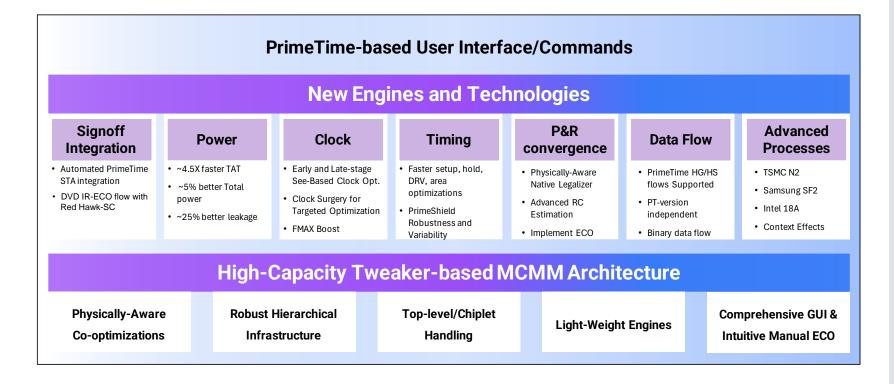

## **High-Capacity Architecture**

Leverages production-proven Tweaker infrastructure

#### New, faster optimization TAT

- Better QoR, and PPA

- Signoff Analysis Integration

- 100% Tweaker scripts migration

- PT version independent

- Faster TAT

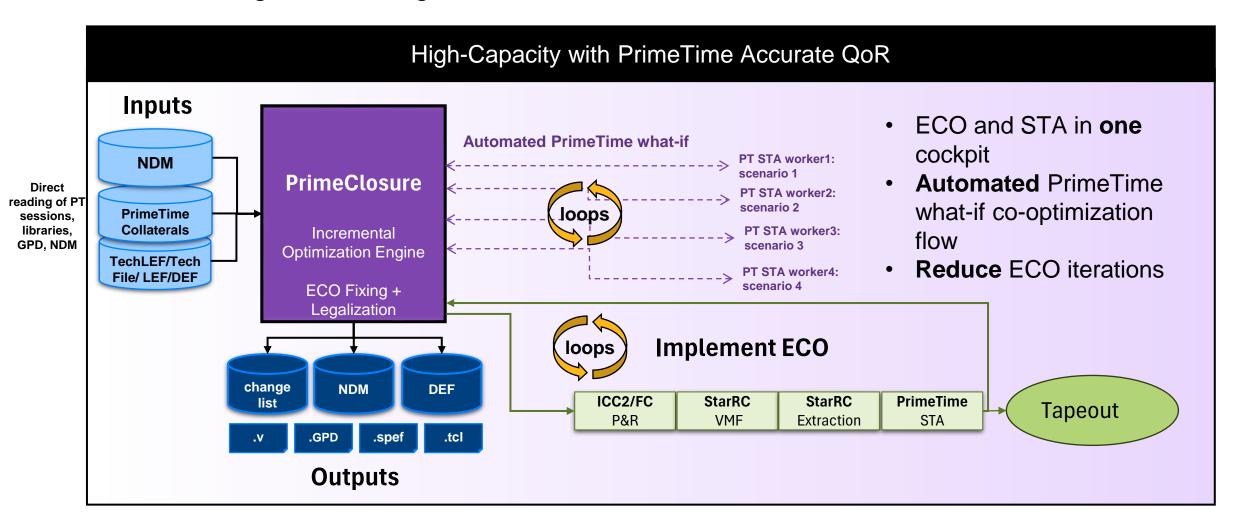

Automated Signoff Accurate QoR for Demanding Designs

PrimeTime integration for signoff QoR

#### SNUG SINGAPORE 2024 7

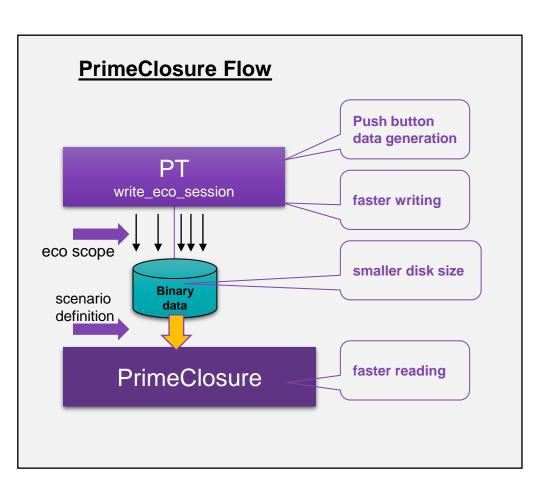

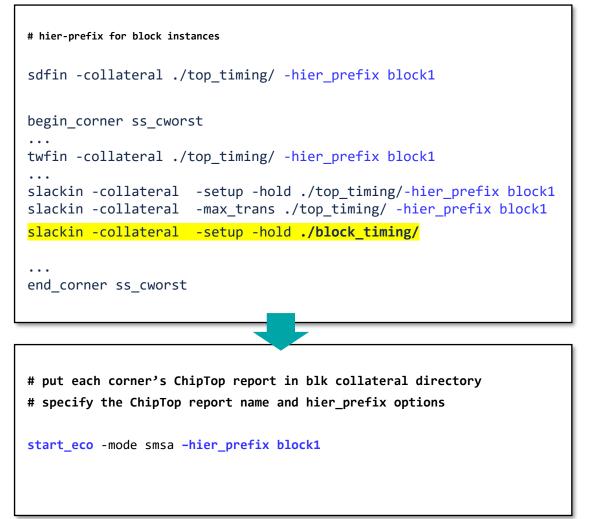

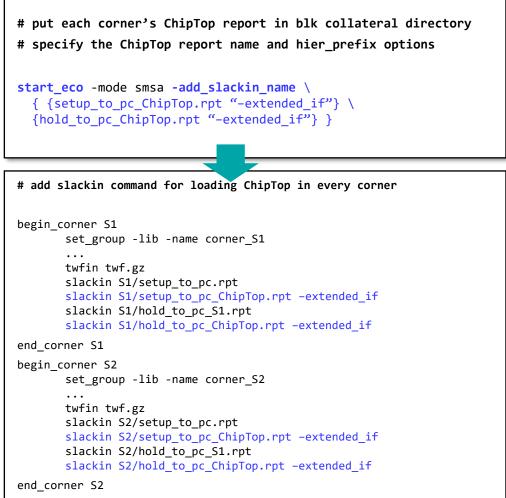

write\_eco\_session and start\_eco auto config mechanisms

Benefits of Integrated ECO Session Data Flow

- PT settings

- library location

- derating, drc, aocv, pocv

- don't touch, don't use

- simplified hier\_prefix, auto partitioning flow •

- timing info transfer, no need for reporting transfer ٠

- netlist, spef, gpd, upf

- voltage scaling, MV settings

- corner building •

- eco scope

- configurable corner definitions

#### **Consolidated and Easy to Transfer**

### Key PrimeClosure Differentiations

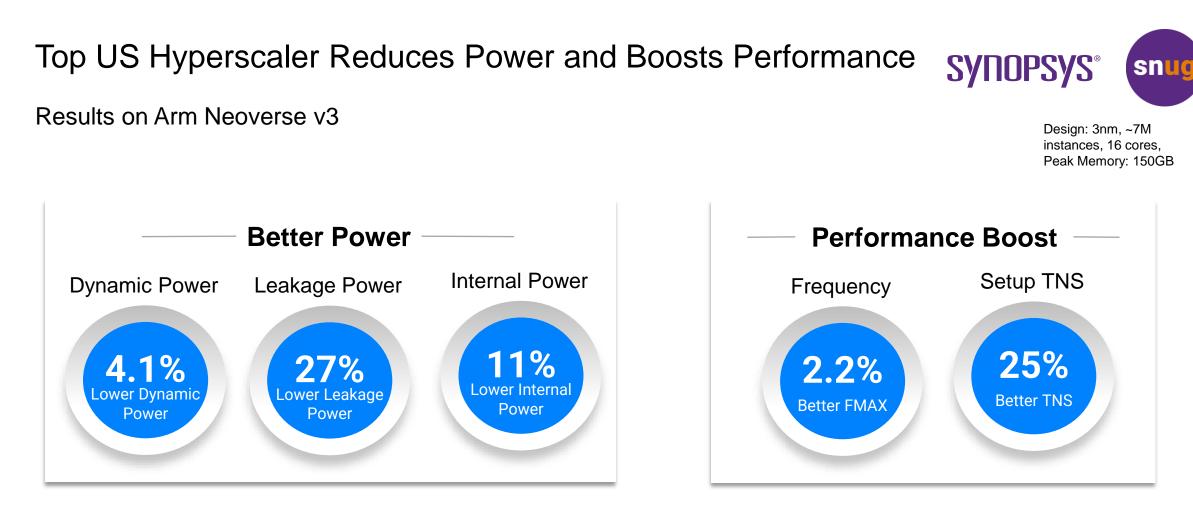

| Power Group | Leakage       | (mW)     | Power Group | Internal (mW) |          |  |

|-------------|---------------|----------|-------------|---------------|----------|--|

|             | Combinational | Register |             | Combinational | Register |  |

| preECO      | 158.9         | 53.4     | preECO      | 30.6          | 99.7     |  |

| postECO     | 111.7         | 40.8     | postECO     | 28.1          | 86.3     |  |

| Savings     | 47.2          | 12.6     | Savings     | 2.5           | 13.4     |  |

| Average     | -27%          |          | Average     | -119          | 6        |  |

- Clock Surgery delivered 2.2% FMAX boost

- TNS improved by about ~25% on endpoint opt DB

- Power ECO TAT is ~4X faster TAT

- Results are post-implementation

PrimeClosure Delivers Superior Results @ 5nm Evaluation

Better Hold QoR, Setup QoR, TAT, and post implementation vs. Tweaker

Timing QoR Comparison (PC vs. TWK)

| Hold               | violations (Pre- | -ECO->         | Post-ECO)             |              | Setup violations (Pre-ECO->Post-ECO)                                        |

|--------------------|------------------|----------------|-----------------------|--------------|-----------------------------------------------------------------------------|

|                    | T                | otal           | reg ->                | reg          | Total reg -> reg                                                            |

| LING               | _0 17 _> _(      | 0 17           | -0 14 ->              | -0.10        | WNS -0.18 -> -0.18 -0.10 -> -0.01                                           |

| TNS                | -864.29 -> -27   | 1 42           | -625 52 ->            | -32 67 -     | TNS -384.36 -> -378.98 -5.39 -> -0.01                                       |

| NUM                | 90675 -> 10      |                | 82367 ->              | 2404         | NUM 7274 -> 6514 760 -> 1                                                   |

|                    |                  |                |                       | c            | ost PC oco - timing                                                         |

|                    |                  |                |                       | F            | ost PC eco - timing                                                         |

| Ho 1 d             | violations (Pre  | ≥-ECO-         | ->Post-ECO)           | F            | ost PC eco - timing<br><mark>Setup violations (Pre-ECO-&gt;Post-ECO)</mark> |

| Hold               |                  | e-ECO-<br>otal | ->Post-ECO)<br>reg -> | F<br>reg     |                                                                             |

|                    |                  | otal           | reg ->                | reg          | Setup violations (Pre-ECO->Post-ECO)<br>Total reg -> reg                    |

| Hold<br>UNS<br>TNS | Te               | otal<br>0.17   | reg -><br>-0.14 ->    | reg<br>-0.05 | Setup violations (Pre-ECO->Post-ECO)<br>Total reg -> reg                    |

- ~84% improvement in Hold QoR

- >4X reduction in violations

- Better improvement in Setup QoR

#### Post-implementation (PC vs. TWK)

**SYNOPSYS**

sn

| min                                                                        | UNS                                                   | TNS                                                    | PATHS                                    | 100                   | 50                               | 20                      | 10                        | 5                         | 0                             |

|----------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|------------------------------------------|-----------------------|----------------------------------|-------------------------|---------------------------|---------------------------|-------------------------------|

| core_clk                                                                   | -0.1                                                  | -42.731                                                | 5640                                     | 0                     | 69                               | 491                     | 627                       | 850                       | 3603                          |

| ate_core_clk                                                               | -0.1                                                  | -41.702                                                | 5368                                     | 0                     | 66                               | 482                     | 624                       | 824                       | 3372                          |

| wrck_clk                                                                   | -0.054                                                | -1.144                                                 | 230                                      | 0                     | 2                                | 12                      | 14                        | 21                        | 181                           |

| CIF                                                                        | -0.047                                                | -0.771                                                 | 149                                      | 0                     | 0                                | 6                       | 16                        | 15                        | 112                           |

| clock_gating_default                                                       | -0.008                                                | -0.019                                                 | 8                                        | 0                     | 0                                | 0                       | 0                         | 1                         | ?                             |

| ate_wrck_clk                                                               | -0.001                                                | -0.001                                                 | 1                                        | 0                     | 0                                | 0                       | 0                         | 0                         | 1                             |

| TOTAL_R2R                                                                  | -0.1                                                  | -86.368                                                | 11396                                    | 0                     | 137                              | 991                     | 1281                      | 1711                      | 7276                          |

| Post PC eco implem                                                         | nentation                                             | - hold timir                                           | g                                        |                       |                                  |                         |                           |                           |                               |

| Post PC eco implem                                                         | nentation<br>uns                                      | - hold timir<br>TNS                                    | g<br>Paths                               | 100                   | 50                               | 20                      | 10                        | 5                         | 0                             |

|                                                                            |                                                       |                                                        | Ŭ                                        | 100<br>0              | 50                               | 20                      | 10<br>185                 | 5                         |                               |

| nin                                                                        | WNS<br>-0.068<br>-0.068                               | TNS<br>-12.889<br>-12.039                              | PATHS<br>3266<br>2986                    |                       | 50<br>1<br>1                     |                         |                           |                           | 264<br>239                    |

| nin<br>core_clk<br>ate_core_clk<br>wrck_clk                                | UNS<br>-0.068<br>-0.068<br>-0.035                     | TNS<br>-12.889<br>-12.039<br>-0.46                     | PATHS<br>3266<br>2986<br>123             |                       | 50<br>1<br>1<br>0                | 77                      | 185<br>178<br>7           | 354                       | 264<br>239<br>105             |

| nin<br>core_clk<br>ate_core_clk<br>wrck_clk<br>ClF                         | UNS<br>-0.068<br>-0.068<br>-0.035<br>-0.017           | TNS<br>-12.889<br>-12.039<br>-0.46<br>-0.285           | PATHS<br>3266<br>2986                    |                       | 50<br>1<br>1<br>0<br>0           | 77<br>74                | 185<br>178<br>7<br>2      | 354<br>336                | 264<br>239<br>105<br>118      |

| nin<br>core_clk<br>ate_core_clk<br>wrck_clk<br>CIF<br>clock_gating_default | UNS<br>-0.068<br>-0.068<br>-0.035<br>-0.017<br>-0.006 | TNS<br>-12.889<br>-12.039<br>-0.46<br>-0.285<br>-0.018 | PATHS<br>3266<br>2986<br>123<br>122<br>6 | 0<br>0<br>0<br>0<br>0 | 1<br>1<br>0<br>0<br>0            | 77<br>74<br>5<br>0<br>0 | 185<br>178<br>7<br>2<br>0 | 354<br>336<br>6<br>2<br>1 | 264<br>239<br>105<br>118<br>5 |

| nin<br>core_clk<br>ate_core_clk<br>wrck_clk<br>ClF                         | UNS<br>-0.068<br>-0.068<br>-0.035<br>-0.017           | TNS<br>-12.889<br>-12.039<br>-0.46<br>-0.285           | PATHS<br>3266<br>2986<br>123<br>122      |                       | 50<br>1<br>1<br>0<br>0<br>0<br>0 | 77<br>74<br>5<br>0      | 185<br>178<br>7<br>2      | 354<br>336                | 264<br>239<br>105<br>118      |

~70% better Hold QoR

- Technology node: N5

- Size (# of cells/mem):3.57M/510

- # of Corner: 12

- Violation type: max\_tran, setup,hold

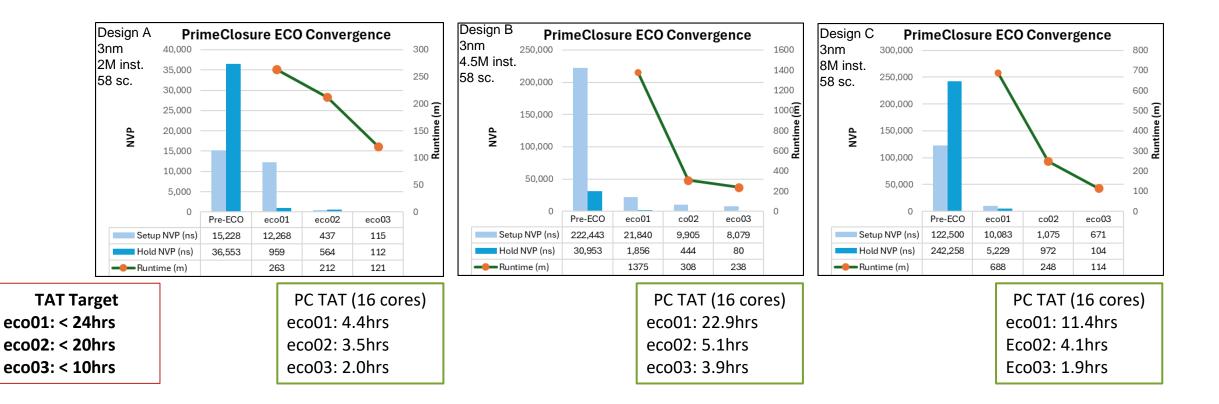

### Top 5 Semiconductor Reduced ECO Iterations by 40%

PrimeClosure delivered better timing, leakage power, and TAT

TAT can be reduced with more cores

Strong Hierarchical Technologies Reduce Time-to-Results for Large Designs

HyperScale,

**STA**

HyperGrid, Flat

enable fastest TAT, memory reduction on single boxes → *low cost-per-run*

SNUG SINGAPORE 2024 12

hierarchy and corner

2X Speedup TAT

reduction

•

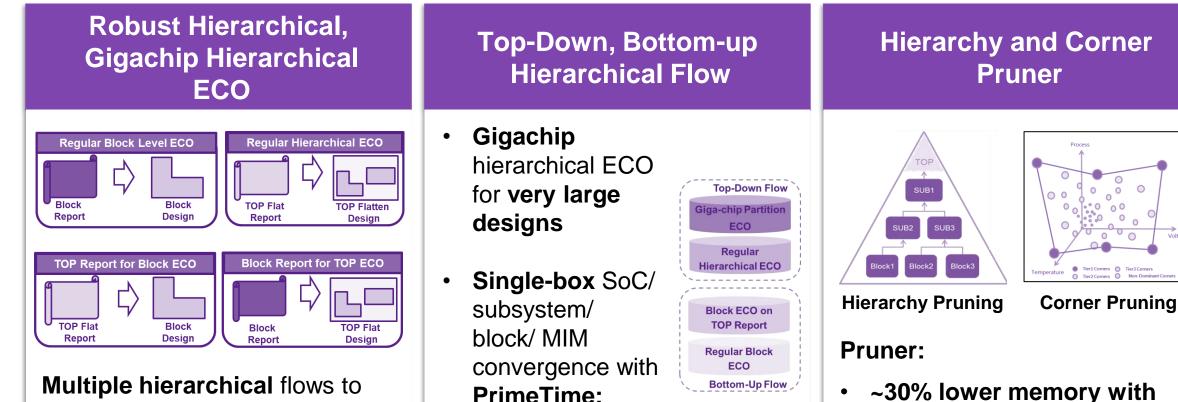

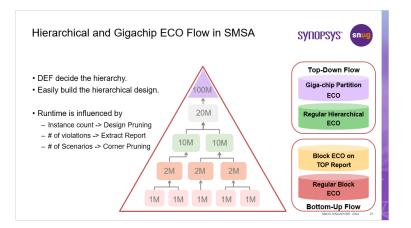

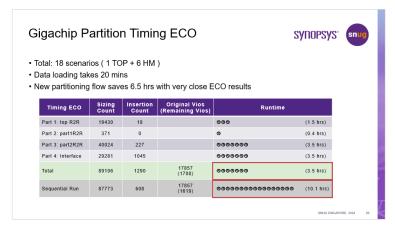

### PrimeClosure Gigachip Hierarchical Flow

Hierarchical ECO TAT Acceleration Solution

Runtime Bottleneck

Identification

ECO Strategies to Reduce TAT

• Speed up with Gigachip Hierarchical Flow

| Mote ECO Strategies of Hierarchical Design synopsys |                                 |                                     |                                                        |                                                                                                 |  |  |

|-----------------------------------------------------|---------------------------------|-------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

|                                                     | Block Leve                      | ECO                                 | Hieratica                                              | I Level ECO                                                                                     |  |  |

|                                                     | Block<br>Report Block<br>Design | TOP Flatten<br>Report Design        | TOP Flatten<br>Report                                  | TOP Flatten<br>Report TOP Flatten<br>Design                                                     |  |  |

| Feature                                             | (1) Regular Block Level ECO     | (2) TOP Report for Block ECO        | (3) Gigachip Partition ECO                             | (4) Regular Hierarchical ECO                                                                    |  |  |

| Suitable<br>Case                                    | 1. Block Design                 | 1. Block Design with Chip<br>Report | 1. Design which instance count ><br>30M instance count | 1. Design which instance count <<br>30M instance count<br>2. Violation which lesser than<br>20K |  |  |

| ECO<br>Target                                       | R2R ECO                         | IO + R2R ECO                        | Partition R2R + Interface ECO                          | Flatten ECO                                                                                     |  |  |

| Violation<br>Reduction                              | Extract Report                  | Extract Report                      | Design Pruning + Extract Report                        | Design Pruning + Extract Report                                                                 |  |  |

|                                                     |                                 |                                     |                                                        | SNUG SINGAPORE 2024 28                                                                          |  |  |

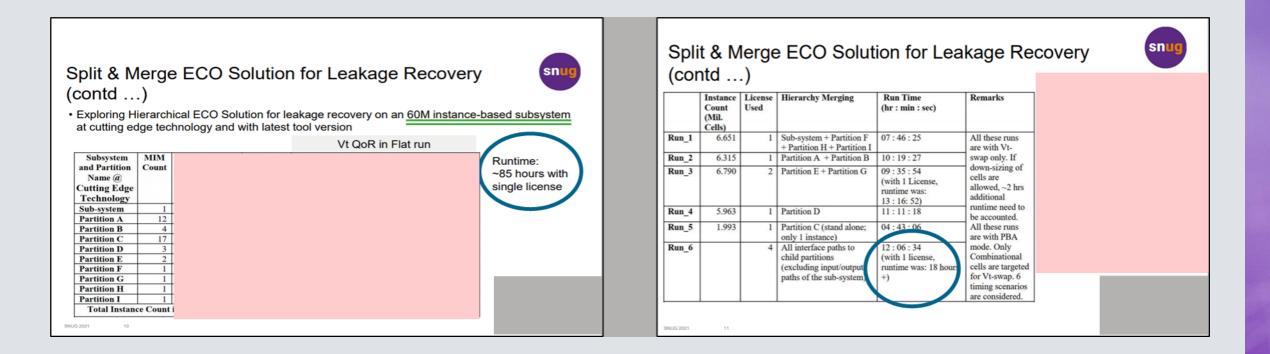

### Hierarchical Leakage Recovery Delivers ~7X TTR Speedup

Top 10 semiconductor company presentation at SNUG

#### **Total Time-to-Results Reduced from 85hours to 12hours**

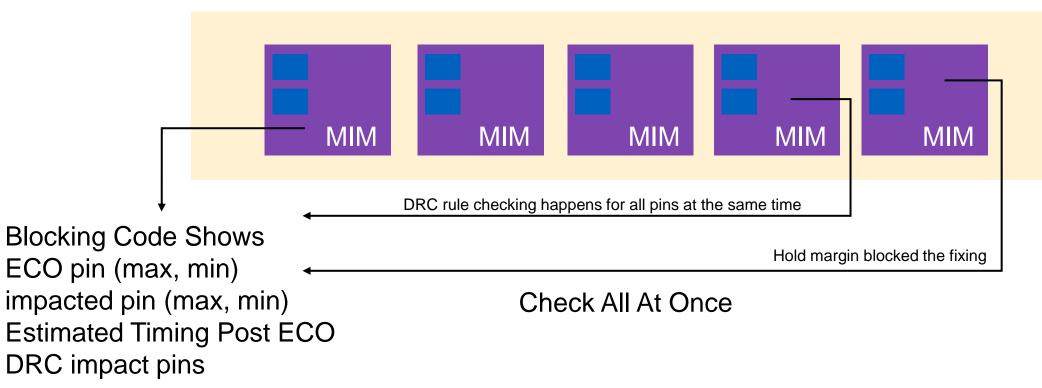

## Efficient MIM Flow

Multiple Instantiated Module Flow

- ECO for MIM

- Hierarchical MIM

- Consolidated Timing Information

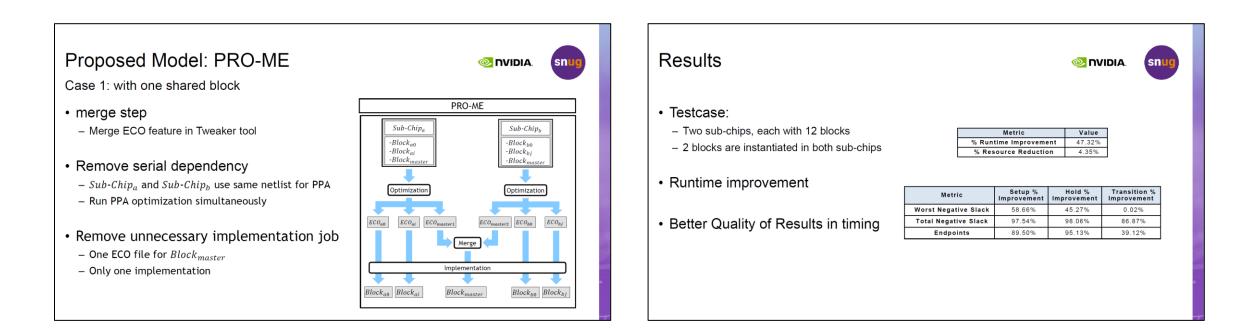

### Customer Success Story of MIM Flow

• Merge ECO Flow user example presented in SNUG 2024

https://www.synopsys.com/community/snug/snug-silicon-valley/location-proceedings-2024.html

#### ial Information

SNUG SINGAPORE 2024 17

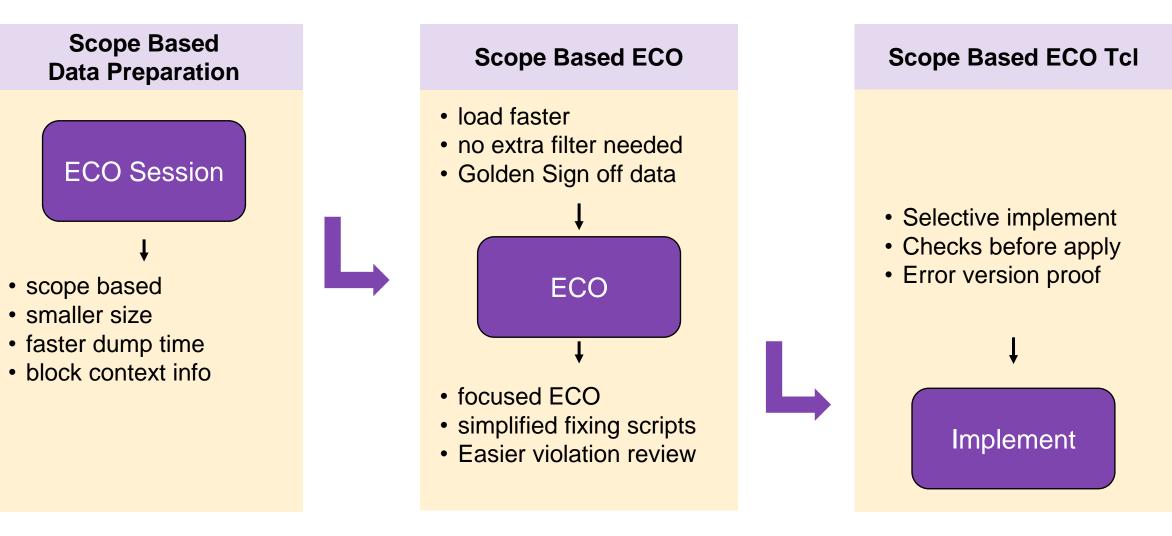

### Scope Based Technology Applied to ECO Phases

Result in Faster TAT, Reduced File Size, Flexibility to Selectively Group Output

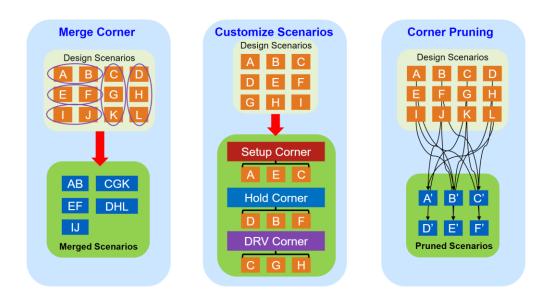

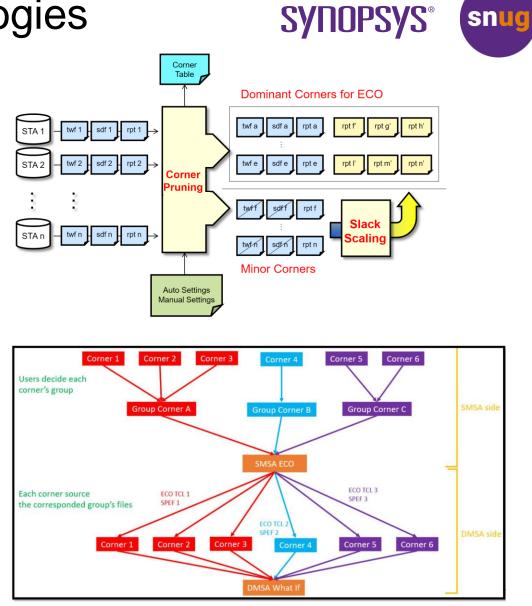

## Smart Corner Reduction Technologies

**Enables Faster TAT and Memory Reduction**

- Merge Corner

- Customizable Scenario Definitions

- Corner Pruning

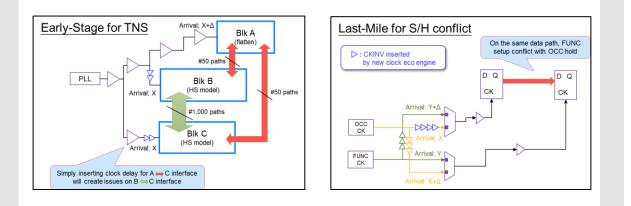

#### Seed-Based Clock ECO Improves Timing and Convergence

#### Better TNS and improved productivity

- New technology looks at optimal locations along entire clock network

- Minimizes # of points where changes need to be made (insertion, bypass)

- Looks across multiple stages, applicable to both block or cross boundary paths

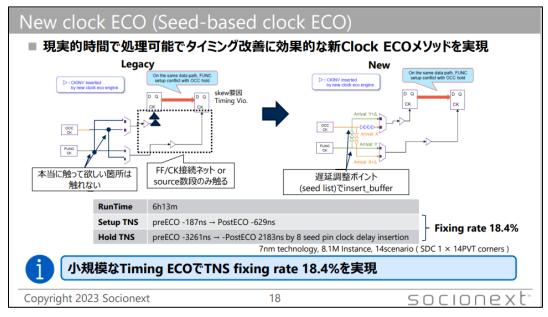

#### Socionext: TNS Fixing Rate Improved by 18%

Seed Base Clock ECO Target Total TNS (setup+hold) and improved 18.4% by just performing 8 insertion commands

Better QoR for setup timing can be obtained by using cell stealing technology

while maintaining hold timing

**SYNOPSYS**<sup>®</sup>

snug

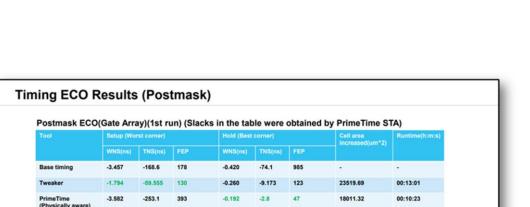

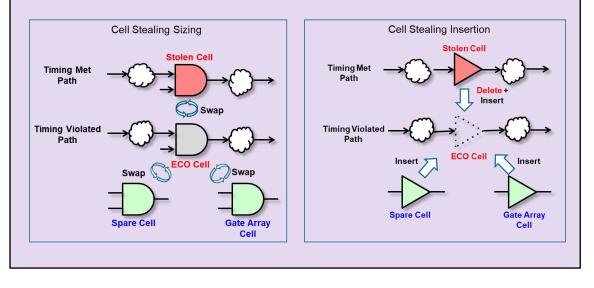

#### Unique Metal ECO Transforms Driven Further Timing Closure Demonstrated ~60% setup TNS improvement at top memory company

Post-Mask Transforms Improve Timing QoR

- Numerous post-mask transforms for improving timing QoR

- SpareCell/GateArray/RecyclingCell/ConstantCell/C ellStealing

- Better setup timing QoR using cell-stealing technology

Setup: Mainly improved by cell stealing (over 60% improvement in TNS)

Hold: Mainly improved by buffer insertion

>60% improvement in setup TNS

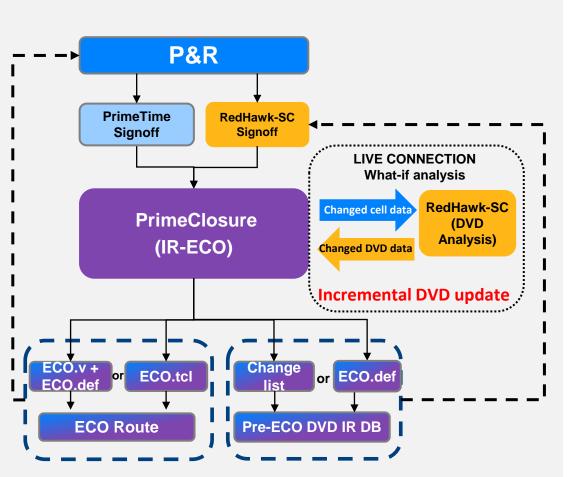

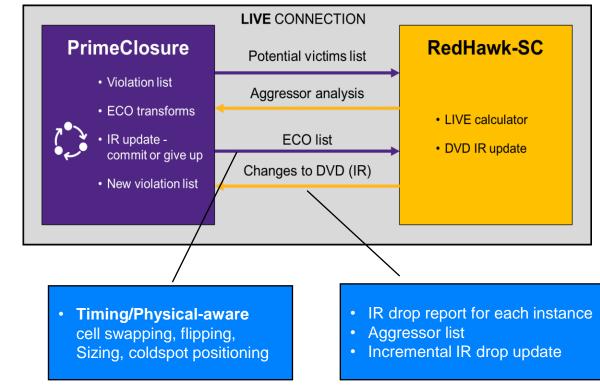

### PrimeClosure / Redhawk-SC Dynamic IR-ECO Flow

State of the art Ansys and Synopsys collaboration to ensure convergent last-mile closure

Incremental Automated IR Drop Update Methodology

**SYNOPSYS**<sup>®</sup>

snug

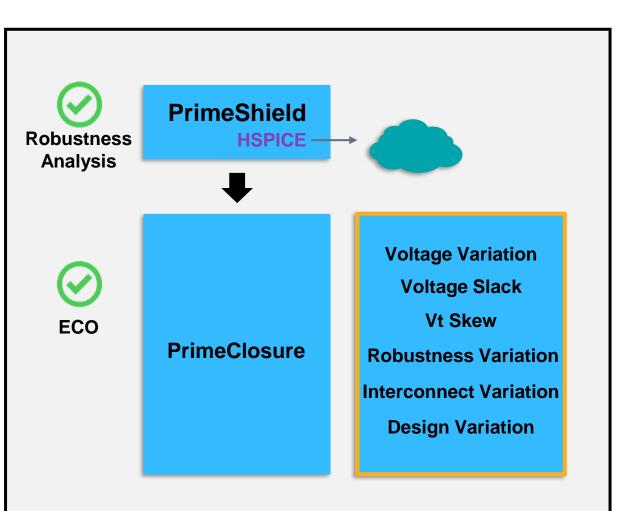

### PrimeClosure/PrimeShield Robustness ECO Flow

Improved design reliability with PrimeShield analysis and PrimeClosure ECO fixing

• Integrated with PrimeShield robustness analysis PrimeClosure brings superior closure for robustness, voltage, parasitic variation, aging analysis improves overall design PPA-RA (Power, Performance, Area, Robustness, Aging).

| Robustness<br>Type   | ЕСО Туре                        | smsa fix<br>types             | ECO<br>Methodology                 |  |

|----------------------|---------------------------------|-------------------------------|------------------------------------|--|

|                      | Variation                       | variation                     |                                    |  |

| Cell Robustness      | Voltage                         | voltage                       | VT_swap +<br>sizing                |  |

|                      | Transition                      | transition                    | с. <u> </u>                        |  |

|                      | Voltage<br>slack<br>(Vmin)      | voltage_slack                 | VT swap +<br>sizing                |  |

| Path                 | VT skew<br>(Mix VT)             | vt_skew_setup<br>vt_skew_hold | VT swap +<br>Sizing +<br>insertion |  |

| Robustness           | Interconnec<br>t skew<br>(BEOL) | isa_setup<br>isa_hold         | VT swap<br>sizing+inserti<br>on    |  |

|                      | DvD-aware<br>ECO                | setup hold                    | VT swap +<br>sizing<br>+insertion  |  |

| Design<br>Robustness | POCV<br>variation               | dva_setup<br>dva_hold         | VT+sizing+<br>insertion            |  |

| Robustiless          | Bottleneck                      | bottleneck                    | VT+sizing                          |  |

**SYNOPSYS**<sup>®</sup>

snug

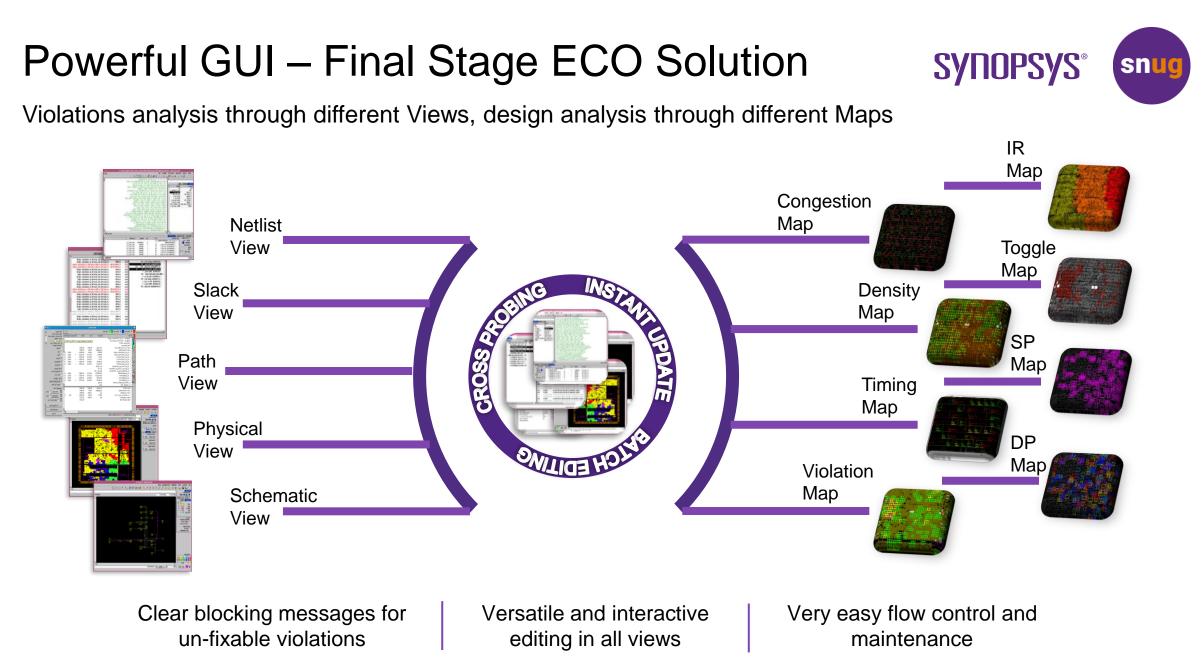

### PC UI – Simple and Fully Customizable

MCMM architecture to handle B+ instance designs, and deliver lower cost-per-run

Efficient resource utilization for multi-billion instance designs

100% PrimeTime accurate QoR reduces ECO iterations

Seamless convergence with P&R with signoff accuracy

High Capacity to handle 100's of block with mixed PNR solution

# THANK YOU

Our Technology, **Your** Innovation<sup>™</sup>