**SIEMENS EDA**

# Tessent<sup>™</sup> Shell User's Manual

Software Version 2022.4 Document Revision 28

#### Unpublished work. © 2022 Siemens

This Documentation contains trade secrets or otherwise confidential information owned by Siemens Industry Software Inc. or its affiliates (collectively, "Siemens"), or its licensors. Access to and use of this Documentation is strictly limited as set forth in Customer's applicable agreement(s) with Siemens. This Documentation may not be copied, distributed, or otherwise disclosed by Customer without the express written permission of Siemens, and may not be used in any way not expressly authorized by Siemens.

This Documentation is for information and instruction purposes. Siemens reserves the right to make changes in specifications and other information contained in this Documentation without prior notice, and the reader should, in all cases, consult Siemens to determine whether any changes have been made.

No representation or other affirmation of fact contained in this Documentation shall be deemed to be a warranty or give rise to any liability of Siemens whatsoever.

If you have a signed license agreement with Siemens for the product with which this Documentation will be used, your use of this Documentation is subject to the scope of license and the software protection and security provisions of that agreement. If you do not have such a signed license agreement, your use is subject to the Siemens Universal Customer Agreement, which may be viewed at https://www.sw.siemens.com/en-US/sw-terms/base/uca/, as supplemented by the product specific terms which may be viewed at https://www.sw.siemens.com/en-US/sw-terms/supplements/.

SIEMENS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS DOCUMENTATION INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. SIEMENS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL OR PUNITIVE DAMAGES, LOST DATA OR PROFITS, EVEN IF SUCH DAMAGES WERE FORESEEABLE, ARISING OUT OF OR RELATED TO THIS DOCUMENTATION OR THE INFORMATION CONTAINED IN IT, EVEN IF SIEMENS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TRADEMARKS: The trademarks, logos, and service marks (collectively, "Marks") used herein are the property of Siemens or other parties. No one is permitted to use these Marks without the prior written consent of Siemens or the owner of the Marks, as applicable. The use herein of third party Marks is not an attempt to indicate Siemens as a source of a product, but is intended to indicate a product from, or associated with, a particular third party. A list of Siemens' Marks may be viewed at: www.plm.automation.siemens.com/global/en/legal/trademarks.html. The registered trademark Linux<sup>®</sup> is used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on a world-wide basis.

#### **About Siemens Digital Industries Software**

Siemens Digital Industries Software is a leading global provider of product life cycle management (PLM) software and services with 7 million licensed seats and 71,000 customers worldwide. Headquartered in Plano, Texas, Siemens Digital Industries Software works collaboratively with companies to deliver open solutions that help them turn more ideas into successful products. For more information on Siemens Digital Industries Software products and services, visit www.siemens.com/plm.

Support Center: support.sw.siemens.com Send Feedback on Documentation: support.sw.siemens.com/doc\_feedback\_form

# **Revision History ISO-26262**

| Revision | Changes                                                                                                                                                           | Status/<br>Date      |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 28       | Modifications to improve the readability and comprehension of<br>the content. Approved by Lucille Woo.                                                            | Released<br>Dec 2022 |

|          | All technical enhancements, changes, and fixes listed in the <i>Tessent Release Notes</i> for this product are reflected in this document. Approved by Ron Press. |                      |

| 27       | Modifications to improve the readability and comprehension of the content. Approved by Lucille Woo.                                                               | Released<br>Sep 2022 |

|          | All technical enhancements, changes, and fixes listed in the <i>Tessent Release Notes</i> for this product are reflected in this document. Approved by Ron Press. | 1                    |

| 26       | Modifications to improve the readability and comprehension of the content. Approved by Lucille Woo.                                                               | Released<br>Jun 2022 |

|          | All technical enhancements, changes, and fixes listed in the <i>Tessent Release Notes</i> for this product are reflected in this document. Approved by Ron Press. |                      |

| 25       | Modifications to improve the readability and comprehension of the content. Approved by Lucille Woo.                                                               | Released<br>Mar 2022 |

|          | All technical enhancements, changes, and fixes listed in the <i>Tessent Release Notes</i> for this product are reflected in this document. Approved by Ron Press. |                      |

Author: In-house procedures and working practices require multiple authors for documents. All associated authors for each topic within this document are tracked within the Siemens documentation source. For specific topic authors, contact the Siemens Digital Industries Software documentation department.

Revision History: Released documents include a revision history of up to four revisions. For earlier revision history, refer to earlier releases of documentation on Support Center.

Tessent™ Shell User's Manual, v2022.4

### **Revision History ISO-26262**

| Chapter 1 Tessent Shell Introduction                                   | 27 |

|------------------------------------------------------------------------|----|

|                                                                        |    |

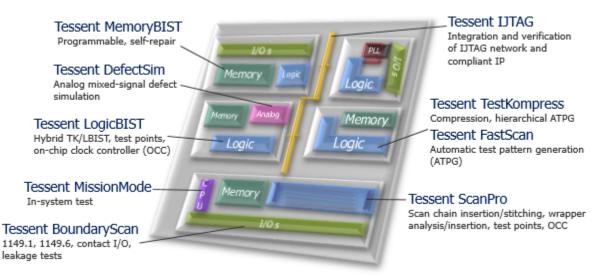

| What Is Tessent Shell?                                                 | 27 |

| What Can You Do With Tessent Shell?                                    | 28 |

| Tessent Shell Tcl Interface                                            | 30 |

| Command Conventions.                                                   | 30 |

| Escaped Hierarchical Names in Command Tcl Lists                        | 31 |

| Command Completion                                                     | 32 |

| Dofile Transcription                                                   | 33 |

| Tcl Command Registration                                               | 34 |

| Chapter 2                                                              |    |

| Tool Invocation, Contexts, Modes, and Data Models                      | 35 |

| Tool Invocation                                                        | 35 |

| Contexts and System Modes                                              | 37 |

| Contexts                                                               | 37 |

| System Modes                                                           | 39 |

| Context and System Mode Combinations                                   | 39 |

| Design Levels                                                          | 40 |

| Design Data Models.                                                    | 41 |

| Flat Design Data Model                                                 | 41 |

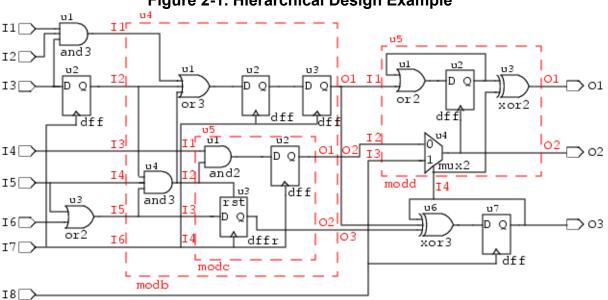

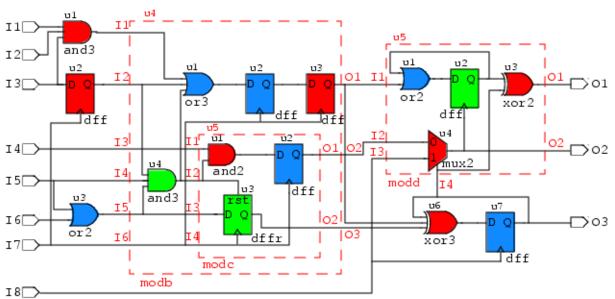

| Hierarchical Design Data Model                                         | 41 |

| ICL Data Model                                                         | 43 |

| Object Attributes                                                      | 43 |

| Chapter 3                                                              |    |

| Design Introspection and Editing                                       | 45 |

| Design Introspection                                                   | 46 |

| Object Specification Format                                            | 46 |

| Collections                                                            | 46 |

| Design Introspection Examples                                          | 49 |

| Design Introspection Command Summary                                   | 53 |

| Bundle Object Introspection                                            | 55 |

| Bundle Object.                                                         | 55 |

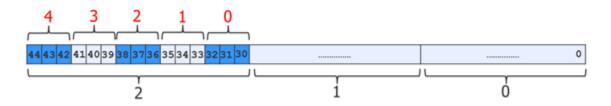

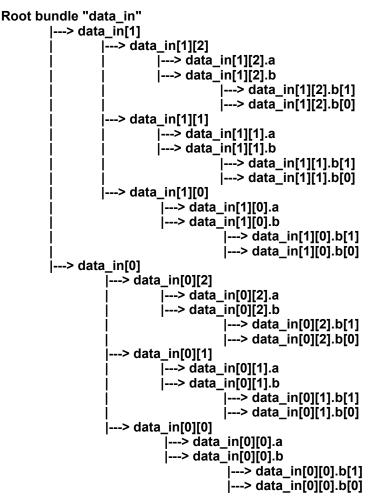

| Bundle Object Data Model                                               | 60 |

| Introspection                                                          | 63 |

| Bundle Object Introspection Examples                                   | 67 |

| Fan-in and Fanout Tracing of Complex Signals and Bundle Object Tracing | 70 |

| Connectivity Through Complex Signals                                   | 74 |

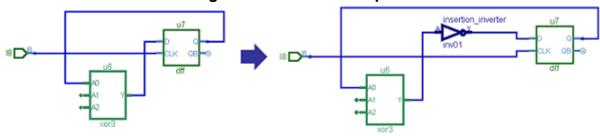

| Design Editing                                                         | 79 |

| Design Editing Command Summary                                    | 80  |

|-------------------------------------------------------------------|-----|

| Editing Complex Signals                                           | 82  |

| Editing Complex Signals With the DftSpecification Wrapper.        | 82  |

| Editing Complex Signals: Limitations and Compatibility            |     |

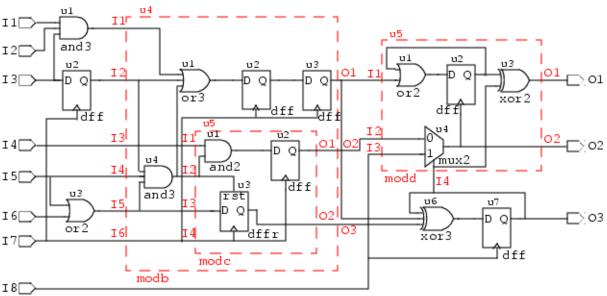

| Design Editing Examples                                           | 84  |

| Simulation Contexts.                                              | 90  |

| Simulation Context Overview                                       | 90  |

| Introspection and Analysis Using Simulation Contexts              |     |

| Automatic Design Mapping.                                         | 94  |

| ICL and TCD Post-Synthesis Update                                 | 94  |

| Updating ICL Attributes From the Design                           |     |

| Matching Rules for Port Names in Post-Synthesis Update            |     |

| Controlling the Name Mapping                                      | 96  |

| ICL Objects vs. Design Objects Introspection.                     | 97  |

| Chapter 4                                                         |     |

| DFT Architecture Guidelines for Hierarchical Designs              | 99  |

| Hierarchical DFT Overview                                         | 100 |

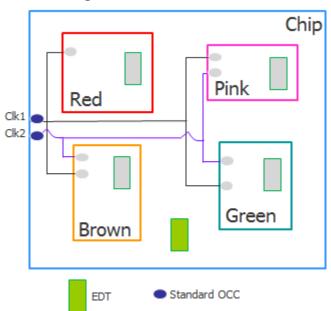

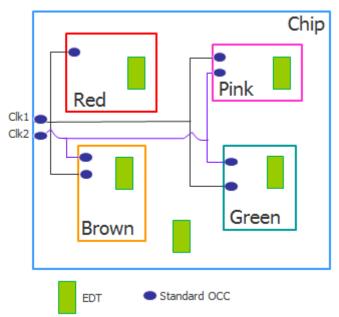

| Physical Layout Regions in Hierarchical Test                      |     |

| Pattern Retargeting                                               |     |

| Wrapped Cores and Wrapper Cells                                   | 101 |

| Internal Mode and External Mode                                   | 102 |

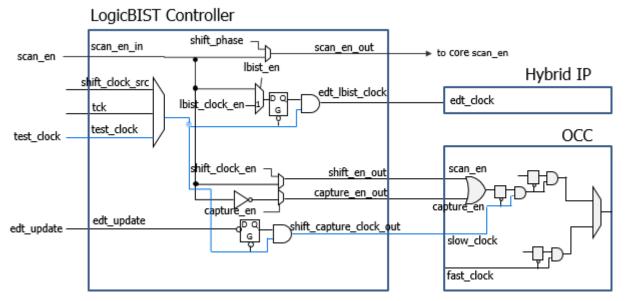

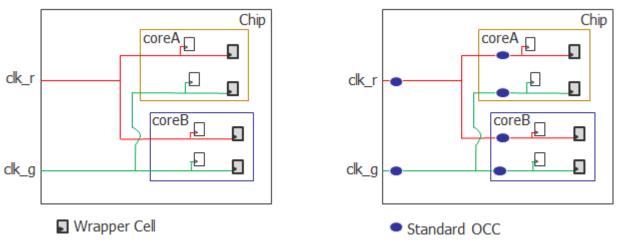

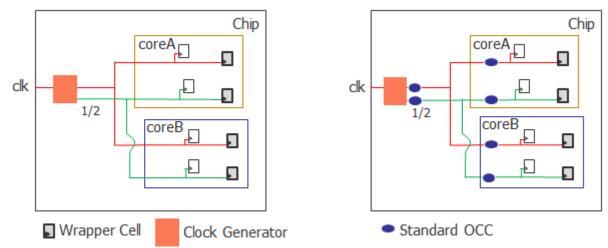

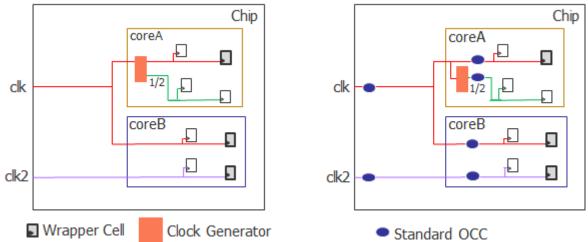

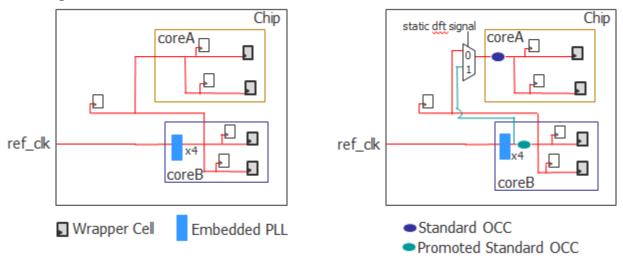

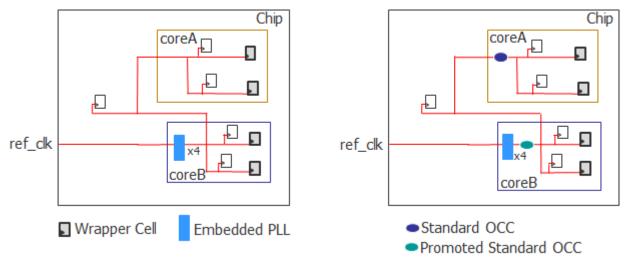

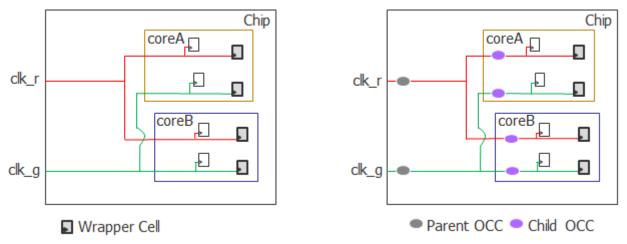

| On-Chip Clock Controller                                          | 103 |

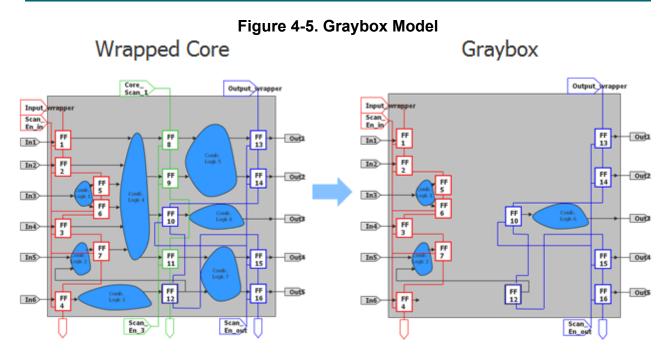

| Graybox Model                                                     | 104 |

| Top-Down Planning Before Bottom-Up Implementation                 | 106 |

| Clocking Architecture.                                            | 106 |

| Resource Availability                                             |     |

| Test Scheduling.                                                  | 107 |

| Specific Tasks That May Require Planning                          | 110 |

| Sample DFT Planning Steps                                         |     |

| DFT Implementation Strategy                                       | 111 |

| Chapter 5                                                         |     |

| Tessent Shell Workflows                                           |     |

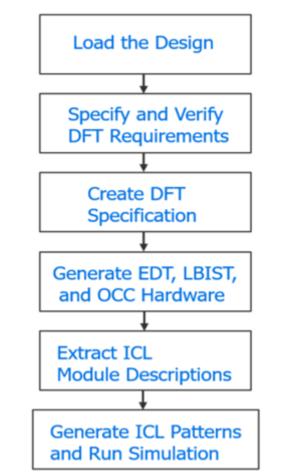

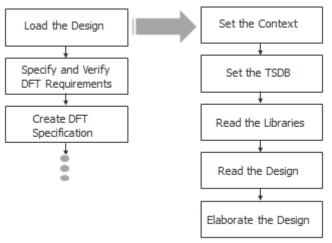

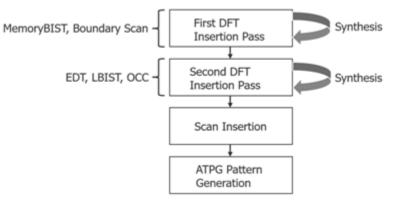

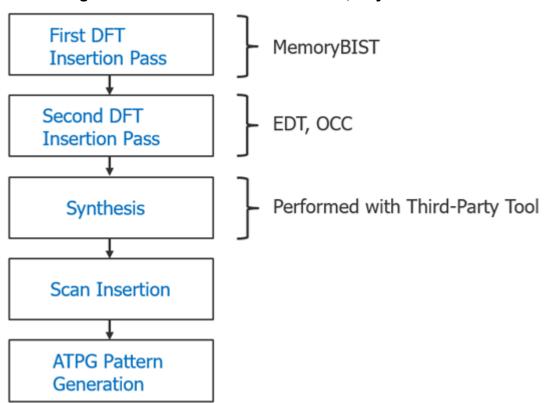

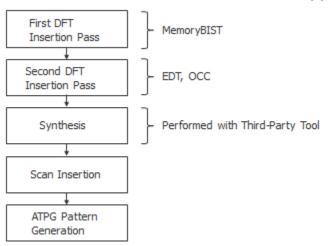

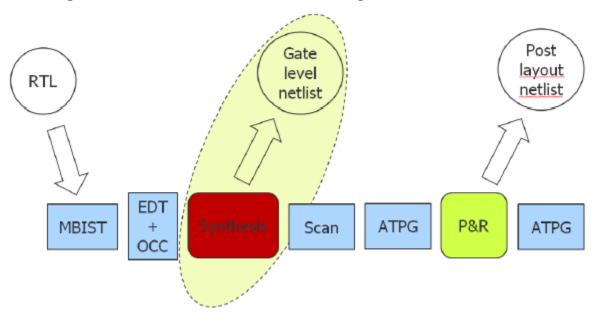

| Tessent Shell Flow for Flat Designs                               | 116 |

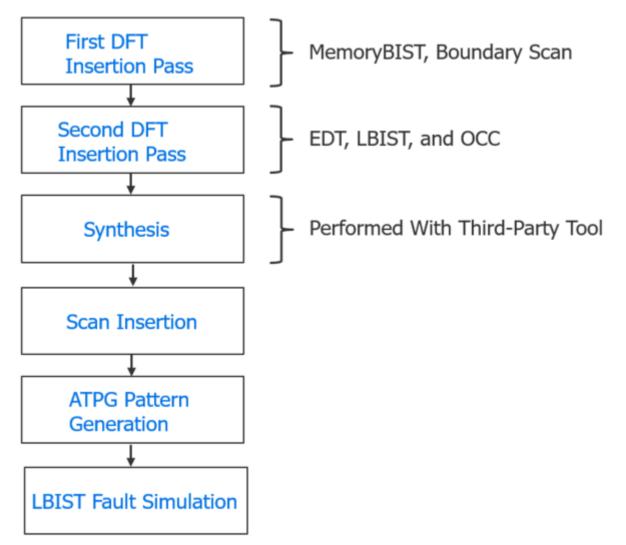

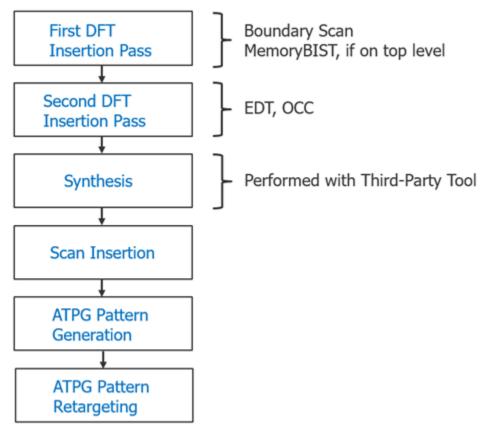

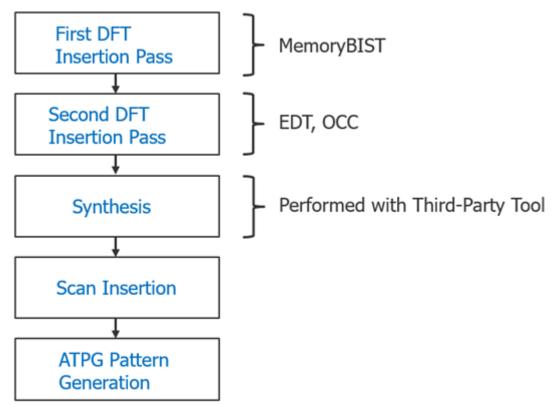

| Overview of the RTL and Scan DFT Insertion Flow                   |     |

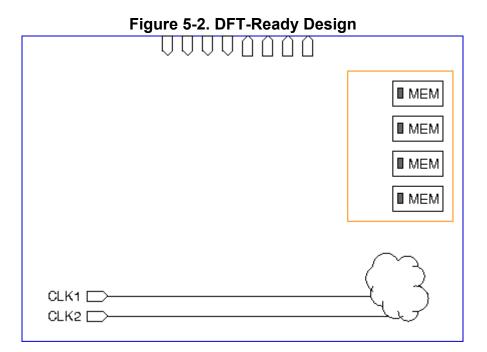

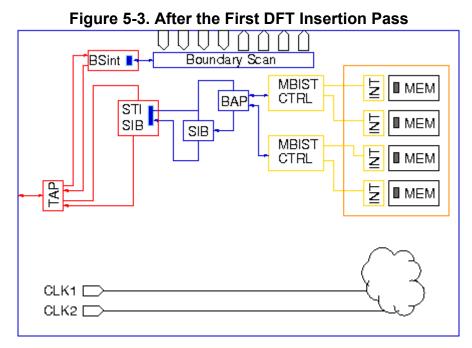

| First DFT Insertion Pass: Performing MemoryBIST and Boundary Scan | 120 |

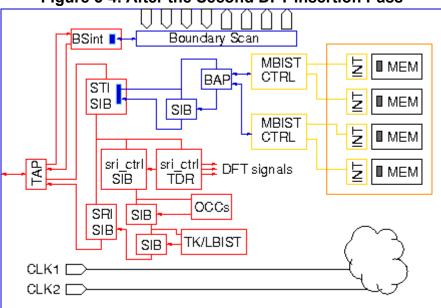

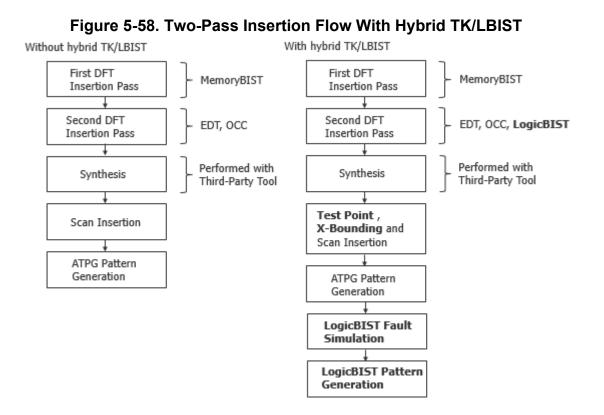

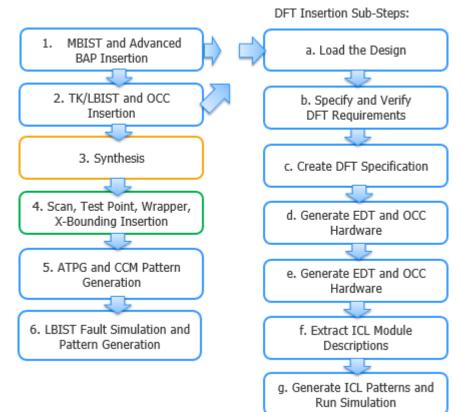

| Second DFT Insertion Pass: EDT, Hybrid TK/LBIST, and OCC          | 124 |

| Loading the Design.                                               | 125 |

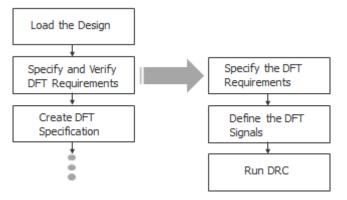

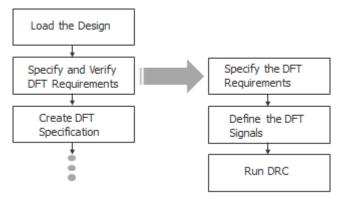

| Specifying and Verifying the DFT Requirements                     | 127 |

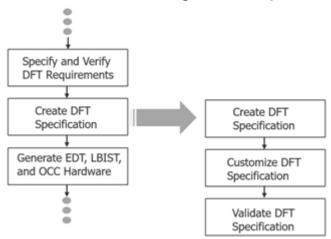

| Creating the DFT Specification                                    | 130 |

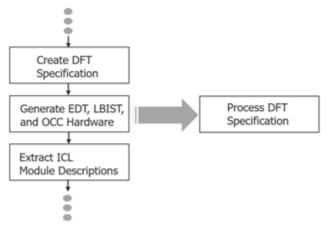

| Generating the EDT, Hybrid TK/LBIST, and OCC Hardware             |     |

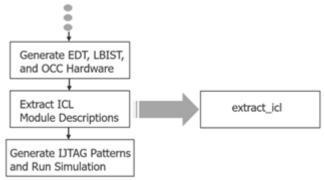

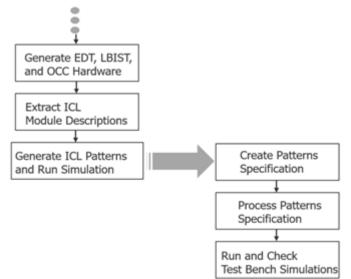

| Extracting the ICL Module Description                             | 134 |

| Generating ICL Patterns and Running Simulation                    |     |

| Performing Synthesis                                              | 136 |

| Performing Scan Chain Insertion (Flat Design)                     | 137 |

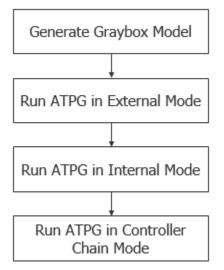

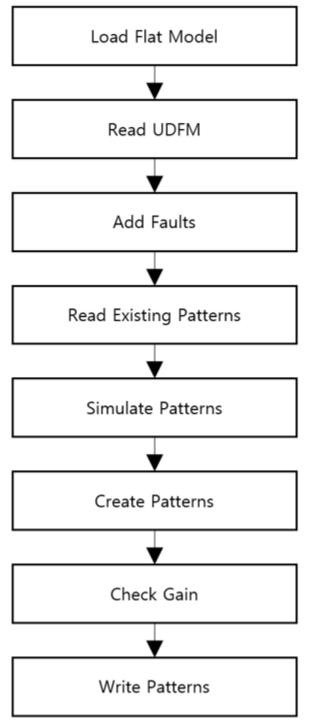

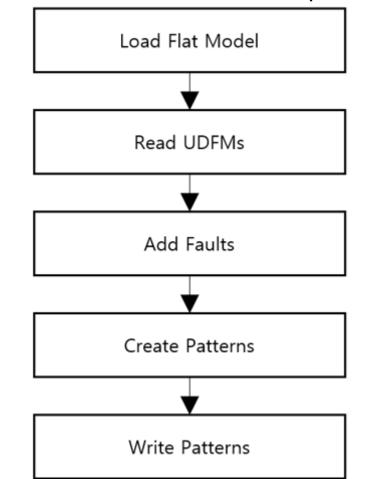

| Performing ATPG Pattern Generation                                |     |

| Simulating LBIST Faults                                           | 141 |

| Considerations for Using Gate-Level Verilog Netlists                         | . 143 |

|------------------------------------------------------------------------------|-------|

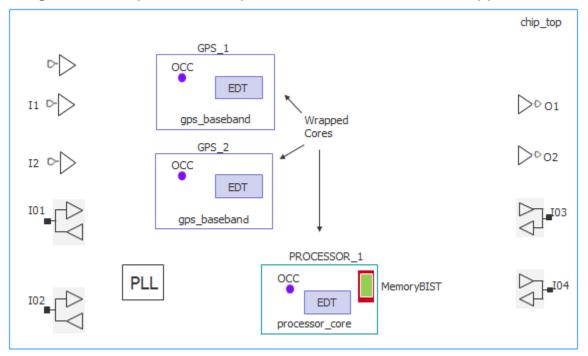

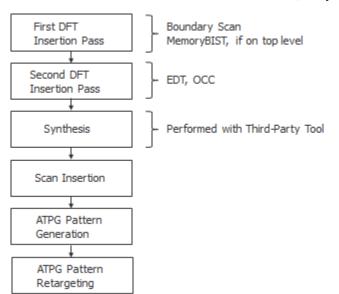

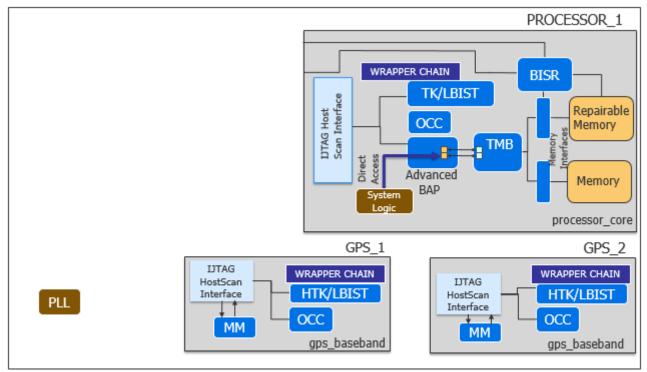

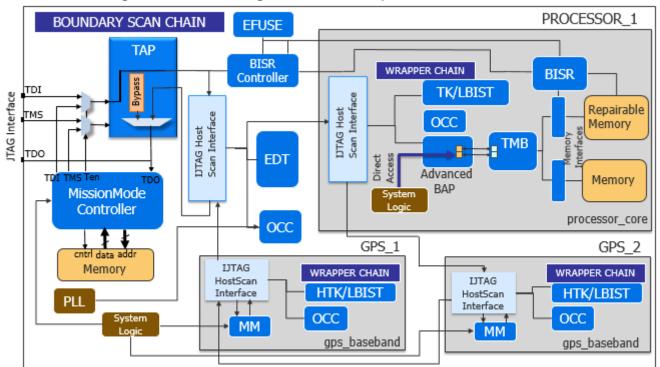

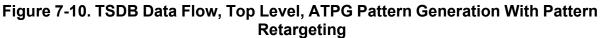

| Tessent Shell Flow for Hierarchical Designs                                  | . 145 |

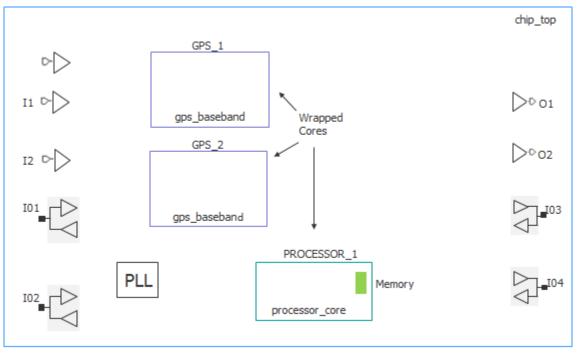

| Hierarchical DFT Terminology                                                 |       |

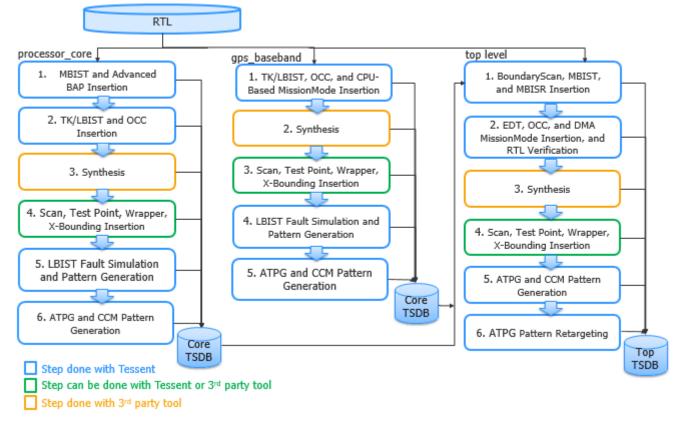

| How the DFT Insertion Flow Applies to Hierarchical Designs                   |       |

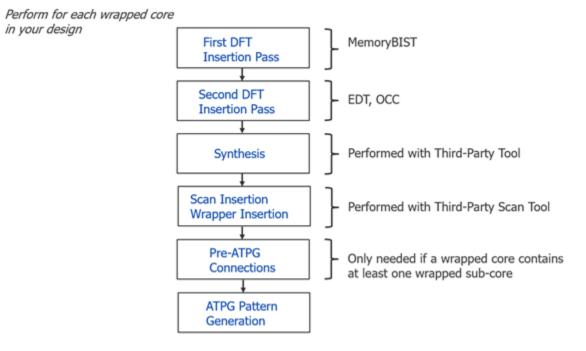

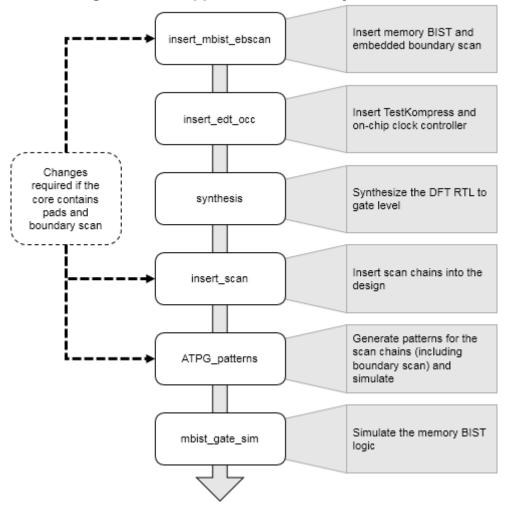

| RTL and Scan DFT Insertion Flow for Physical Blocks                          | . 150 |

| First DFT Insertion Pass: Performing Block-Level MemoryBIST                  |       |

| Second DFT Insertion Pass: Inserting Block-Level EDT and OCC                 |       |

| Specifying and Verifying the DFT Requirements: DFT Signals for Wrapped Cores |       |

| Performing Scan Chain Insertion: Wrapped Core                                |       |

| Verifying the ICL Model                                                      |       |

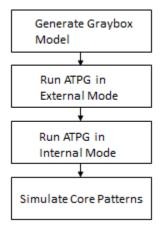

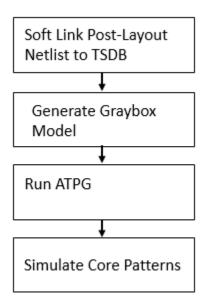

| Performing ATPG Pattern Generation: Wrapped Core                             |       |

| Running Recommended Validation Step for Pre-Layout Design Sign Off           | . 167 |

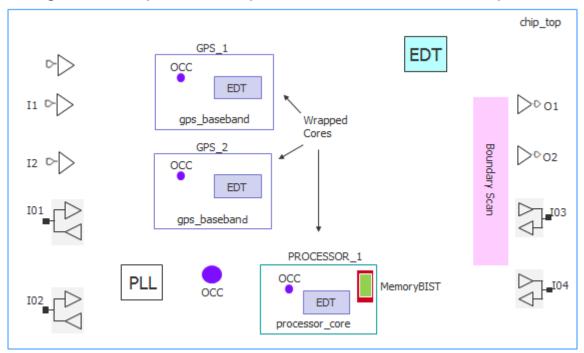

| RTL and Scan DFT Insertion Flow for the Top Chip.                            |       |

| Top-Level DFT Insertion Example                                              |       |

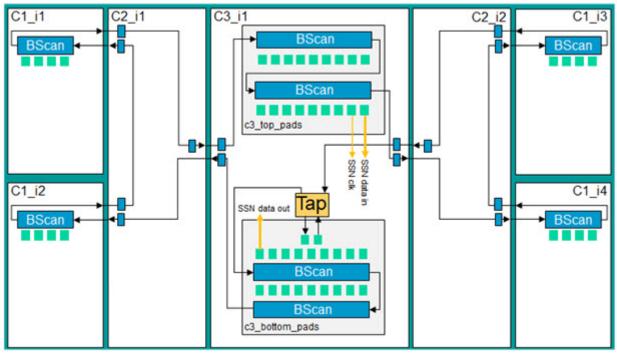

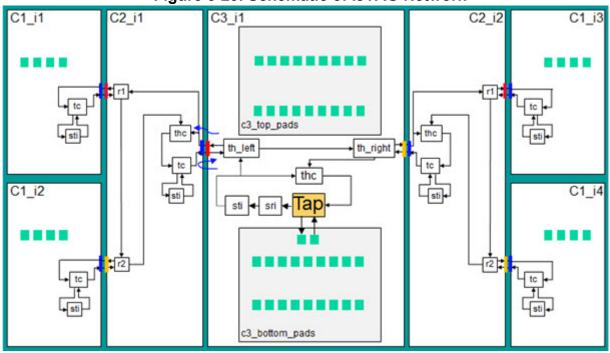

| First DFT Insertion Pass: Performing Top-Level MemoryBIST and Boundary Scan  |       |

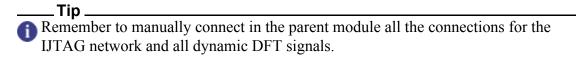

| Second DFT Insertion Pass: Inserting Top-Level EDT and OCC                   |       |

| Top-Level Scan Chain Insertion Example                                       |       |

| Top-Level ATPG Pattern Generation Example                                    |       |

| Performing Top-Level ATPG Pattern Retargeting.                               |       |

| RTL and Scan DFT Insertion Flow for Sub-Blocks                               |       |

| DFT Insertion Flow for the Sub-Block                                         |       |

| DFT Insertion Flow for the Next Parent Level                                 |       |

| RTL and Scan DFT Insertion Flow for Instrument Blocks                        |       |

| DFT Insertion Flow for the Instrument Block                                  |       |

| Instrument Block DFT Insertion Flow for the Next Parent Level                |       |

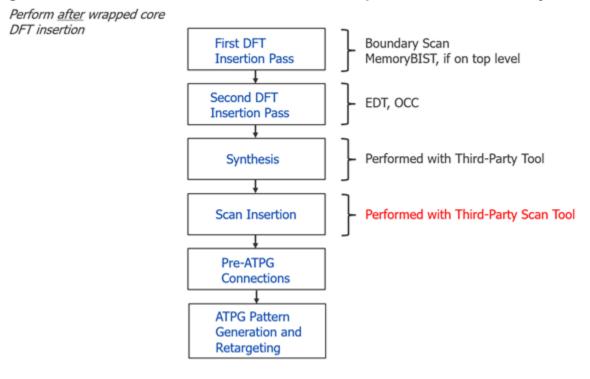

| RTL and DFT Insertion Flow With Third-Party Scan                             |       |

| DFT Insertion Flow With Third-Party Scan Insertion                           |       |

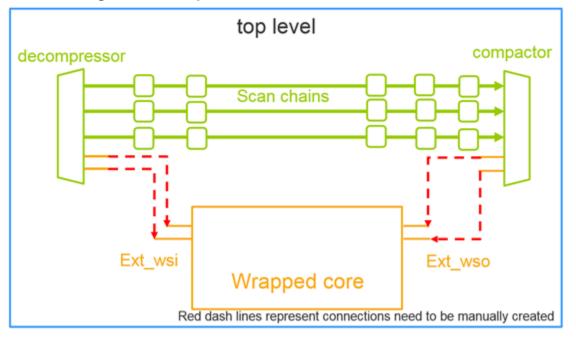

| Wrapped Core DFT Insertion With Third-Party Scan                             | . 195 |

| Top Chip DFT Insertion with Third-Party Scan.                                |       |

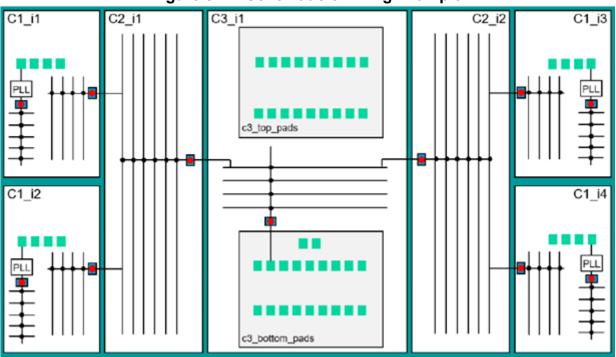

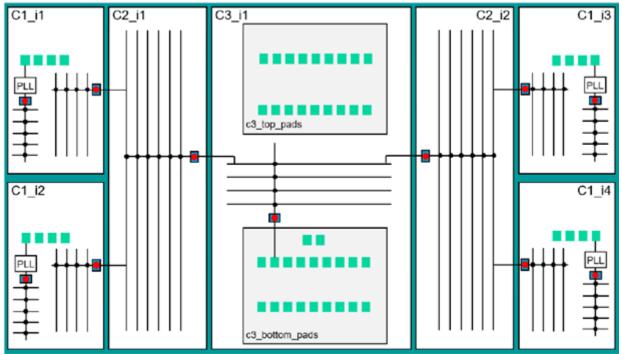

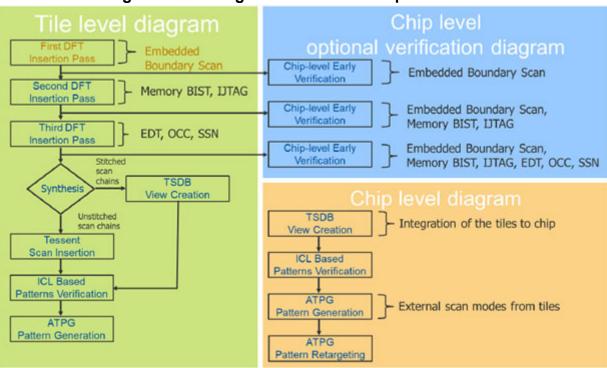

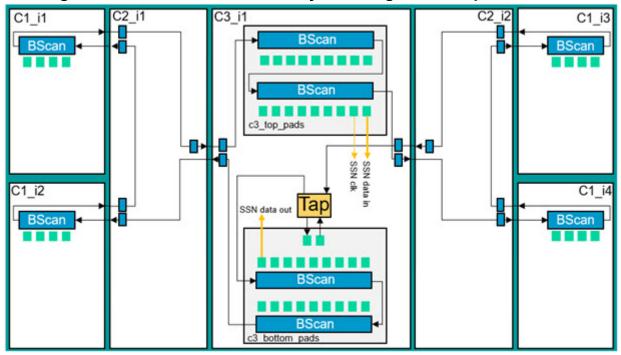

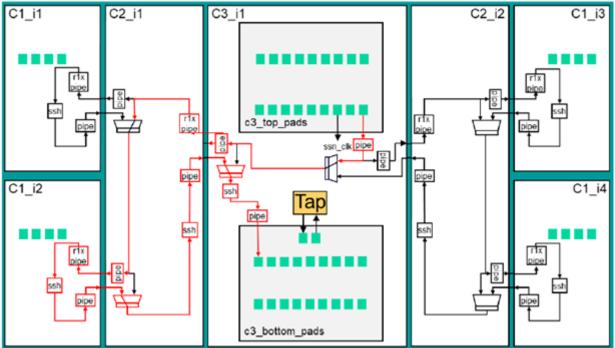

| Tessent Shell Flow for Tiled Designs                                         |       |

| Tiling DFT Terminology                                                       |       |

| How The DFT Insertion Flow Applies to Tiled Designs                          |       |

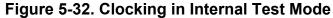

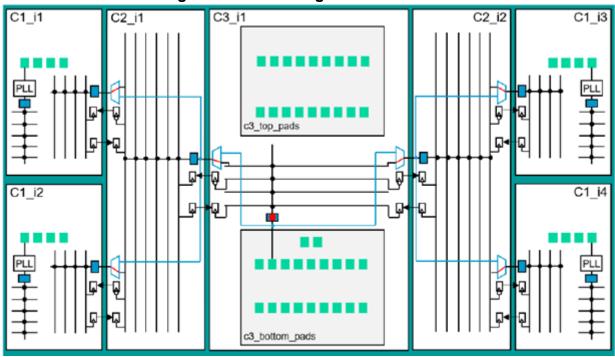

| Clocking During Logic Test                                                   |       |

| Pre-DFT Design Modification and Integration.                                 |       |

| Chip Level Port Requirements and Connections                                 |       |

| Tile Level Port Connections and Requirements.                                |       |

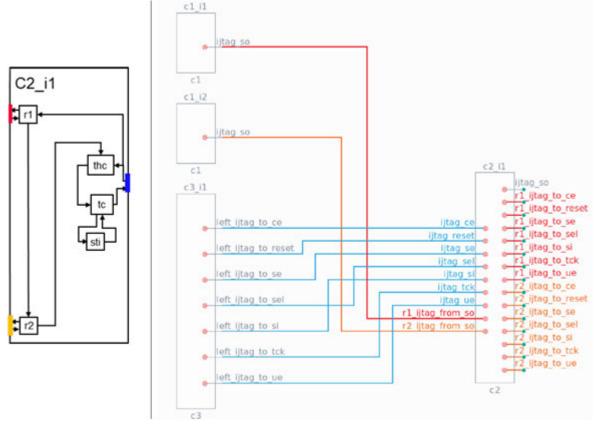

| Creation of IJTAG Graybox Example Flow for a Tiled Design                    | . 233 |

| Tiling Flow Used in Example.                                                 |       |

| DFT Flow for Tiles Without TAP and BISR Controllers                          |       |

| Embedded Boundary Scan Insertion in Tiles Without a TAP Controller           |       |

| IJTAG Network Insertion in Tiles Without a TAP Controller                    |       |

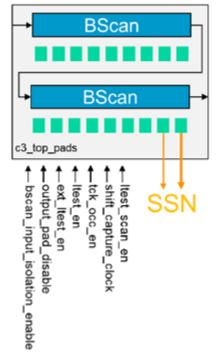

| Memory Test Insertion in Tiles Without TAP and BISR Controllers              |       |

| SSN and EDT Insertion in Tiles Without TAP and BISR Controllers              |       |

| Scan Insertion and Scan Modes in Tiles Without TAP and BISR Controllers      |       |

| Patterns Generation in Tiles Without a TAP Controller                        |       |

| Verification and Simulations                                                 |       |

| Embedded Boundary Scan Insertion in Tiles With a TAP Controller              |       |

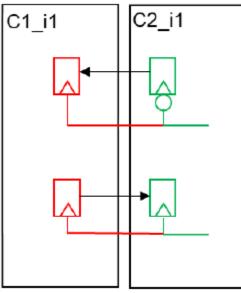

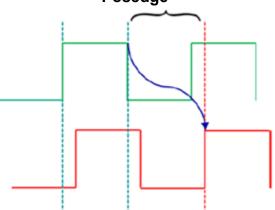

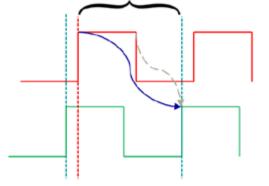

| IJTAG Network Insertion in Tiles With a TAP Controller                       |       |

|                                                                              | . 201 |

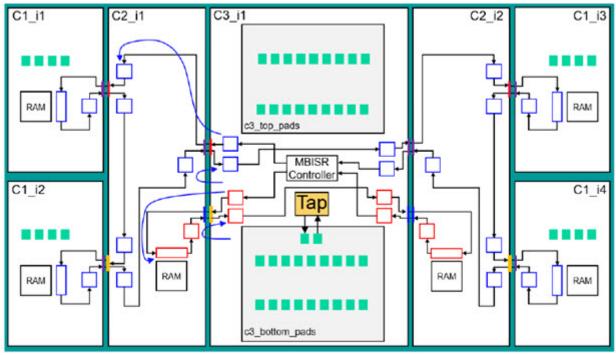

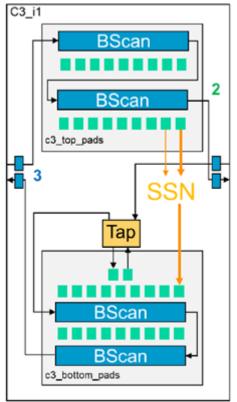

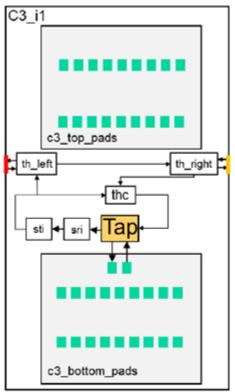

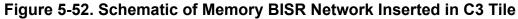

| Memory BISR Insertion for Tiles With a BISR Controller                                    | 263  |

|-------------------------------------------------------------------------------------------|------|

|                                                                                           | 265  |

| Scan Insertion and Scan Modes for Tiles with Promoted OCCs                                | 267  |

| Chip-Level Integration for the Tiling Flow                                                | 269  |

|                                                                                           | 269  |

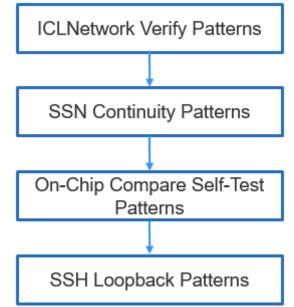

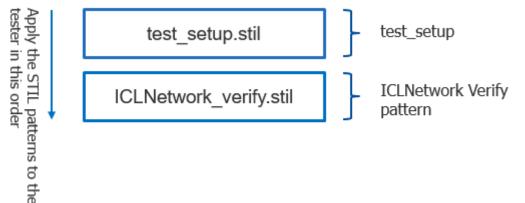

| IJTAG Based Verification Patterns                                                         | 270  |

|                                                                                           | 270  |

|                                                                                           | 275  |

|                                                                                           | 277  |

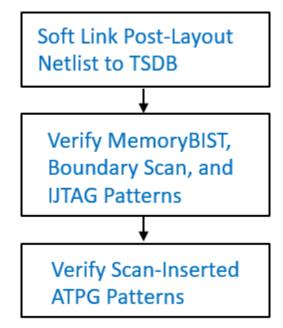

| Overview of the Post-Layout Validation Flow                                               | 277  |

| Soft Link TSDB and Post-Layout Netlist                                                    | 278  |

|                                                                                           | 279  |

|                                                                                           | 280  |

|                                                                                           | 282  |

|                                                                                           | 287  |

| Simulation Wrapper Creation                                                               | 287  |

| Testbench Examples                                                                        | 290  |

| Hybrid TK/LBIST Flow for Flat Designs                                                     | 295  |

| RTL and Scan DFT Insertion Flow With Hybrid TK/LBIST                                      | 295  |

|                                                                                           | 296  |

|                                                                                           | 299  |

|                                                                                           | 304  |

|                                                                                           | 307  |

|                                                                                           | 309  |

|                                                                                           | 312  |

| $-\partial$                                                                               | 314  |

|                                                                                           | 317  |

| Overview of Multiple Load ATPG on Memories for Wrapped Cores With Built-in Self Re<br>317 | pair |

|                                                                                           | 318  |

|                                                                                           | 321  |

|                                                                                           | 324  |

|                                                                                           | 324  |

|                                                                                           | 327  |

|                                                                                           | 327  |

|                                                                                           | 327  |

|                                                                                           | 328  |

|                                                                                           | 329  |

|                                                                                           | 329  |

|                                                                                           | 527  |

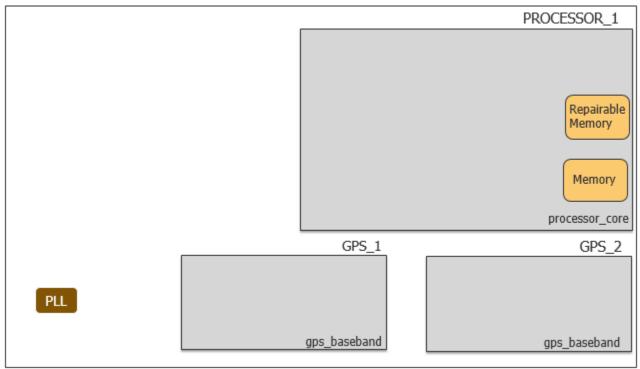

| Chapter 6                                                                                 |      |

| •                                                                                         | 331  |

|                                                                                           | 332  |

|                                                                                           | 333  |

|                                                                                           | 338  |

|                                                                                           | 339  |

|                                                                                           | 340  |

|                                                                                           | 340  |

|                                                                                           | 545  |

| Test Point, X-Bounding, and Scan Insertion: processor_core                                                                                                                                                                                                | 347                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ATPG Pattern Generation: processor_core                                                                                                                                                                                                                   |                                        |

| LogicBIST Fault Simulation: processor_core                                                                                                                                                                                                                |                                        |

| LogicBIST Pattern Generation: processor_core.                                                                                                                                                                                                             | 354                                    |

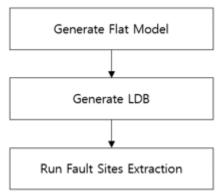

| Interconnect Bridge/Open UDFM Generation: processor_core                                                                                                                                                                                                  | 356                                    |

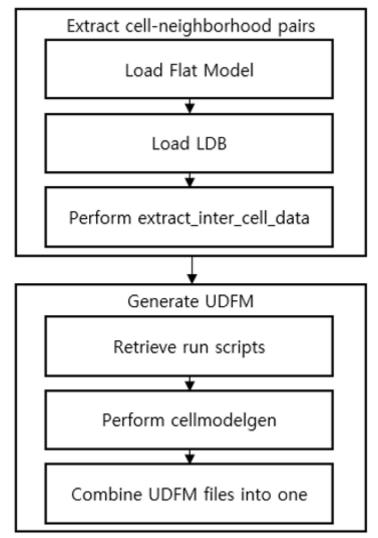

| Cell-Neighborhood UDFM Generation: processor_core                                                                                                                                                                                                         | 358                                    |

| Automotive-Grade ATPG Pattern Generation: processor_core                                                                                                                                                                                                  | 362                                    |

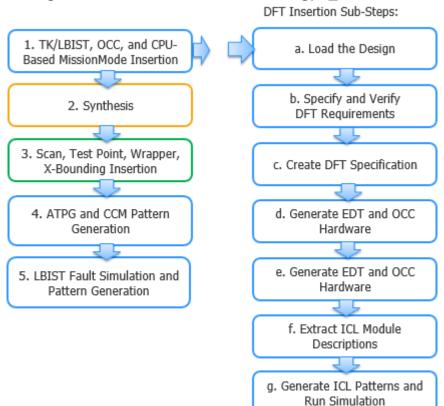

| DFT Insertion Flow for the GPS Baseband Physical Block                                                                                                                                                                                                    | 369                                    |

| DFT Insertion Pass With In-System Test: gps_baseband                                                                                                                                                                                                      |                                        |

| LogicBIST Fault Simulation With One NCP: gps_baseband                                                                                                                                                                                                     | 374                                    |

| Interconnect Bridge/Open UDFM Generation: gps_baseband                                                                                                                                                                                                    |                                        |

| Cell-Neighborhood UDFM Generation: gps_baseband                                                                                                                                                                                                           | 375                                    |

| Automotive-Grade ATPG Pattern Generation: gps_baseband                                                                                                                                                                                                    | 375                                    |

| Top-Level DFT Insertion for the Automotive Flow                                                                                                                                                                                                           | 376                                    |

| First DFT Insertion Pass: Top with MemoryBIST, BISR, and Boundary Scan                                                                                                                                                                                    | 376                                    |

| Second DFT Insertion Pass: Top with EDT, OCC, and In-System Test                                                                                                                                                                                          |                                        |

| Scan Insertion for the Top Design                                                                                                                                                                                                                         | 387                                    |

| ATPG Pattern Generation for the Top Design                                                                                                                                                                                                                | 389                                    |

| ATPG Pattern Retargeting for the Top Design.                                                                                                                                                                                                              | 390                                    |

| Interconnect Bridge/Open UDFM Generation for the Top Design                                                                                                                                                                                               | 390                                    |

| Cell-Neighborhood UDFM Generation for the Top Design.                                                                                                                                                                                                     |                                        |

| Automotive-Grade ATPG Pattern Generation for the Top Design                                                                                                                                                                                               | 391                                    |

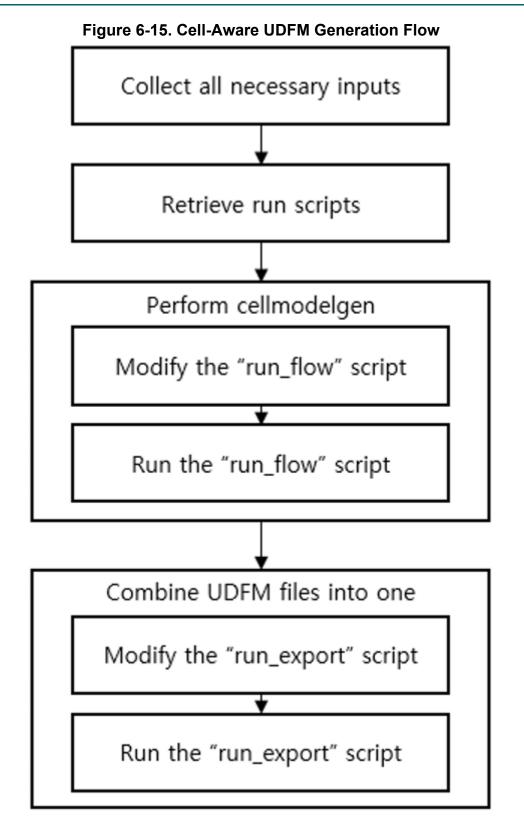

| UDFM Generation for Cell-Aware ATPG                                                                                                                                                                                                                       |                                        |

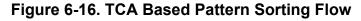

| TCA Based Pattern Sorting.                                                                                                                                                                                                                                | 393                                    |

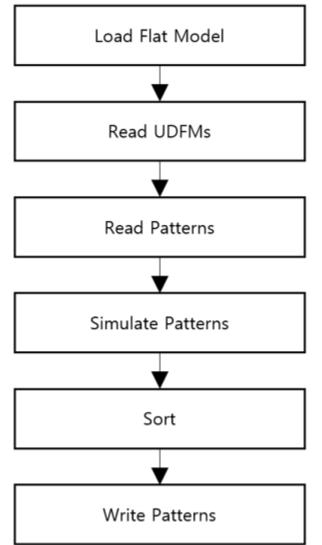

| Functional Mode Fault Tolerance for Static IJTAG Signals                                                                                                                                                                                                  | 395                                    |

|                                                                                                                                                                                                                                                           |                                        |

| Chapter 7                                                                                                                                                                                                                                                 |                                        |

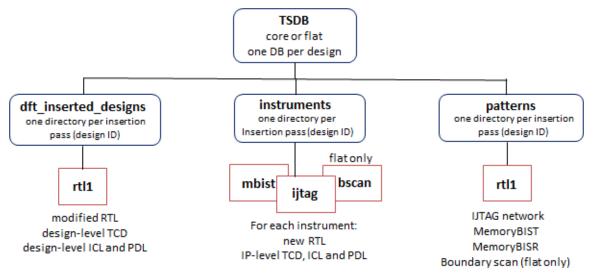

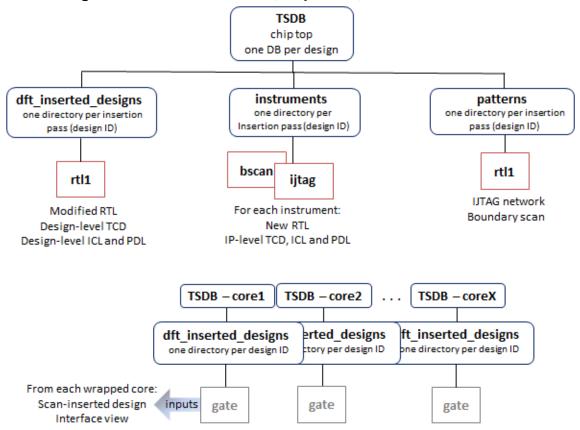

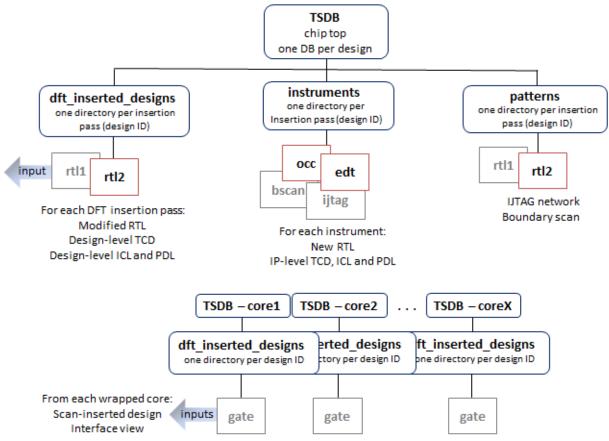

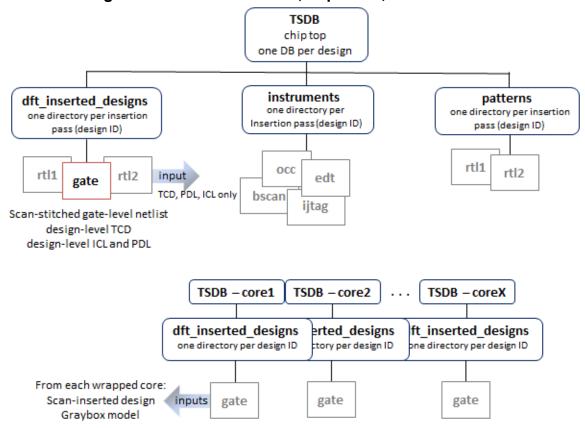

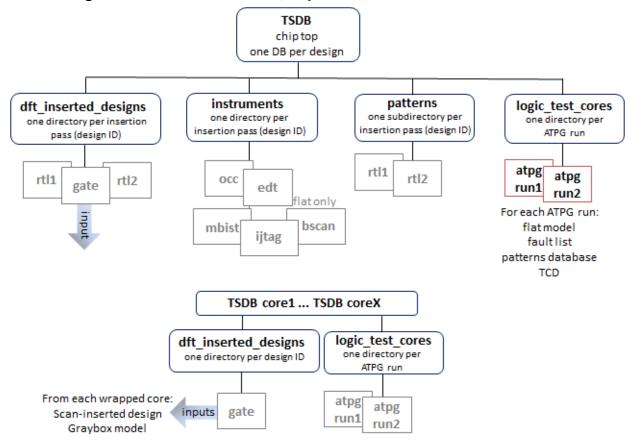

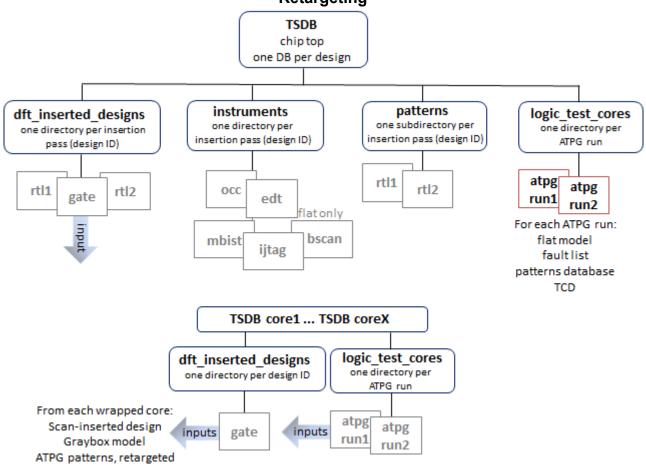

| <b>TSDB Data Flow for the Tessent Shell Flow</b>                                                                                                                                                                                                          | 401                                    |

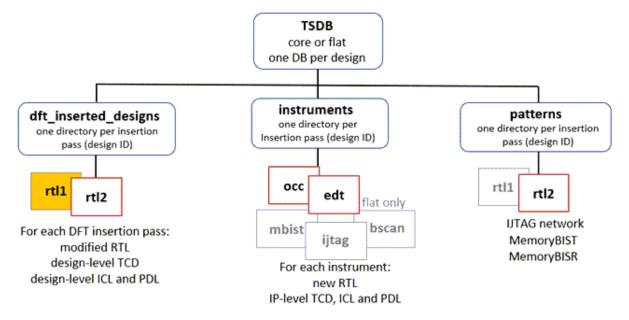

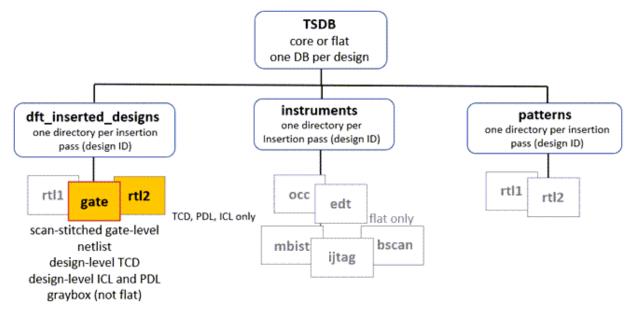

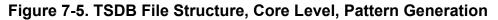

| Core-Level or Flat TSDB Data Flow                                                                                                                                                                                                                         | 401                                    |

| Top-Level TSDB Data Flow                                                                                                                                                                                                                                  | 407                                    |

| 1                                                                                                                                                                                                                                                         |                                        |

| Chapter 8                                                                                                                                                                                                                                                 |                                        |

| Streaming Scan Network (SSN)                                                                                                                                                                                                                              | 415                                    |

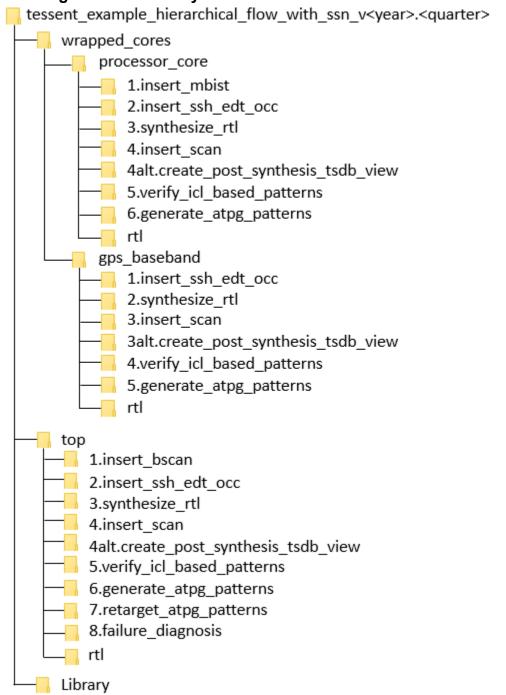

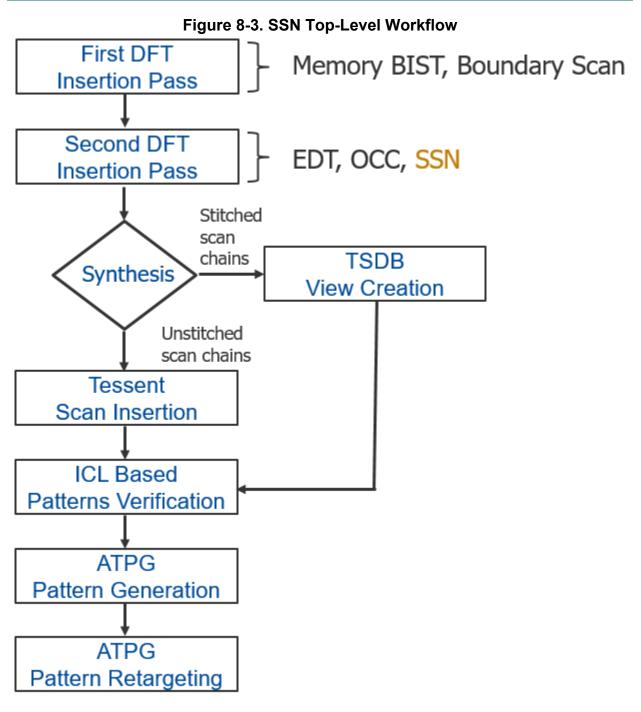

| Tessent SSN Workflows                                                                                                                                                                                                                                     |                                        |

| Block-Level SSN Insertion and Verification                                                                                                                                                                                                                | 419                                    |

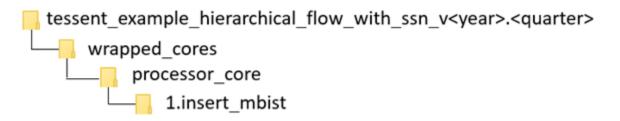

| First DFT Insertion Pass: Performing Block-Level MemoryBIST                                                                                                                                                                                               | 421                                    |

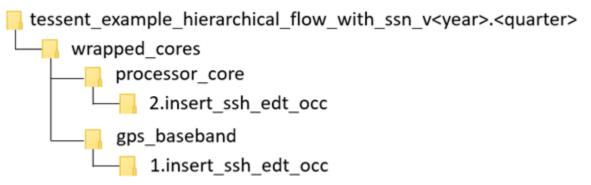

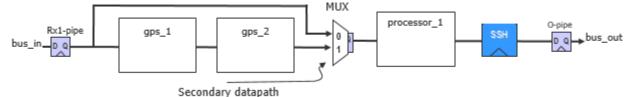

| Second DFT Insertion Pass: Inserting Block-Level EDT, OCC, and SSN                                                                                                                                                                                        | 421                                    |

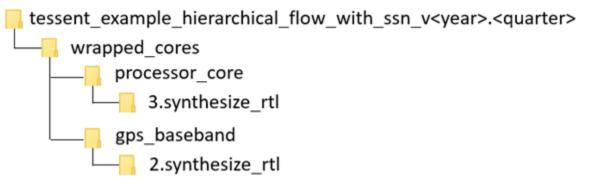

| Synthesis for Block-Level Insertion                                                                                                                                                                                                                       | 428                                    |

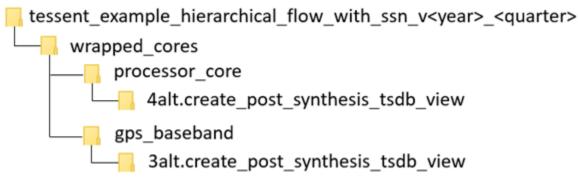

| Creating the Post-Synthesis TSDB View (Block-Level)                                                                                                                                                                                                       | 429                                    |

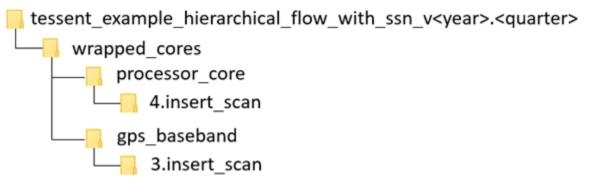

| Performing Scan Chain Insertion With Tessent Scan (Block-Level).                                                                                                                                                                                          | 431                                    |

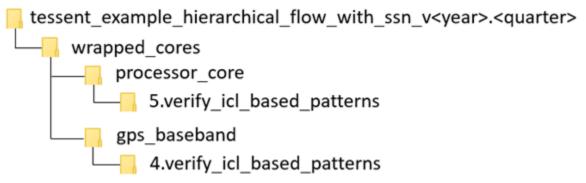

| Verifying the ICL-Based Patterns After Synthesis (Block-Level).                                                                                                                                                                                           |                                        |

|                                                                                                                                                                                                                                                           | 131                                    |

|                                                                                                                                                                                                                                                           | 434                                    |

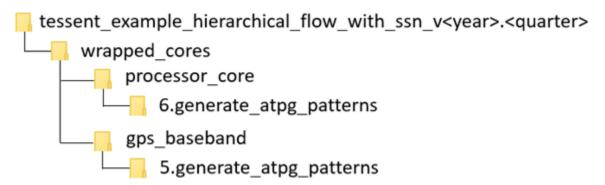

| Generating Block-Level ATPG Patterns                                                                                                                                                                                                                      | 437                                    |

| Generating Block-Level ATPG Patterns                                                                                                                                                                                                                      | 437<br>444                             |

| Generating Block-Level ATPG Patterns                                                                                                                                                                                                                      | 437<br>444<br>446                      |

| Generating Block-Level ATPG Patterns                                                                                                                                                                                                                      | 437<br>444<br>446<br>449               |

| Generating Block-Level ATPG Patterns<br>Top-Level SSN Insertion and Verification.<br>First DFT Insertion Pass: Performing Top-Level MemoryBIST.<br>Second DFT Insertion Pass: Inserting Top-Level EDT, OCC, and SSN.<br>Synthesis for Top-Level Insertion | 437<br>444<br>446<br>449<br>457        |

| Generating Block-Level ATPG Patterns                                                                                                                                                                                                                      | 437<br>444<br>446<br>449<br>457<br>458 |

| Verifying the ICL-Based Patterns After Synthesis (Top-Level)                 | 459 |

|------------------------------------------------------------------------------|-----|

| Generating Top-Level ATPG Patterns                                           | 459 |

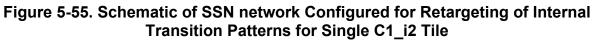

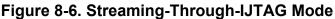

| Retargeting ATPG Patterns                                                    | 461 |

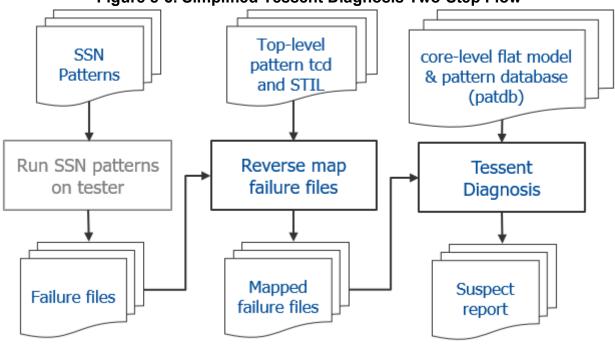

| Performing Reverse Failure Mapping for SSN Pattern Diagnosis.                | 464 |

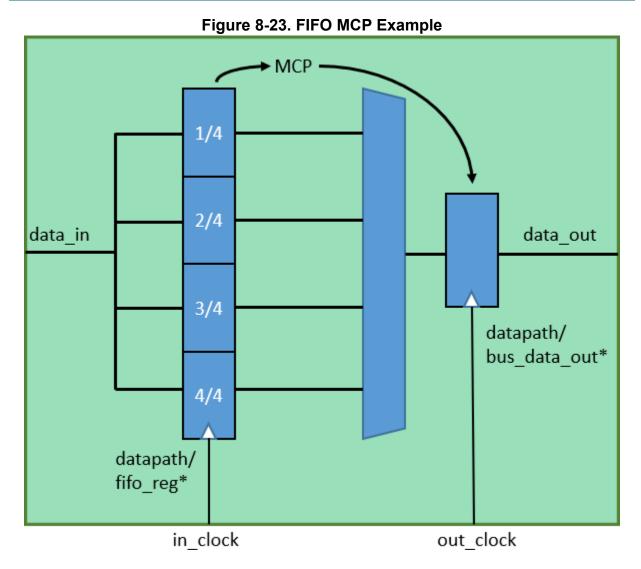

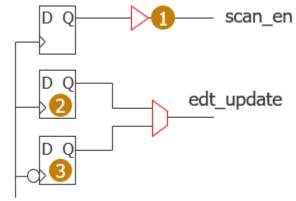

| Advanced Topics                                                              | 469 |

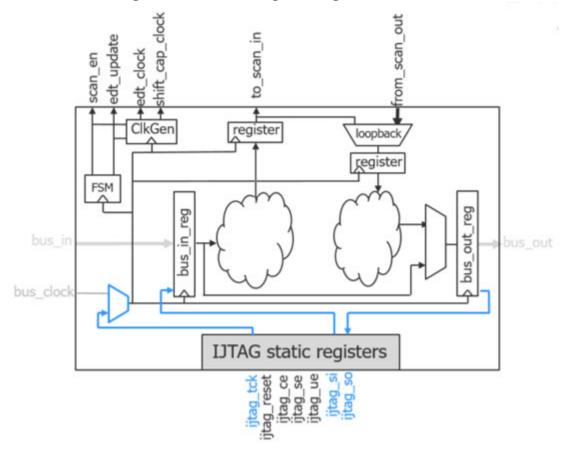

| Streaming-Through-IJTAG Scan Data                                            | 469 |

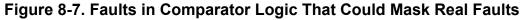

| On-Chip Compare With SSN                                                     |     |

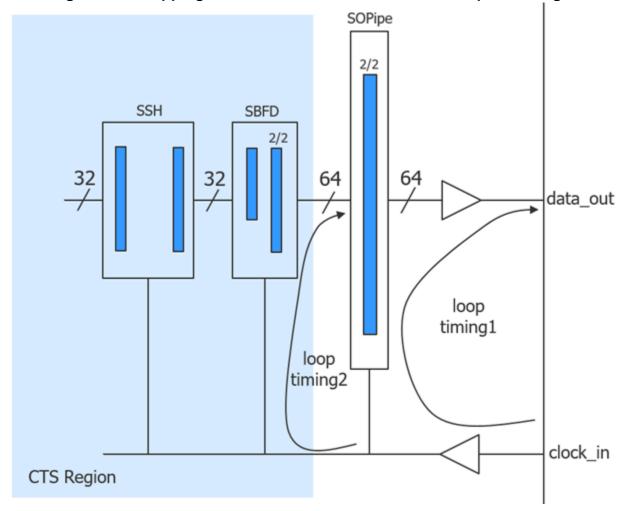

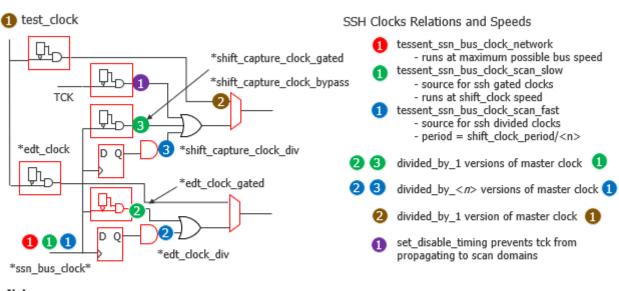

| Types of Clock Networks To Use With SSN                                      | 482 |

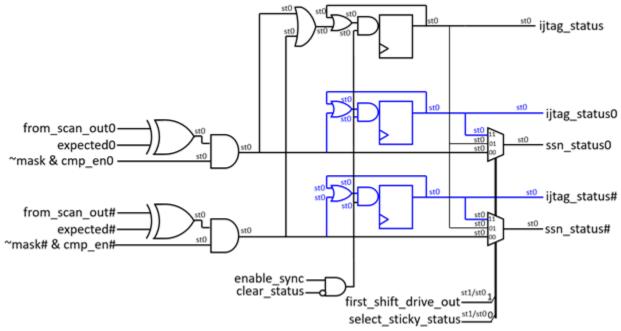

| Broadcast to Identical SSN Datapaths                                         |     |

| Yield Statistics on ATE With SSN                                             | 486 |

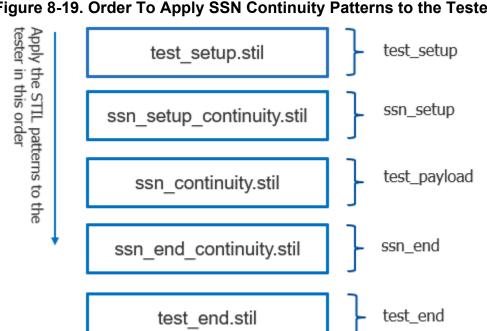

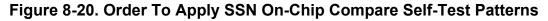

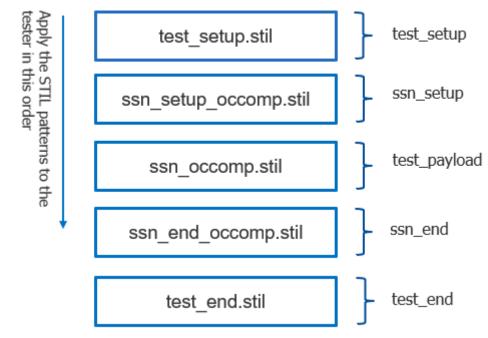

| Manufacturing Patterns With SSN                                              | 492 |

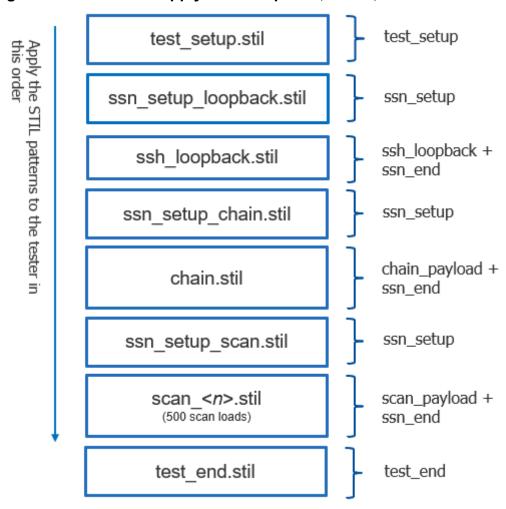

| Manufacturing Pattern Quick Reference                                        |     |

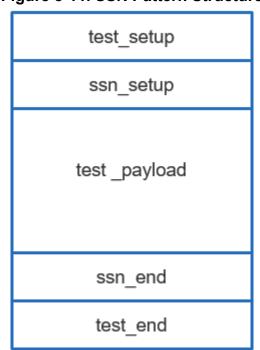

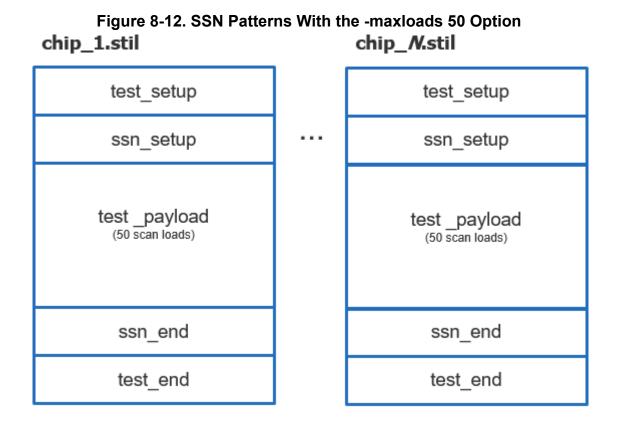

| SSN Pattern Structure                                                        |     |

| How To Write Complete SSN Patterns                                           |     |

| How To Write JTAG and Payload Procedures Separately.                         |     |

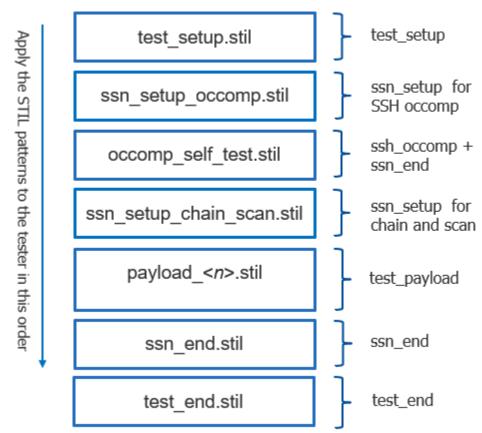

| How To Write SSN On-Chip Compare Patterns                                    | 499 |

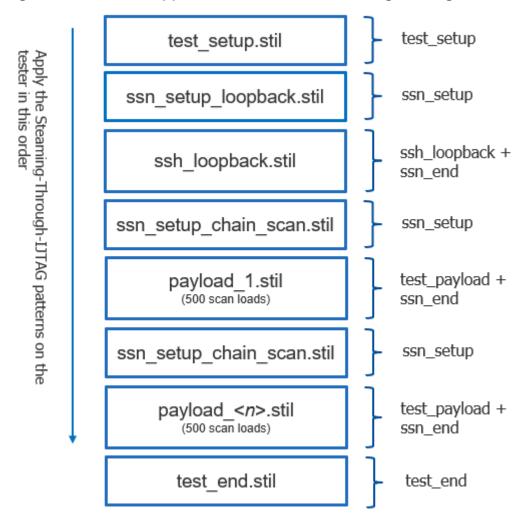

| How To Write Streaming-Through-IJTAG Patterns                                |     |

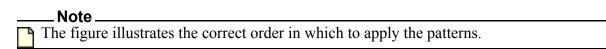

| SSN Debug on the Tester                                                      | 503 |

| Signoff Patterns With SSN                                                    |     |

| Block-Level Signoff Patterns                                                 |     |

| Top-Level Signoff Patterns                                                   |     |

|                                                                              |     |

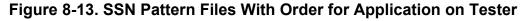

| Signoff Pattern Quick Reference                                              | 517 |

| SSN SDC Constraints in the Design Flow                                       | 518 |

|                                                                              |     |

| SSN/SSH SDC Constraint Descriptions.                                         |     |

| Burn-In Pattern Support                                                      | 555 |

| Burn-In Pattern Överview                                                     |     |

| Recommended Flows for Creating Burn-In Patterns                              | 557 |

| Burn-In Functionality Limitations                                            | 559 |

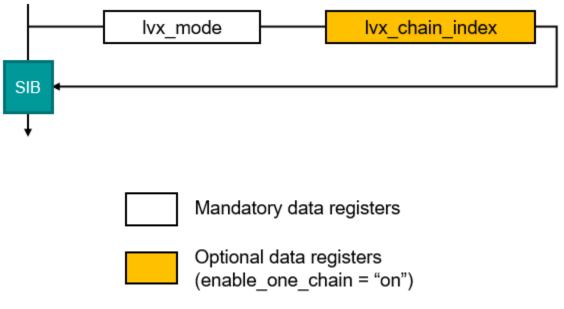

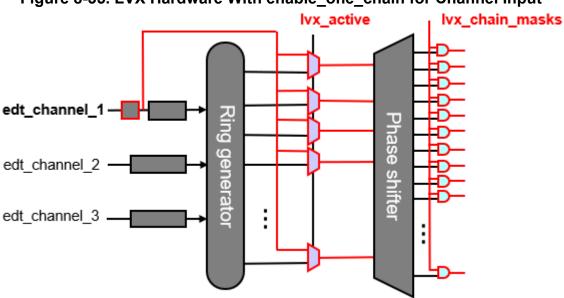

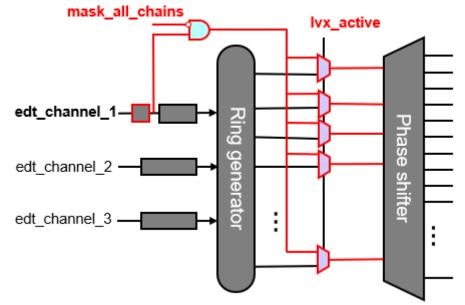

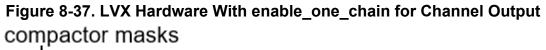

| LVX Support.                                                                 | 560 |

| LVX Hardware Requirements                                                    |     |

| Creating EDT With LVX Hardware.                                              | 560 |

| LVX Operation Modes With LVX Hardware Configuration.                         |     |

| Configuring and Generating LVX Patterns                                      | 567 |

| Tessent SSN Examples and Solutions                                           | 570 |

| Third-Party OCCs With SSN                                                    |     |

| SSN Frequently Asked Questions                                               |     |

| SSN Limitations                                                              | 574 |

|                                                                              |     |

| Chapter 9                                                                    |     |

| Tessent Examples and Solutions                                               |     |

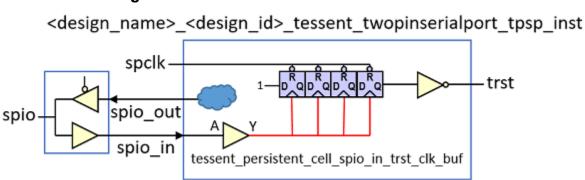

| How to Avoid Simulation Issues When Using the Two-Pin Serial Port Controller | 578 |

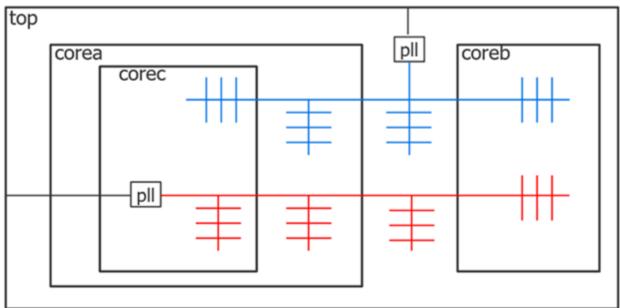

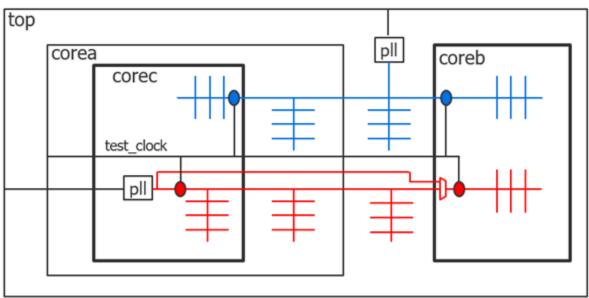

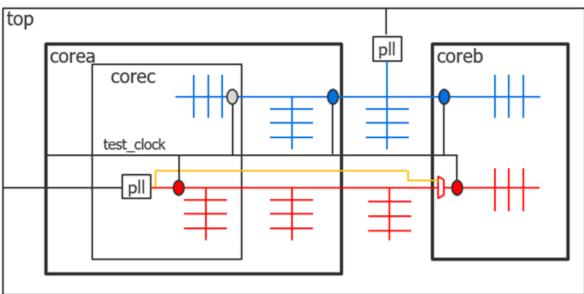

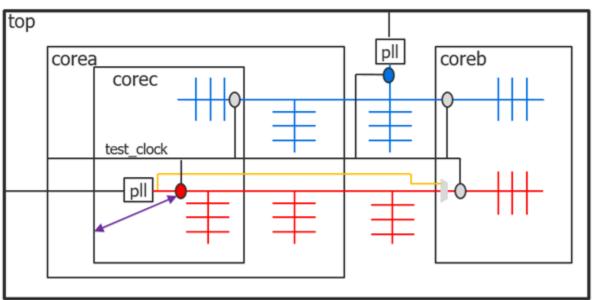

| How to Handle Clocks Sourced by Embedded PLLs During Logic Test              | 580 |

| How to Design Capture Windows for Hybrid TK/LBIST.                           |     |

| How to Use Boundary Scan in a Wrapped Core                                   | 588 |

| How to Use an Older Core TSDB With Newly-Inserted DFT Cores                  | 591 |

| TAP Configuration                                                            |     |

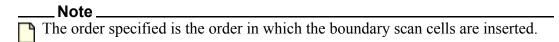

| Insert a Stand-Alone TAP in a Design                                         |     |

| -                                                                            |     |

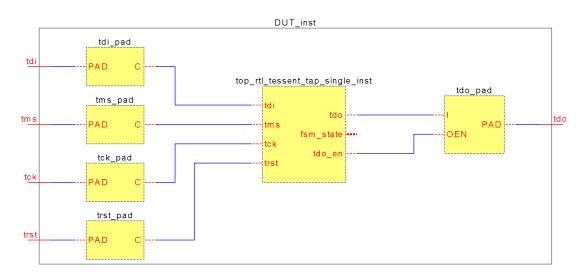

| Insert a TAP with an IJTAG Host Scan Interface.                                      | 594               |

|--------------------------------------------------------------------------------------|-------------------|

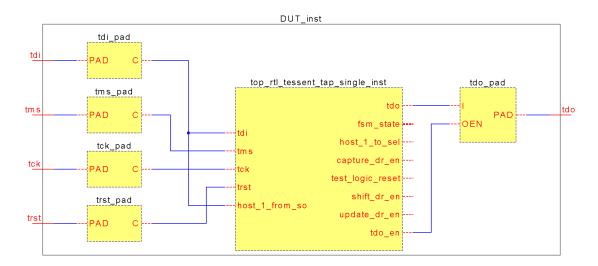

| Insert a Compliance Enable TAP with an IJTAG Interface                               | 595               |

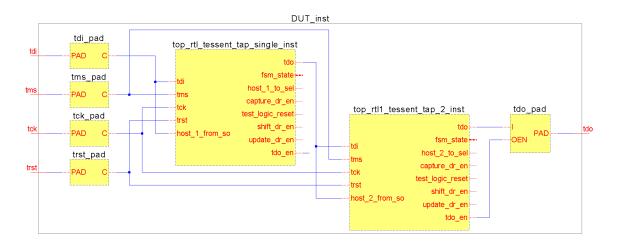

| Insert a Daisy-Chained TAP                                                           | 597               |

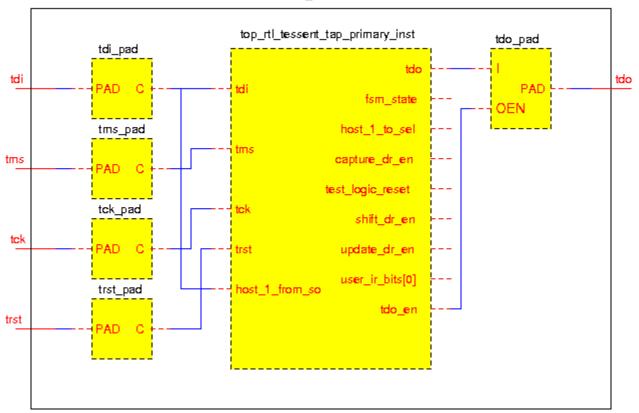

| Insert a Primary TAP                                                                 | 598               |

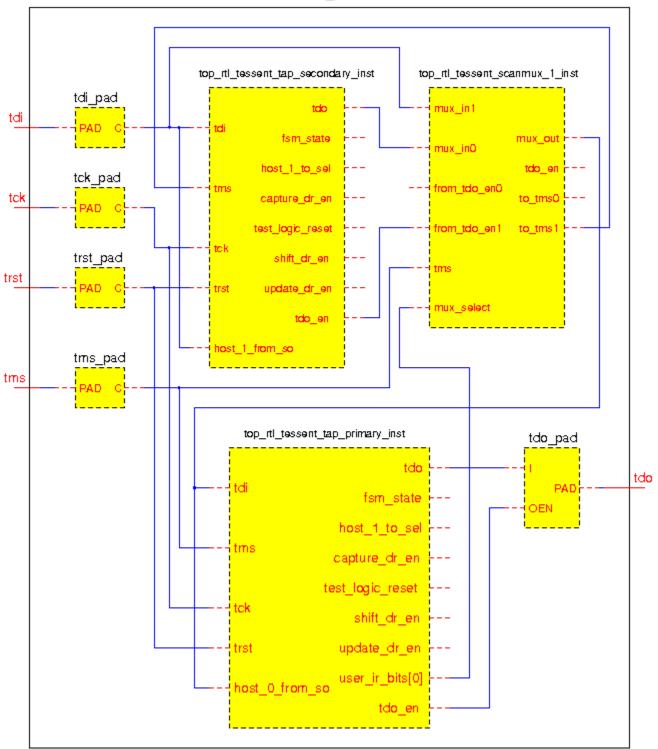

| Insert a Secondary TAP                                                               | 600               |

| Connecting to a Third-Party TAP.                                                     | 603               |

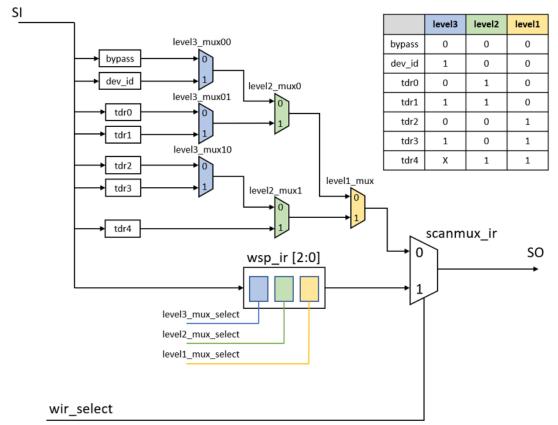

| How to Create a WSP Controller in Tessent Shell                                      | 603               |

| How to Set Up Third-Party Synthesis                                                  | 611               |

| How to Set Up Support for Third-Party OCCs                                           | 614               |

| How to Configure Files for Third-Party OCCs                                          | 614               |

| Test Logic Insertion                                                                 | 615               |

| Configuration for Scan Insertion                                                     | 617               |

| Pattern Generation and Simulation                                                    | 617               |

| Post-Synthesis Update                                                                | 621               |

| ICL and TCD Post-Synthesis Update                                                    | 621               |

| Limitations Related to System Verilog Interface Arrays.                              | 622               |

| Updating ICL Attributes From the Design                                              | 623               |

| Matching Requirements for Port Names in Post-Synthesis Update                        | 624               |

| Design Name Mapping Commands                                                         | 625               |

| Design Name Mapping.                                                                 | 625               |

| Default Matching Rules for the get_pins, get_ports, and get_instances -match_rtl_reg |                   |

| Commands                                                                             | 625               |

|                                                                                      |                   |

| Chapter 10                                                                           |                   |

| Test Procedure File                                                                  | <b>627</b>        |

| Test Procedure File Creation                                                         | 628               |

| Test Procedure File Syntax                                                           | 628               |

| Test Procedure File Structure                                                        | 633               |

| #include Statement                                                                   | 633               |

| Set Statement                                                                        | 634               |

| Alias Definition                                                                     | 637               |

| Timing Variables                                                                     | 639               |

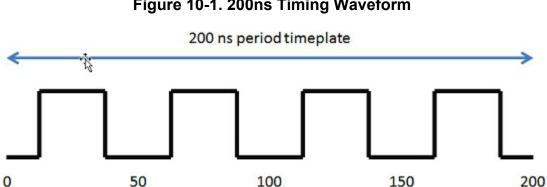

| Timeplate Definition.                                                                |                   |

| Multiple-Pulse Clocks.                                                               |                   |

|                                                                                      | 648               |

| Inferred Timing                                                                      | 649               |

| Differences Between Default add clock and 1x Multiplier Clock                        | 650               |

| Always Block                                                                         | 650               |

| Procedure Definition.                                                                | 651               |

| Clock Control Definition                                                             | 662               |

|                                                                                      | 671               |

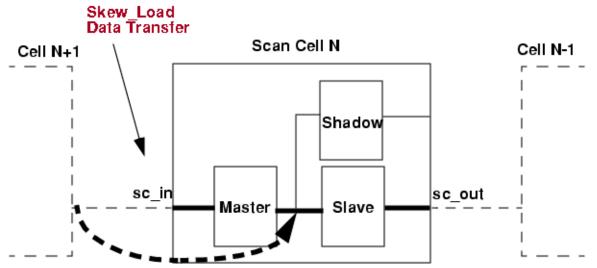

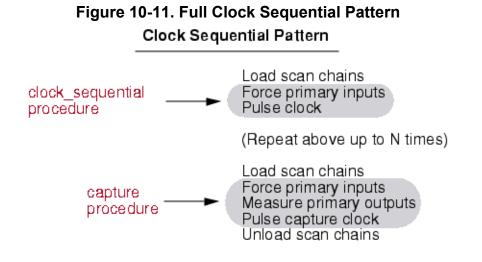

| The Procedures                                                                       | 672               |

|                                                                                      | 072               |

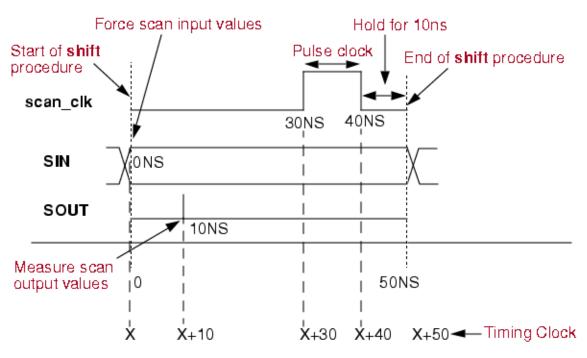

| Shift (Required)          Alternate Shift Procedure (Optional)                       | 675               |

|                                                                                      | 675<br>677        |

|                                                                                      | 677               |

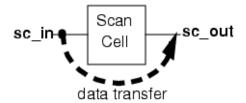

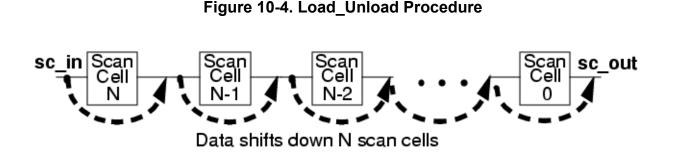

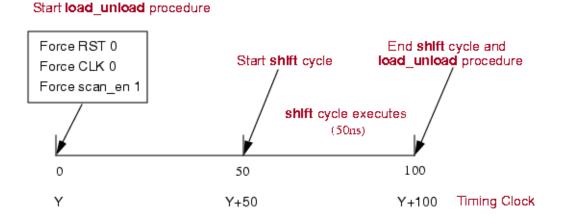

| Load_Unload (Required)                                                               | 677<br>678        |

| Load_Unload (Required)                                                               | 677<br>678<br>681 |

| Load_Unload (Required)                                                               | 677<br>678        |

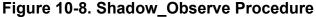

| Skew_Load (Optional)                                                                                                                                                                                                   | 684                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Clock_run (Optional)                                                                                                                                                                                                   | 686                                                  |

| Capture Procedures (Optional)                                                                                                                                                                                          | 688                                                  |

| Rules for Creating and Editing a Default Capture Procedure                                                                                                                                                             | 689                                                  |

| Rules for Creating and Editing Named Capture Procedures                                                                                                                                                                | 689                                                  |

| Slow and Load Types in the Cycle Statement                                                                                                                                                                             | 691                                                  |

| launch capture pair Statement                                                                                                                                                                                          | 692                                                  |

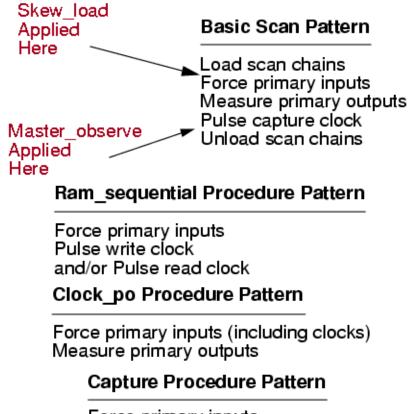

| Clock_sequential (Optional)                                                                                                                                                                                            | 693                                                  |

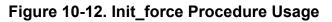

| Init_force (Optional)                                                                                                                                                                                                  | 694                                                  |

| Test_end (Optional, all ATPG tools)                                                                                                                                                                                    | 695                                                  |

| Sub procedure                                                                                                                                                                                                          | 696                                                  |

| Additional Support for Test Procedure Files                                                                                                                                                                            | 698                                                  |

| Creating Test Procedure Files for End Measure Mode                                                                                                                                                                     | 699                                                  |

| Serial Register Load and Unload for LogicBIST and ATPG                                                                                                                                                                 | 703                                                  |

| Register Load and Unload Use Models                                                                                                                                                                                    | 703                                                  |

| Static Versus Dynamic Register Variables                                                                                                                                                                               | 703                                                  |

| Test Procedure File Modifications                                                                                                                                                                                      | 704                                                  |

| Dofile Modifications.                                                                                                                                                                                                  | 707                                                  |

| Serial Load and Unload DRC Rules                                                                                                                                                                                       | 710                                                  |

| P13 and P54                                                                                                                                                                                                            | 710                                                  |

| P66                                                                                                                                                                                                                    | 710                                                  |

| W5                                                                                                                                                                                                                     | 711                                                  |

| Procedure Examples                                                                                                                                                                                                     |                                                      |

| Notes About Using the stil2tessent Tool                                                                                                                                                                                |                                                      |

|                                                                                                                                                                                                                        |                                                      |

| Extraction of Strobe Timing Information from STIL (SPF)                                                                                                                                                                | 716                                                  |

| The STIL ClockStructures Block                                                                                                                                                                                         | 716<br>717                                           |

| Test Procedure File Commands and Output Formats                                                                                                                                                                        | /1/                                                  |

| Chapter 11                                                                                                                                                                                                             |                                                      |

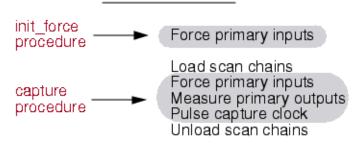

| Tessent Visualizer                                                                                                                                                                                                     | 719                                                  |

|                                                                                                                                                                                                                        |                                                      |

| Invoking Tessent Visualizer                                                                                                                                                                                            | 720                                                  |

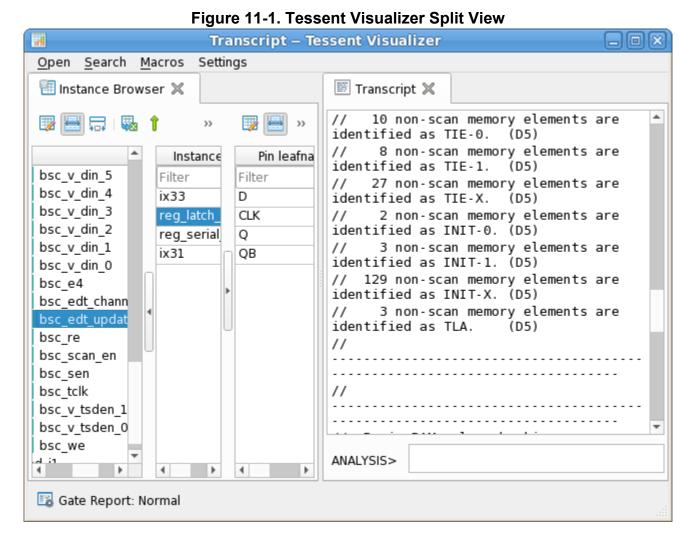

| Framework Overview                                                                                                                                                                                                     | 722                                                  |

| Tessent Visualizer Components and Preferences                                                                                                                                                                          |                                                      |

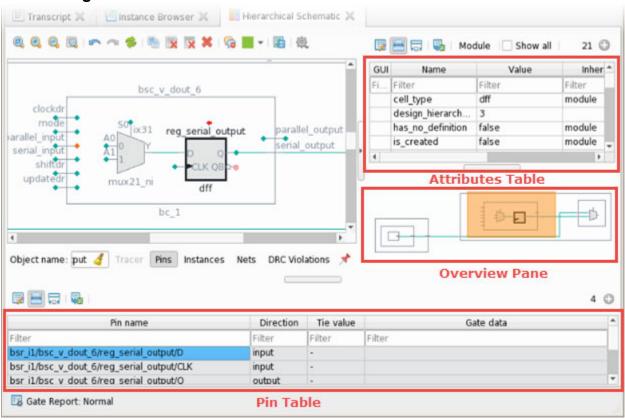

| Tables                                                                                                                                                                                                                 |                                                      |

| Table Toolbar Features.                                                                                                                                                                                                | 727                                                  |

|                                                                                                                                                                                                                        |                                                      |

| Columns and Filters Editor.                                                                                                                                                                                            | 729                                                  |

| Columns and Filters Editor                                                                                                                                                                                             | 730                                                  |

| Columns and Filters Editor                                                                                                                                                                                             | 730<br>733                                           |

| Columns and Filters Editor                                                                                                                                                                                             | 730<br>733<br>733                                    |

| Columns and Filters Editor                                                                                                                                                                                             | 730<br>733                                           |

| Columns and Filters Editor                                                                                                                                                                                             | 730<br>733<br>733                                    |

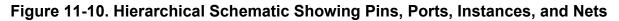

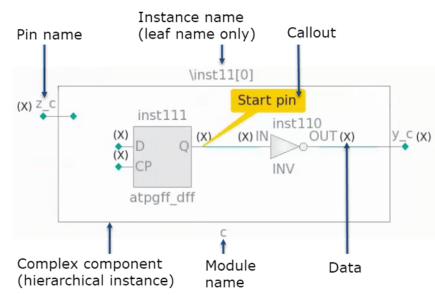

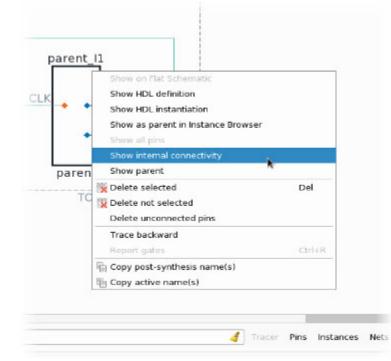

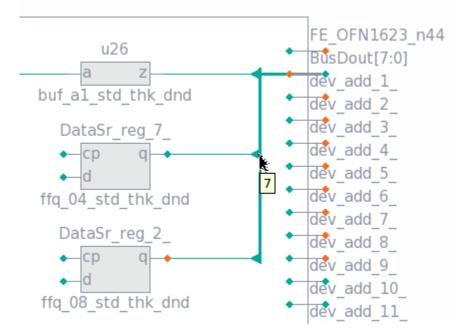

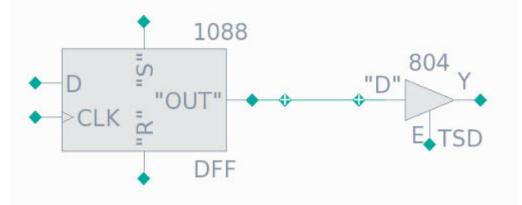

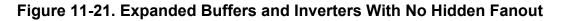

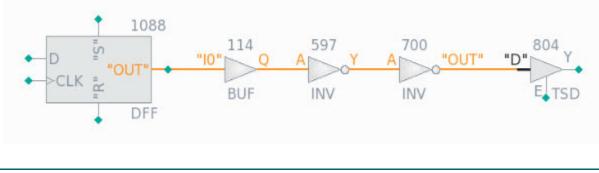

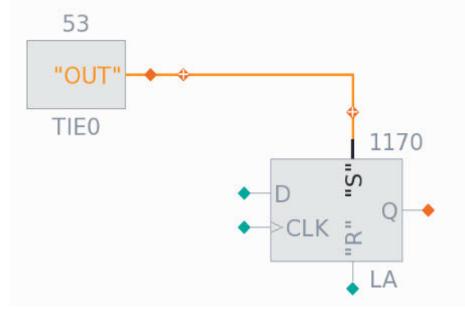

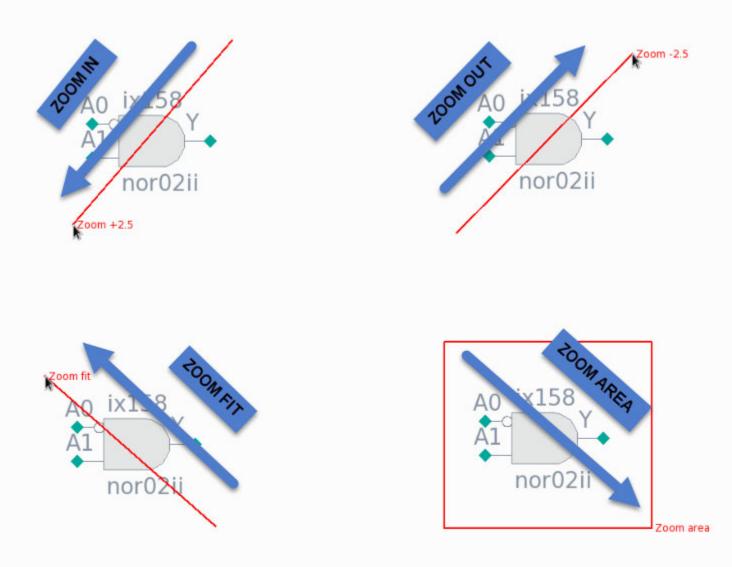

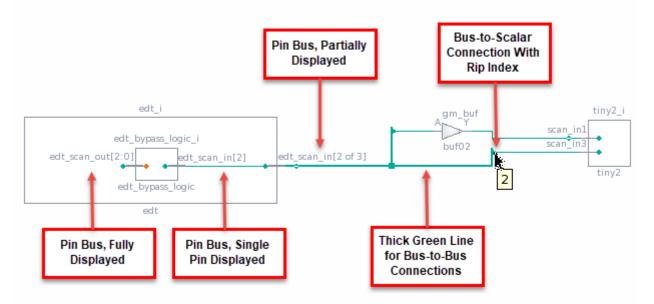

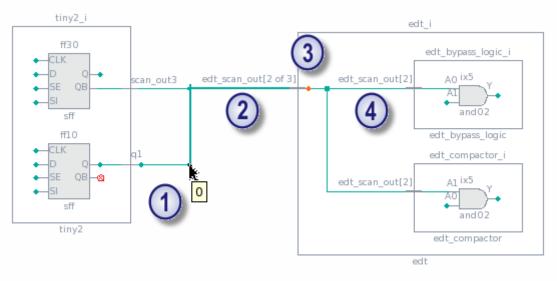

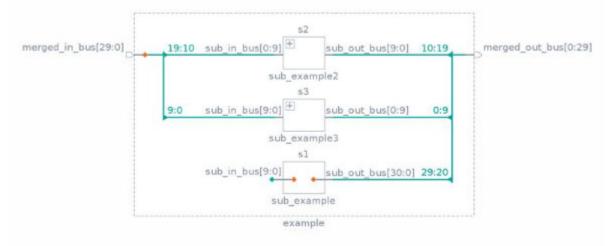

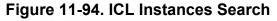

| Columns and Filters Editor.<br>Table Filters<br>Data Sorting<br>Row Highlighting<br>Schematics                                                                                                                         | 730<br>733<br>733<br>735                             |

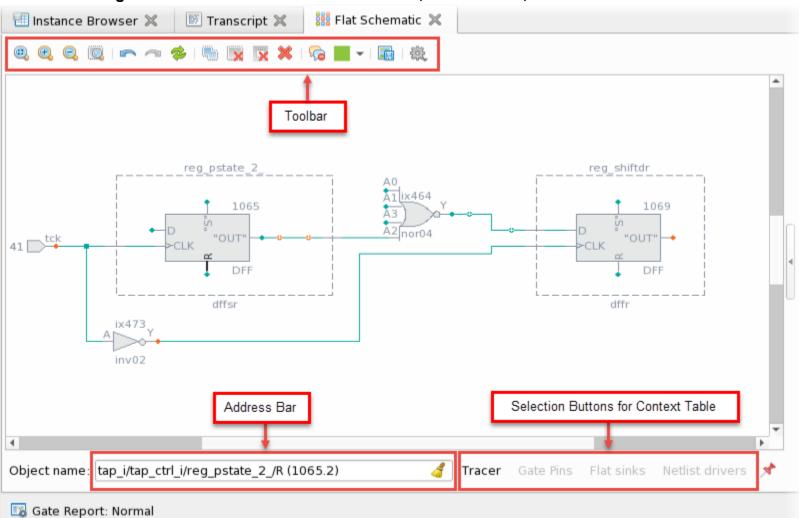

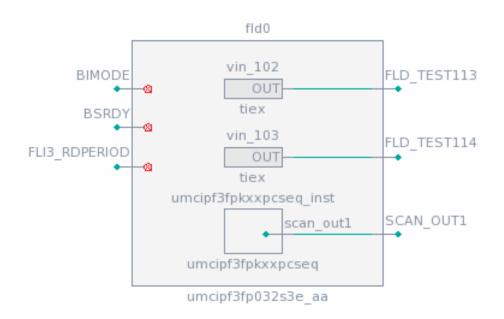

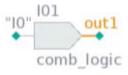

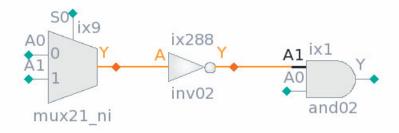

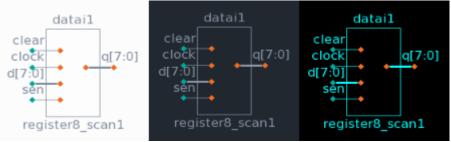

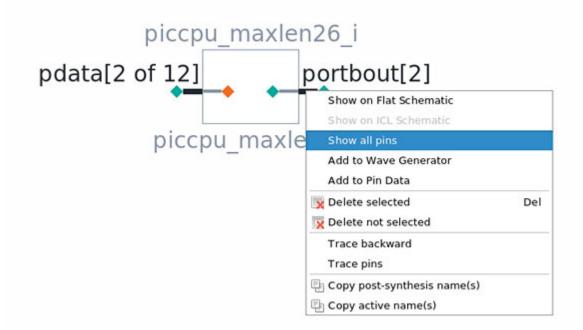

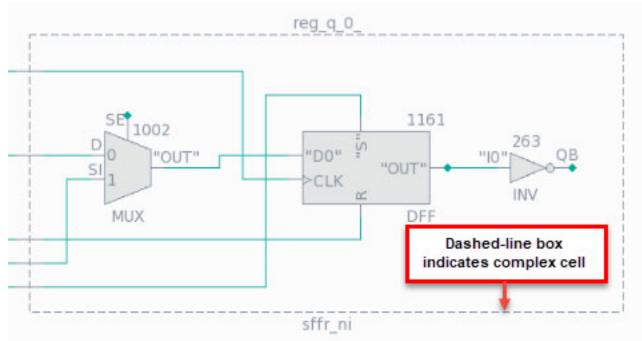

| Columns and Filters Editor.         Table Filters         Data Sorting         Now Highlighting.         Schematics         Toolbar         Schematic Symbols         Context Tables                                   | 730<br>733<br>733<br>735<br>736                      |

| Columns and Filters Editor.<br>Table Filters<br>Data Sorting<br>Row Highlighting<br>Schematics<br>Toolbar<br>Schematic Symbols                                                                                         | 730<br>733<br>733<br>735<br>736<br>739               |

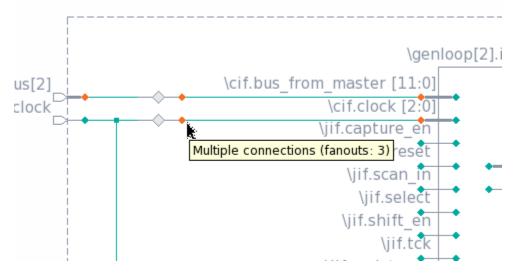

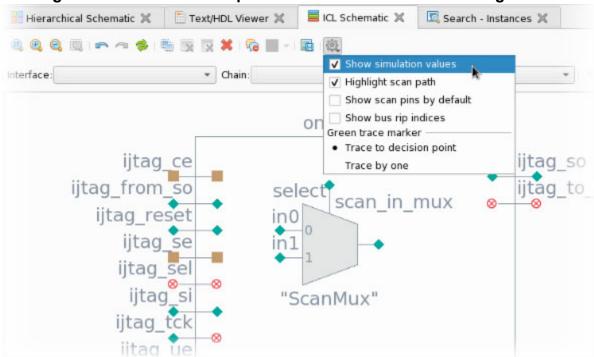

| Columns and Filters Editor.<br>Table Filters .<br>Data Sorting .<br>Row Highlighting .<br>Schematics .<br>Toolbar<br>Schematic Symbols .<br>Context Tables .<br>Signal Net Tracing Strategies.<br>Displayed Property . | 730<br>733<br>733<br>735<br>736<br>739<br>751        |

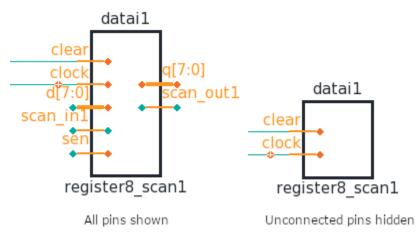

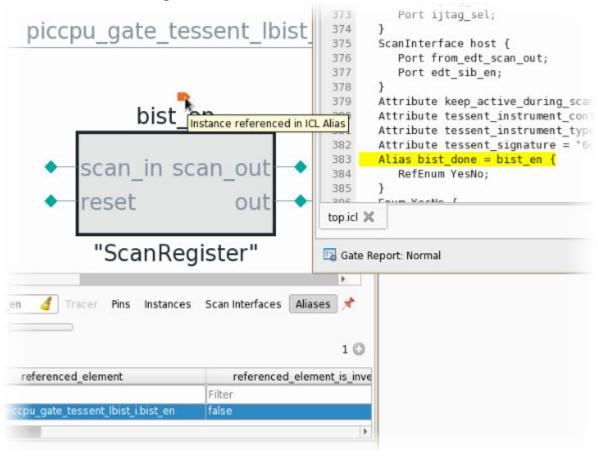

| Columns and Filters Editor.Table FiltersData SortingRow HighlightingSchematicsToolbarSchematic SymbolsContext TablesSignal Net Tracing Strategies                                                                      | 730<br>733<br>733<br>735<br>736<br>739<br>751<br>761 |

| Columns and Filters Editor.<br>Table Filters .<br>Data Sorting .<br>Row Highlighting .<br>Schematics .<br>Toolbar<br>Schematic Symbols .<br>Context Tables .<br>Signal Net Tracing Strategies.<br>Displayed Property . | 730<br>733<br>735<br>736<br>739<br>751<br>761<br>764 |

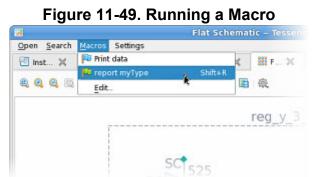

| Macros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 769                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

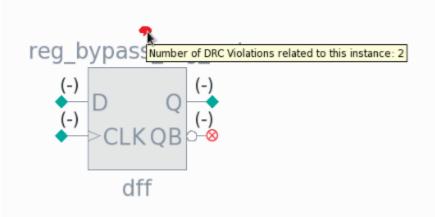

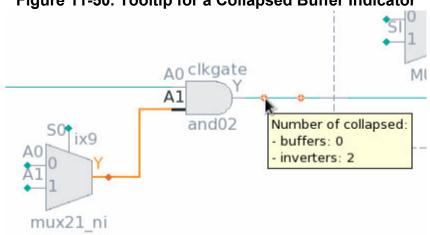

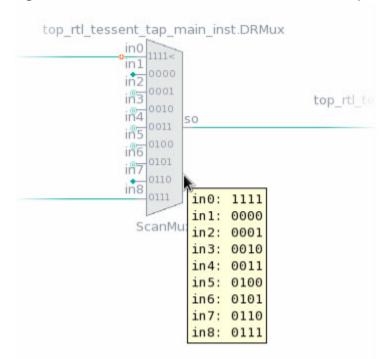

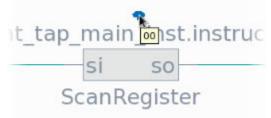

| Tooltips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 770                                                                                                                                                                                 |

| Gate Report Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 771                                                                                                                                                                                 |

| Saving and Restoring the Session State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 772                                                                                                                                                                                 |

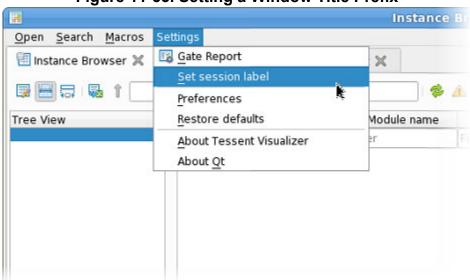

| Window Title Prefixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 772                                                                                                                                                                                 |

| Tessent Visualizer GUI Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 774                                                                                                                                                                                 |

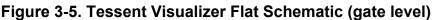

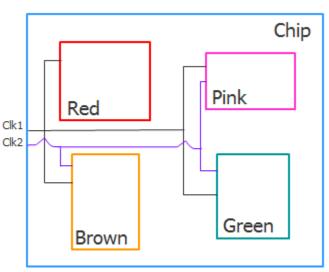

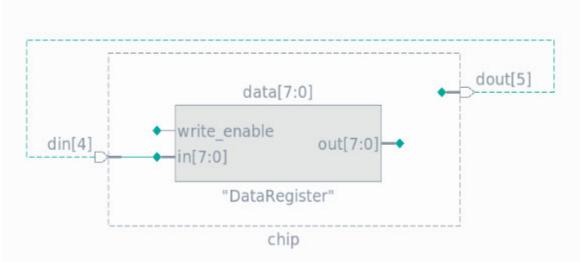

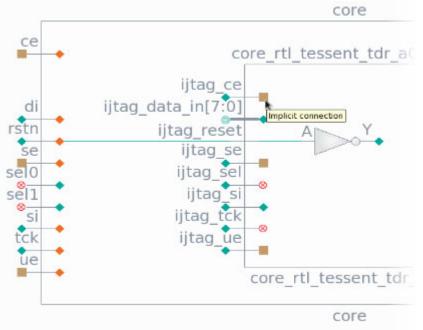

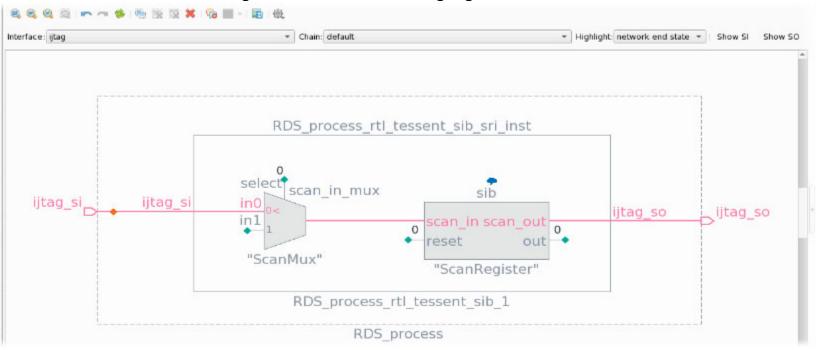

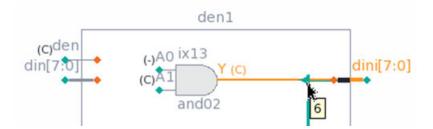

| Hierarchical Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 774                                                                                                                                                                                 |

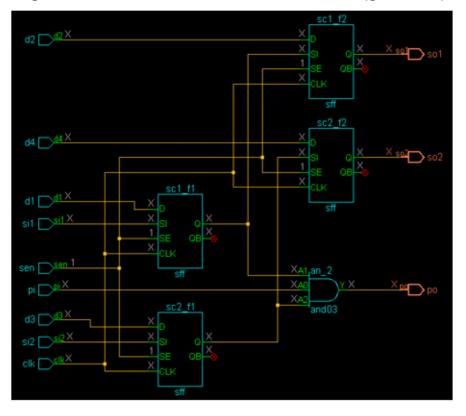

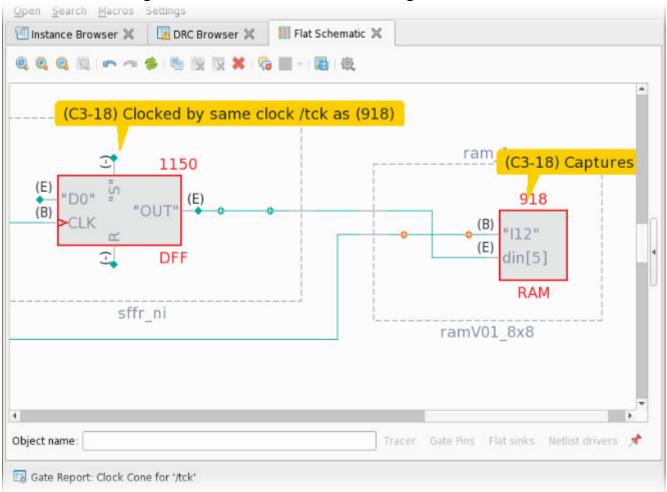

| Flat Schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 781                                                                                                                                                                                 |

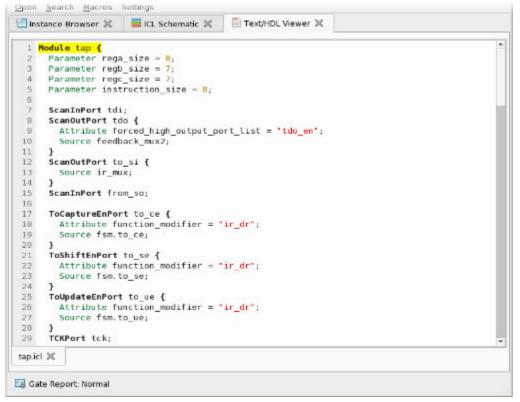

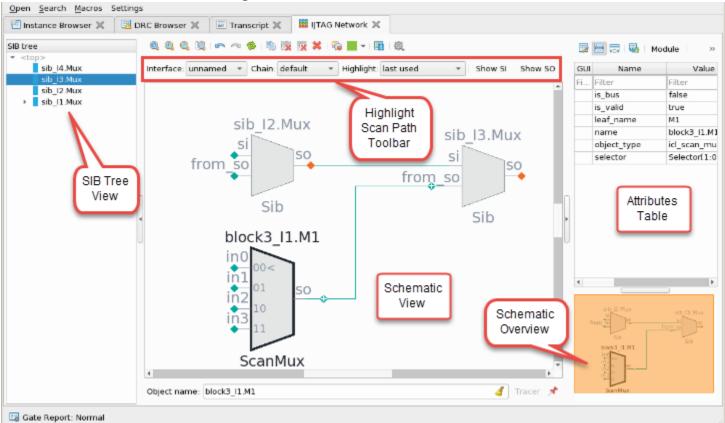

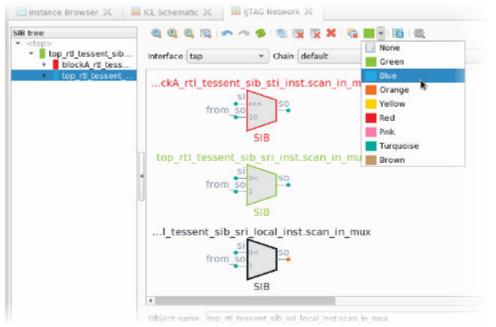

| ICL Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 783                                                                                                                                                                                 |

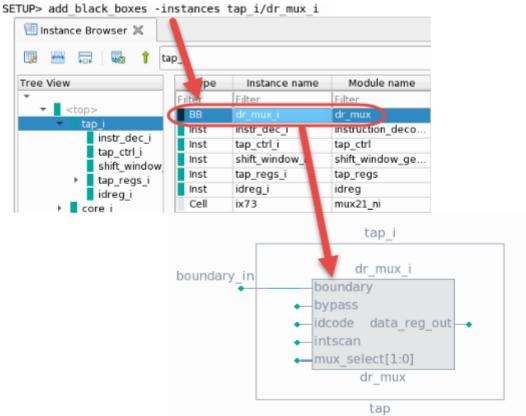

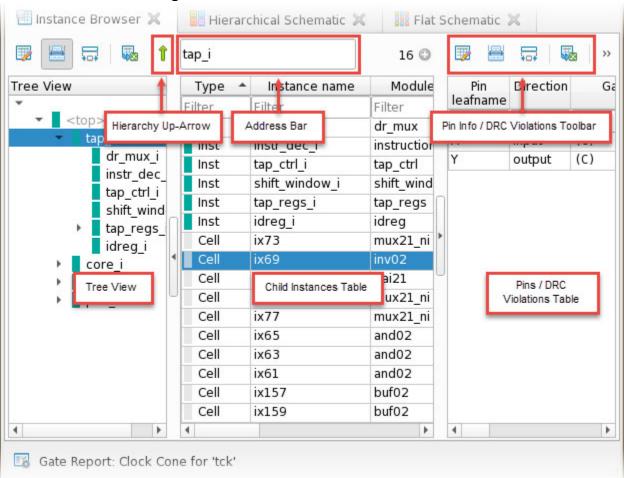

| Instance Browser.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 789                                                                                                                                                                                 |

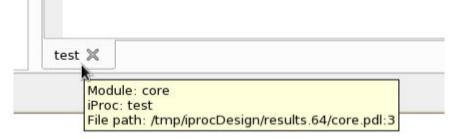

| ICL Instance Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 792                                                                                                                                                                                 |

| Wave Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 793                                                                                                                                                                                 |

| Cell Library Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 795                                                                                                                                                                                 |

| DRC Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 796                                                                                                                                                                                 |

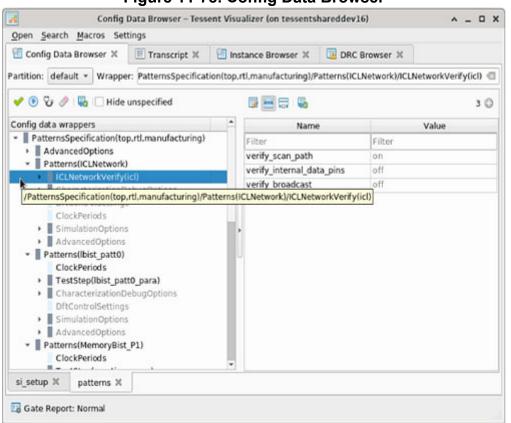

| Config Data Browser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 799                                                                                                                                                                                 |

| Pin Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 802                                                                                                                                                                                 |

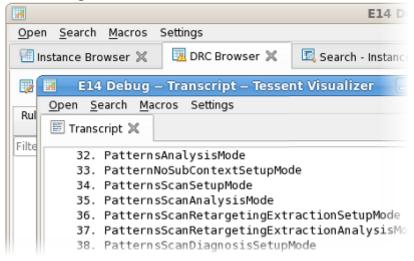

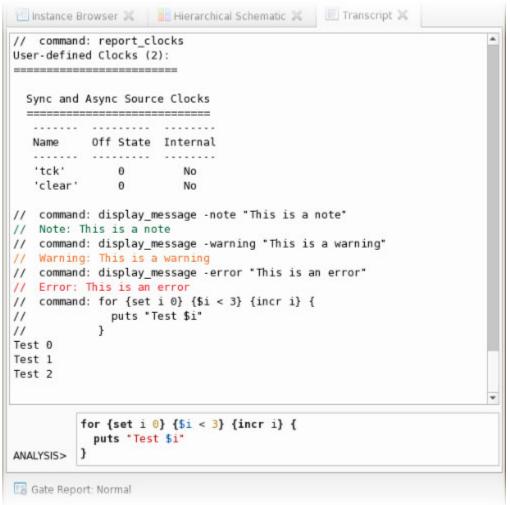

| Transcript                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 803                                                                                                                                                                                 |

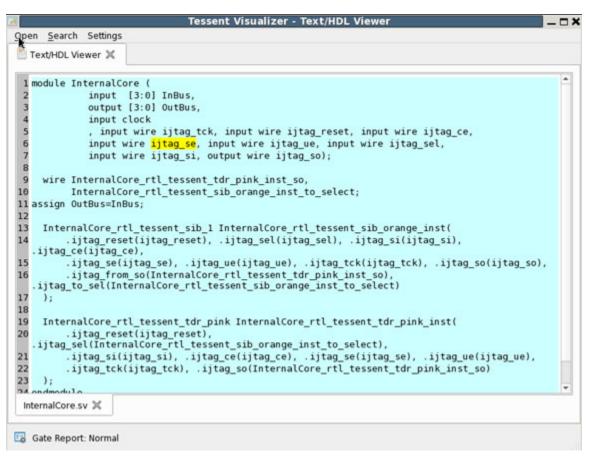

| Text/HDL Viewer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 804                                                                                                                                                                                 |