# Conformal<sup>®</sup> ECO User Guide

Product Version 24.1 May 2024 © 2012-2024 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

Cadence is committed to using respectful language in our code and communications. We are also active in the removal and/or replacement of inappropriate language from existing content. This product documentation may however contain material that is no longer considered appropriate but still reflects long-standing industry terminology. Such content will be addressed at a time when the related software can be updated without end-user impact.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

# **Contents**

| Preface ECO                                  |

|----------------------------------------------|

| About This Manual                            |

| <u>Audience</u>                              |

| How This Manual Is Organized                 |

| Related Documents                            |

| Conventions                                  |

| Syntax Structure                             |

| GUI Convention                               |

| 1                                            |

| <u>                                     </u> |

| Introduction to the Conformal ECO Solution   |

| <u>Overview</u>                              |

| <u>-eatures</u> 10                           |

| Conformal ECO Flows                          |

| Supported Platforms                          |

| _anguage Support                             |

| Starting the ECO Designer Software13         |

| 1                                            |

| <u>I</u><br>Dala Dang'nan sala               |

| Data Requirements15                          |

| nput Requirements15                          |

| OPTIMIZE PATCH File Requirements16           |

|                                              |

| <u>2</u>                                     |

| Conformal Flattened ECO Flow2                |

|                                              |

| Flow Steps                                   |

| Sample Dofiles                               |

| 3<br>Conformal ECO for Hierarchical Files2                   | 27 |

|--------------------------------------------------------------|----|

|                                                              |    |

| Pro Mack ECO Flows                                           |    |

| Pre-Mask ECO Flows                                           |    |

| Pre-Mask ECO                                                 |    |

| Pre-Mask Physical ECO                                        |    |

| Steps for Implementing a Physically-Aware, Pre-Mask ECO      |    |

| Sample Dofiles                                               | 6  |

| <u>5</u>                                                     |    |

|                                                              |    |

| Post-Mask ECO Flows                                          |    |

| Overview         3           Input Requirements         3    |    |

| Post-Mask ECO with Standard Cells                            |    |

| Steps for Implementing a Post-Mask ECO with Standard Cells 4 | .0 |

| Post-Mask ECO with Gate Array Cells                          |    |

| Steps for Implementing a Post-Mask ECO with Gate Array Cells |    |

| Sample Dollies                                               | -4 |

| <u>6</u>                                                     |    |

| Conformal ECO Power-Aware Flow 4                             | .5 |

|                                                              |    |

| <u>7</u>                                                     |    |

| ECO Patch Files                                              | .9 |

| Creating ECO Patch Files                                     |    |

| Adding Input and Output Ports5                               |    |

| Automatically Adding and Deleting ECO Pins 5                 |    |

| Applying the ECO Patch and Writing Out the ECO Netlist       |    |

| Mapping and Optimizing the ECO Patch File 5                  | J  |

| 8 Checking the ECO Netlist55                                           |

|------------------------------------------------------------------------|

| <u>9</u>                                                               |

| ECO Cut Point Flow57                                                   |

|                                                                        |

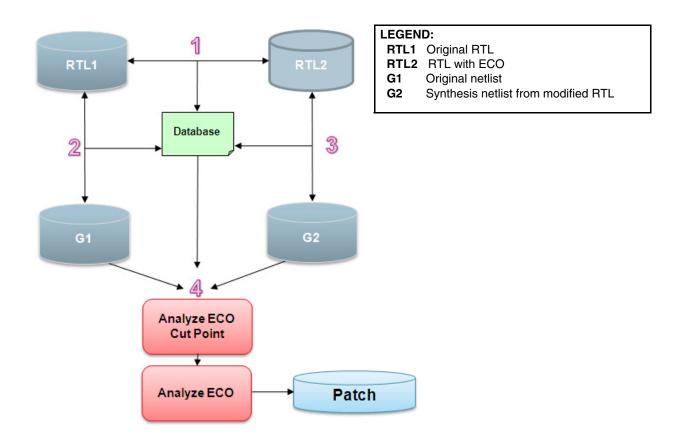

| ECO Cut Point Flow (Diagram)                                           |

| ECO Cut Point Flow (Steps)                                             |

| Finding Cut Point Candidates                                           |

| Comparing RTL1 and RTL2                                                |

| Comparing RTL2 and G2                                                  |

| Inserting Cut Points                                                   |

| inserting out Foints                                                   |

| <u>10</u><br>Generic Script Format67                                   |

| <u>11</u>                                                              |

| Debugging and Troubleshooting in Conformal ECO 69                      |

| <u>List of Debugging Topics</u> 69                                     |

| ANALYZE ECO Fails                                                      |

| APPLY PATCH or OPTIMIZE PATCH Fails Due to Referenced Cells/Modules 72 |

| Cannot Find Corresponding Nets                                         |

| Duplicate Fanout Branches74                                            |

| ECO_SYNTHESIS Needs Information                                        |

| Extra or Invalid Ports are Reported76                                  |

| Invalid Data Value77                                                   |

| Fanout Branch Missing78                                                |

| Tool Reports No NEQs to ECO                                            |

| Lines are Commented Out After -eco aware80                             |

| Missing Modules                                                        |

| Missing Tie Cells                                                      |

| Modules in the Patch File83                                            |

| NEQ point(s) Found in a Submodule 84                                   |

| No Mapping for Gate Array                                 | 85 |

|-----------------------------------------------------------|----|

| Spare Cells Used That are Not Part of the Spare Cell List |    |

| Spare Cell DFF is Not Available                           |    |

| Super Threading is Disabled                               | 88 |

| NEQs Due to Unexpected Blackboxes                         | 89 |

| Unexpected NEQ Between G2 and G3                          | 90 |

| Unexpected Patch Size                                     | 91 |

| NFQs Due to Unmapped Points                               | 92 |

# **Preface ECO**

### **About This Manual**

The Cadence® Encounter® Conformal® ECO Designer enables designers to implement RTL engineering change orders (ECOs) for pre- and post-mask layout. It features automatic ECO analysis, logic optimization, and design netlist modification, with equivalence checking.

### **Audience**

This manual is written for experienced designers of digital integrated circuits who must be familiar with RTL, synthesis, and design verification; as well as having a solid understanding of UNIX and Tcl/Tk programming.

# **How This Manual Is Organized**

The chapters in this manual are organized to follow the flow of tasks through the design process. Because of variations in design implementations and methodologies, the order of the chapters will not correspond to any specific design flow.

Each chapter focuses on the concepts and tasks related to the particular design phase or topic being discussed.

### **Related Documents**

For more information about the Conformal family of products, see the following documents. You can access these and other Cadence documents with the Cadence Help online documentation system. For a complete list of documents provided with this release, see the CDSDoc library.

■ Conformal Equivalence Checking Reference

Describes the commands and modeling messages for the Encounter<sup>®</sup> Conformal Equivalence Checking solutions, including Conformal ECO Designer.

Preface ECO

### ■ Conformal Equivalence Checking User Guide

Describes how to install, configure, and use Conformal to verify RTL, gate, or transistor-level designs.

# **Additional Learning Resources**

Cadence offers the following training course on Conformal ECO:

■ Conformal ECO

## **Conventions**

# **Syntax Structure**

| Convention | Definition                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------|

| Bold Case  | Indicates the command name.                                                                                        |

| UPPERCASE  | Indicates the required minimum character entry.                                                                    |

| < >        | Indicates required arguments. Do not type the angle brackets.                                                      |

| [ ]        | Indicates optional arguments. Do not type the square brackets.                                                     |

|            | Indicates a choice among alternatives. Do not type the vertical bar.                                               |

| \          | The backslash character (\) at the end of a line shows that the command you are typing continues on the next line. |

| •••        | Indicates multiple entries of an argument.                                                                         |

| *          | Indicates that Conformal lets the wildcard (*) represent any zero or more characters.                              |

Preface ECO

# **GUI Convention**

| Convention     | Definition                                                                                                 |

|----------------|------------------------------------------------------------------------------------------------------------|

| Menu – Command | Indicates command sequences under a menu. For example: Choose File – Read Design.                          |

| Left-click     | Click the left mouse button on the specified item.                                                         |

| Right-click    | Click the right mouse button on the specified item.                                                        |

| Click          | Click the left mouse button unless otherwise specified.                                                    |

| Double-Click   | Click twice on the left mouse button.                                                                      |

| Drag           | Press and hold the left mouse button, and then move the pointer to the destination and release the button. |

Preface ECO

1

# Introduction to the Conformal ECO Solution

This manual documents the commands, features, and flows that are specific to the Encounter<sup>®</sup> Conformal<sup>®</sup> ECO solution:

- Overview on page 9

- Features on page 10

- Supported Platforms on page 12

- Language Support on page 12

- Starting the ECO Designer Software on page 13

# **Overview**

Note: This feature requires a Conformal ECO XL or GXL license.

Conformal ECO Designer offers functional ECO analysis, optimization, and generation capability. It combines proven equivalence checking and functional checks, and uses formal techniques to analyze and implement the functional ECO.

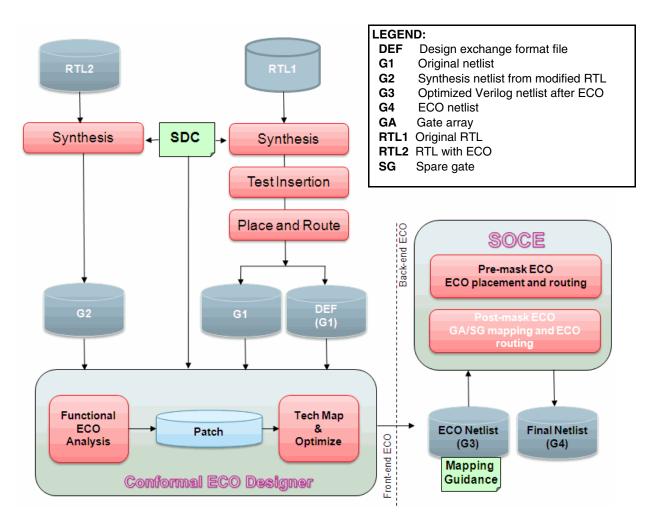

This chapter describes the Conformal ECO methodology and how to use the ECO Designer software to automatically implement functional ECOs. You can provide the resulting netlist to SoC Encounter for incremental optimization and place-and-route.

ECOs can also be classified according to optimization stage:

- Pre-mask ECOs are done before the chip-mask is manufactured. For a pre-mask ECO, the software assumes any cell in the library is available for implementing the ECO.

- Post-mask ECOs are done after the chip-mask is manufactured. For a post-mask ECO, the software restricts the implementation to only use spare cells based on their physical location in the design and their timing requirements.

#### Introduction to the Conformal ECO Solution

Note: Conformal ECO does not support retimed designs and/or blocks.

### **Features**

Conformal ECO Designer combines logic equivalence checking (for the most complex SoC and datapath-intensive designs) with functional ECO analysis, design netlist modification, and logic optimization.

Equivalence checking for ECOs

During development, a design undergoes numerous iterations prior to final layout, and each step in this process has the potential to introduce logical bugs. Conformal ECO Designer checks the functional equivalence of different versions of a design at these various stages and enables designers to identify and correct errors as soon as they are introduced. Equivalence checking also plays an important role in the ECO implementation process. It helps the ECO analysis tool identify which modules and logic cones in the design require change to implement the ECO. Equivalence checking is also used at the end of the process to ensure the ECO implementation was successful both for front-end and back-end signoff.

Functional ECO analysis

Conformal ECO Designer has a built-in ECO analysis engine that can identify the differences between the original design netlist and the new design netlist. Users can perform ECO analysis on the entire design or on specific modules within the design hierarchy, which is typically more efficient. Once the ECO analysis step is completed and the logic change optimized, Conformal ECO Designer performs the necessary netlist modifications to achieve the new function in the original design netlist. The output is the ECO netlist. Alternately, Conformal ECO Designer can write out an ECO script that can be used to make direct changes to the place-and-route database.

Physically-aware premask ECOs

Conformal ECO Designer (GXL) has the ability to read the DEF layout database corresponding to the original place-and-route design netlist, capTbl, LEF, Liberty synthesis libraries, and SDC timing constraints to optimize, estimate routing, and legally place the generated ECO logic into the design floorplan. The output of Conformal ECO Designer is the ECO netlist and the corresponding placement DEF file. This flow can reduce timing closure iterations during place and route especially in late state pre-mask ECO situations.

Spare gate mapping for post-mask ECOs

Conformal ECO Designer (GXL) has the ability to read the DEF layout database corresponding to the original design netlist, capTbl, LEF, Liberty synthesis libraries, and

#### Introduction to the Conformal ECO Solution

SDC to optimally map ECO logic to standard cell and gate array spare gates. The mapping engine is timing- and spare-cell-location aware. This capability enables the designer to get an early estimate of the ECO feasibility and effectively drive the backend implementation flow. Conformal ECO Designer (GXL) can also recycle freed-up cells in the ECO mapping process. The output is the ECO netlist and a spare gate mapping file. This mapping file instructs the place-and-route tool how to map the newly added ECO logic to specific spare logic resources in the layout.

#### Integrated environment

An intuitive graphical user interface (GUI) is provided for setup and debugging, allowing the user to work more productively and quickly pinpoint the cause of equivalence mismatches.

#### Included are:

- Graphical debugging through an integrated schematic viewer that shows logic values for each error vector

- □ Full cross-highlighting between RTL model and circuit

- Automatic error candidate identification with assigned and weighted percentages

- □ Logic-cone pruning to focus debugging on relevant information

#### Smart setup and diagnosis

Conformal ECO Designer includes a set of intelligent ANALYZE commands to ease setup and diagnosis. For example, ANALYZE SETUP investigates the current environment and automatically remedies common setup issues sometimes experienced by new users. In tandem, ANALYZE NONEQUIVALENT can be invoked if non-equivalences are encountered. The command then presents a one-line answer as to what is wrong.

## **Conformal ECO Flows**

The following lists the flows described in this document:

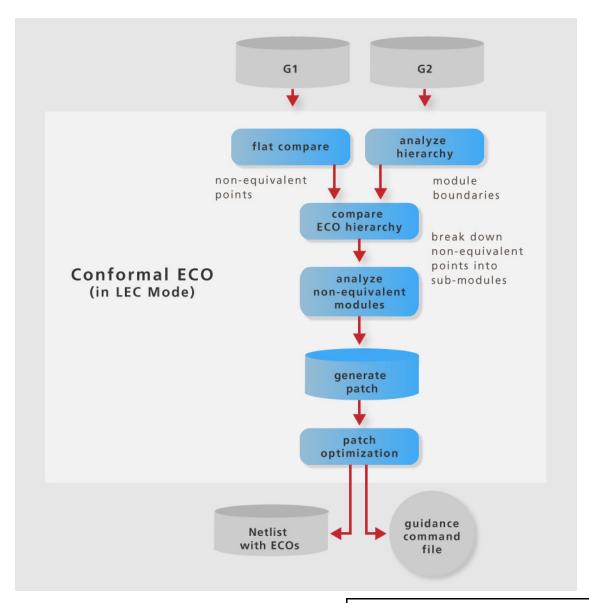

#### ■ Conformal Flattened ECO Flow on page 23

This is the recommended Conformal ECO flow. In this flow, you run a flat compare on a hierarchical design. This flow can help when your hierarchical dofile is causing false non-equivalent points (due to things like clock gate cloning/decloning, inverter pushes, or boundary optimization).

Conformal ECO for Hierarchical Files on page 27

#### Introduction to the Conformal ECO Solution

With this flow, Conformal ECO Designer will write out as many modules as possible for hierarchical compare. Conformal ECO Designer will use the module boundaries to create as small a patch as possible.

Pre-Mask ECO Flows on page 29

Pre-mask ECOs are performed during place and route and before the design is taped out.

- □ Pre-Mask ECO on page 30

- □ Pre-Mask Physical ECO on page 33

- Post-Mask ECO Flows on page 37

Post-mask ECOs are performed after the design has been sent to manufacturing. Once fabrication has begun, the number of gates on the die is fixed and any changes will need to be accomplished with these resources.

- Post-Mask ECO with Standard Cells on page 39

- Post-Mask ECO with Gate Array Cells on page 42

- Conformal ECO Power-Aware Flow on page 45

In the Conformal ECO power-aware flow, functional ECO is performed on a design within the same domain. Conformal ECO passes power intent files to RTL compiler for optimization.

# **Supported Platforms**

- Linux (32-bit, 64-bit)

- Sun Solaris (64-bit)

- IBM AIX (64-bit)

# Language Support

- Verilog® (1995, 2001, 2005)

- SystemVerilog

- VHDL (87, 93)

- SPICE (traditional, LVS)

# Introduction to the Conformal ECO Solution

- **EDIF**

- Liberty

- Mixed languages

# Starting the ECO Designer Software

You can start the Conformal ECO Designer software with an XL license or GXL license. Conformal ECO XL is primarily targeted for pre-mask ECOs and does not require physical design awareness. Conformal ECO GXL is targeted for pre and post-mask ECOs. For postmask ECOs, spare gate physical location, quantity, type, and timing requirements must be considered as input for the tool.

To start Conformal ECO XL, run the following command:

> lec -eco

To start Conformal ECO GXL, run the following command:

> lec -ecogxl

The lec command has the following additional options. This list is also available using the lec -help command before you start your session.

| -32                            | Runs the Encounter <sup>®</sup> Conformal <sup>®</sup> software in 32-bit mode. <i>This is the default.</i>                                                                                                                                         |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -64                            | Runs the Encounter <sup>®</sup> Conformal <sup>®</sup> software in 64-bit mode.                                                                                                                                                                     |

| -Dofile <filename></filename>  | Runs the script <filename> after starting LEC.</filename>                                                                                                                                                                                           |

| -LOGfile <filename></filename> | Sets up a log filed called <filename>.</filename>                                                                                                                                                                                                   |

| -Gui   -NOGui                  | Starts the session in GUI or non-GUI mode.                                                                                                                                                                                                          |

| -TclMode                       | After the session starts, the tool enters Tcl mode.                                                                                                                                                                                                 |

| -NOColor   -Color              | In the non-GUI mode, you can start the Conformal software with the -color option to specify that you want all of the messages to be color-coded. (For example, error messages appear in red text.) By default, color-coding is off in non-GUI mode. |

| -DARK_Color   -LIGHT_Color     | If you are using the -color mode, adjusts the brightness of the colors used.                                                                                                                                                                        |

#### Introduction to the Conformal ECO Solution

-DEFault [init\_filename] | -NODEFault]

Specifies whether to process the initial command file (init\_filename or .conformal\_lec) by default

during startup.

-Banner | -NOBanner | Specifies whether to display the LEC banner during

startup.

-RESETTC Reset GUI default settings.

-NOLIcwait If all licenses are checked out, exit immediately.

-Info Display the product information and exit.

-Version Displays the product version. Once you have started

your session, you can also use the VERSION

command to display the Conformal software version number. This is useful when starting a transcript log file to ensure that the file contains a reference to the

Conformal version that created the results.

-restore\_session <session\_file\_name>

Restores a session that was saved using the checkpoint/restart facility (SAVE SESSION

-checkpoint command).

1

# **Data Requirements**

This chapter describes everything that you should prepare before starting the flows described in this book (if an item is specific to a particular flow, it will be noted as such).

- Input Requirements on page 15

- OPTIMIZE PATCH File Requirements on page 16

# **Input Requirements**

The following tables summarize the various input data mentioned in the <u>Pre-Mask ECO Flows</u> and the <u>Post-Mask ECO Flows</u>.

| Required Data   | Description                | Requirement Level | Applicable Flow |

|-----------------|----------------------------|-------------------|-----------------|

| G1              | Original netlist (after    | Mandatory         | Pre-Mask        |

|                 | layout)                    | -                 | Post-Mask       |

| G2              | Netlist after synthesis    | Mandatory         | Pre-Mask        |

|                 |                            |                   | Post-Mask       |

| Liberty library | Library for RC             | Mandatory         | Pre-Mask        |

|                 | •                          | -                 | Post-Mask       |

| Verilog library | Verilog simulation library | Optional          | Pre-Mask        |

|                 |                            |                   | Post-Mask       |

| RTL1            | Original RTL               | Recommended       | Pre-Mask        |

|                 |                            |                   | Post-Mask       |

| RTL2            | RTL with ECO               | Recommended       | Pre-Mask        |

|                 |                            |                   | Post-Mask       |

| Design          | DFT constraints and/or     | Recommended       | Pre-Mask        |

| constraints     | renaming rules             |                   | Post-Mask       |

**Data Requirements**

| -                                                                                          |                                                           |                   |                                |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|--------------------------------|

| Required Data                                                                              | Description                                               | Requirement Level | Applicable Flow                |

| ECO Information                                                                            | Pre-Mask                                                  |                   |                                |

| ■ Name of mod                                                                              | ules that require an ECO (F                               | Recommended)      | Post-Mask                      |

| Names of por<br>(Recommend                                                                 | ed due to an ECO                                          |                   |                                |

| ■ Names of ports that are renamed by an ECO (Optional)                                     |                                                           |                   |                                |

| <ul> <li>Names of registers that were added or renamed by an ECO<br/>(Optional)</li> </ul> |                                                           |                   |                                |

| Spare cell name                                                                            | Names of the spare cells that you can use for ECO         | Mandatory         | Pre-Mask Physical<br>Post-Mask |

| LEF                                                                                        | Contains library information for a class of designs       | Mandatory         | Pre-Mask Physical<br>Post-Mask |

| DEF                                                                                        | Describes the logical and physical layout of design       | Mandatory         | Pre-Mask Physical<br>Post-Mask |

| CapTbl                                                                                     | Contains parasitic resistance and capacitance information | Recommended       | Pre-Mask Physical<br>Post-Mask |

# **OPTIMIZE PATCH File Requirements**

In several ECO flows, you will read in several types of files: Synopsys Design Constraints (SDC), Library Exchange Format files (LEF), Design Exchange Format files (DEF), capacitance tables (capTbl), and timing libraries (lib) for both gate array filler cells and gate array cells. These files are read in using the OPTIMIZE PATCH command. For example:

16

```

optimize patch -workdir WORK_POST -usespare \

-library ../../lib/liberty/FreePDK45_lib_v1.0_typical.lib \

-sdc ../../pr/g1.pr.sdc \

-lef ../../lib/lef/FreePDK45_lib_v1.0.lef \

-def ../../pr/g1.pr.def \

-captable ../../pr/g1.cap.gz \

...

```

This section provides a brief overview of those files.

- <u>Timing Libraries</u> on page 17

- SDC on page 17

**Data Requirements**

- <u>LEF</u> on page 17

- <u>DEF</u> on page 19

- capTbl on page 20

Conformal ECO sends these input files to RTL Compiler

#### **Timing Libraries**

Using the OPTIMIZE PATCH command, you will read in the timing libraries. For the post-mask flow with gate-array cells, the libraries must contain:

- The gate array filler cells; these cells typically do not contain timing arcs or functionality.

- The function for the gate array. Conformal ECO use this to determine how to map the filler cells to the cells for the ECO changes.

**Note:** The tool will run a consistency check between the LEF files and the timing library files to ensure there is a one-to-one mapping between them. The technology functional libcells must be present in both the LEF and the library files. Otherwise, the tool will error out.

#### **SDC**

Synopsys Design Constraint (SDC) is a format that allows designers to utilize the same sets of constraints to drive synthesis, timing analysis, and place-and-route.

#### LEF

A Library Exchange Format (LEF) file contains library information for a class of designs. Library data includes layer, via, placement site type, and macro cell definitions.

You can define all of your library information in a single LEF file; however this creates a large file that can be complex and hard to manage. Instead, you should divide the information into two files:

- Technology LEF Files on page 18

- Cell Library LEF Files on page 19

#### General Rules

Note the following information when creating LEF files:

#### **Data Requirements**

- Lines in the LEF file are limited to 2,048 characters (extra characters are truncated). Distance is specified in microns.

- Distance precision is controlled by the UNITS statement.

- LEF statements end with a semicolon (; ). You *must* leave a space between the last character in the statement and the semicolon.

- You can specify statements in any order; however, data must be defined before it is used.

#### Requirements for the Post-Mask Flow

- You must read in all LEF files (technology LEF, cell library LEF, std cells, and memories)

- The LEF files must contain the definitions for gate array and gate array filler cells

- Gate array cells should not be modeled as CLASS CORE SPACER in the LEF file. Use CLASS CORE instead.

- Gate array filler cells can contain either CLASS CORE or CLASS CORE SPACER. "SPACER" specifies that this cell is used to fill in space between regular core cells.

- The tool will run a consistency check between the LEF files and the timing library files to ensure there is a one-to-one mapping between them. The technology functional libcells must be present in both the LEF and the library files. Otherwise, the tool will error out.

#### Technology LEF Files

A technology LEF file contains all of the LEF technology information for a design, such as placement and routing design rules, and process information for layers. A technology LEF file can include any of the following LEF statements:

```

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[UNITS statement]

[MANUFACTURINGGRID statement]

[USEMINSPACING statement]

[CLEARANCEMEASURE statement ;]

[PROPERTYDEFINITIONS statement]

[LAYER (Nonrouting) statement

LAYER (Routing) statement] ...

[SPACING statement ]

[MAXVIASTACK statement]

[VIA statement] ...

[VIARULE statement] ...

[VIARULE GENERATE statement] ...

[NONDEFAULTRULE statement] ...

[SITE statement] ...

[BEGINEXT statement] ...

[END LIBRARY]

```

**Data Requirements**

#### Cell Library LEF Files

A cell library LEF file contains the macro and standard cell information for a design. A library LEF file can include any of the following statements:

```

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[VIA statement] ...

[SITE statement]

[MACRO statement

[PIN statement] ...

[OBS statement ...] ] ...

[BEGINEXT statement] ...

[END LIBRARY]

```

When reading in LEF files, always read in the technology LEF file first.

#### **DEF**

The Design Exchange Format (DEF) is file format that can describe the logical and physical layout of design. It represents the netlist and circuit layout. DEF is used in conjunction with the Library Exchange Format (LEF) to represent complete physical layout of an integrated circuit while it is being designed.

#### General Rules

Note the following when creating DEF files.

- Lines in the DEF file are limited to 2,048 characters (extra characters are truncated on input).

- Net names and cell names also are limited to 2,048 characters.

- DEF statements end with a semicolon (;). You *must* leave a space before the semicolon.

- Each section can be specified only once. Sections end with END SECTION.

- You must define all objects before you reference them except for the + ORIGINAL argument in the NETS section.

- No regular expressions or wildcard characters are recognized except for (\* pinName in the SPECIALNETS section.

**Data Requirements**

#### Requirements for the Post-Mask Flow

- The information about your design must be described in a single DEF file. Multiple DEF files are not supported in this flow.

- The gate array filler cells must already have been placed in the DEF file.

- The placement attribute for these cells should be FIXED attribute in the DEF file.

#### Order of Statements

Standard DEF files can contain the following statements and sections. You can define the statements and sections in any order; however, data must be defined before it is used.

```

[ VERSION statement ]

[ DIVIDERCHAR statement ]

[ BUSBITCHARS statement ]

DESIGN statement

[ TECHNOLOGY statement ]

UNITS statement ]

[ HISTORY statement ] ...

[ PROPERTYDEFINITIONS section ]

[ DIEAREA statement ]

[ ROWS statement ] ...

[ TRACKS statement ] ...

[ GCELLGRID statement ] ...

[ VIAS statement ]

[ STYLES statement ]

NONDEFAULTRULES statement ]

[ REGIONS statement ]

[ COMPONENTS section ]

[ PINS section ]

[ PINPROPERTIES section ]

[ BLOCKAGES section ]

[ SLOTS section ]

[ FILLS section ]

[ SPECIALNETS section ]

NETS section ]

SCANCHAINS section ]

[ GROUPS section ]

[ BEGINEXT section ] ...

END DESIGN statement

```

#### capTbl

Although the DEF file can provide data for parasitic extraction, the parasitic resistance and capacitance information defined in the capacitance table is very detailed and provides a much better approximation of the actual parasitics.

The sections of the capacitance table are used by Encounter RTL Compiler:

■ ShrinkFactor

**Data Requirements**

- PROCESS\_VARIATION

- BASIC\_CAP\_TABLE

**Note:** You should use the same process corner capTbl file as used for the timing libraries that are read in with the OPTIMIZE PATCH command.

Data Requirements

2

# **Conformal Flattened ECO Flow**

This section describes the Flattened ECO Flow (FEF). This flow is the recommended Conformal ECO flow.

In this flow, you run a flat compare on a hierarchical design. This flow can help when your hierarchical dofile is causing false non-equivalent points (due to things like clock gate cloning/decloning, inverter pushes, or boundary optimization).

This flow is not ideal for flat designs or when you have clean hierarchical dofiles (for example, two dofiles with ECO modules are compared and their NEQs match those reported by ANALYZE HIER\_COMPARE).

This flow has the following benefits:

- Focuses ECO analysis on the non-equivalent key points identified from a flat compare

- Supports hierarchical clock gating that is not a part of an ECO. For example, if you have two hierarchical gates that do not match, you can perform a flat compare, but create a patch to the hierarchical netlist.

- Works with the current hierarchical flow. You can also run a combination of the hierarchical ECO flow and the FEF flow (running FEF on select modules).

- On-demand insertion of ECO pin/ports through an ECO pin dofile.

- Easier set up. All ECO patches can be created with one command. Running a hierarchical dofile is not required.

# **Flow Diagram**

#### **LEGEND:**

G1 Original netlist

G2 Synthesis netlist from modified RTL

## Conformal Flattened ECO Flow

# Flow Steps

Once you enter LEC mode, a typical scenario for a flattened ECO flow involves the following steps:

1. Use the SET ECO OPTION -flat command (in Setup mode) to specify that your intention is to run the FEF flow. Specifying this command executes the following commands:

```

SET FLATTEN MODEL -ECO

SET FLATTEN MODEL -ENABLE_ANALYZE_HIER_COMPARE

```

It also automatically adds the following options to the ANALYZE HIER\_COMPARE command (when -ECO\_AWARE is specified):

```

-CONstraints

-NOEXact_pin_match

-FUNCTION_Pin_mapping

-INPUT_OUTPUT_Pin_equivalence

-THRESHOLD 0

```

**Note:** When running a flattened ECO flow, set the -threshold of ANALYZE HIER COMPARE to 0, so that the tool can determine all of the module boundaries.

- 2. Add any additional options to the ANALYZE HIER\_COMPARE command,

- **3.** Use the ADD COMPARE POINTS -all and COMPARE commands to start the comparison between the flattened designs. This will determine the non-equivalent points.

- **4.** Use the COMPARE ECO HIERARCHY command to break down the non-equivalent points (determined in step 2) into their sub-modules, based on the module boundaries (determined by step 1).

- $\textbf{5. Use the} \ \mathtt{ANALYZE} \ \mathtt{ECO-hierarchical} \ \textbf{command to create all the necessary patches}.$

- During this step, you can also create a dofile that creates only ECO pins that are part of the non-equivalent cones (through the <code>-ecopin\_dofile</code> option).

- **6.** Apply and optimize the patch using the APPLY PATCH and OPTIMIZE PATCH commands, respectively.

# **Sample Dofiles**

For a sample dofile that illustrates this flow, refer to the "Sample Dofiles" section on the web interface.

25

Conformal Flattened ECO Flow

To launch the web interface, use the set web on command. This command outputs a URL, which you can paste into any of the following web browsers: Internet Explorer 9, Firefox 4, and Chrome 10. The web interface contains the documentation and FAQs for 12.1 features.

3

# **Conformal ECO for Hierarchical Files**

With this flow, Conformal ECO Designer writes out as many modules as possible for hierarchical compare. With this approach, Conformal ECO Designer will use the module boundaries to create as small a patch as possible.

The LEC "write hier\_compare dofile -balanced\_extractions" command analyzes the modules and their instantiations in LEC mode to generate the hierarchical dofile script that verifies the two hierarchical designs (starting from the lower-level modules, progressing to the top root module). This command is recommended when one of the netlists has gone through back-end synthesis, such as clock-tree-synthesis (CTS), resulting in an inversion push across submodule boundaries, extra ports, or ports with mismatched names.

For a full sample dofile that illustrates this flow, refer to the "Sample Dofiles" section on the web interface.

To launch the web interface, use the set web on command. This command outputs a URL, which you can paste into any of the following web browsers: Internet Explorer 9, Firefox 4, and Chrome 10. The web interface contains the documentation and FAQs for 12.1 features.

Conformal ECO for Hierarchical Files

4

# **Pre-Mask ECO Flows**

This section describes how to perform pre-mask ECO optimization using Conformal ECO.

- Pre-Mask ECO on page 30

- □ Steps for Implementing a Pre-Mask ECO on page 31

- Pre-Mask Physical ECO on page 33

- Steps for Implementing a Physically-Aware, Pre-Mask ECO on page 35

- Sample Dofiles on page 36

In the flows described in this chapter, you will read in several types of data and files. These requirements are described in <u>Chapter 1</u>, "<u>Data Requirements</u>".

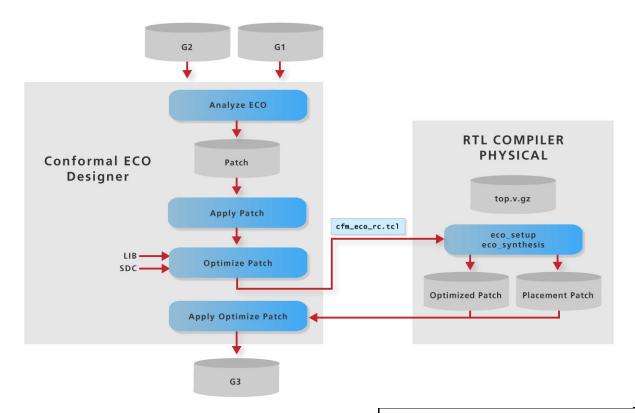

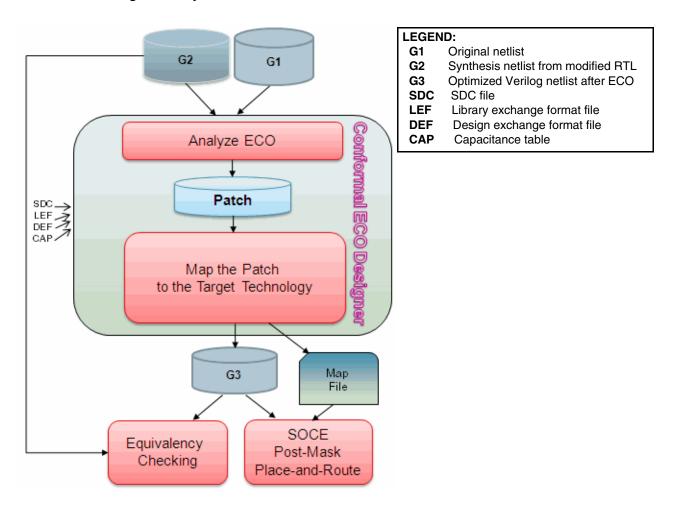

# **Pre-Mask ECO**

Pre-mask ECOs are performed during place and route and before the design is taped out.

#### LEGEND:

G1 Original netlist

G2 Synthesis netlist from modified RTL G3 Optimized Verilog netlist after ECO

LIB Timing library SDC

SDC file

cfm\_eco\_rc.tcl Tcl script to map and

Pre-Mask ECO Flows

#### Steps for Implementing a Pre-Mask ECO

A typical scenario for a pre-mask ECO flow involves the following steps:

The following steps outline a typical situation:

1. Compare the old RTL to the old netlist.

This comparison should be equivalent. You might need to disable the scan by adding scan constraints.

2. Synthesize the new RTL.

If possible, use the same synthesis tool, version, and script that was used to create the old netlist. Minimize any changes. Synthesizing the new RTL is required to increase the probability of the ECO meeting timing.

**3.** Compare the new RTL to the new netlist.

This comparison should be equivalent.

4. Compare the old RTL to the new RTL.

This comparison should be nonequivalent.

- **a.** Ensure to set the X conversion to 'Don't Care' for the new RTL and 'E' for the old RTL. This is the default setting if you read the new RTL as the Golden design and the old RTL as the Revised design.

- **b.** Run both flat and hierarchical comparison; do not run a dynamic, hierarchical comparison. Note the nonequivalent modules. You will specify these as ECO modules in step 5 using the ADD MODULE ATTRIBUTE -eco\_module command.

- **c.** Run a UNIX diff on the RTL files to see exactly what was changed. The comparison results and the diff results should be consistent.

- **5.** Compare the old netlist to the new netlist.

- **a.** Run hierarchical compare on the old netlist and the new netlist; compare as many modules as possible. Again, do not use dynamic hierarchical compare. You will most likely need to use the same scan constraints used in step 1.

- **b.** Compare the results from 5.a. to the results from step 4.b. The nonequivalent modules should be consistent with the comparison results and diff results should be consistent with that of step 4.

- **6.** Create ECO patch files using the old netlist and the new netlist.

Pre-Mask ECO Flows

After verifying that all the nonequivalent points in step 5 are caused by the change in functionality, you can use the Conformal software to create a patch file for each nonequivalent module. The patch contains the changes that will transform the functionality of the design.

# Important

Any ADD ECO PIN commands used during this step must also be used for steps 7 and 8. If there is any flattening done during the creation of the ECO patch file, you must perform the same flattening for steps 7 and 8.

See "Creating ECO Patch Files" on page 49 for more information.

**7.** Apply patch and write out ECO netlist.

You can use a patch file to create the ECO netlist after analyzing all of the ECO modules, then write out a netlist that has not been mapped or optimized. See <u>"Applying the ECO Patch and Writing Out the ECO Netlist"</u> on page 52 for more information.

- 8. Use the OPTIMIZE PATCH command to:

- □ Read in SDC, QRC technology file and LEF. For more information on these formats, see <u>"OPTIMIZE PATCH File Requirements"</u> on page 16.

- Map and optimize ECO patch file.

Use the Conformal software to map and optimize the patch file using Genus technology. The software then writes out an Genus script in the working directory that will optimize the patches. See "Mapping and Optimizing the ECO Patch File" on page 53 for more information.

#### 9. Check the ECO netlist.

You should run equivalency checking on the ECO netlist versus the G2 netlist. After that, the netlist can be read into the Innovus tool for incremental optimization and place and route. See "Checking the ECO Netlist" on page 55 for more information.

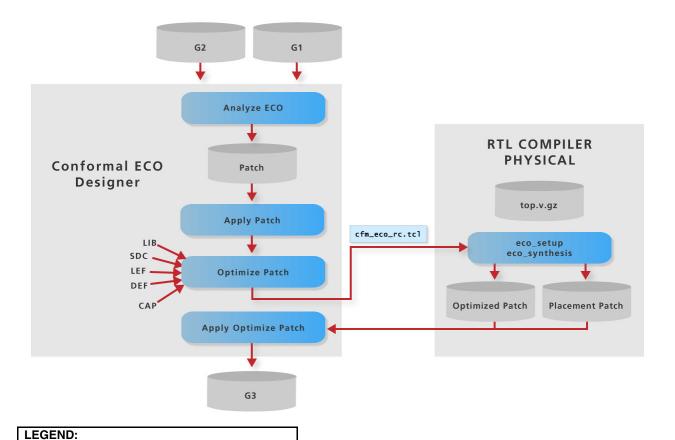

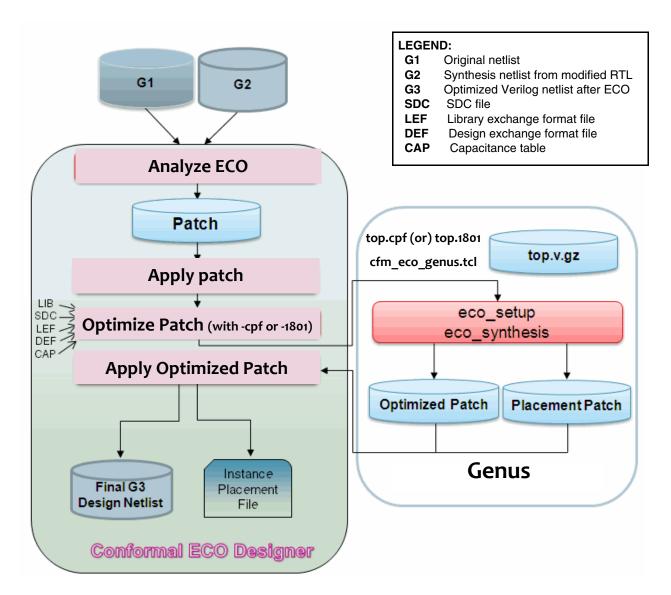

# **Pre-Mask Physical ECO**

This feature requires a Conformal ECO GXL license.

In the following diagram, Conformal ECO generates an optimized Verilog G3 netlist and an instance placement file (in Tcl/text format).

Figure 4-1 Generating an Instance Placement File (in Tcl/Text Format)

# G1 Original Netlist G2 Netlist after ECO G3 Optimized Verilog netlist LIB Timing library SDC SDC file

LEF Library exchange format file

DEF Design exchange format file

QRC QRC technology file

cfm\_eco\_rc.tcl Instance placement file

In the following diagram, Conformal ECO outputs either a DEF or placement guidance file.

Figure 4-2 Generating a DEF or Placement Guidance File

#### G1 Original netlist G2 Synthesis netlist from modified RTL Optimized Verilog netlist after ECO G3 LIB Timing library SDC SDC file LEF Library exchange format file **DEF** Design exchange format file QRC QRC technology file cfm\_eco\_rc.tcl Tcl script to map and optimize the patch

Pre-Mask ECO Flows

# Steps for Implementing a Physically-Aware, Pre-Mask ECO

The following outlines the typical scenario for implementing physically-aware, pre-mask ECOs:

using the following commands:

1. Hierarchically compare the original netlist with the modified netlist. This step involves

- WRITE HIER\_COMPARE DOFILE -balanced\_extraction (suggested)— Extracts a balanced set of hierarchical constraints by simultaneously using flattened golden and flattened revised designs.

- □ RUN HIER\_COMPARE -nodynamic—Runs static hierarchical comparison without auto-flattening the submodules.

- 2. Create ECO patch files using the original netlist (G1) and the netlist after ECO (G2).

After verifying that all the nonequivalent points in the previous step are caused by the change in functionality, you can use the Conformal software to create a patch file for each nonequivalent module. The patch contains the changes that will transform the functionality of the design.

See <u>Creating ECO Patch Files</u> on page 49 for more information.

**3.** Apply the patch and write out the ECO netlist (G3).

You can use a patch file to create the ECO netlist after analyzing all of the ECO modules, then write out a netlist that has not been mapped or optimized. See <u>Applying the ECO Patch and Writing Out the ECO Netlist</u> on page 52 for more information.

- 4. Use the OPTIMIZE PATCH command to:

- Read in SDC, timing libraries, QRC technology file, LEF, and DEF files. For more information on these formats, see <u>"OPTIMIZE PATCH File Requirements"</u> on page 16.

- Map and optimize ECO patch file.

- Use the Conformal software to map and optimize the patch file using Genus technology. The software then writes out an Genus script in the working directory that will optimize the patches. See <u>Mapping and Optimizing the ECO Patch File</u> on page 53 for more information.

- Specify that this optimization is for physically-aware, premask ECOs (-placescript option). This option also writes out the placement script (in Innovus Tcl script format) in the working directory that will optimize the patches and execute the script.

Pre-Mask ECO Flows

**5.** For each ECO module in the list, Genus Physical will write out the placement coordinates of each ECO cell instance in the patch. Conformal ECO will read back the optimized patches and placement files and write out the Verilog G3 netlist and the consolidated placement guidance file (in Tcl/text format).

If you want to output a DEF placement guidance file (instead of Tcl/text format), use the WRITE ECO DEF command to generate the DEF (after the OPTIMIZE PATCH command).

# **Sample Dofiles**

For a sample dofile that illustrates this flow, refer to the "Sample Dofiles" section on the web interface.

To launch the web interface, use the "set web on" command. This command outputs a URL, which you can paste into any of the following web browsers: Internet Explorer 9, Firefox 4, and Chrome 10. The web interface contains the documentation and FAQs for 12.1 features.

5

# **Post-Mask ECO Flows**

- Overview on page 38

- <u>Input Requirements</u> on page 38

- Post-Mask ECO with Standard Cells on page 39

- Steps for Implementing a Post-Mask ECO with Standard Cells on page 40

- Post-Mask ECO with Gate Array Cells on page 42

- □ Steps for Implementing a Post-Mask ECO with Gate Array Cells on page 43

37

■ Sample Dofiles on page 44

Post-Mask ECO Flows

# **Overview**

Post-mask ECO uses two types of spare logic resources:

- Post-Mask ECO with Standard Cells—Compact and run faster than gate-array cells. However, their logic type and location is fixed.

- Post-Mask ECO with Gate Array Cells—Offers more flexibility through different configurations. However, they are larger and slower than standard cells.

You can also have a combination of standard and gate array cells.

# **Input Requirements**

In the flows described in this chapter, you will read in several types of input data and files. These requirements are described in <u>Chapter 1</u>, "<u>Data Requirements</u>".

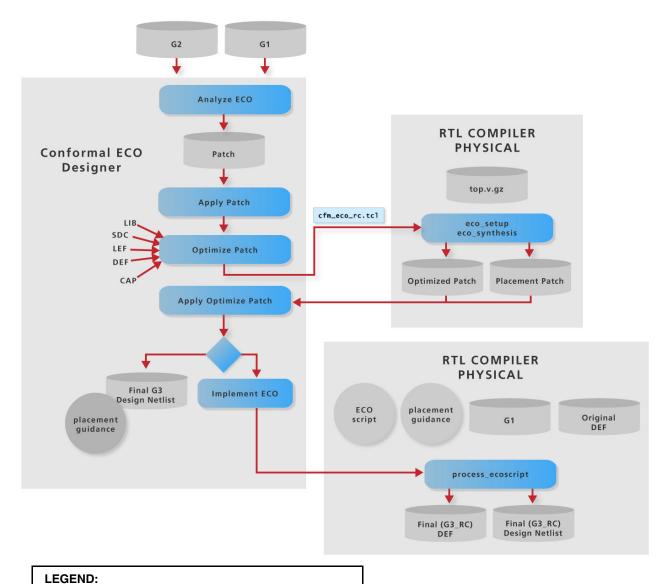

# Post-Mask ECO with Standard Cells

This section describes the Encounter Conformal ECO Designer flow for a post-mask ECO with standard cells.

In the following diagram, the design has completed place-and-route. If the functionality needs to be changed (either for a bug or additional functionality), new RTL is written and the new functionality needs to be added to the placed and routed design. The new RTL is synthesized and this new netlist and the old netlist are processed by the Conformal software to create the ECO netlist. The ECO netlist is based on the old netlist, yet has the functionality of the new netlist.

For a post-mask ECO, you must read the original physical database and parasitic files into the software, which will optimize the spare cell mapping based on the available spare cells. If there are very few spare resources, or the ECO change is very large, there might not be

Post-Mask ECO Flows

enough resources to implement the ECO. Conformal ECO helps to enable early predictability into the post-mask ECO process.

# Steps for Implementing a Post-Mask ECO with Standard Cells

The following steps outline a typical situation:

1. Compare the old RTL to the old netlist.

This comparison should be equivalent. You might need to disable the scan by adding scan constraints.

2. Synthesize the new RTL.

If possible, use the same synthesis tool, version, and script that was used to create the old netlist. Minimize any changes. Synthesizing the new RTL is required to increase the probability of the ECO meeting timing.

**3.** Compare the new RTL to the new netlist.

This comparison should be equivalent.

4. Compare the old RTL to the new RTL.

This comparison should be non equivalent. Make sure to set the X conversion to 'Don't Care' for the new RTL and 'E' for the old RTL. This is the default setting if you read the new RTL as the Golden design and the old RTL as the Revised design. Run both flat and hierarchical comparison. Do not use dynamic hierarchical compare. Note exactly which modules and registers are affected.

Run a UNIX diff on the RTL files to see exactly what was changed. The comparison results and the diff results should be consistent.

**5.** Compare the old netlist to the new netlist.

Run hierarchical compare on the old netlist and the new netlist. Try to get hierarchical comparison to compare as many modules as possible. Again, do not use dynamic hierarchical compare. You will probably have to use the same scan constraints used in step 1. Compare these results to the information from step 4. The nonequivalent modules should be consistent with the comparison results and diff results in step 4.

**6.** Create ECO patch files using the old netlist and the new netlist.

After verifying that all the non equivalent points in step 5 are caused by the change in functionality, you can use the Conformal software to create a patch file for each nonequivalent module. The patch contains the changes that will transform the functionality of the design.

Post-Mask ECO Flows

# /Important

Any ADD ECO PIN commands used during this step must also be used for steps 7 and 8.If there is any flattening done during the creation of the ECO patch file, you must perform the same flattening for steps 7 and 8.

See "Creating ECO Patch Files" on page 49 for more information.

## **7.** Add spare cells.

Use the ADD SPARE CELL command to add spare or freed cells as the available cells for the OPTIMIZE PATCH command.

**Note:** For a post-mask ECO, each ECO patch should have at least one spare tie cell for each phase. For example, a hierarchical design with three ECO modules (resulting in three patches) would need three tie-hi and three tie-low spare cells.

8. Apply patch and write out ECO netlist.

You can use a patch file to create the ECO netlist after analyzing all of the ECO modules, then write out a netlist that has not been mapped or optimized. See <u>"Applying the ECO Patch and Writing Out the ECO Netlist"</u> on page 52 for more information.

- **9.** Use the OPTIMIZE PATCH command to:

- □ Read in SDC, capacitance tables and LEF. For more information on these formats, see <u>"OPTIMIZE PATCH File Requirements"</u> on page 16.

- Map and optimize ECO patch file.

Use the Conformal software to map and optimize the patch file using Encounter RTL Compiler technology. The software then writes out an RTL Compiler script in the working directory that will optimize the patches. See "Mapping and Optimizing the ECO Patch File" on page 53 for more information.

#### 10. Check the ECO netlist.

You should run equivalency checking on the ECO netlist versus the G2 netlist. After that, the netlist can be read into the SoC Encounter tool for incremental optimization and place and route. See <u>"Checking the ECO Netlist"</u> on page 55 for more information.

# Post-Mask ECO with Gate Array Cells

Gate array cells are special cells reserved for ECO changes only. They are added and scattered throughout the design as gate array filler cells, so when there is a need for ECO, these cells can be configured into gate array standard cells (combinational and/or sequential depending on the technology) using top metal changes.

The following diagram illustrates the Encounter Conformal ECO Designer flow for a post-mask ECO with gate array cells.

In the diagram, the design has completed steps 1-5 of the flow described in <u>"Post-Mask ECO with Standard Cells"</u> on page 39.

Post-Mask ECO Flows

# Steps for Implementing a Post-Mask ECO with Gate Array Cells

After verifying that all the non equivalent points are caused by the change in functionality, you can use the Conformal software to create a patch file for each nonequivalent module. The patch contains the changes that will transform the functionality of the design.

1. Create ECO patch files using the old netlist and the new netlist.

After verifying that all the non equivalent points in step 5 are caused by the change in functionality, you can use the Conformal software to create a patch file for each nonequivalent module. The patch contains the changes that will transform the functionality of the design.

## 2. Add spare cells.

Use the ADD SPARE CELL command to add spare, freed, or gate array filler cells as the available cells for the OPTIMIZE PATCH command.

Use the -GAlibcell option of the OPTIMIZE PATCH command to specify the gate array library cell instance names.

- **3.** Use the OPTIMIZE PATCH command to:

- □ Read in SDC, capacitance tables and LEF. For more information on these formats, see <u>"OPTIMIZE PATCH File Requirements"</u> on page 16.

- Map and optimize ECO patch file.

Use the Conformal software to map the patch file to the target technology cells using the restricted set specified in step 2. The software then writes out an RTL Compiler script in the working directory that will optimize the patches.

The tool then applies the mapped patch file to the old gate netlist (G1) and writes out an ECO netlist (G3) and map file.

See Mapping and Optimizing the ECO Patch File on page 53 for more information.

## **4.** Check the ECO netlist (G3).

You should run equivalency checking on the ECO netlist versus the G2 netlist. After that, the netlist can be read into the SoC Encounter tool for incremental optimization and place and route.

Post-Mask ECO Flows

# **Sample Dofiles**

For a sample dofile that illustrates this flow, refer to the "Sample Dofiles" section on the web interface.

To launch the web interface, use the "set web on" command. This command outputs a URL, which you can paste into any of the following web browsers: Internet Explorer 9, Firefox 4, and Chrome 10. The web interface contains the documentation and FAQs for 12.1 features.

6

# **Conformal ECO Power-Aware Flow**

This feature requires a Conformal ECO GXL license.

In the Conformal ECO power-aware flow, functional ECO is performed on a design within the same domain. Conformal ECO passes power intent files to Genus for optimization (using the <code>-cpf</code> or <code>-1801</code> option of <code>OPTIMIZE PATCH</code>). ECOs can be analyzed in flattened or hierarchical comparisons, as long as the domain boundaries are not modified. You can perform pre- or post-mask mapping of library cells based on the power domains specified in the power intent file. Note the following limitations:

- Combinational ECO must be fully contained within a power domain

- Sequential ECO must be fully contained within a power domain that cannot remap to a detention DFF

- The CPF or 1801 specification must remain unchanged

Figure 6-1 Power Aware Flow

The pre-mask and post-mask physical flows require input files (LIB, SDC, LEF, DEF, and CAP) described in <u>"OPTIMIZE PATCH File Requirements"</u> on page 16. The pre-mask, non-physical flow does not require these files.

# Conformal ECO Power-Aware Flow

The following illustrates the command sequence for the power aware pre-mask flow:

#### Conformal ECO

# # Import the design read lib lib.v read design -gol read design -rev g2.v ## Create the patch analyze eco patch.v apply patch -auto ### Optimize the patch in Genus with CPF or 1801 optimize patch [-cpf <cpf\_file> -1801 <1801 file>] report eco changes write eco design

## Genus (cfm\_eco\_genus.tcl)

```

set_attribute use_tiehilo_for_const unique /

eco_setup non_physical \

-degenerate_combo_elts_to_basic \

-read_nl_elab \

-library { } \

-sdc ../ivs_pr_power_cts_wc.sdc \

-cpf ../ivs_pr_power_L.cpf \

-1801 ../ivs pr power L.upf \

-top mod ivs pr power \

-netlist top.v.gz

eco_synthesis pre_mask \

-top_mod ivs_pr_power \

-effort high \

-eco module names { ........}

quit

```

The following illustrates the command sequence for the power aware post-mask flow:

## Conformal ECO

```

# Import the design

read lib lib.v

read design -gol g1.v

read design -rev g2.v

## Create the patch

analyze eco patch.v

apply patch -auto

add spare cell ...

### Optimize the patch in Genus

with CPF or 1801

optimize patch [-cpf <cpf_file>

-1801 <1801 file>]

Report eco changes

Write eco design

```

### Genus Physical (cfm\_eco\_genus.tcl)

```

set_attribute use_tiehilo_for_const unique /

eco_setup physical \setminus

-degenerate_combo_elts_to_basic \

-cpf ../../cpf/top.cpf \

or

-1801 ../../upf/top.upf \

-def ../../pr/g1.pr.def \

-lef_library {../../lib/lef \

FreePDK45_lib_v1.0.lef} \

-top mod vga enh top \

-netlist top.v.qz

eco_synthesis post_mask_physical \

-top_mod vga_enh_top \

-effort high\

-eco_module_names \

{{/vga_enh_top/vga_vtim_eco}}\

-sp_inst_list { .......}

xuit

```

Conformal ECO Power-Aware Flow

7

# **ECO Patch Files**

- Creating ECO Patch Files on page 49

- Applying the ECO Patch and Writing Out the ECO Netlist on page 52

- Mapping and Optimizing the ECO Patch File on page 53

# **Creating ECO Patch Files**

Use the <u>ANALYZE ECO</u> command to create a patch file for each nonequivalent module. The patch file defines a patch module and contains the changes that will transform the functionality of the design. The patch module name is the original nonequivalent module name with an <u>eco</u> appended.

The following is an example script which first compares the old RTL to the new RTL, and then compares the old netlist to the new netlist prior to running ANALYZE ECO:

```

//Script 1: Compares old RTL to new RTL

set log file r1r2.log -replace

usage -auto

read library typical.lib -liberty

read design rtl1.v -golden // RTL1

read design rtl2.v -revised // RTL2

report design data

write hier dofile hier_R1R2.do -constraint -noexact -usage -replace \

-balanced_extractions -function_pin_mapping -input_output_pin_equivalence \

-threshold 0 \

-prepend_string "analyze datapath -verbose"

run hier hier R1R2.do -nodynamic

// Script 2: Compares old netlist to new netlist

set log file g1g2_eco.log -rep

usage -auto

read library typical.lib -liberty

```

**ECO Patch Files**

```

read design top.pr.gv -golden // Old netlist

read design top.1.gv -revised // New netlist

set flatten model -eco

set flatten model -gated clock

add pin constraint 0 scan se -golden

add ignored output scan_out_0 scan_out_1 -golden

uniquify -all -nolibrary -revised

add module attribute mod* -eco_module -noflatten -both

write hier dofile analyze.do -constraints -noexact_pin_match \

-balanced_extractions -function_pin_mapping -input_output_pin_equivalence \

-eco_aware \

-threshold 0 \

-ecopin_dofile ecopins.do -replace

dofile ecopins.do

run hier compare analyze.do -nodynamic

// modules mod1 and mod2 are affected by the ECO

set root module mod1 -both

set system mode lec

add compare point -all

compare

analyze eco patch1.v -preserve_clock -replace

set system mode setup

set root module mod2 -both

set system mode lec

add compare point -all

compare

analyze eco patch2.v -preserve_clock -replace

```

# **Adding Input and Output Ports**

If the ECO changes require new module ports, use the <u>ADD ECO PIN</u> command. The following example adds several input and output ports to a module called colproc:

```

add eco pin colproc clut_req addr_1 -golden -input

add eco pin colproc xcnt ctrl_sync -golden -output

```

When using ADD ECO PIN, make sure you run it before hierarchical compare.

Using  ${\tt ADD}\ {\tt ECO}\ {\tt PIN}$  is not necessary for submodules if you generate the patch with the flat methodology.

**ECO Patch Files**

There are situations where you might not want to perform the ECO with a hierarchical methodology; for instance, where the old netlist is flat. An example of the flat methodology is as follows:

```

set log file g1g2.eco.log -replace

usage -auto

read library typical.lib -liberty

read design top.pr.gv -golden // Old netlist

read design top.1.gv -revised // New netlist

report design data

report black box

set flatten model -gated_clock

set flatten model -eco

add pin constraint 0 scan_se -golden

add ignored output scan_out_0 scan_out_1 -golden

set system mode lec

add compare point -all

compare

analyze eco patch.v -preserve_clock -replace

```

# **Automatically Adding and Deleting ECO Pins**

To automatically add and/or delete ECO pins by executing either of the following commands. They both write out a dofile for adding/deleting ECO pins to the golden design as compared to the revised design.

■ write hier\_compare dofile -ecopin\_dofile <filename>

## For example:

```

write hier_compare dofile hier.do -replace \

-constraint -noexact_pin_match \

-balanced_extractions \

-function_pin_mapping \

-input_output_pin_equivalence \

-eco_aware \

-threshold 0 \

-ecopin_dofile ecopins.do \

-verbose

```

This is the recommended command. The <code>-constraint</code> and <code>-noexact\_pin\_match</code> command options are required, because you cannot delete pins in the middle of a bus and the added cell must be immediately adjacent to the original bus.

**ECO Patch Files**

analyze hier\_compare -ecopin\_dofile <filename>

With this command, you do not need to go back to LEC mode to execute analyze\_hier.do. For example:

```

analyze hier_compare -dofile hier_analyze.do -replace \

-constraints \

-noexact_pin_match \

-function_pin_mapping \

-input_output_pin_equivalence \

-eco_aware \

-threshold 0 \

-ecopin_dofile ecopins.do \

```

The -constraint and -noexact\_pin\_match command options are required, because you cannot delete pins in the middle of a bus and the added cell must be immediately adjacent to the original bus.

# Applying the ECO Patch and Writing Out the ECO Netlist

You can use a patch file to create the ECO netlist after analyzing all of the ECO modules (in the following example, mod1 and mod2). Go back into Setup mode and set the root module back to the top-level module, delete all of the blackboxes from the hierarchical compare, then apply the patches. Running the APPLY PATCH command changes the design based on the patch module.

```

set system mode setup

set root module top -both

delete black box -all -hier -both

apply patch -keephierarchy -golden -auto

write design top.eco.gv -replace -auto

```

At this point you can also write out a netlist that has not been mapped or optimized.

#### Notes:

- The changes made by the APPLY PATCH command are not reflected in the schematic of the hierarchical design.

- The APPLY PATCH command's -auto option automatically reads in and applies all patches that were created with the ANALYZE ECO command in the current session.

**ECO Patch Files**

# Mapping and Optimizing the ECO Patch File

The patch files created by the ANALYZE ECO command contains logic that is unoptimized and might contain unmapped logic cells.

The Conformal software can map and optimize the patch file using Encounter RTL Compiler technology. Make sure that the proper RTL Compiler version (10.1 or later) is installed and that it is the first rc command in the search path. If you want to override the search path, you can specify the exact rc command.

# **Pre-mask Flow Script**

The OPTIMIZE PATCH command writes out an RTL Compiler script (cfm\_eco\_rc.tcl) in the working directory that will optimize the patches and automatically executes the RC script. You must run the APPLY PATCH -keephierarchy command before running OPTIMIZE PATCH. After OPTIMIZE PATCH successfully completes, the ECO design will be in memory and can be written out. The optimized patches will be in the working directory. In most premask cases, you can check the ECO netlist at this point (see Checking the ECO Netlist on page 55 for more information).

```

apply patch -keephierarchy -auto

optimize patch -workdir WORK_PRE \

-library ../../lib/liberty/FreePDK45_lib_v1.0_typical.lib \

-sdc ../../syn1/g1.rc.sdc \

-INStancenaming "ECO2inst_%d" -NETnaming "ECO2net_%d" -SEQuentialnaming \

"ECO2reg_%s" \

-rcexec "rc -nogui" \

-verbose

// Write out the G3 ECO Netlist

write eco design -newfile %s.pre.G3 -replace -report ECOprelogics.rpt

```

You can retain all freed instances in the original netlist and apply a value of X (unconnected), 0 (tie low), or 1 (tie high) to input pins of any freed instance with the APPLY PATCH command's -keepfreed, -tiefreed0, and -tiefreed1 options, respectively.

**Note:** The WRITE ECO DESIGN command attempts to minimize the text differences in the netlist that is written out. This command will not work if the FLATTEN command was previously run against G1; in this case, use WRITE DESIGN to write out the G3 netlist.

To customize the RC script or map the patch with some other process, you must apply the patch and write out the design (see <u>Applying the ECO Patch and Writing Out the ECO Netlist</u> on page 52).

**ECO Patch Files**

# **Post-mask Flow Script**

The following shows an example of a post-mask flow script where Conformal ECO does physically-aware spare-gate mappin

g. This feature requires an ECO-GXL license. A DEF file corresponding to the old netlist is necessary for the post-mask flow to derive spare gate physical information. You can read in other physical information (LEF and CAP tables) to help the physically aware mapping. You can also read in the SDC (Design Constraints) to derive timing constraints for each module.

```

apply patch -keephierarchy -auto

```

Use the ADD SPARE CELL command to specify the DEF file and spare cells.

```

add spare cell -def ../top.pr.def -spare spare_*/spr_gate*

add spare cell -freedcell

report spare cell

```

Use the OPTIMIZE PATCH command's -mapscript option to write out the location-aware spare-gate mapping result in the form of a TCL script that you can use with your back-end tool.

```

optimize patch -workdir WORK_POST -usespare \

-library ../lib/typical.lib \

-sdc ../sdc/top.sdc \

-lef ../lib/lef/top.lef \

-def ../pr/top.pr.def \

-mapscript swapcells.tcl \

-INStancenaming "ECO2inst_%d" -NETnaming "ECO2net_%d" -SEQuentialnaming "ECO2reg_%s" \

-rcexec "rc -nogui" \

-verbose

write eco design -newfile %s.post.G3 -replace -report ECOpostlogics.rpt

```

#### Notes:

- There might not be enough spare and free resources available to implement the ECO.

Make sure that all spare cells are specified with the ADD SPARE CELL command.

- The mapping process will not map registers and latches to spare or freed cells. You can manually edit the ECO netlist to change the register and latch cell type.

8

# **Checking the ECO Netlist**

Run equivalency checking on the new netlist to the ECO to make sure the ECO netlist has the correct functionality. If test needs to be disabled, also perform a comparison with test enabled to the old netlist. This comparison should be equivalent.

The ECO netlist can now be read into the SoC Encounter tool for incremental optimization and place and route.

Checking the ECO Netlist

9

# **ECO Cut Point Flow**

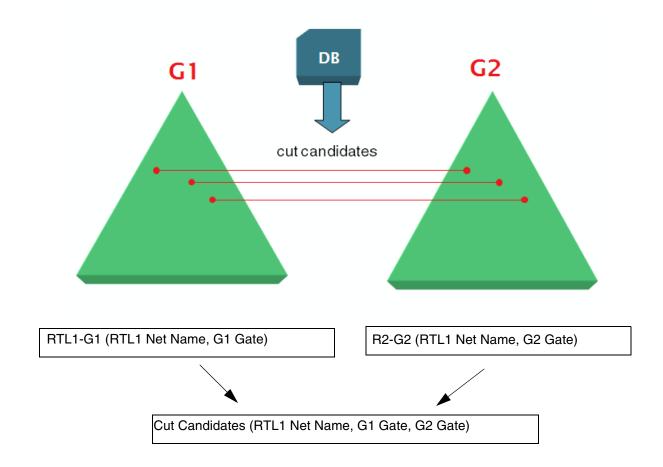

Use the ECO cut point flow when you want an automated way to refine and possibly reduce the size of an ECO patch. This flow leverages ECO input data and existing RTL- and gate-level netlist information to create a database of reference points; this database will drive the reduction of the ECO patch size.

# **ECO Cut Point Flow (Diagram)**

# **ECO Cut Point Flow (Steps)**

A typical scenario for the ECO cut point flow involves the following steps:

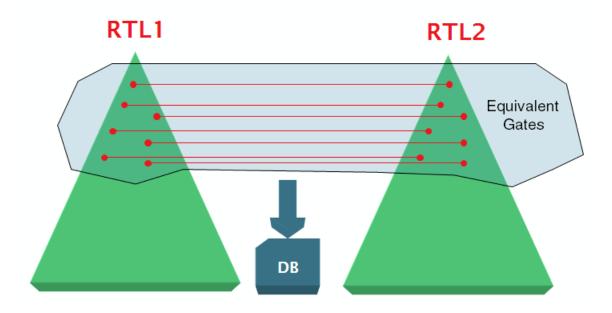

- 1. Compare RTL1 and RTL2.

- **a.** Use the READ DESIGN command to read in the original RTL (RTL1) and the RTL (RTL2) that has the ECO.

- **b.** In LEC mode, use the ADD COMPARED POINTS command to add mapped points to the compare list.

- **c.** Use the COMPARE command to start the comparison.

**ECO Cut Point Flow**

**d.** Use the ANALYZE ECO command with the -create\_db option to analyze the comparison, find potential RTL net cutpoint candidates, and to save the candidates into the cut point database.

## For example:

```

set x conversion e -both

read design r1.v -golden -replace

read design r2.v -revised -replace

set system mode lec

add compare point -all

compare

analyze eco -create_db r1r2 r1r2.db

```

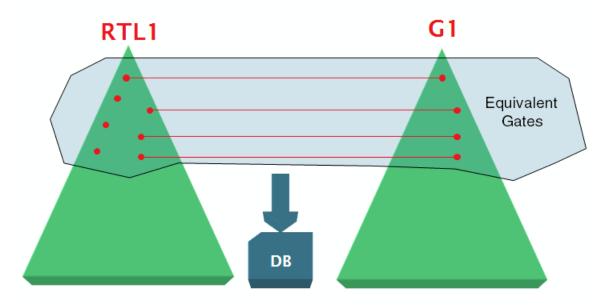

## 2. Compare RTL1 and G1.

- **a.** Use the READ DESIGN command to read in the original RTL (RTL1) and the original netlist (G1).

- **b.** In LEC mode, use the ADD COMPARED POINTS command to add mapped points to the compare list.

- **c.** Use the COMPARE command to start the comparison.

- **d.** Use the ANALYZE ECO command with the -cutpoint option to analyze the comparison, find equivalent "RTL1 net- G1 gate" pairs into the cut point database.

## For example:

```

read design r1.v -golden -replace

read design g1.v -revised -replace

set system mode lec

add compare point -all

compare

analyze eco -create_db r1g1 r1g1.db -import_db r1r2.db

```

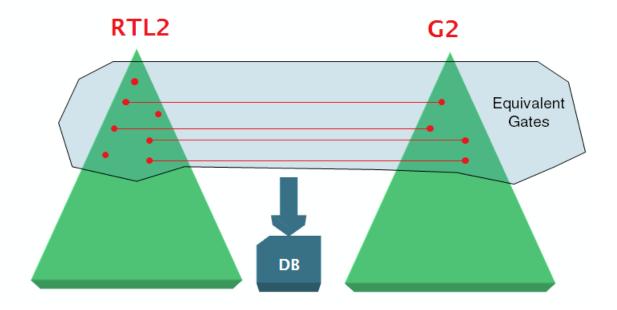

#### **3.** Compare RTL2 and G2.

- a. Use the READ DESIGN command to read in the RTL2 and G2.

- **b.** In LEC mode, use the ADD COMPARED POINTS command to add mapped points to the compare list.

- **c.** Use the COMPARE command to start the comparison.

- **d.** Use the ANALYZE ECO command with the -cutpoint option to analyze the comparison, find equivalent "RTL2 net- G1 gate" pairs in the cut point database.

**ECO Cut Point Flow**

# For example:

```

read design r2.v -golden -replace

read design g2.v -revised -replace

set system mode lec

add compare point -all

compare

analyze eco -create db r2g2 r2g2.db -import db r1r2.db

```

**4.** Combine the database entries from steps 2 and 3 to form triples (RTL nets, G1 gates, and G2 gates) and insert into G1 and G2. For example:

```

read library ../LIB/VERILOG/*.v -both -replace

read design g1.v -golden -replace

read design g2.v -revised -replace

set eco option -flat

flatten -nolib -matchhier -revised

uniquify -all -nolib -revised

add pin constraint 0 scan_se -golden

set system mode lec

analyze hier -eco_aware

add compare points -all

compare

compare eco hier

report eco cut -import_db ./DB/r1g1.db ./DB/r2g2.db -auto -file

addcut.do

dofile addcut.do

analyze eco cutpoint

analyze eco patch.v -replace

set system mode setup

apply patch -auto

```

**ECO Cut Point Flow**

# Sample output for ANALYZE ECO CUTPOINT: