# cādence<sup>™</sup>

# **Conformal® Equivalence Checking User Guide**

Conformal L, Conformal XL, and Conformal GXL

Product Version 23.2 October 2023 © 1997– 2023 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

Cadence is committed to using respectful language in our code and communications. We are also active in the removal and/or replacement of inappropriate language from existing content. This product documentation may however contain material that is no longer considered appropriate but still reflects long-standing industry terminology. Such content will be addressed at a time when the related software can be updated without end-user impact.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

# Contents

| About This Manual             | 9  |

|-------------------------------|----|

| Audience                      | 9  |

| How This Manual Is Organized  | 9  |

| Conventions                   | 20 |

| Syntax Structure              | 20 |

| GUI Convention                | 21 |

| Additional Learning Resources | 21 |

# 1

| Introduction to the Conformal Equivalence Checker 23 |

|------------------------------------------------------|

| <u>Overview</u>                                      |

| Conformal Features                                   |

| Supported File Formats                               |

| Conformal Methodology 27                             |

| Preparing the Designs                                |

| Mapping and Comparing                                |

| Diagnosing                                           |

| Conformal Operation                                  |

| System Modes                                         |

| <u>Transition</u>                                    |

| <u>Mapping</u>                                       |

| <u>Comparison</u>                                    |

| <u>Diagnosis</u>                                     |

| Overview of Conformal Tcl                            |

| Conventions                                          |

| Specifying the Command Entry Mode                    |

| Using Native Conformal Commands                      |

| Duplicate Commands                                   |

| <u>Tcl Version</u>                                   |

| <u>2</u>                                          |

|---------------------------------------------------|

| Getting Started 37                                |

| Product and Installation Information              |

| Start-Up Command Options 38                       |

| Initial Command Files                             |

| Dofile Command Files                              |

| Saving and Restoring a Session 48                 |

| Save and Restore Commands                         |

| Checkpoint and Restart Facility                   |

| Transcript Messages                               |

| <u>Aliases</u>                                    |

| Setting Preferences                               |

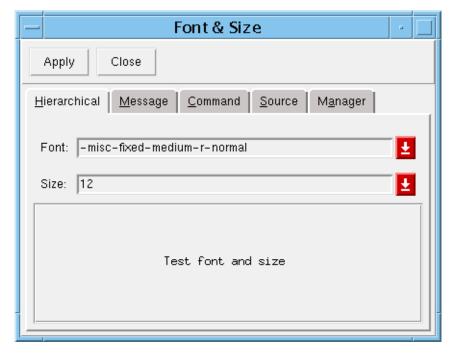

| Font & Size                                       |

| Hierarchical Browser On 51                        |

| Hierarchical Browser Sync. up                     |

| <u>Icon Bar</u>                                   |

| Show Static Infobox                               |

| Simplified Schematic Viewing                      |

| Accessing Online Help and Documentation           |

| Launching Cadence Help                            |

| Getting Help for Cadence Help 53                  |

| Getting Help on Commands to Run Tools             |

| Getting Help on Commands and Messages             |

| Searching the Help Database for Specified Strings |

| Using the Help Menu                               |

| Platform Integration                              |

| Dofile Generation from First Encounter 55         |

| Dofile Generation from RC Synthesis Tools         |

| Using Conformal With Virtuoso 62                  |

|                                                   |

## <u>3</u>

| Using the Graphical User Interface | 63 |

|------------------------------------|----|

| Main Window                        | 64 |

| Selecting Multiple Items           | 64 |

| Drag and Drop                |

|------------------------------|

| <u>Menu Bar</u>              |

| <u>Window Menu</u>           |

| <u>Icon Bar</u>              |

| Find Hierarchical Module     |

| Hierarchical Browser         |

| Transcript Window            |

| Command Entry Window         |

| <u>Status Bar</u>            |

| Exiting the GUI and Software |

| <u>File Menu</u>             |

| <u>Setup Menu</u>            |

| <u>Report Menu</u>           |

| <u>Run Menu - Compare</u>    |

| <u>Tools Menu</u>            |

## <u>4</u>

| Command Line Features         | 79 |

|-------------------------------|----|

| Command Line Editing          | 79 |

| Command Line Completion       | 81 |

| Using Command Line Completion | 81 |

| Repeating Actions             | 81 |

| <u>Notes</u>                  | 82 |

## <u>5</u>

| <u>5</u>                                |                |

|-----------------------------------------|----------------|

| Managing Rule Checks                    | 33             |

| HDL Rule Manager                        | 34             |

| HDL Rule Manager Fields and Options     | 35             |

| Severity Levels                         | 36             |

| Enabling and Disabling Rule Checks 8    | 37             |

| Running Incremental Rule Checks 8       | 37             |

| Reporting Messages for Rule Checks 8    | 38             |

| Viewing a Specific Message 8            | 38             |

| Viewing Source Code for an Occurrence 8 | 38             |

| Modeling Messages                       | <del>)</del> 0 |

|                                         |                |

| <u>6</u>                                          |

|---------------------------------------------------|

| Using the Setup Mode                              |

| <u>Overview</u>                                   |

| Setting Options                                   |

| <u>Changing the Root Module</u>                   |

| Adding Search Paths                               |

| Adding Notranslate Modules                        |

| Setting Global Options For Mapping and Comparison |

| Reading in Libraries and Designs                  |

| Reading in Library Files                          |

| Reading in Design Files                           |

| Using Verilog Command Filelists                   |

| Library-based Compilation 111                     |

|                                                   |

| Comparing Design Hierarchies 113                  |

| Comparing Libraries                               |

| Design Constraints                                |

| <u>Blackboxes</u>                                 |

| Net Constraints                                   |

| Pin Constraints                                   |

| Pin Equivalences                                  |

| Primary Inputs                                    |

| Primary Outputs                                   |

| <u>Tied Signals</u>                               |

| Instance Constraints                              |

| Instance Equivalences                             |

| <u>Cut Points</u>                                 |

| Flattening Options                                |

| Specifying Key Point Mapping Options              |

| Retaining Gate Pin Information                    |

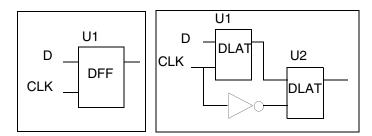

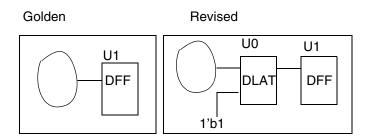

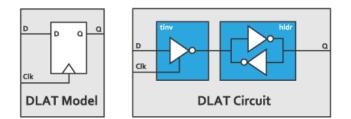

| Converting DLATs to DFFs 137                      |

| Converting DLATs to Buffers                       |

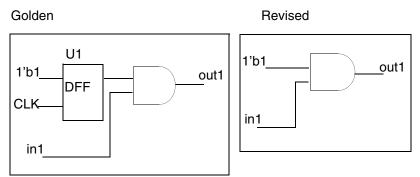

| Converting DFF or DLAT to Zero or One Gate        |

| Gated-Clock Learning                              |

| Converting DFFs to DLATs                          |

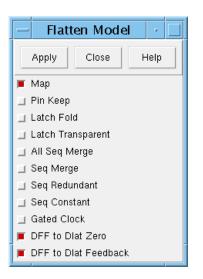

| Flatten Model Form | 144 |

|--------------------|-----|

| Mapping Settings   | 145 |

| Mapping Methods    | 146 |

| Renaming Rules     | 147 |

# <u>7</u>

| Using the LEC Mode 155                                              |

|---------------------------------------------------------------------|

| Moving to LEC Mode                                                  |

| Mapping Modifications                                               |

| Altering Key Point Mapping                                          |

| Adding Mapped Points                                                |

| Inverting Mapping Phase                                             |

| Saving Mapping Results                                              |

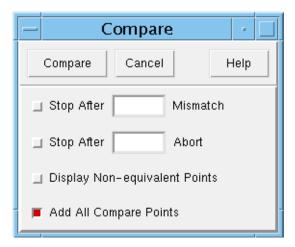

| Compare Options                                                     |

| Adding Compared Points                                              |

| Setting the Compare Effort 159                                      |

| Setting a CPU Limit                                                 |

| Reporting Compare Time                                              |

| Conformal does not record compare time for trivial cones.Comparison |

| Reporting Compare Data                                              |

| Reporting Statistics                                                |

| Reporting CPU Use                                                   |

| Report Verification                                                 |

| Running Additional Reports                                          |

| Black Boxes Report                                                  |

| Cut Points Report                                                   |

| Design Data Report                                                  |

| Environment Report                                                  |

| Floating Signals Report                                             |

| Instance Constraints Report 164                                     |

| Instance Equivalences Report                                        |

| Messages Report                                                     |

| Modules Report                                                      |

| Notranslate Modules Report                                          |

| Pin Constraints Report                                              |

| Pin Equivalences Report 167 |

|-----------------------------|

| Primary Inputs Report       |

|                             |

| Primary Outputs Report      |

| Renaming Rules Report       |

| Search Paths Report         |

| Tied Signals Report         |

| Mapped Points Report        |

| Unmapped Points Report      |

| Compared Points Report      |

| Compare Data Report         |

| Statistics Report           |

## <u>8</u> Debuggir

| <u>Debugging</u>                                       |

|--------------------------------------------------------|

| Diagnosing Non-Equivalent Points                       |

| Proving Equivalence                                    |

| Adding Dynamic Constraints                             |

| Displaying Error Patterns                              |

| Reporting Design Similarities 176                      |

| <u>Gate Manager</u>                                    |

| Gate Manager Fields and Options 180                    |

| Refreshing the Window                                  |

| Opening Schematics from the Gate Manager               |

| Using the Preferences Drop-Down Menu 181               |

| Filtering the Gate List                                |

| Finding Gates                                          |

| Reporting Gate Information                             |

| Customizing the Gate List Section with Specified Gates |

| Proving Equivalency for Two Specified Gates            |

| Removing Gates from the Prove List 185                 |

| Locating an Equivalent Gate                            |

| Adding and Deleting Dynamic Constraints                |

| Locating a Gate in the Design Hierarchy 186            |

| Highlighting a Point in the Hierarchical Browser       |

| Viewing a Gate's Location in the Source Code           |

| Highlighting a Point in the Source Code Manager                  |

|------------------------------------------------------------------|

| Viewing a Schematic Representation of One Gate                   |

| Gate Reporting                                                   |

| Setting the Gate Report                                          |

| Gate Tracing                                                     |

| Gate Report Structure                                            |

| Mapping Manager                                                  |

| Mapping Manager Fields and Options                               |

| Setting Preferences                                              |

| Copying Information from the Mapping Manager                     |

| <u>Selecting Points</u>                                          |

| Adding Unmapped Points as Mapped Points                          |

| Reporting Information on an Unreachable Gate                     |

| Reporting Renaming Rules                                         |

| Re-Mapping Key Points                                            |

| Adding All Compared Points                                       |

| Deleting One or More Mapped Points 19                            |

| Adding One or More Compared Points 19                            |

| Changing the Mapping Phase of a Mapped Point                     |

| Highlighting a Mapped Point in the Compared Points Section       |

| Comparing Key Points                                             |

| Deleting One or More Compared Points 19                          |

| Diagnosing a Non-Equivalent Point in the Compared Points Section |

| Sorting Compared Points by Support Size                          |

| Sorting Compared Points by Non-Corresponding Support Cones       |

| Changing the Mapping Phase of a Compared Point                   |

| Highlighting a Compared Point in the Mapped Points Section       |

| Displaying the Information Box                                   |

| Filtering the Display                                            |

| Finding Key Points                                               |

| Displaying Specified Classes of Points                           |

| Deleting Mapped or Compared Points                               |

| Displaying Diagnosis Data                                        |

| Reporting Gate Information                                       |

| Displaying Fan-in and Fan-Out Information                        |

| Locating a Point in the Source Code                              |

| Locating a Point in the Design Hierarchy 205            |

|---------------------------------------------------------|

| Viewing a Schematic of a Point                          |

| Diagnosis Manager                                       |

| Diagnosis Manager Fields and Options                    |

| Setting Preferences                                     |

| Copying Information from the Diagnosis Manager 214      |

| Refreshing the Window                                   |

| Displaying the Information Box                          |

| Selecting a New Active Diagnosis Point 214              |

| Changing the Simulation Value 214                       |

| Saving Modified Values as an Error Pattern 215          |

| Viewing a Schematic                                     |

| Changing the Mapping Phase of a Mapped Point            |

| Deleting Mapped Points                                  |

| Reporting Renaming Rules                                |

| Adding Unmapped Points as Mapped Points                 |

| Viewing a Schematic Representation of Diagnosis Points  |

| Displaying the Fill Fanin Cone                          |

| Displaying Gate Information                             |

| Showing a Gate's Location in the Source Code            |

| Showing Where a Gate is Located in the Design Hierarchy |

| Exit Status Codes                                       |

|                                                         |

## <u>9</u>

| Resolving Aborts          | 23 |

|---------------------------|----|

| <u>Overview</u>           | 24 |

| Avoiding Aborts           | 24 |

| RTL Guidelines            | 24 |

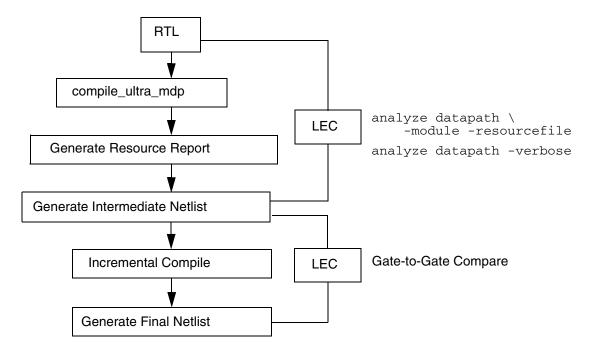

| MDP Flow                  | 27 |

| RTL Compiler Flow         | 27 |

| Resolving Aborts          | 28 |

| Hierarchical Comparison 2 | 28 |

| Analyzing Abort Points    | 28 |

| Multithreading            | 29 |

| Partitioning              | 29 |

| - |

|---|

## <u>10</u>

| Running Hierarchical Comparison                     |

|-----------------------------------------------------|

| Comparing Designs at the Module Level               |

| Running Dynamic Hierarchical Comparison             |

| Interrupting a Hierarchical Comparison              |

| Hierarchical Comparison Command Flow                |

| Read the Libraries and Designs 238                  |

| Generate a Hierarchical Compare Dofile              |

| No Blackboxing                                      |

| Constraint Propagation                              |

| Renaming Rules                                      |

| Hierarchical Compare Dofile Execution               |

| Hierarchical Comparison for Abort Resolution        |

| Hierarchical Module Comparison Window               |

| Hierarchical Module Comparison Fields and Options   |

| Setting General Options                             |

| Reporting CPU Use                                   |

| Working with Hierarchical Compare Dofiles           |

| Finding Module Names                                |

| Deselecting the Dual Scroll Option 249              |

| Viewing a Module's Compare Status 249               |

| Specifying Blackbox Modules                         |

| Deleting Previously Added Blackbox Modules 249      |

| Ignoring Modules during Comparison                  |

| Deleting No-Blackbox Status                         |

| Running a Hierarchical Comparison                   |

| Comparing Lower-Level Modules 250                   |

| Highlighting Non-Equivalent Modules                 |

| Deleting and Resetting Hierarchical Compare Results |

| Specifying the Root Module                          |

# <u>11</u>

| Advanced Capabilities                               |

|-----------------------------------------------------|

| <u>Overview</u>                                     |

| Supported Datapath Structures and Optimizations     |

| <br><u>Multipliers</u> 256                          |

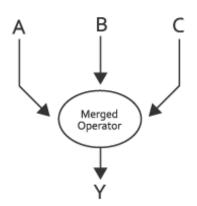

| Operator Merging                                    |

| Resource Sharing                                    |

| Sequential Merge Optimization 258                   |

| Module-Based Datapath Analysis                      |

| Datapath Module Abstraction                         |

| Datapath Module Abstraction Reporting and Diagnosis |

| Handling Aborts in Datapath Module Abstraction      |

| Datapath Operator Learning                          |

| DC Synthesis Flow                                   |

| Sample DC Script                                    |

| DC Commands                                         |

| MDP Effort Levels                                   |

| Dofile Example for Intermediate Netlists            |

| Dofile Example for Intermediate to Final Netlist    |

| Extracting Testcases for Datapath Modules           |

| Recreating Testcases for Datapath Modules           |

| Isolating Aborted Datapath Modules                  |

| Word-Level Datapath Analysis 272                    |

| Datapath Learning                                   |

| Reporting and Diagnosis of Datapath Analysis        |

| Sequential Merge Analysis                           |

| Sequential Merge Flow                               |

| Synthesis Requirements                              |

| Sequential Merge Verification                       |

| Setting the Effort Level                            |

| Diagnosing Instance/Sequential Merge Nonequivalence |

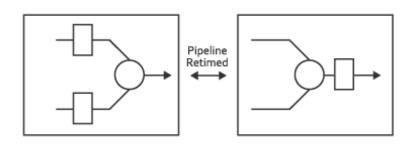

| <u>Retiming</u>                                     |

| Basic Pipeline Retiming                             |

| Advanced Pipeline Retiming                          |

| Pipeline Retiming on a List of Specified Registers  |

| Pipeline Backward Retiming                 |

|--------------------------------------------|

| Merging Equivalent Registers 280           |

| Retiming Diagnosis                         |

| Flattened Retiming Analysis                |

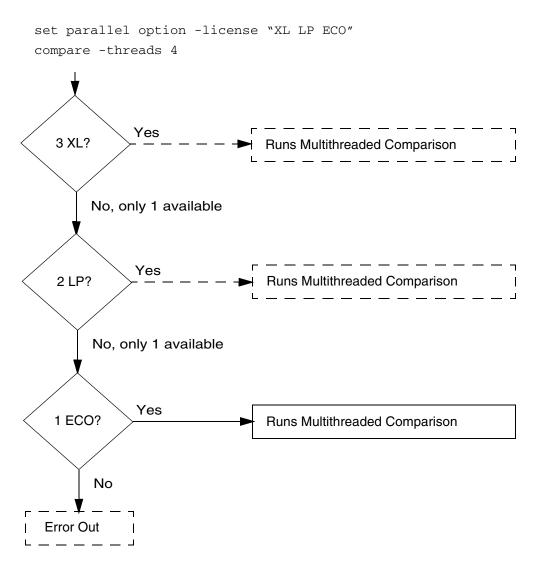

| Multithreading Process 281                 |

| Multithreading Model                       |

| Enabling Multithreaded Processing          |

| Setting Comparison Effort Levels           |

| Setting Comparison Options 283             |

| Number of Threads Recommendation           |

| Running Jobs on Server Farms               |

| Licensing Requirements                     |

| Temporary Files and Directories            |

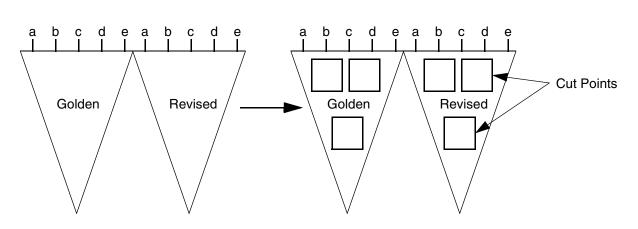

| Multi-Threaded Functional Partitioning     |

| Adding Partition Points                    |

| Adding Partition Points for Comparison     |

| Name-based Physical Partitioning           |

| Comparison with Functional Partitioning    |

| Analyzing Non-Equivalence                  |

| Example Report                             |

| Analyzing Implication Values               |

| Netlist Analysis                           |

| Extracting Half Adder and Full Adder Cells |

| Identifying and Optimizing Library Cells   |

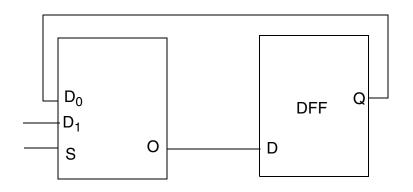

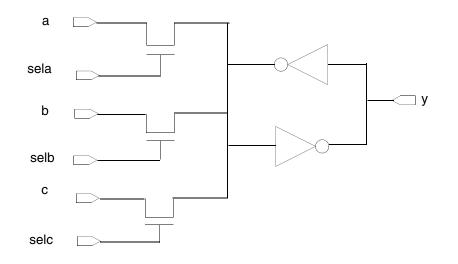

| Extracting MUX Logic for DFFs 294          |

| Sample Dofile                              |

|                                            |

## <u>12</u>

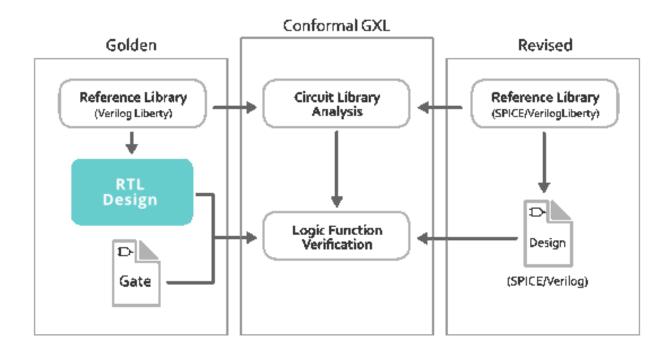

| Layout Versus Schematic            | 297 |

|------------------------------------|-----|

| Overview                           | 298 |

| LVR Functionality                  | 298 |

| Starting Conformal GXL             | 299 |

| LVR Flow                           | 299 |

| Circuit Library Analysis           | 300 |

| Design Logic Function Verification | 301 |

| LVR Implementation |                 | <br> | <br> | <br>302 |

|--------------------|-----------------|------|------|---------|

| Suggested Uses     |                 | <br> | <br> | <br>302 |

| Conformal Dofile   | <u>Examples</u> | <br> | <br> | <br>302 |

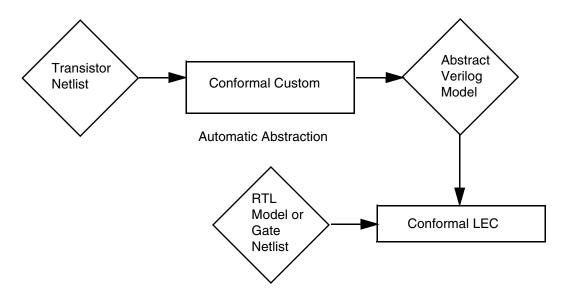

# <u>13</u>

| Conformal Custom                              |

|-----------------------------------------------|

| <u>Overview</u>                               |

| Custom Licensing                              |

| Abstraction Methods                           |

| Starting Conformal GXL                        |

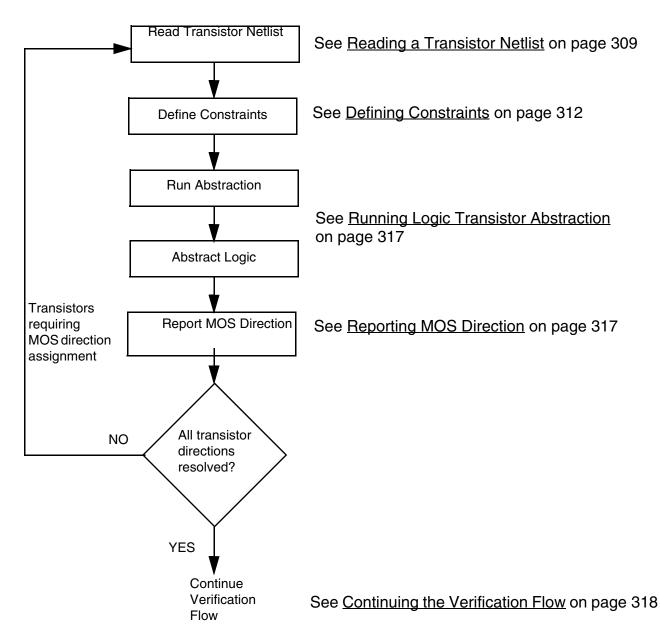

| Conformal GXL Process Flow                    |

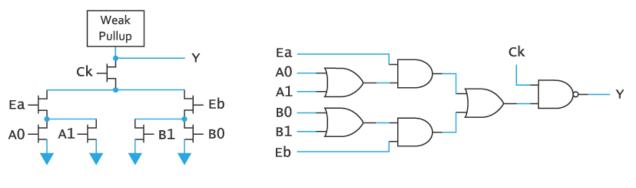

| Reading a Transistor Netlist                  |

| Defining Constraints                          |

| Running Logic Transistor Abstraction          |

| Reporting MOS Direction                       |

| Continuing the Verification Flow              |

| Specifying Conditions for Abstracting Logic   |

| Analyzing Switch and Primitive Drive Strength |

| <u>Custom Menu</u>                            |

| <u>General Setup</u>                          |

| Tie Off Cell Pins to 0 or 1         323       |

| Set Equivalent or Inverted Cell Input Pins    |

| Group Single Pins into Bus                    |

| <u>Flatten</u>                                |

| <u>Ungroup Module</u>                         |

| Group Instances into New Module               |

| <u>Custom Setup</u>                           |

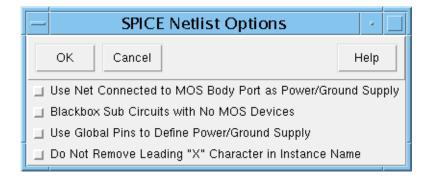

| SPICE Netlist Options                         |

| MOS Devices Name                              |

| Pre-charge Clocks                             |

| Module Pin Direction                          |

| Circuit to Logic Transformation Settings      |

| MOS Direction                                 |

| Define Power and Ground Supply 341            |

| Data Entry Menu                               |

## <u>14</u>

## Conformal ECO Designer Functionality and Methodology . 361

#

| VHDL Support                            |

|-----------------------------------------|

| Supported and Unsupported IEEE Packages |

| Vital Package Support                   |

| <u>Read Design</u>                      |

| Library Mapping                         |

| <u>Architectures</u>                    |

| <u>Global Signal</u>                    |

| <u>Configurations</u>                   |

| Component Configuration                 |

| Nested Configurations                   |

| <u>Declarations</u>                     |

| Initial Value                           |

| Shared Variable                         |

| <u>Names</u>                            |

| <u>Sliced Names</u>                     |

| Predefined Attributes                   |

| User-Defined Attributes 383             |

| <u>Expressions</u>    |

|-----------------------|

| Function Calls        |

| Sequential Statements |

| Wait Statements       |

| Signal Assignment     |

| Procedure Calls       |

| For Loops             |

| <u>While Loops</u>    |

| Concurrent Statements |

| Signal Assignment     |

## <u>B</u> Verilog Support

| Verilog Support                     |

|-------------------------------------|

| Verilog Configurations              |

| Supported Constructs                |

| Synthesizable UDPs                  |

| Instance Configuration Examples 395 |

| Verilog 2001 Support Tables         |

| <u>Supported</u>                    |

| Limited Support                     |

| <u>Ignored</u>                      |

| Not Applicable                      |

## <u>C</u>

|           | Tasks and Functions                      |

|-----------|------------------------------------------|

|           | <u>Classes</u>                           |

|           | Randomization & Constraints              |

|           | Synchronization                          |

|           | Scheduling Semantics                     |

|           | Clocking Blocks                          |

|           | Program Blocks                           |

|           | <u>Assertions</u>                        |

|           | <u>Coverage</u>                          |

|           | Modules and Hierarchy                    |

|           | <u>Interfaces</u>                        |

|           | <u>Packages</u>                          |

|           | Configuration Libraries                  |

|           | System Tasks and Functions               |

|           | <u>VCD Data</u>                          |

|           | Macros and Compiler Directives           |

|           | <u>APIs</u>                              |

|           | Configuring the Contents of a Design 434 |

|           | <u>Annexes</u>                           |

|           | <u>Non-std</u>                           |

| <u>Sy</u> | stem Verilog Assertions (SVA)            |

|           | Supported SVA System Functions           |

|           | Default Clocking                         |

|           | Property Declaration                     |

|           | Property Binding                         |

|           | Supported SVA Properties                 |

|           | Clocked Boolean Expression               |

|           | <u>Examples</u>                          |

# <u>D</u>

| Supported Directives         | 443 |

|------------------------------|-----|

| Supported Vendors            | 444 |

| Supported Directives         | 444 |

| Conformal Directive Examples | 446 |

| Enabling One Directive       | 447 |

| Disabling All Directives for One Vendor 44     | .8 |

|------------------------------------------------|----|

| Disabling Specified Directives for One Vendor  | .8 |

| Enabling a List of Directives from an RTL File | .8 |

# <u>E</u>

| Conformal Sample Test Case 449        |

|---------------------------------------|

| Starting Conformal                    |

| Reading the Library                   |

| Read the Designs                      |

| Changing to the LEC System Mode 452   |

| Viewing Unmapped and Mapped Points    |

| Running a Comparison                  |

| Diagnosing a Non-Equivalent Point 454 |

| Non-Corresponding Support Section 455 |

| Error Pattern Section                 |

| Error Candidate Section               |

| Opening the Schematic Viewer          |

| Adding Pin Constraints                |

| Rerunning the Comparison              |

| Exiting                               |

| Standard Dofile Example               |

|                                       |

## <u>F</u> <u>Top-level IO Port Modeling</u>...... 463

| <u>G</u>                       |     |

|--------------------------------|-----|

| Conformal Primitive Gate Types | 465 |

# **About This Manual**

The Encounter<sup>®</sup> Conformal<sup>®</sup> logical equivalence checking tools verify RTL, gate, or transistor-level designs. As part of the functional verification platform, Conformal gives you complete equivalence checking (EC) solution available for verifying complex system-on-a-chip (SoC) designs from RTL to layout.

Conformal includes the following solutions:

Conformal L

Conformal L has equivalency checking capabilities with functional checks for ASIC design flows.

Conformal XL

Conformal XL includes Conformal L and extends equivalency checking capabilities to datapath synthesis and layout.

Conformal GXL

Conformal XL includes Conformal XL and extends equivalency checking capabilities to digital custom logic and custom memories.

Conformal LowPower

Conformal LowPower enables low power equivalence and functional checks for isolation cells, level-shifter cells, and state retention cells.

## Audience

This manual is written for experienced designers of digital integrated circuits who must be familiar with RTL, synthesis, and design verification; as well as having a solid understanding of UNIX and Tcl/Tk programming.

## How This Manual Is Organized

The chapters in this manual are organized to follow the flow of tasks through the design process. Because of variations in design implementations and methodologies, the order of the chapters will not correspond to any specific design flow. Each chapter focuses on the concepts and tasks related to the particular design phase or topic being discussed.

In addition, the following sections provide prerequisite information for using the Conformal software:

■ Chapter 1, "Introduction to the Conformal Equivalence Checker"

Describes the process flow and the major components of the Conformal operation.

■ Chapter 2, "Getting Started"

Describes how to install, set up, and run the Conformal Equivalence Checker software, and use the online Help system.

## Conventions

## Syntax Structure

| Convention | Definition                                                                                                         |  |

|------------|--------------------------------------------------------------------------------------------------------------------|--|

| Bold Case  | Indicates the command name.                                                                                        |  |

| UPPERCASE  | Indicates the required minimum character entry.                                                                    |  |

| < >        | Indicates required arguments. Do not type the angle brackets.                                                      |  |

| [ ]        | Indicates optional arguments. Do not type the square brackets.                                                     |  |

|            | Indicates a choice among alternatives. Do not type the vertical bar.                                               |  |

| \          | The backslash character (\) at the end of a line shows that the command you are typing continues on the next line. |  |

| •••        | Indicates multiple entries of an argument.                                                                         |  |

| *          | Indicates that Conformal lets the wildcard (*) represent any zero or more characters.                              |  |

## **GUI Convention**

| Convention     | Definition                                                                                                 |

|----------------|------------------------------------------------------------------------------------------------------------|

| Menu – Command | Indicates command sequences under a menu. For example:<br>Choose <i>File – Read Design.</i>                |

| Left-click     | Click the left mouse button on the specified item.                                                         |

| Right-click    | Click the right mouse button on the specified item.                                                        |

| Click          | Click the left mouse button unless otherwise specified.                                                    |

| Double-Click   | Click twice on the left mouse button.                                                                      |

| Drag           | Press and hold the left mouse button, and then move the pointer to the destination and release the button. |

## **Additional Learning Resources**

Cadence offers the following training courses on Conformal:

- Custom Equivalence Checking with Conformal EC

- <u>Conformal ECO</u>

- Logic Equivalence Checking with Conformal EC

- Low-Power Verification with Conformal

1

# Introduction to the Conformal Equivalence Checker

- <u>Overview</u> on page 24

- <u>Conformal Features</u> on page 25

- <u>Supported File Formats</u> on page 26

- <u>Conformal Methodology</u> on page 27

- <u>Preparing the Designs</u> on page 28

- <u>Mapping and Comparing</u> on page 28

- Diagnosing on page 28

- <u>Conformal Operation</u> on page 28

- □ <u>System Modes</u> on page 29

- □ <u>Transition</u> on page 29

- □ <u>Mapping</u> on page 30

- □ <u>Comparison</u> on page 30

- Diagnosis on page 31

- <u>Overview of Conformal Tcl</u> on page 32

- □ <u>Conventions</u> on page 32

- Specifying the Command Entry Mode on page 33

- Using Native Conformal Commands on page 34

- Duplicate Commands on page 34

## Overview

The Conformal Equivalence Checking solutions are logical equivalence checking tools that verify RTL, gate, or transistor-level designs. As part of the Encounter<sup>®</sup> Conformal<sup>®</sup> functional verification platform, Conformal gives you the only complete equivalence checking (EC) solution available for verifying complex system-on-a-chip (SoC) designs from RTL to layout. It verifies the widest variety of circuits, including complex arithmetic logic, datapath, memories, and custom logic. Conformal has high-performance, high-capacity, and excellent debugging capabilities. These features are combined in an integrated environment.

Conformal Equivalence Checking solutions consist of three products:

Conformal L

EC capability with functional checks for ASIC design flow

Conformal XL

Extends EC capability to complex datapath synthesis and layout

Conformal GXL

Extends EC capability to digital custom logic and custom memories

Conformal supports standard library and design interface formats and integrates readily into existing design environments. The flexibility of these tools lets you efficiently impose constraints and apply guidance. Conformal is self-contained and is not tied to any particular synthesis environment. Thus, it gives you a higher degree of confidence than equivalence checkers integrated with a particular logic synthesis tool.

Conformal employs proprietary *key point mapping* and *formal functional comparison* algorithms that incorporate many innovative techniques for solving a wide range of problems. The comparison engine has superior performance and successfully completes verification of designs with differences.

Conformal also has excellent debugging capabilities. It automatically diagnoses design mis-matches and accurately pinpoints the source of the differences.

## **Conformal Features**

Conformal incorporates many features that streamline and authenticate the design process, while giving you flexibility.

■ Supports Full-Chip Verification

Conformal has excellent processing speed that significantly reduces verification time for high-capacity, high-complexity, full-chip designs.

■ Supports Multiple Design Formats

Conformal supports Verilog<sup>®</sup>, VHDL, SPICE, EDIF, and NDL design formats.

- Supports Standard Library Formats Conformal supports Verilog simulation libraries and the Synopsys<sup>®</sup> Liberty<sup>TM</sup> Format Libraries.

- Employs Verilog/VHDL-RTL and Transistor Function Abstraction

Conformal has a built-in Verilog/VHDL-RTL and transistor function abstraction engine that lets you verify Verilog/VHDL-RTL, gate, or transistor level designs.

Employs Advanced, Automatic Mapping

Conformal contains advanced and proprietary sequential element mapping algorithms that identify corresponding sequential elements automatically with minimal user resources. This feature relieves you of the tedious job of specifying corresponding flip-flops and latches.

■ Employs an Efficient and Effective Comparison Engine

Conformal has a superior formal comparison engine to ensure successful verification of non-similar designs with different hierarchical structures. Conformal contains a unique correlation learning technology that effectively explores both structural and functional relationships of the logic in two designs and dramatically reduces the verification run time. This technology does not require high memory use and is very effective for both similar and dissimilar designs.

■ Includes Automatic Diagnosis

When a logic mismatch is found, designers find that it is absolutely essential to be able to quickly locate the source of functional differences. Conformal automatically diagnoses functional differences, narrowing them to a small number of possible locations in the design. This feature helps you identify and effectively correct problems and reduce debugging time.

■ Includes Integrated Debugging

Conformal has extensive gate reporting integrated with the schematic viewer. This feature gives you flexibility and immediate feedback for debugging and diagnosis.

## **Supported File Formats**

The following table lists the file formats and versions that the Conformal software supports, and the related commands that parse these files.

| VHDL          | IEEE Std 1076-1993 (default)<br>IEEE Std 1076-1987 | READ DESIGN -vhdl<br>READ LIBRARY -vhdl                   |

|---------------|----------------------------------------------------|-----------------------------------------------------------|

| Verilog       | IEEE 1364-1995 (default)<br>IEEE 1364-2001         | READ DESIGN -verilog<br>READ LIBRARY -verilog             |

| SystemVerilog | IEEE 1800-2009                                     | READ DESIGN -systemverilog<br>READ LIBRARY -systemverilog |

| Liberty       | 2007.3                                             | READ DESIGN -liberty<br>READ LIBRARY -liberty             |

| CPF           | 1.0, 1.0e, 1.1 and 2.0                             | READ POWER INTENT                                         |

## **Conformal Methodology**

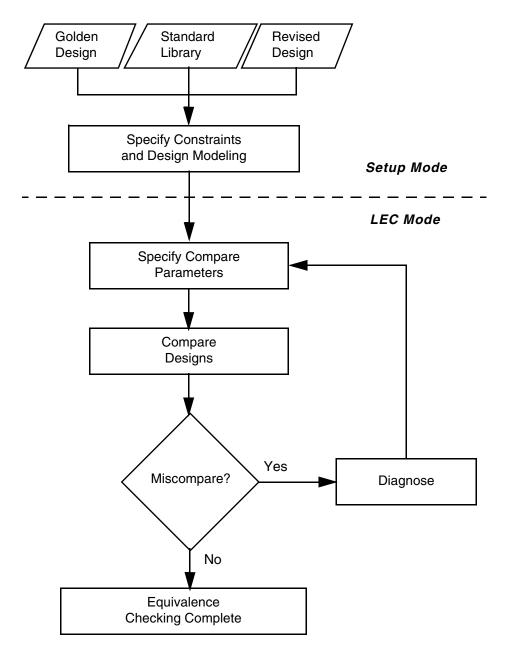

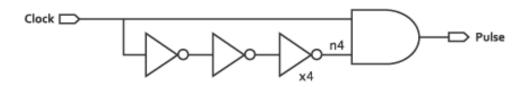

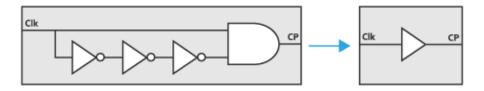

The following flowchart illustrates the Conformal process flow.

### **Preparing the Designs**

During the first phase of equivalence checking, Conformal reads in the Golden and Revised designs and their associated libraries. The designs can be any of the following formats:

- Verilog

- VHDL

- EDIF

- NDL

- SPICE

Conformal supports Verilog simulation libraries and Synopsys Liberty libraries.

After reading in designs and libraries, you can tailor the session to your particular needs by specifying constraints and parameters. When all of these Setup mode tasks are complete, you can change to LEC mode and the next session phase.

#### Mapping and Comparing

During the second and third phases of equivalence checking, Conformal automatically maps key points and compares them. When the comparison is complete, Conformal pinpoints the differences.

## Diagnosing

During the final phase of the Conformal process flow, you can employ a combination of the integrated diagnosis tools to examine differences. These tools include the Schematic Viewer and Source Code Manager. After you have remedied the differences, a new verification session begins.

## **Conformal Operation**

This section details the Conformal integrated debugging environment, describing each of the major components of the Conformal operation.

#### System Modes

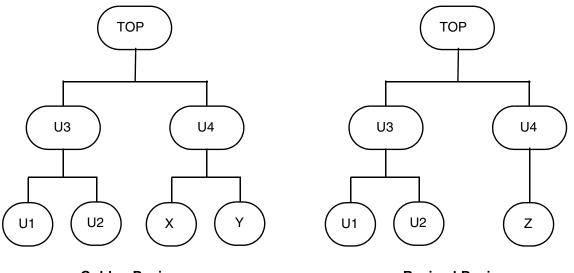

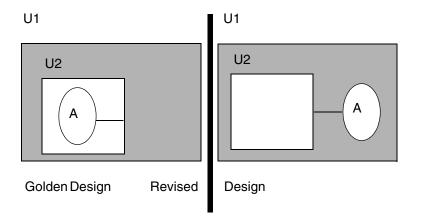

Conformal operates in two system modes: *Setup* and *LEC*. In the Setup mode, Conformal reads two designs. You designate the design types, which are Golden and Revised. (Generally, the Revised design is a modified or post-processed design that Conformal compares to the Golden design.) Additionally, you apply constraints and design settings in the Setup mode. Finally, you can specify Conformal compare options and mapping methods. When you have set all design conditions, you can move to the LEC system mode.

## Transition

The following two sections relate to events that occur as Conformal transitions from the Setup to the LEC mode.

#### Rule Checking

Conformal checks various rules during parsing. You can specify how Conformal will respond to rule violations before you read in the designs and libraries. Additionally, you can choose to view a report displaying all of the library and design rule violations that occurred during parsing.

For additional information about rule checking, see the *Conformal HDL Rule Check Reference*.

#### **Key Points**

In the transition from the Setup to the LEC system mode, Conformal flattens and models the Golden and Revised designs and automatically maps the key points. Key points are defined as:

- Primary Inputs

- Primary Outputs

- D Flip-Flops

- D Latches

- TIE-E Gates (error gate, created when x-assignment exists in Revised design)

- TIE-Z Gates (high impedance or floating signals)

- Blackboxes

■ Cut Gates (artificial gates that break combinational loops)

### Mapping

Conformal employs three name-based methods to map key points and one no-name method. Name-based mapping is useful for gate-to-gate comparisons when small changes have been made to the logic. Conversely, the no-name-mapping method is useful when Conformal must map designs with completely different names. By default, Conformal automatically maps key points with the name-first mapping method when it exits the Setup mode. Any key points that Conformal does not map are classified as unmapped points.

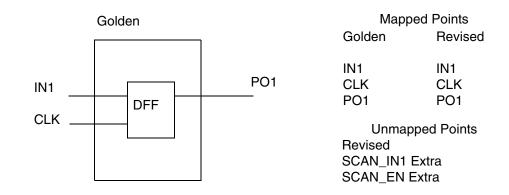

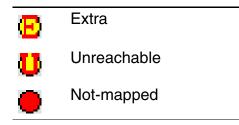

#### **Unmapped Points**

After Conformal maps key points, the remaining unmapped points are classified into one of three categories: extra, unreachable, or not-mapped.

- Extra unmapped points are key points that are present in only one of the designs, Golden or Revised.

- Unreachable unmapped points are key points that do not have an observable point, such as a primary output.

- Not-mapped unmapped key points are key points that are reachable but do not have a corresponding point in the logic fan-in cone of the corresponding design.

#### Comparison

After Conformal maps the key points, the next step of the verification is comparison.

#### **Compare Points**

You can designate mapped points for comparison. Comparison examines these compare points to determine if they are equivalent or non-equivalent.

#### Run Time and Performance

The comparison determines if the compared points are:

- Equivalent

- Non-equivalent

- Inverted-equivalent

- Aborted

In the case of aborted compare points, you can change the compare effort to a higher setting. Thus, Conformal can continue the comparison on only the aborted compare points. Conformal can also display the complete run time and total memory use for the comparison.

#### Reports

When Conformal completes the comparison, you can get summary reports showing which key points are equivalent and which are non-equivalent. Then, you can diagnose non-equivalent points to determine the cause of the difference.

#### Diagnosis

Diagnosis is the process of examining non-equivalent points and identifying the most likely error candidates. In this phase of verification, examine non-equivalent points using the integrated tools as described below.

#### **Error Patterns and Candidates**

The Conformal diagnosis feature precisely locates the cause of a non-equivalent point. During this process, Conformal displays the error patterns that caused the difference and lists the possible candidates. Included in this list is the percent of probability, which is shown in decimal form. The most likely candidate is 1.00.

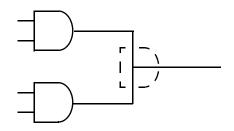

#### Gate Reporting

With the above diagnosis information gathered, you are ready to employ gate reporting to trace the fan-in or fan-out cone of the non equivalent point. Additionally, you can view a schematic representation of the non-equivalent point.

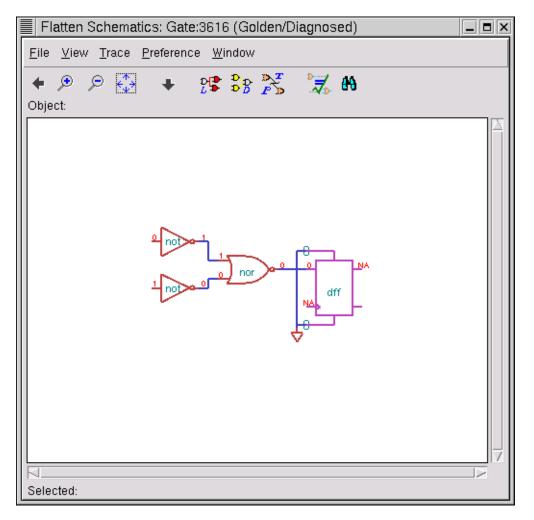

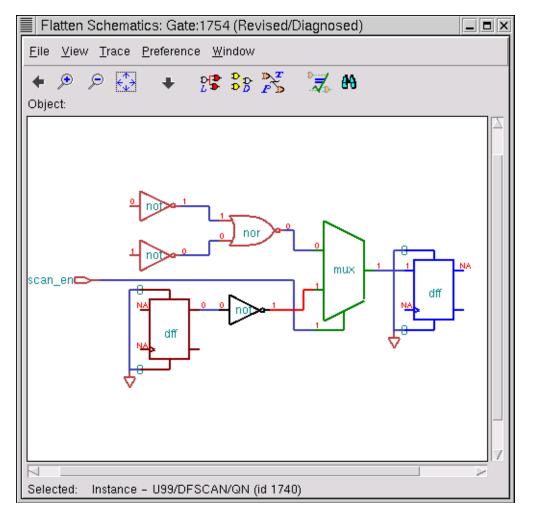

#### **Schematic Viewing**

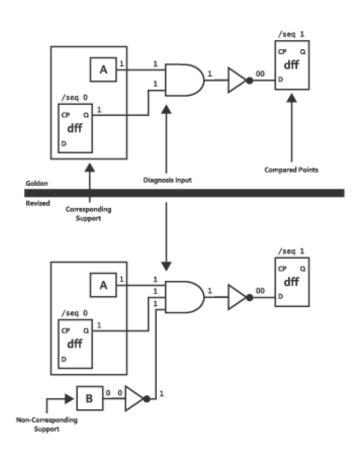

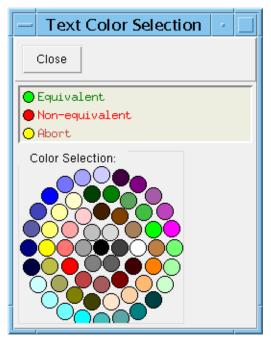

When you view the schematic representation of the non-equivalent point, the viewer displays the fan-in cone with the corresponding and non-corresponding supporting key points and their simulation values. The non-equivalent compared point, diagnosis input point, supporting key points, and error candidates are all color-coded for visual accessibility. The schematic

viewer displays the Golden and Revised schematic representations side-by-side in separate windows, for quick comparison.

#### Source Code Viewing

To further diagnose non-equivalent points, you can access the Source Code Browser. This tool lets you specify a gate in the Revised or Golden design and view its relative location in the source code.

## **Overview of Conformal Tcl**

Conformal supports two types of Tool Command Language (Tcl) commands: native Tcl commands and Conformal Tcl commands that have been tailored for use with Conformal to query the design database. Information retrieved from the design database is referenced by pointers (which are also called object handles in Tcl).

For a complete description of the Tcl design access commands and the Tcl Utility commands, see the <u>Tcl Command Entry Mode Support</u> chapter of the *Conformal Equivalence Checking Reference Manual*. Each section includes the syntax for individual commands, definitions for the applicable arguments, command examples, and what Conformal returns.

The focus of the chapter is Conformal Tcl commands. Therefore, if you want to learn more about *native* Tcl commands, refer to the public Tcl manual widely available online. To see a list of supported Tcl commands, enter a question mark (?) at the Tcl prompt.

Note: This has no effect when Conformal is in the default command entry mode.

As you work with the Tcl commands, you will find that some of the commands invalidate the object handles you saved in Tcl variables. For example, when you change the design with set root module, every object handle is invalidated. When an object handle is invalidated, yet still referred to by a Tcl variable, the memory is not free until you reassign the Tcl variable to another value.

By its very nature, the Tcl command interface is not as efficient as internal C functions. Therefore, you will encounter some performance penalties when you access large amounts of information using Tcl commands. For example, most of the get commands return a TCL LIST, thus costing memory and speed.

#### Conventions

Conventions used in the Conformal Tcl command documentation differ somewhat from those used in the remainder of the manual. For example, Conformal Tcl commands are case-

sensitive (you must type them in lowercase). Therefore, as a reminder, they appear in lowercase.

- commands Tcl commands appear in the text and in examples in lowercase with a Courier font. And since Conformal Tcl commands are case-sensitive, you must type them in lowercase. (However, options are not case-sensitive.) Default options are noted.

- Hierarchical context (/)

If a name begins with a slash (/), Conformal considers the name in a hierarchical context.

For example: /U02/U199

- Module context Module context operations always work on the current module. For example, find -net zero refers to a net named zero that is in the current module.

- Pin object\_type

Pin object\_types appear in the format instance\_name/pin\_name. For example:

- Pin object\_type in module context:

A pin named data on instance U01 of the current module is specified as U01/data.

- Pin object\_type in hierarchical context: In hierarchical context, the string is preceded by a slash. Thus, the pin is specified as /U01/data.

- Wildcards: (\*) and (?) Conformal supports the wildcard \* or ? in an object\_name, but only at the bottom hierarchical level:

find -net /d\*

Return examples are: /d1 and /d0

## Specifying the Command Entry Mode

In Conformal, there are two modes: the default Conformal command entry mode (VPXMODE) and the Tcl command entry mode (TCLMODE). Use the TCLMODE command to switch Conformal to the Tcl command entry mode.

To change to Tcl command entry mode, run the following command:

tclmode

To return to the default Conformal command entry mode, run the following command:

vpxmode

#### **Using Native Conformal Commands**

When Conformal is in Tcl command entry mode, typically you will run native Tcl and Conformal Tcl commands. However, you can also run native Conformal commands as shown in the examples below.

To run native Conformal commands:

■ Example one: Preface the native Conformal command with the vpx keyword.

vpx read design counter.v

Partial entry matching is allowed:

vpx rea de counter.v

Example two: Use an underscore for spaces in commands. With this feature, type the entire command; Conformal does not permit partial entry matching for native Conformal commands in Tcl command entry mode unless you preface the command with the vpx keyword (as shown in Example one, above).

read\_design counter.v

To get quick help for native Conformal command names:

#### To Get Quick Help for Native Conformal Command Names

If you type a native Conformal command incorrectly using the underscore method in Example two (above), Conformal echos commands with common prefixes. For example, type:

add\_in

#### Conformal returns:

```

ambiguous command name "add_in": add_instance_attribute add_instance_constraints

add_instance_equivalences

```

#### **Duplicate Commands**

The following native Tcl commands are also defined as native Conformal commands:

break continue exit

## Important

The behaviors of these commands are not the same in Tcl command entry mode as they are in Conformal command entry mode. Use these commands with caution.

Refer to the *Conformal Equivalence Checking Reference Manual* for detailed descriptions of the native Conformal commands.

## **Tcl Version**

To determine the current version of Tcl used by Conformal:

```

SETUP> tclmode

TCL_SETUP> puts $tcl_version

8.5

or

TCL_SETUP> info tclversion

8.5

```

To get more detailed patch level information, one can use

TCL\_SETUP> info patchlevel 8.5.2

To know from where the tcl script is being used from, one can do:

```

TCL_SETUP> info library

<cadence lec installation>/share/cfm/lec/tcl8.5

```

# **Getting Started**

- Product and Installation Information on page 38

- <u>Start-Up Command Options</u> on page 38

- Initial Command Files on page 40

- Dofile Command Files on page 41

- <u>Saving and Restoring a Session</u> on page 45

- <u>Checkpoint and Restart Facility</u> on page 45

- <u>Setting Preferences</u> on page 50

- Accessing Online Help and Documentation on page 52

- Platform Integration on page 55

# **Product and Installation Information**

For product, release, and installation information, see the README file at any of the following locations:

- <u>downloads.cadence.com</u>, where you can review the README before you download the Conformal software.

- In the software installation, where it is also available when you are using or running the Encounter<sup>®</sup> Conformal<sup>®</sup> software.

- At the top level of your installation hierarchy.

# **Start-Up Command Options**

The following lists the licensing options for the lec command when starting the Encounter<sup>®</sup> Conformal<sup>®</sup> software. For example, if you have an XL or GXL license, you must specify this at startup with the -xl or -gxl option. For example, to start the Conformal software with the XL license in GUI mode, you would enter the following at the UNIX prompt:

UNIX% lec -xl

Without the -x1 or -gx1 option, the Conformal software starts with the default L license.

Once you start your session, you can use the LICENSE command to display the current license status in the transcript output.

| -L        | Launches the Encounter <sup>®</sup> Conformal <sup>®</sup> Equivalence Checker                                                                           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Note: This is the default when running the $\verb+lec$ command with no options.                                                                          |

| -RCV      | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with an RTL-Compiler verification license                                                      |

| -XL       | Launches Encounter $^{\ensuremath{\mathbb{R}}}$ Conformal $^{\ensuremath{\mathbb{R}}}$ L with Datapath and advanced equivalence checking capabilities    |

| -GXL      | Launches Encounter $^{\ensuremath{\mathbb{R}}}$ Conformal $^{\ensuremath{\mathbb{R}}}$ XL with digital custom logic and memory verification capabilities |

| -ECO      | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with ECO                                                                                       |

| -ECOGXL   | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with ECO GXL capabilities (physical design awareness)                                          |

| -LP/-LPXL | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with Low Power Verification                                                                    |

#### Conformal Equivalence Checking User Guide Getting Started

| -CCD    | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> L with a Conformal Constraint<br>Designer L license                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| -CCDXL  | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with a Conformal Constraint<br>Designer XL license                                       |

| -LPGXL  | Launches Encounter <sup>®</sup> Conformal <sup>®</sup> XL with digital custom logic, memory verification, and low power verification capabilities. |

| -VERIFY | Encounter <sup>®</sup> Conformal <sup>®</sup> Extended Checks                                                                                      |

The lec command has the following additional options. This list is also available using the lec -help command *before* you start your session.

| -Dofile <filename></filename>                                                                   | Runs the script <filename> after starting LEC.<br/>See <u>"Dofile Command Files"</u> on page 41 for more<br/>information.</filename>                                                     |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -LOGfile <filename></filename>                                                                  | Sets up a log filed called <filename>.</filename>                                                                                                                                        |

| -RESTART_checkpoint <filenam< td=""><td>ne&gt; [-protect <password>]</password></td></filenam<> | ne> [-protect <password>]</password>                                                                                                                                                     |

|                                                                                                 | Restarts a session that was saved using the CHECKPOINT command.                                                                                                                          |

| -INFO_CHECKpoint <filename></filename>                                                          |                                                                                                                                                                                          |

|                                                                                                 | Information of the checkpoint <filename></filename>                                                                                                                                      |

| -Gui   -NOGui                                                                                   | Starts the session in GUI or non-GUI mode.                                                                                                                                               |

| -TclMode                                                                                        | After the session starts, the tool enters Tcl mode.                                                                                                                                      |

| -NOColor   -Color                                                                               | Controls color-coded messaging when in non-GUI mode. By default, color-coding is off.                                                                                                    |

| -DEFault [init_filename]   -                                                                    | -NODEFault]                                                                                                                                                                              |

|                                                                                                 | Specifies whether to process the initial command file (init_filename or .conformal_lec) by default during startup. For more information, see <u>"Initial Command Files</u> " on page 40. |

| -Banner   -NOBanner                                                                             | Specifies whether to display the LEC banner during startup.                                                                                                                              |

| -RESETrc                                                                                        | Reset GUI default settings.                                                                                                                                                              |

| -NOLIcwait                                                                                      | If all licenses are checked out, exit immediately.                                                                                                                                       |

| -Info    | Display the product information and exit.                                                                                                                                                                                                                                                                                  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -Version | Displays the product version. Once you have started<br>your session, you can also use the VERSION<br>command to display the Conformal software version<br>number. This is useful when starting a transcript log<br>file to ensure that the file contains a reference to the<br>Conformal version that created the results. |

### **Initial Command Files**

When you start the Conformal software, it searches for and executes initial command files (.conformal\_lec). The software checks for the <code>CONFORMAL\_RC</code> environment variable. If this variable is set, Conformal uses the file this variable refers to and does not search for other files.

If the CONFORMAL\_RC variable is not set, the software continues the search as follows:

- 1. The installation directory

- 2. The home directory

- 3. The current working directory

**Note:** The software does not include .conformal\_lec in the release.

If one or more of these files exist, the software runs them in the order noted above. This search order gives you flexibility in using the initial command file. You can set up initial command files for any or all of the following purposes:

- Global initial command file for all users

- Global initial command file for an individual user

- Initial command file for a test case

The file contents vary according to your needs; for example, they can include commands, aliases, and dofiles. You can use this file for any purpose at the system, user, and local levels.

### Important

Do not use an initialization file to run a complete batch file. Use dofiles, as explained in the following section, for this purpose.

### **Dofile Command Files**

The Conformal Equivalence Checker command files (other than initial command files) are called dofiles. As you execute commands in GUI mode using the drop-down menus and windows, the Conformal software displays the text for the corresponding commands in the Transcript window, which is located in the lower portion of the main window.

Execute dofiles during startup or with the DOFILE command. When you create a dofile, follow these guidelines:

- Each new command must begin on a new line.

- Two or three slashes (// or ///) precede comments.

For more information, see Comments in Dofiles on page 44.

Dofiles can execute additional dofiles.

You can use the DOFILE command (or the -dofile command option at startup) to read in and execute a command file that includes any set of commands.

#### Using a Dofile at Startup

In GUI mode, the -dofile option is useful for running a set of commands that set up your environment and advance to a specific point in the verification session. The following example command substitutes your dofile name for  $my_dofile$ :

UNIX% lec -dofile my\_dofile

In non-GUI mode, you can use the -dofile option for running batched sets of commands. The following example command substitutes your dofile name for  $my_dofile$ :

UNIX% lec -nogui -dofile my\_dofile

#### Saving a Dofile

To save the commands entered during a current session that you can use later as a batch file to repeat the session, use the SAVE DOFILE command, or the Save Dofile form in GUI mode (*File – Do Dofile*).

When running a session from a dofile, this command does not save individual commands that might have been included in a separate dofile (that is, it saves the manually entered commands, which might include a dofile <filename> command).

Use the Save Dofile form to save commands to a dofile to be used later as a batch file to repeat the Conformal Equivalence Checker session.

| _         | — Save Dofile 🛛 🗌    |        |  |  |

|-----------|----------------------|--------|--|--|

| ок        | Cancel               |        |  |  |

| Filename  | dofile.do            | Browse |  |  |

| Open Mode | 🔶 Replace 🛭 🕹 Append |        |  |  |

#### Save Dofile Fields and Options

| Filename  | Specifies the name of the dofile. You can enter the path of the dofile or click <i>Browse</i> and select a location from the Save Dofile browser window.            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open Mode | Overwrites or appends to the dofile. <i>Replace</i> overwrites the contents of an existing dofile, and <i>Append</i> appends to the contents of an existing dofile. |

#### **Executing Commands in a File**

At any time during a session, execute commands in a batch mode using the DOFILE command or the Do Dofile form in GUI mode (*File – Do Dofile*). By default, the dofile aborts at any command that generates an error message.

Use the Do Dofile form to execute a batch file of commands, or run a set of commands from a previous session.

| — Do Dofile                                                                                                                           | •                |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Directories:                                                                                                                          | Select<br>Cancel |

| <pre>bome     jeffl     design     testcase         demo_cpu         feedback conste         verifyLP         verplex_demo_lit </pre> |                  |

| List Files of Type:                                                                                                                   |                  |

#### Do Dofile Fields and Options

DirectoriesDouble-click the file folders to expand the directories and<br/>view the dofile names in the Files list.FilesShows the available files. Use the List Files of Type<br/>pull-down menu at the bottom of the form to filter file<br/>display. You choose All files, Dofiles, or Command<br/>files.

#### Interrupting a Dofile

Within a dofile, use the BREAK command to interrupt a dofile and return to the current system mode.

#### Resuming Running a Dofile

When a dofile executes the BREAK command, the Conformal software issues a warning and prompts you to use the CONTINUE command to resume running the dofile:

//Warning: Break dofile `my\_dofile' at line 32. Use `continue' command to continue.

#### **Specifying Error Handling**

Use the SET DOFILE ABORT command in a dofile to specify how the Conformal software responds to errors it encounters:

■ set dofile abort on

Aborts the dofile and generate a message.

■ set dofile abort off

Continues with the dofile and generate a message.

set dofile abort exit

Exits the session.

#### **Comments in Dofiles**

The Conformal software provides two types of comments in a dofile:

1. Two slashes (//) comments out the rest of command. // must have space before it if you add it to the middle of the text.

In this example, the following command lines are commented out:

In this example, the read library command is run for lib01.lib through lib\_03.lib, commenting out lib04.lib through lib\_06.lib, and not specifying the *-*liberty and *-*both options:

2. Three slashes (///) comments out the rest of the line. /// must have a space before it if you add it to the middle of the text.

In this example, the first line only runs the read library command, commenting out <code>lib\_01.lib</code> and <code>lib\_02.lib</code>, and including <code>lib03.lib</code> through <code>lib\_06.lib</code>, and specifying the <code>-liberty</code> and <code>-both</code> options:

```

read library ///../library/lib_01.lib ../library/lib_02.lib \

```

```

../library/lib_03.lib ../library/lib_04.lib \

../library/lib_05.lib ../library/lib_06.lib \

-liberty -both

```

### Saving and Restoring a Session

In the current release, there are two ways to save a session:

- <u>Save and Restore Commands</u> on page 45

- <u>Checkpoint and Restart Facility</u> on page 45

### Save and Restore Commands

Use the SAVE SESSION command, or the Save Session form (*File – Save Session*), to save session up to a current point in binary format, which can be restored later. You can use this if priorities demand that another session preempt your session

Use the RESTORE SESSION command, or the Restore Session form (*File – Restore Session*), to restore a session you previously initiated and saved. Before using this procedure, Conformal must be in its initial state. Therefore, you must either reset the system to the initial state with the RESET command or *Reset Design* menu option (*File – Reset Design*), or exit and restart the Conformal software.

*Limitation*: When you use the *Restore Session* menu option, you must restore the session on the same platform and with the same Conformal version.

### **Checkpoint and Restart Facility**

The checkpoint and restart facility saves all the data from a session (CHECKPOINT command) as a *checkpoint* such that it can be restarted at a later time (<start\_up\_command> -restart\_checkpoint <*checkpoint\_file\_name>* [-protect <*password>*] [-force]).

Note: The GUI mode will be disabled when you restart the checkpoint process.

| Applicable | CHECKPOINT                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| commands   | INFO CHECKPOINT                                                                                                                                       |

|            | <start_up_command> -restart_checkpoint <checkpoint_file_name><br/>[-protect <password>] [-force]</password></checkpoint_file_name></start_up_command> |

**Getting Started**

| Data preserved        | When you save your session as a checkpoint, the tool preserves the: |  |  |

|-----------------------|---------------------------------------------------------------------|--|--|

|                       | <ul> <li>Hierarchical and flattened databases</li> </ul>            |  |  |

|                       | Environment settings                                                |  |  |

|                       | ■ Constraints                                                       |  |  |

|                       | Verification results                                                |  |  |

|                       | User-defined variables                                              |  |  |

|                       | User-defined procedures                                             |  |  |

| Supported<br>Platform | Linux                                                               |  |  |

#### Limitations:

This feature has the following limitations:

■ If you are creating a checkpoint file that you plan to restart using a different license server, add the restart license server to the LM\_LICENSE\_FILE variable before invoking Conformal and *before* creating the checkpoint file; otherwise, you will not be able to restart the checkpoint file with the new server. For example:

setenv LM\_LICENSE\_FILE "\$LM\_LICENSE\_FILE":5280@mylic01

- Do not enter the GUI mode if you plan to create a checkpoint file that you will want to run later in the GUI mode. If a checkpoint file is created after having entered GUI mode, when the checkpoint file is restarted, it will restart and run in non-GUI mode and the GUI mode is disabled. If a checkpoint file is created before entering the GUI mode, the checkpoint file can enter the GUI mode when it is restarted.

- Checkpoint and restarts works on only the following Linux platforms: 32/64-bit Linux kernel versions 2.6.9-34, 2.6.9-42, 2.6.9-67, 2.6.9-78, 2.6.9-89, 2.6.10, 2.6.14, 2.6.16, 2.6.18, 2.6.25, 2.6.26 and 2.6.27

- You cannot specify the stack limit in a restarted tool process. You can, however, specify the stack limit when you save the checkpoint:

CHECKPOINT -stack <multiplier>

Default multiplier is 1 (in other words, 64MB).

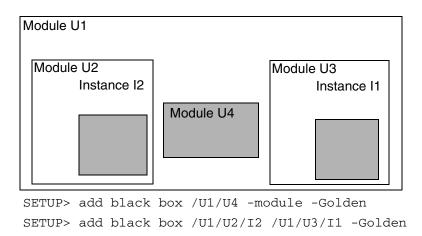

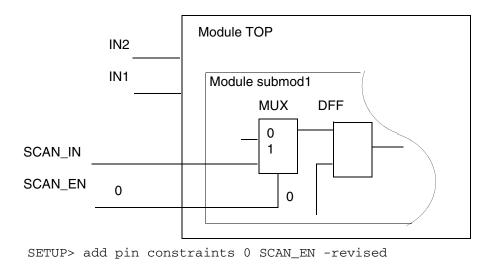

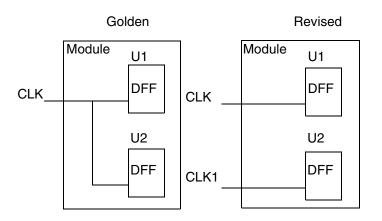

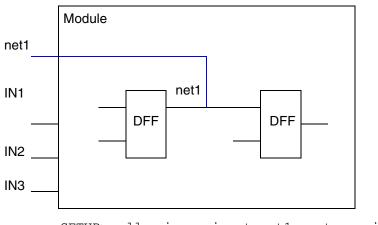

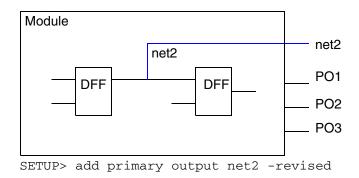

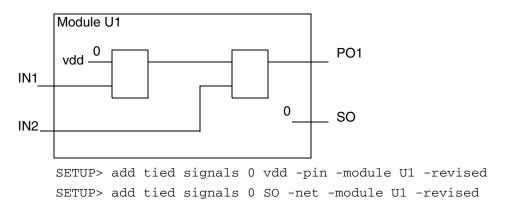

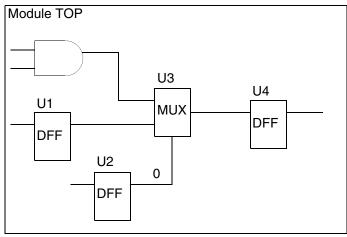

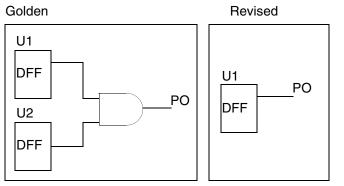

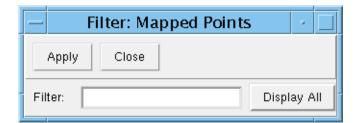

### Transcript Messages