# SpyGlass<sup>®</sup> MBIST Submethodology (for GuideWare 2017.12)

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

© 2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

#### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

#### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

# Contents

| Preface                                                           | 9          |

|-------------------------------------------------------------------|------------|

| About This Book                                                   |            |

| Contents of This Book                                             |            |

| Typographical Conventions                                         |            |

| Typographical conventions                                         |            |

| The Need for Automatic Incertion of MDIST at an Early (           | Staga of a |

| The Need for Automatic Insertion of MBIST at an Early S<br>Design | 13         |

| Overview                                                          |            |

| Who this Document is for                                          |            |

| What You Need to have and know to Use this Document               |            |

| What this Document is About                                       |            |

| Tool Versions                                                     |            |

| References                                                        |            |

| MBIST Overview                                                    |            |

| Generic MBIST Components                                          |            |

| Restrictions Imposed by the Technology                            |            |

| Final View                                                        |            |

| Vendor Data and User Data                                         |            |

| Approach for Inserting MBIST into a Design                        | 20         |

| Overview                                                          |            |

| Stages during SpyGlass DFT MBIST Insertion                        |            |

| Creating a Vendor File                                            |            |

| Defining Classes                                                  |            |

| Specifying Connections                                            |            |

| Disconnecting Existing Connections                                |            |

| Specifying Chain Connections                                      |            |

| Combining Signals through Gates                                   |            |

| Collecting Design Data and Preparing for MBIST Run                |            |

| Creating a User Data File                                         |            |

| Preparing the Setup                                               |            |

| Defining the Existing Instances                                   |            |

| Inserting/Replacing and Defining New Instances                    |            |

| Removing the Existing Instances                                   |            |

| Establishing Custom Connections                                   |            |

| Inserting MBIST                                                 | 38   |

|-----------------------------------------------------------------|------|

| Specifying the Location of Modified Design Files                | 39   |

| Verifying the Post-BIST Design                                  | 39   |

| Viewing the Modified Design                                     | 39   |

| Verifying the AND/OR/EXOR Logic Tree                            | 39   |

| Steps for Inserting MBIST into a Design                         | . 41 |

| Creating a Vendor File                                          |      |

| Defining Classes                                                | 41   |

| Specifying Connections                                          |      |

| Disconnecting Existing Connections                              |      |

| Specifying Chain Connections                                    | 50   |

| Combining Signals through Gates                                 |      |

| Collecting Design Data and Preparing for MBIST Run              | 52   |

| mb_report_instances                                             | 52   |

| mb_report_instances -group_by_hierarchy                         | 54   |

| mb_report_instances -dive_in                                    |      |

| Creating a User Data File                                       | 58   |

| Preparing the Setup                                             |      |

| Defining the Existing Instances                                 |      |

| Inserting/Replacing and Defining New Instances                  |      |

| Removing the Existing Instances                                 |      |

| Establishing Custom Connections                                 |      |

| Inserting MBIST: The mb_insert Tcl Command                      |      |

| Specifying the Location of Modified Design Files                |      |

| Verifying the Post-BIST Design                                  |      |

| Viewing the Modified Design                                     |      |

| Verifying the AND/OR/EXOR Logic Tree                            |      |

| Verifying the Connectivity of Critical Paths                    |      |

| Verifying the Connectivity of Critical Nodes to Ground or Power |      |

| Summary: Usage of the mb_assert* Commands                       |      |

| Bottom-up Methodology                                           | 80   |

| The Bottom-up Flow                                              |      |

| Design Read for Bottom-up Flow                                  |      |

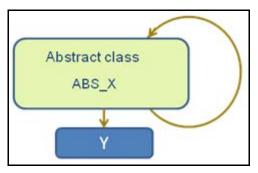

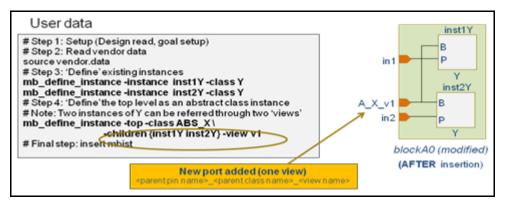

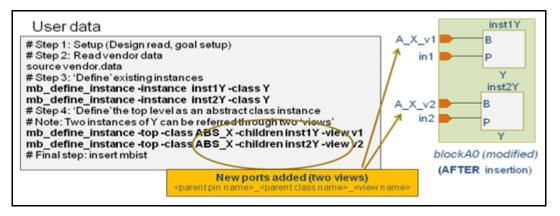

| Abstract Classes                                                |      |

| More on Abstract Classes                                        |      |

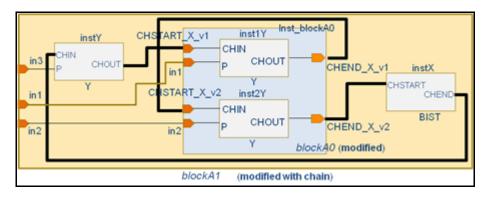

| Introducing Views                                               |      |

| Abstract Classes with auto_configure                            |      |

| Implication of a View as Defined for an Abstract Class Object   | 94   |

| Shell Creation during Bottom-up Flow                            |      |

| Working with Gate-Level Designs for MBIST Insertion             | 102  |

| TIPs and FAQs                                                                             | 103               |

|-------------------------------------------------------------------------------------------|-------------------|

| Appendix A: Guidelines of Using Braces in Tcl Files Specifi<br>SpyGlass DFT MBIST Product | ied to the<br>119 |

| Key Points of Consideration                                                               | 120               |

| Guideline for Options Accepting a Single Value                                            |                   |

| Guideline for Options Accepting Multiple Values                                           |                   |

| Guideline for Options Accepting regexp and a Single Value                                 |                   |

| Guideline for Options Accepting regexp and Multiple Values                                |                   |

| Tcl Commands in the SpyGlass DFT MBIST Product                                            | 122               |

|                                                                                           |                   |

| Appendix B: An Example of Using Waivers                                                   | 125               |

| Appendix C: Working with Generated Names                                                  | 127               |

| Naming Conventions Used for the Generate Blocks                                           | 127               |

| A Complete Example                                                                        |                   |

| • •                                                                                       |                   |

| Appendix D: An Example of Shell View Created during Bo<br>Flow                            |                   |

# **About This Book**

The SpyGlass  $\ensuremath{\mathbb{B}}$  MBIST methodology guide describes the flow for using the MBIST methodology.

# **Contents of This Book**

The SpyGlass MBIST methodology guide has the following sections:

| Section                                                                       | Description                                                             |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| The Need for Automatic Insertion<br>of MBIST at an Early Stage of a<br>Design | The need for automatic insertion of MBIST at an early stage of a design |

# **Typographical Conventions**

This document uses the following typographical conventions:

| To indicate                              | Convention Used                                                   |

|------------------------------------------|-------------------------------------------------------------------|

| Program code                             | OUT <= IN;                                                        |

| Object names                             | OUT                                                               |

| Variables representing objects names     | <sig-name></sig-name>                                             |

| Message                                  | Active low signal name ' <sig-name>' must end with _X.</sig-name> |

| Message location                         | OUT <= IN;                                                        |

| Reworked example<br>with message removed | OUT_X <= IN;                                                      |

| Important Information                    | NOTE: This rule                                                   |

The following table describes the syntax used in this document:

| Syntax                | Description                                           |

|-----------------------|-------------------------------------------------------|

| [ ] (Square brackets) | An optional entry                                     |

| { } (Curly braces)    | An entry that can be specified once or multiple times |

| (Vertical bar)        | A list of choices out of which you can choose one     |

| (Horizontal ellipsis) | Other options that you can specify                    |

# The Need for Automatic Insertion of MBIST at an Early Stage of a Design

### **Overview**

The SpyGlass DFT MBIST product automates the insertion of Memory Built-In Self-Test (MBIST) IP into a design at the RTL level. The product also works at the gate level; however, working at the RTL level has many advantages that are crucial in leading-edge SoC designs.

Inserting MBIST at the RTL level reduces the cost of functional verification of the BIST structures. In addition, the synthesis optimization/early floor planning considers the MBIST logic, resulting in much more predictable quality of results and reduced iterations between the RTL-level and gatelevel implementations.

### Who this Document is for

The document is useful for both novice and advanced users of SpyGlass.

### What You Need to have and know to Use this Document

You are expected to have basic knowledge of SpyGlass operations.

The SpyGlass DFT MBIST product requires a clean design into SpyGlass. Please refer to the *SpyGlass Design Read Methodology* document for details. The flow is based on Tcl environment available for SpyGlass operations and therefore the user is referred to the *SpyGlass Tcl Shell Interface User Guide* for more details. The user is also referred to the *SpyGlass DFT MBIST Tcl Flow Reference Guide* for the details of MBIST specific commands.

### What this Document is About

This document introduces a method to run the SpyGlass DFT MBIST product.

### **Tool Versions**

- SpyGlass Version: Version N-2017.12-SP2

- SpyGlass DFT MBIST Version: Version N-2017.12-SP2

- GuideWare: 2017.12

#### References

- SpyGlass Explorer User Guide

- SpyGlass Explorer Reference Guide

- SpyGlass Tcl Shell Interface User Guide

- SpyGlass Design Read-In Methodology

- SpyGlass GuideWare Reference Methodology User Guide

- SpyGlass MBIST Tcl Flow Reference Guide

## **MBIST Overview**

This section describes the basic goals for the MBIST insertion process, various generic components, and restrictions imposed by the technology.

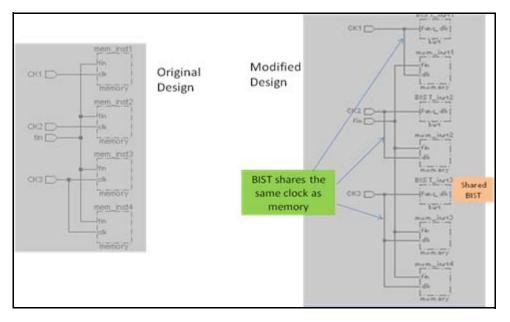

### **Generic MBIST Components**

The SpyGlass DFT MBIST product is designed to work with various BIST components, some of which are as follows:

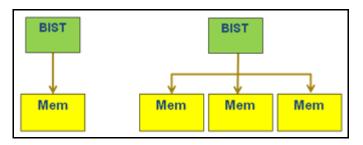

BIST Engines: BIST engines are hardware components that generate patterns to apply to the memories. They can be either dedicated to a memory or assigned to serve multiple memories.

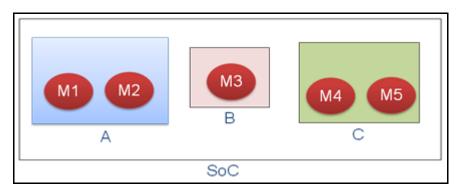

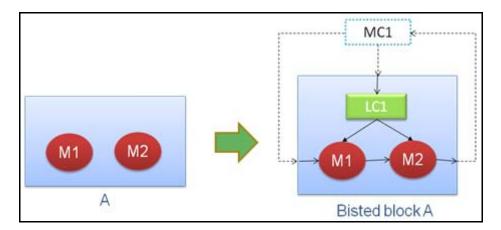

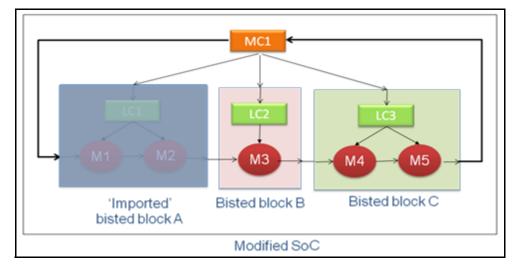

FIGURE 1. BIST Engines

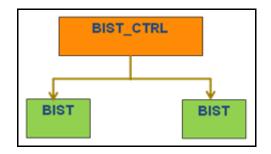

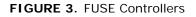

BIST Controllers: BIST controllers control various BIST engines. A hierarchy of BIST controllers, that is, components at various levels of hierarchies, is supported. Such controllers can be connected in chains with memories or other controllers.

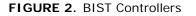

FUSE Controllers: FUSE controllers detect a 'defective' row/column in a memory and help replace it with redundant rows/columns inside the same memory. A hierarchy of FUSE controllers, that is, components at various levels of hierarchies, is supported. Such controllers can be connected in chains with multiple memories or other controllers.

■ JTAG controllers or other new instances: A standard TAP controller (IEEE 1149.1) is inserted and then the MBIST control circuits are connected to this TAP controller for initiating MBIST and collecting the status from the BIST operation on memories. New blocks, that is, blocks that are not part of the original RTL design, can be inserted in various custom connections in order to facilitate MBIST activity.

### **Restrictions Imposed by the Technology**

The architecture choice may be restricted by the specific technology. Examples of such restrictions are as follows:

- A specific shared BIST engine may be restricted to a limited number of memories.

- A specific FUSE controller may be restricted to no more than 32 memories in a chain.

### **Final View**

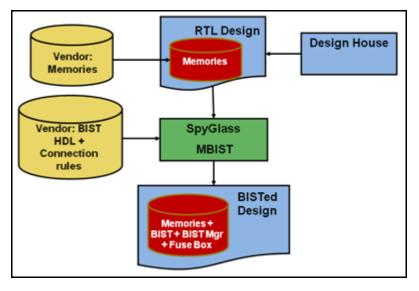

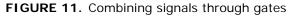

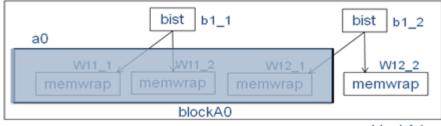

The SpyGlass DFT MBIST product works in guidance with the vendor's library, applies technology restrictions, and generates a BIST-inserted design. A representative view of the post-BIST design is shown in the following figure:

Note that in the above figure, the memories in the original RTL exist at various levels of hierarchy. In addition, the other components are inserted

as part of MBIST insertion. Here, the designer selects the insertion level.

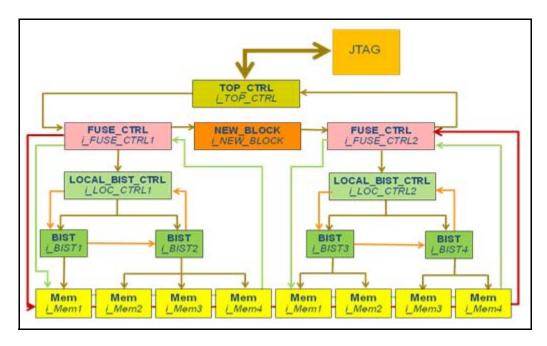

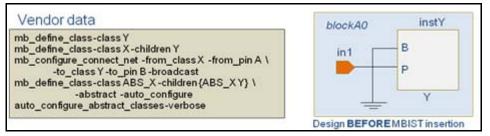

#### Vendor Data and User Data

The SpyGlass DFT MBIST product works with technology-specific data provided by the vendor. The designer provides 'design-dependent' data that refers to the vendor data and uses the SpyGlass DFT MBIST product. Thus, the use model can be represented by the following diagram.

FIGURE 5. Vendor data and user data

Vendor data is design-independent and created by the vendor with technology restrictions in mind. This data will be used in any design targeted for the vendor's technology.

User data is design-dependent and must be available for each design. The designer, while creating the user data, should have the knowledge of the vendor data and should understand how the vendor information can be used to achieve the MBIST structure. In the following section, we will

MBIST Overview

describe the essential structure of the user data file.

## Approach for Inserting MBIST into a Design

This section describes the approaches/activities involved as part of MBIST insertion. More details about the specific instructions and variations are described in the *Steps for Inserting MBIST into a Design* section.

### **Overview**

The following figure illustrates the recommended flow to perform MBIST insertion into a design by using the SpyGlass DFT MBIST product.

FIGURE 6. Use model of the SpyGlass DFT MBIST product

The SpyGlass DFT MBIST product provides an automated way to insert any vendor-specific BIST components into the designer's RTL. The SpyGlass DFT MBIST product is not tied to any vendor house so that the designer has the flexibility to work with any vendor of his choice.

### Stages during SpyGlass DFT MBIST Insertion

This section gives a brief overview of each stage of SpyGlass DFT MBIST insertion.

The SpyGlass DFT MBIST insertion is divided into the following stages:

- Creating a Vendor File

- Collecting Design Data and Preparing for MBIST Run

- Creating a User Data File

- Verifying the Post-BIST Design

The following two distinct steps are required before starting the MBIST insertion process:

- 1. Vendor file creation by the vendor (one time effort), and

- 2. User file creation by the designer (once for each design)

### **Creating a Vendor File**

To create a vendor file, perform the following steps:

- 1. Define classes

- 2. Specify connections

- 3. Disconnect existing connections

- 4. Specify chain connections

- 5. Combine signals through gates

For detailed information on creating a vendor file using the SpyGlass DFT MBIST product, see *Creating a Vendor File*.

#### **Defining Classes**

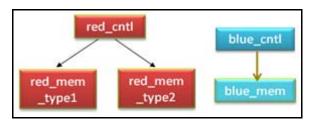

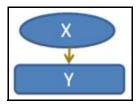

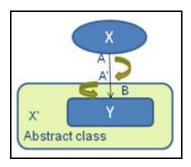

All the components relevant for MBIST (for example memories, controllers, etc.) are classified in a few named 'classes'. Then parent-child relationship is established among various class members. A sample scheme of class definition and their relationship is shown in the following diagram.

Five classes are defined: 'red\_cntl', 'red\_mem\_type1', 'red\_mem\_type2', 'blue-cntl' and 'blue\_mem'. Two relationships are defined: 'red\_mem\_type1' and 'red\_mem\_type2' are the children of 'red\_cntl'. Similarly, class 'blue\_mem' is a child of 'blue\_cntl'. Note, so far we have defined only the classes and their relationships. We are still not referring to any instances in a design (this will be done in the user file). The advantages of defining such classes and their relationship make it possible to define operations permissible only to such class members.

For defining classes in using the SpyGlass DFT MBIST product, see *Defining Classes*.

#### **Specifying Connections**

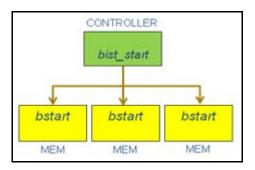

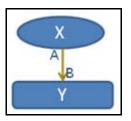

Once we have defined 'classes' and their 'children' we are ready to specify connections between them. An example of a 'required' connection in BIST-inserted design is for the BIST controller to supply the 'bist\_start' control signal to the memory, as shown below:

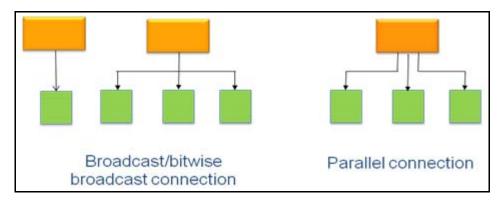

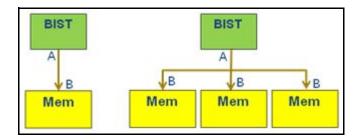

In this scheme, both 'CONTROLLER' and 'MEM' have been defined as two classes, MEM being the child of CONROLLER. The vendor data should contain the necessary specification for such a connection. Moreover, as we will see in a following section, the connection could be a 'broadcast, or 'parallel' connection.

For specifying connections using the SpyGlass DFT MBIST product, see *Specifying Connections*.

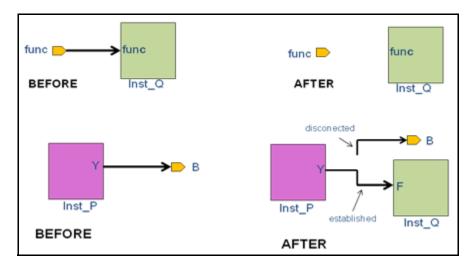

#### **Disconnecting Existing Connections**

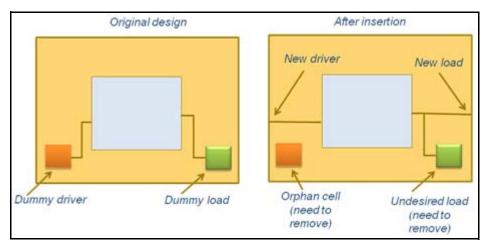

In addition to establishing connections, it is often useful to disconnect existing connections. The activities may include simply disconnecting an existing connection, or disconnecting an existing connection from a driver (load) followed by establishing new driver (load).

FIGURE 9. Disconnecting existing connections

For disconnecting existing connections using the SpyGlass DFT MBIST product, see *Disconnecting Existing Connections*.

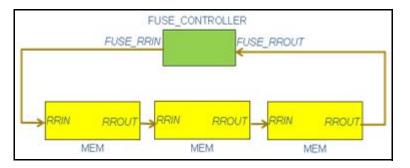

#### **Specifying Chain Connections**

It may be necessary to specify required chain connections for various design components. As an example, the vendor may require a fuse controller to connect to a specific class of memories through a chain, as shown below:

In this example, FUSE\_CONTROLLER and MEM should be defined as two different classes and MEM defined as a child of FUSE\_CONTROLLER. Vendor data requires that a daisy chain be formed from the 'FUSE\_RRIN' pin of the FUSE\_CONTROLLER to the 'FUSE\_RROUT' pin of the same class object through the pins 'RRIN' and 'RROUT' of MEM.

For specifying chain connections using the SpyGlass DFT MBIST product, see *Specifying Chain Connections*.

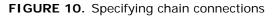

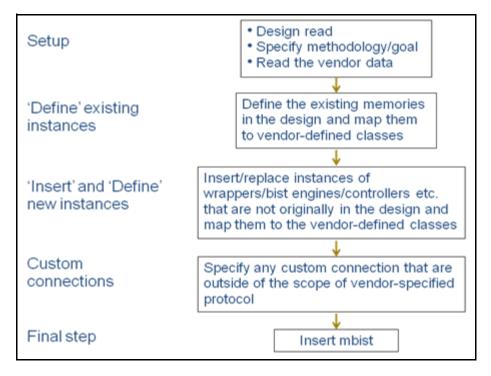

#### **Combining Signals through Gates**

It is often required that status signals from multiple BIST engines/ controllers are combined with gates like AND/OR/EXOR or technology library specific gates to generate global status signals. The following example shows that the 'bbad' (indicating failed test) signals from three BIST engines are combined through an OR gate and the resultant status signal is connected to a BIST controller.

In this case, BISTCNTL and BIST should be defined as two classes with BIST being the child of BISTCNTL. The vendor data specifies that the all the signals connected to the 'bbad' pin of the BIST instances are combined through an OR gate and the resultant signal drives the 'bstatus' pin of BISTCNTL instance. Note, the vendor may also optionally specify the 2input gate to a specific cell from a technology library.

In summary, the vendor data

- indicates class definitions for memories and controllers

- indicates parent-child relationships among the classes

- indicates permissible connections between the classes

- indicates how chain connections are defined

- indicates how signals produced by class objects can be combined through generic/technology-specific 'AND'/'OR'/'EXOR' gates

We will describe more in detail about the specific instructions and variations of these specifications in the section *Steps for Inserting MBIST into a Design*.

Verification of the post-BIST design is critical to ensure the integrity of the insertion and connection process. For example, for the above example, one would like to check that the 'bbad' pins of the three BIST instances are indeed connected to the 'bstatus' pin of the instance of BISTCNTL. Details to accomplish verification will be presented in section XX.

For combining signals through gates using the SpyGlass DFT MBIST product, see *Combining Signals through Gates*.

### **Collecting Design Data and Preparing for MBIST Run**

The designer is responsible for design-dependent data. It is mandatory that the designer is aware of the various memory instances present in the design. It is also the designer's responsibility to identify the association of memories with BIST engines. One needs to create the instance-specific association among all the BIST components.

As part of the BIST insertion process, the designer must find answers to the following questions:

- What are the memory instances in the design? How they are mapped to the vendor-specified classes?

- Which memory instances are to be associated with which BIST engine instances? Which classes the BIST engine instances belong to?

- Which BIST controller instances will control which BIST engine instances? Which classes the BIST controller instances belong to?

In summary, as the designer is getting ready to run the insertion step, the following design-specific information should be available. This examples assumes a certain set of BIST components to work with (this class hierarchy depends on the vendor).

FIGURE 12. Collecting design data and preparing for MBIST run

For more information on how the SpyGlass DFT MBIST product can be used to extract data to help the designer prepare for the MBIST insertion, see

Approach for Inserting MBIST into a Design

Collecting Design Data and Preparing for MBIST Run.

#### **Creating a User Data File**

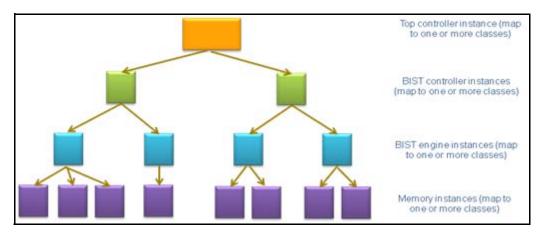

To create a user data file, perform the following steps:

- 1. Prepare the setup

- 2. Define the existing instances

- 3. Insert/replace and define new instances

- 4. Remove the existing instances

- 5. Establish custom connections

- 6. Insert MBIST

- 7. (Optional) Specify the location of modified design files

The above steps are illustrated in the following diagram:

FIGURE 13. Steps for creating a user data file

For detailed information on creating a user data file using the SpyGlass DFT MBIST product, see *Creating a User Data File*.

#### **Preparing the Setup**

The SpyGlass DFT MBIST product works in an environment based on Tcl called 'sg\_shell'. The vendor data and the user data are in Tcl format and can use all the standard Tcl scripting techniques.

To prepare the setup for running the SpyGlass DFT MBIST product, perform the following steps:

- 1. Read the design

- 2. Read the BIST-related components

- 3. Specify the methodology and goal

- 4. Read the vendor data

- 5. Control the output format

For detailed information on preparing the setup using the SpyGlass DFT MBIST product, see *Preparing the Setup*.

#### **Reading the Design**

The first step of the SpyGlass DFT MBIST product is to read the design. The design can be specified in Verilog, VHDL, or mixed language format. It is necessary to create a SpyGlass 'project', supply a list of RTL files, specify path to library directories containing libraries, specify the library files, and supply a list of technology libraries (in case of technology mapped netlist) in '.sglib' format. We will describe commonly encountered requirements in section *Creating a User Data File*. Refer to the 'design read' methodology in SpyGlass user guide.

#### **Reading Compressed Files**

SpyGlass DFT MBIST product reads compressed files and will generate compressed files if modifications to any of these files are produced.

#### **Reading the BIST-Related Components**

In order to be able to insert the BIST related components you need to read the RTL descriptions of them. Also, note that they are not part of the supplied design yet. They will become part of the design after the BIST insertion. However, at this stage you can supply the description of the BIST components through the usual design read process, like – reading the RTL models explicitly, supplying them through set\_option v command or set\_option y command as in the Verilog paradigm. This process will be illustrated in the 'step-by-step' section of this document.

#### Specifying the Methodology and Goal

This is an essential requirement for SpyGlass operation to specify a 'Methodology' and 'Goal'. For the MBIST purpose we need to select the '\$SPYGLASS\_HOME/Methodology/MBIST\_DFT' methodology and 'mbist\_dft' goal.

#### **Reading the Vendor Data**

At this step, we read the vendor data or the technology information through a TCL read command.

#### **Controlling the Output Format**

During this setup step, we can control the nature of the output data produced by the BIST insertion steps. This consists of the following:

- How the modified module changes its name

- How the modified design file name changes (control one or both of the prefix and suffix of the file name)

- How any modified signal changes its name

#### Example

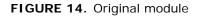

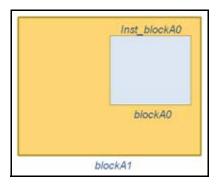

Consider the following modules:

After BIST insertion, the module names are modified as follows:

FIGURE 15. Modified module after BIST insertion

**NOTE:** The name of the modified top-level module is never changed. This is because at a higher level of the design, the modified top-level module is continued to be referred by the same name.

SpyGlass, however, maintains the uniqueness of any generated name. This means that whenever there is a name clash, the name is 'uniquified'. We will find out more details of this user control steps in the "step-by-step" section.

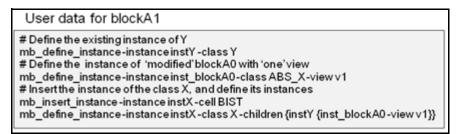

#### **Defining the Existing Instances**

The user needs to know the memory instances (with the hierarchical instance names) existing in the design. The vendor data would have already defined specific 'classes' for these memories. At this stage, the user identifies such existing instances and maps them to the vendor-specified 'classes'.

For this purpose and for inserting new instances, the user may need to maintain this instances) in a convenient format such as a table as shown below:

| SI # | Memory instance                         | Memory type         | Controller instance name                     | Controller name     |

|------|-----------------------------------------|---------------------|----------------------------------------------|---------------------|

|      |                                         |                     |                                              |                     |

| 1    | i_distributed.i_big_mem.i_mem1          | MEM_2048x32m8_LTB1  | i_distributed.i_big_mem.i_mem1_ctrl          | COLLAR_6_Dedicated  |

| 2    | i_distributed.i_big_mem.i_mem2          | MEM_2048x32m8_LTB1  | i_distributed.i_big_mem.i_mem2_ctrl          | COLLAR_7_Dedicated  |

| 3    | i_distributed.i_big_mem.i_mem3          | MEM_2048x32m8_LTB1  | i_distributed.i_big_mem.i_mem3_ctrl          | COLLAR_8_Dedicated  |

| 4    | i_shared.i_big_mem.i_mem1               | MEM_2048x32m8_LTB1  | i_shared.i_big_mem.CONTROLLER_4              | COLLAR_10_Parallel  |

| 5    | i_shared.i_big_mem.i_mem2               | MEM_2048x32m8_LTB1  | i_shared.i_big_mem.CONTROLLER_4              | COLLAR_10_Parallel  |

| 6    | i_shared.i_big_mem.i_mem3               | MEM_2048x32m8_LTB1  | i_shared.i_big_mem.CONTROLLER_4              | COLLAR_10_Parallel  |

| 7    | i_distributed.i_small_mem.i_mem0.i_mem1 | MEM_256x8m8_LTB1    | i_distributed.i_small_mem.i_mem0.i_mem1_ctrl | COLLAR_3_Dedicated  |

| 8    | i_distributed.i_small_mem.i_mem0.i_mem2 | MEM_256x8m8_LTB1    | i_distributed.i_small_mem.i_mem0.i_mem2_ctrl | COLLAR_4_Dedicated  |

| 9    | i_distributed.i_small_mem.i_mem3        | MEM_256x8m8_LTB1    | i_distributed.i_small_mem.i_mem3_ctrl        | COLLAR_5_Dedicated  |

| 10   | i_red1.i_mem2                           | MEM_4096x32m8_LRTB2 | CONTROLLER_3                                 | COLLAR_2_ParallelR  |

| 11   | i_red2.i_mem2                           | MEM_4096x32m8_LRTB2 | CONTROLLER_3                                 | COLLAR_2_ParallelR  |

| 12   | i_red3.i_mem2                           | MEM_4096x32m8_LRTB2 | CONTROLLER_3                                 | COLLAR_2_ParallelR  |

| 13   | i_red1.i_mem1                           | MEM_4096x32m8_LRTB2 | CONTROLLER_1                                 | COLLAR_1_ParallelR  |

| 14   | i_red2.i_mem1                           | MEM_4096x32m8_LRTB2 | CONTROLLER_1                                 | COLLAR_1_ParallelR  |

| 15   | i_red3.i_mem1                           | MEM_4096x32m8_LRTB2 | CONTROLLER_1                                 | COLLAR_1_ParallelR  |

| 16   | i_shared.i_small_mem.i_mem0.i_mem1      | MEM_256x8m4_L       | i_shared.i_small_mem.CONTROLLER_2            | COLLAR_9_Parallel   |

| 17   | i_shared.i_small_mem.i_mem0.i_mem2      | MEM_256x8m4_L       | i_shared.i_small_mem.CONTROLLER_2            | COLLAR_9_Parallel   |

| 18   | i_shared.i_small_mem.i_mem3             | MEM_256x8m4_L       | i_shared.i_small_mem.CONTROLLER_2            | COLLAR_9_Parallel   |

| 19   | i_mem1                                  | MEM_512x16m4_LB4    | i_mem1_DPREG_ctrl                            | COLLAR_11_Dedicated |

|      |                                         |                     | CONTROLLER_5                                 | TOP_BIST_CTRL       |

#### TABLE 1 Memory instances

Note, the user maintains a list of memories and their instance names (as shown in col. 2 and 3 in the above table) in the design. The memory types are typically defined as 'classes' in the vendor data. At this step, the user maps the instances (with hierarchical names) to the pre-defined 'classes'.

Such a table is not required by the SpyGlass DFT MBIST product. However, it may be useful to facilitate supplying the correct directions to drive the tool.

For defining the existing instances using the SpyGlass DFT MBIST product, see *Defining the Existing Instances*.

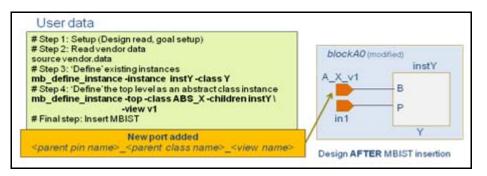

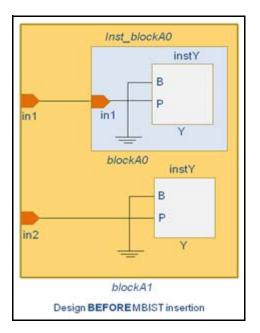

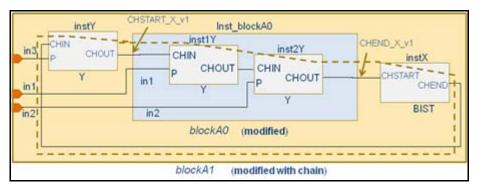

#### **Inserting/Replacing and Defining New Instances**

#### **Inserting New Instances**

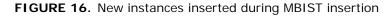

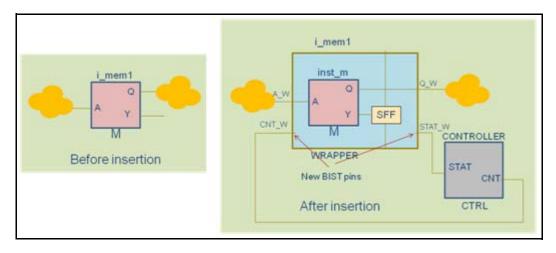

At this step, user indicates which new instances are to be inserted. The new instances are the BIST engines, controllers etc. Examples of inserting controllers ('dedicated' and 'shared' types) are as shown in the following diagrams.

As shown in the diagrams above, the controller instance is inserted as intended by the user. The connections between the memory and the controller instance are guided by the connection rules indicated in the vendor data file.

#### **Inserting New Instances of Parameterized Modules**

It is often convenient to define instances of parameterized cells where the designer explicitly supplies the parameter values for insertion. See the *Steps for Inserting MBIST into a Design* section for details.

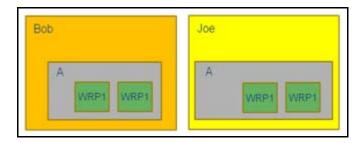

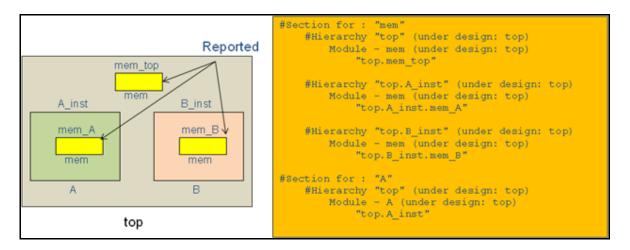

#### **Replacing Existing Instances**

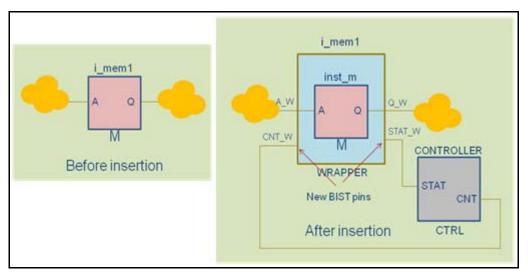

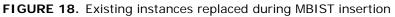

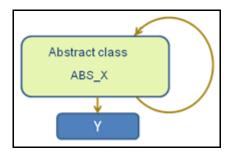

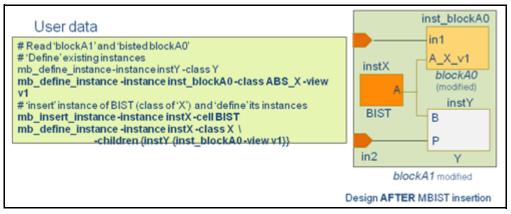

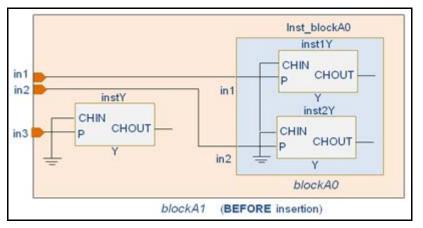

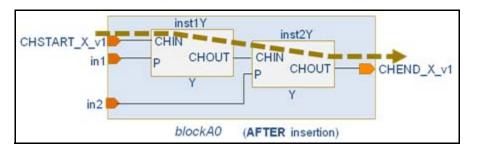

Special situations may require replacing an existing instance by another instance. Consider the case as depicted in the following diagram. After BIST insertion, the design will have additional connections (extra pins on the new instance). Thus, it becomes necessary to 'replace' the memory instance by the instance of the 'WRAPPER'.

FIGURE 17. Existing instances replaced during MBIST insertion

The user must create a 'class' for the wrapper (class declaration for memory is not needed here). The connection between the wrapper instance and the controller instance will be governed by connection rules specified in the vendor data file.

This process should also be able to accommodate the case where all the ports of the memory do not have corresponding 'substitute' on the wrapper. These memory ports are originally unconnected in the design. One possibility is they are consumed by an internal scan chain inside the wrapper, as shown in the following diagram. You will notice that the pin 'Y' of the memory is connected to an internal logic inside the wrapper and does not have a corresponding pin map on the wrapper. See the 'step-by-step' section for details of how this can be accomplished.

For inserting/replacing and defining new instances using the SpyGlass DFT MBIST product, see *Inserting/Replacing and Defining New Instances*.

#### **Removing the Existing Instances**

Situations exist where it is necessary to remove existing instances. For example, placeholders in the original design may become orphans after the MBIST insertion. The designer may explicitly indicate to remove instances of specific cells in the user data file.

FIGURE 19. Existing instances removed during MBIST insertion

For removing the existing instances using the SpyGlass DFT MBIST product, see *Removing the Existing Instances*.

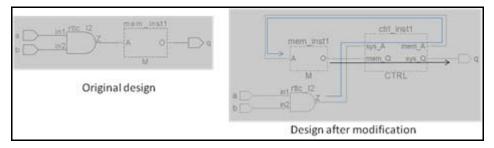

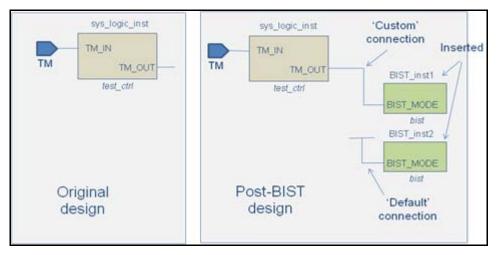

## **Establishing Custom Connections**

Most of the connections/chains between the memories and the BIST components will be established by the rules provided in the vendor data file. However, there may still be the requirement of creating 'custom' connections that are outside of the scope of vendor specification.

FIGURE 20. Establishing custom connections

The diagram above shows various connections between instances in the design.

MBIST may be used to establish any arbitrary point-to-point connection such as:

- Connecting a pin of an instance (newly inserted or existing) to a primary I/O port

- Connecting a pin of an instance to GND or VCC

- Overriding a vendor-directed connection with a custom connection

For establishing custom connections using the SpyGlass DFT MBIST product, see *Establishing Custom Connections*.

## **Inserting MBIST**

This is the final step of MBIST insertion. With the vendor information file and the user's intention in the user data file, the tool generates the modified description of the design by inserting the MBIST components and making all the prescribed connections.

For inserting MBIST into the design using the SpyGlass DFT MBIST product, see *Inserting MBIST: The mb\_insert Tcl Command*.

## Specifying the Location of Modified Design Files

The modified design files are deposited in a specific directory. However, the designer can optionally collect all the modified design files in a user-specified location.

For specifying the location of modified design files using the SpyGlass DFT MBIST product, see *Specifying the Location of Modified Design Files*.

# Verifying the Post-BIST Design

To verify the post-BIST design, perform the following steps:

- 1. View the modified design

- 2. Verify the AND/OR/EXOR logic tree

## Viewing the Modified Design

This is a convenient way of inspecting that the modified RTL is indeed free of syntax errors (syntactically correct Verilog/VHDL/SystemVerilog) and is synthesizable. We recommend that the designer reads the modified design into SpyGlass, runs a generic GuideWare goal (refer to the SpyGlass GuideWare Methodology manual for more information) and view the modified design in the schematic. The designer will be able to view the inserted BIST components, various inter-block connections, and the desired chain connections. We will describe the steps in detail in section 4.

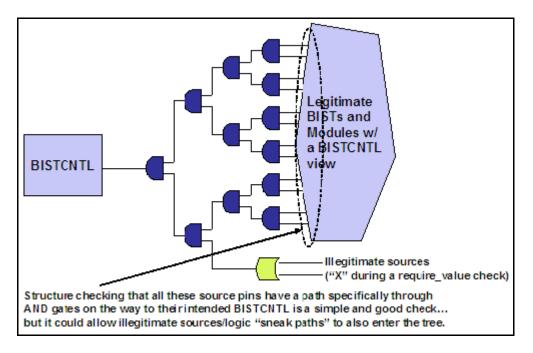

## Verifying the AND/OR/EXOR Logic Tree

The BIST insertion process may be required to logic trees with desired particular logic function. However, 'sneak paths' may be created with either incorrect logic functions or an inappropriate source, as shown in the following diagram.

FIGURE 21. Verifying the AND/OR/EXOR logic tree

It is recommended that the designer run checks through SpyGlass to flag such situations.

For verifying the post-BIST design using the SpyGlass DFT MBIST product, see *Verifying the Post-BIST Design*.

# Steps for Inserting MBIST into a Design

This section describes the steps for using SpyGlass DFT MBIST product. For a description of the Tcl commands, refer to the *SpyGlass MBIST Tcl Flow Reference Guide*. This section will illustrate the most common use model. The description in this section corresponds to the approach discussed in section *Approach for Inserting MBIST into a Design*.

## **Creating a Vendor File**

This section elaborates how the various steps described in the Approach section can be achieved through Tcl commands in the vendor data file. The intention is to illustrate the most common scenarios. For more details and the exact syntax of the Tcl commands, the user should refer to the *SpyGlass MBIST Tcl Flow Refrence Guide*.

## **Defining Classes**

Components are given a class definition with the command 'mb\_define\_class'. This command is also used to describe parent-child relationships.

The class hierarchy structure in our example can be specified as follows:

```

mb_define_class -class red_mem_type1

mb_define_class -class red_mem_type2

mb_define_class -class blue_mem

mb_define_class -class red_cntl -children {red_mem_type1

red_mem_type2}

mb_define_class -class blue_cntl -children blue_mem

```

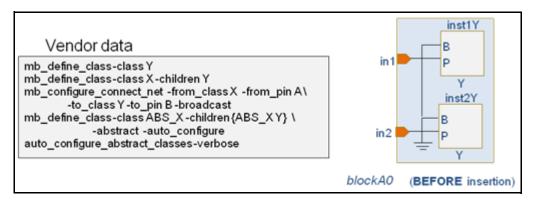

## **Specifying Connections**

Pin-to-pin connections can be established through the 'mb\_configure\_connect\_net' command. Connections can be one-to-one or one-to-many.

There are following types of connections:

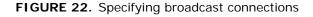

#### Broadcast connections

In this example, scalar pin 'A' of an instance of class 'BIST' must be connected to the scalar pin 'B' of one or more instances of class 'Mem'. This is accomplished through the command:

```

mb_configure_connect_net -from_class BIST -from_pin A \

-to_class Mem -to_pin B -broadcast

```

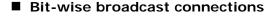

In this example, vector pin 'P' of an instance of class 'BIST' is connected to the similar sized vector pin 'Q' of one or more instances of class 'Mem'. This is accomplished through the command:

```

mb_configure_connect_net -from_class BIST -from_pin P \

-to_class Mem -to_pin Q -bitwise_broadcast

```

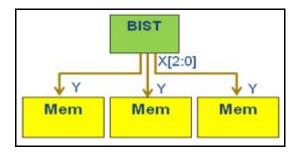

### Parallel connections

In this example, vector pin 'X' of an instance of class 'BIST' is connected to the scalar pin 'Y' of multiple instances of class 'Mem'. This is accomplished through the following command:

```

mb_configure_connect_net -from_class BIST -from_pin X \

-to_class Mem -to_pin Y -parallel

```

### **Common Connection Requirements**

This section describes some of the commonly required connections. Each case begins with a before and after example followed by a description of the associated commands.

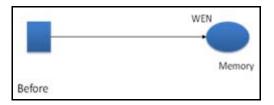

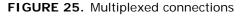

#### Multiplexed connections

The multiplexed connection is used to switch between functional mode and BIST mode:

This multiplex connection is made with the following:

```

mb_configure_connect_net -from_class CONTROLLER

-from_pin WEN -to_class MEMORY -to_pin WEN

-multiplex -select_enable SEN -active HIGH

```

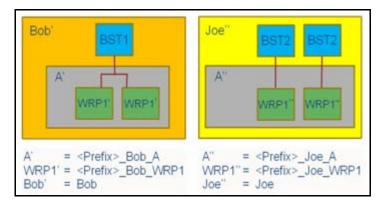

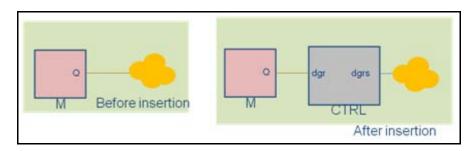

#### Connections through inserted components

The following diagrams illustrate new connections because of component insertion:

After BIST insertion, an instance of class CTRL has been inserted and the above connections have been made. Q pin of M now drives the 'dgr' pin of CTRL and the 'dgrs' pin of CTRL drives the logic. This represents a connection 'through' another class object.

This can be accomplished through the following command:

```

# Vendor

mb_define_class -class M

```

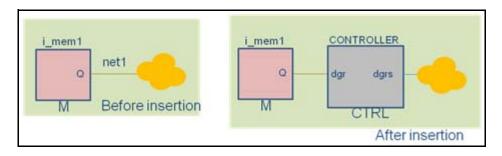

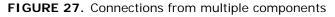

#### Connections from multiple components

A single insertion can require multiple connections as illustrated below.

In this case, a 'shared' controller has been inserted and appropriate connections between the memories and the controller are established. This can be accomplished by the connection rule:

```

# Vendor

mb_define_class -class M

mb_define_class -class CTRL -children M

# The following indicates the legal connections

# between the memories and the controller

mb_configure_connect_net -from_class M -from_pin {Q}

-through_class CTRL -in_pin {dgr_1 dgr_2 dgr_3}

-out_pin {dgrs_1 dgrs_2 dgrs_3} -parallel

```

Connections from a single controller to multiple memories

In this case, each bus from the controller will be split and connected to

multiple pins of the same memory.

FIGURE 28. Connections from a single controller to multiple memories

This can be achieved with the following connection rule:

```

# Vendor

mb_define_class -class M

mb_define_class -class CTRL -children M

# The following indicates the legal connections

# between the memories and the controler

foreach {parallel_ctrl memory} { CTRL M} {

foreach {frpin topin} {{dg_1 dg_2 dg_3} {in1 in2}} {

mb_configure_connect_net \

-to_class [list $memory $memory] -to_pin $topin \

-from_class $parallel_ctrl -from_pin $frpin

-parallel

}

}

```

### Connections to VCC or GND

A vendor directive can be used to connect a specific pin on all objects

belonging to a class to constant nets (VCC or GND), resulting into the following connections:

FIGURE 29. Connections to VCC or GND

The vendor directive can be specified as follows:

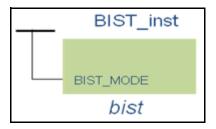

#### Connections to top port

Generic class can be used to define connection with top-level ports in the vendor file.

This is accomplished using the following connection rule:

```

mb_configure_connect_net -from_class WRAP_CC_ECID \

-from_pin Y -to_top_port y

```

In this case, if output port, y, on top does not exist, a new output port by name y is created on top. Also, if connection is routed from the intermediate hierarchy and output port by name Y does not exist on the intermediate hierarchy, then new output port by name Y is created on the intermediate hierarchy.

```

mb_configure_connect_net -from_top_port a \

-to_class WRAP_CC_ECID -to_pin A

```

In this case, if input port, a, on top does not exist, a new input port by name a is created on top. Also, if connection is routed from the intermediate hierarchy and input port by name A does not exist on the intermediate hierarchy, then new input port by name A is created on the intermediate hierarchy.

## **Disconnecting Existing Connections**

Existing connections can be removed with the 'mb\_configure\_connect\_net' command.

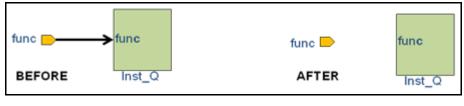

Case 1: Disconnect existing driver and do not establish a new connection to a driver

```

mb_configure_connect_net

```

-to\_class Q -to\_pin func -disconnect

Case 2: Disconnect existing load and do not establish a new connection to load

-from\_class P -from\_pin func -disconnect

-to\_class Q -to\_pin func -broadcast

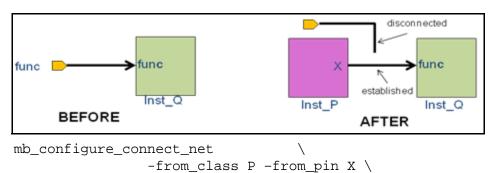

Case 3: Disconnect existing driver and establish new connection to a driver

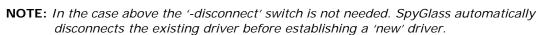

■ **Case 4**: Disconnect load and establish new load

```

-from_class P -from_pin Y \

-to_class Q -to_pin F \

```

-broadcast -disconnect

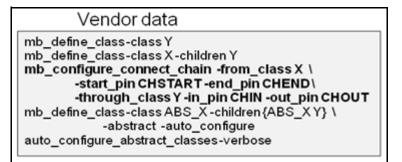

## **Specifying Chain Connections**

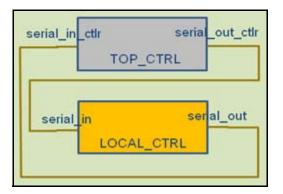

Chains through various class objects can be achieved through the 'mb\_configure\_connect\_chain' command. Consider the following scenario:

FIGURE 30. Specifying chain connections

This requires a chain connection through two class members – TOP\_CTRL and LOCAL\_CTRL. The start of the chain is the 'serial\_out\_ctrl' pin and the end point is the 'serial\_in\_ctrl' pin of TOP\_CTRL.

This configuration is achieved through the following vendor data file command:

```

#Vendor

mb_define_class -class LOCAL_CTRL

mb_define_class -class TOP_CTRL -children LOCAL_CTRL

mb_configure_connect_chain -from_class TOP_CTRL\

-start_pin serial_out_ctlr -end_pin serial_in_ctlr \

-through_class LOCAL_CTRL \

-in_pin serial_in \

-out_pin serial_out

```

Note that the above vendor data merely specifies a configuration rule. In the actual design more than one instance of the 'child class' can be connected in a serial chain with an instance of the 'parent' class

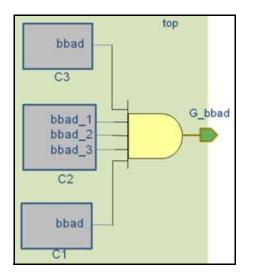

## **Combining Signals through Gates**

Signals generated by several class objects can be combined through the 'mb\_configure\_connect\_gate' command. Permissible combination gate types are 'AND', 'OR' and 'XOR' only. Consider the following scenario describing the AND of five error signals.

FIGURE 31. Combining signals through gates

This diagram shows three different classes of controllers (C1, C2, and C3) that each produce a 'bbad' output status signal. An AND of these signals and brought to the top-level port 'G\_bbad' with the following command:

```

# Vendor:

mb_define_class -class C1

mb_define_class -class C2

mb_define_class -class C3

mb_define_class -class top -children {C1 C2 C3}

#

# Connect the 'bbad*' ports of the controllers

# through AND gate and bring the status signal to

# the top level port 'G_bbad'

mb_configure_connect_gate -type AND \

```

```

-from_class { C1 C2 C2 C2 C3 } \

-from_pin { bbad bbad_1 bbad_2 bbad_3 bbad } \

-to_class top_class -to_pin G_bbad

```

Note, the above vendor configuration information simply dictates that the permissible connections to one such gate are class objects of C1, C2, and C3 only. In the design, however, the user will instantiate one or many instances of such class objects.

User may prefer to use a specific library cell to combine signals. In that case use the'-cell <cell type>' option to specify the technology cell. However, note that the description of the cell has to be supplied to SpyGlass DFT MBIST product as part of design read and such a cell can only be of type 'AND', 'OR' and 'XOR' functionality (the gate should have 2 inputs only). The above configuration indicating the connection to an AND cell 'AND02\_4X' from library can be specified through the modified command:

```

mb_configure_connect_gate -type AND -cell AND02_4X \

-from_class { C1 C2 C2 C2 C3} \

-from_pin { bbad bbad_1 bbad_2 bbad_3 bbad } \

-to_class top_class -to_pin G_bbad

```

The above will result in insertion of a tree of the AND02\_4X cells.

**NOTE:** Connections from 'children' classes feeding 'parent' class is the only direction allowed. In case of an attempt to combine in an opposite direction will result in an error message:

Error: Class <to class> is not a parent or grandparent of <from class>

The reason for this restriction is that such specifications causes ambiguity in selecting one of many target instances of a child class.

## **Collecting Design Data and Preparing for MBIST Run**

Run SpyGlass to collect information about the memory instances in a design.

## mb\_report\_instances

Run this Tcl command to create a report:

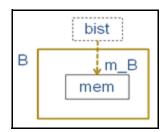

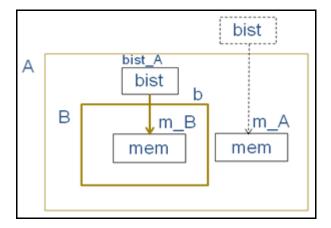

Consider a hierarchical design with instances of specific cells instantiated at various levels:

```

//File: test.v

module test(a1, a2, a3, b1, b2, b3);

input a1, a2, a3;

output b1, b2, b3;

A inst A(.a(a1), .b(b1));

B inst_B(.a(a2), .b(b2));

C inst_C(.a(a3), .b(b3));

endmodule

module A(a, b);

input a;

output b;

B inst_B(.a(a), .b(b));

endmodule

module B(a, b);

input a;

output b;

C inst_C(.a(a), .b(b));

endmodule

module C(a, b);

input a;

output b;

assign b = -a;

endmodule

Prepare the following Tcl file and run in 'sg_shell' environment:

# File: test.tcl

# Create a new project

new_project prj -force

# Design read

read_file -type hdl test.v

set_option top test

# Find out all the instances of the cells whose names (cell

names)

```

```

\# match 'C', 'A' and 'B'

current_methodology $::SPYGLASS_HOME/Methodology/MBIST_DFT

current goal mbist dft

mb_report_instances "*C*" "*A*" "*B*"

save project

close project

exit

It generates the following output:

Module - C (under design: test)

"test.inst_C"

"test.inst B.inst C"

"test.inst A.inst B.inst C"

Module - A (under design: test)

"test.inst A"

Module - B (under design: test)

"test.inst B"

"test.inst A.inst B"

```

Designers can write scripts using this Tcl command and prepare the user data to run SpyGlass DFT MBIST product.

A special case arises when the memory instances are instantiated through 'generate' statements, as often the case in a Verilog 2001 or SystemVerilog design. Care should be taken to understand how the names of such memory instances are created, and how such names should be used in the user data file. Refer to Appendix – C, at a later part in the document, to get a comprehensive idea of this case.

A variation of this command may be used to print the instances in a specific order, i.e. reporting by hierarchy, as shown below.

### mb\_report\_instances -group\_by\_hierarchy

This scheme adopts a 'depth\_first\_search' strategy and reports as follows:

- 1. Search starts at the top level of hierarchy

- 2. Reports all the 'matching' instances at this level

- 3. Dives down a lower level of hierarchy

4. Repeats the same reporting process (in 2)

An example of a run is as follows:

```

mb_report_instances "*wrap2*" "*wrap1*" "*wrap3*" "*wrap4*"

-group_by_hierarchy -report_file myreport.rpt

```

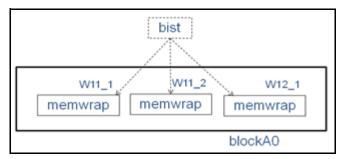

It is also possible to logically group a number of instances such that they are reported together. This often makes sense if the instances (specified to be in the same logical group) are intended to share the same parent (for example BIST controller, etc.).

An example is as follows:

```

mb_report_instances {*SRAM1D*, *SRAM1P*} *SRAM2T* *CAM*

*DRAM* -group_by_hierarchy

```

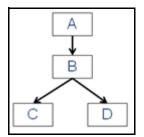

In this example, all the instances of the modules represented by the regexp "\*SRAM1D\*" and "\*SRAM1P\*" are meant to share the same parent. In addition, consider the hierarchy in the design as shown:

In this case, the instances are to be reported as:

Section for SRAM1D, SRAM1P

```

group of instances in the hierarchy A

group of instances in the hierarchy A/B

group of instances in the hierarchy A/B/C

group of instances in the hierarchy A/B/D

```

Section for SRAM2T

```

group of instances in the hierarchy A

group of instances in the hierarchy A/B

group of instances in the hierarchy A/B/C

group of instances in the hierarchy A/B/D

```

```

Section for CAM

group of instances in the hierarchy A

group of instances in the hierarchy A/B

group of instances in the hierarchy A/B/C

group of instances in the hierarchy A/B/D

Section for DRAM

group of instances in the hierarchy A

group of instances in the hierarchy A/B

group of instances in the hierarchy A/B/C

group of instances in the hierarchy A/B/C

```

### mb\_report\_instances -dive\_in

Normally, mb\_report\_instances stops at the boundary of a 'matched' module and does not dive inside it to find instances of any other matching modules. The '-dive\_in' switch allows the search to happen inside an already 'matched' module instance.

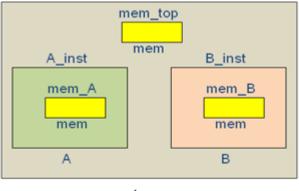

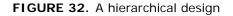

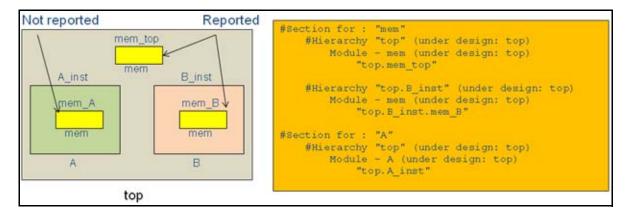

The following shows a hierarchical design where the module 'mem' is instantiated at various levels of hierarchies shown as highlighted.

top

The following command will produce the report shown below. Note that "mem" inside module A is not reported.

FIGURE 33. The report generated for the above hierarchical design

If the '-dive\_in' switch is added to mb\_report\_instances then the search is continued even inside already 'matched' module instances.

```

mb_report_instances {{*mem*}} "A" \

-group_by_hierarchy -report_file myreport.rpt \

-dive_in

```

FIGURE 34. The report generated for the above hierarchical design when -dive\_in option is used

## **Creating a User Data File**

This section describes the steps that will be followed by the user. We will describe and illustrate the user-driven Tcl commands in detail. However, for the exact syntax and more information please refer to the *SpyGlass MBIST Tcl Flow Reference Guide*.

## **Preparing the Setup**

This is the first step of the setup. This is a common setup step required for any SpyGlass analysis. The goal here is to supply the design information in Verilog/VHDL/mixed language format. Refer to the SpyGlass Explorer Reference Guide for more detailed information. Here we are going to describe a common way of reading a typical Verilog design.

Consider reading a Verilog design consisting of multiple files, header files residing under the 'include' directories, libraries spanning across multiple directories specified with '-y'. As a SpyGlass design read requirement it is mandatory to create a 'project' at the beginning. The Tcl commands for reading the design is illustrated as follows:

```

# Create a new 'project' with a name

new project prj DESIGN -force

# Command equivalent to '-v'

set option v ./MEMORY LIB/MEMORY.v

# Command equivalent to `+libext+.v'

set_option libext { .v }

# Command equivalent to `+incdir+'

set option incdir { lib/memory support/verilog/rtl }

# Command equivalent to '-y'

set_option y { lib/sram1d/verilog lib/memory_support/

verilog/rtl lib/memory support/verilog/net rtl }

# Now read the individual files

read file -type verilog lib/sram1d/verilog/wrappers/

WRAPT2A.v

read_file -type verilog testcase/atrenta/rtl/verilog/

DESIGN.v

```

#### Design read through a consolidated command file

Sometimes the designers have already prepared a command file for analyzing their designs through SpyGlass. The same file can be conveniently read for MBIST insertion purpose.

The following command file represents how a Verilog design can be read into SpyGlass:

```

// File: cmdfile.f

-incdir 'incdir_abc'

+libext+.v

-verilog

-y 'ydir'

-v 'lib.v'

header_b.vh

test.v

```

The same file can be read as part of the design read step, as:

```

read_file -type sourcelist cmdfile.f

```

#### Working with compressed RTL files

'Compressed' (gzipped) source files are read as follows:

```

read_file -type hdl <file ame>.gz

```

The files 'included' in Verilog source code and files supplied through the v command can be 'compressed' files. The files to be picked up from the directories specified through the y command can also be compressed. In that case, use the following option:

```

set_option libext {.v.gz}

```

If any of the design descriptions supplied through such compressed files need to be modified by SpyGlass then the output of the modified file is also generated as a compressed file.

Example:

read\_file -type hdl block.v.gz

mb\_set\_prefix\_n\_suffix -file\_suffix sg

After MBIST insertion in this file, the 'modified' file is generated as a compressed file in the name:

block.v\_sg.gz

#### Blackboxing

As mentioned earlier, some modules may be 'unintentionally' blackboxed. Review the following file and look for the violation messages for the following rules:

<project\_name>/mbist\_dft/spyglass\_reports/moresimple.rpt

You may like to understand the cause of these messages and like to fix them to ensure a clean design read. However, if you are sure that there is no memory inside these modules (and hence BIST insertion is not needed) then you may ignore these messages.

- ErrorAnalyzeBBox: This message indicates that the description of the module has not been supplied. The remedy is to supply the HDL for the module.

- WarnAnalyzeBBox: This message indicates that either the module description is 'empty' or the module is not synthesizable (while SpyGlass can understand the port interface of such module, it cannot navigate inside it).

Sometimes designers may be interested to blackbox parts of the design descriptions, for example a few behavior descriptions of the memory hierarchy. This may be accomplished by explicitly supplying the design name:

```

set_option stop {A_block B_block C_block }

```

It is recommended that you confirm that only the desired modules, and nothing else, have been blackboxed. SpyGlass generates the following report:

```

<project name>/mbist_dft/spyglass_reports/SpyGlass/

stop_summary.rpt

```

Review this file to find out the list of modules that have indeed been blackboxed due to the user's directive. The user-specified blackboxes are also indicated by the InfoAnalyzeBBox messages in the file:

```

<project name>/mbist_dft/spyglass_reports/moresimple.rpt

```

#### **Using Waivers**

Sometimes one may like to 'waive' certain messages (generated by SpyGlass DFT MBIST product) depending on nature of the design read. Refer to the SpyGlass Explorer User Guide for more detailed information about the 'waiver' mechanism.

An example of usage of waiver is provided in *Appendix B: An Example of Using Waivers*.

### Working with Encrypted Designs

It may be a requirement to work with an IP provided by a third-party vendor. For confidentiality, the vendor may wish to encrypt the source code of the IP. If there are memory instances in an encrypted IP then these memories will not be BISTed.

The following is the recommended methodology for working with 'encrypted' designs.

1. Use an `include statement to supply the definition of the encrypted IP. Embrace this `include statement within pragmas, as shown below:

```

// File: top.v

module top (....);

```

:

```

// This is the instantiation of the encrypted IP.

// The instance will be blackboxed since no definition will

// be visible to SpyGlass

IP ip_inst(.A(w1), .B(w2), ...);

:

endmodule

// vendor_string translate_off

// This encrypted file contains the description of IP

`include "core.vp"

// vendor_string translate_on

```

2. Use the following option during design read to SpyGlass:

```

set_option pragma vendor_string

```

Here *vendor\_string* is any arbitrary string suitably chosen by the RTL developer. Because of the 'set\_option' directive, SpyGlass will not read the content enclosed in between the pragmas. The advantage to this approach is that the reference to the definition (of the encrypted IP) will be available in the modified RTL (post-MBIST insertion) for other tools to use.

### Specifying the Description of the BIST components

The description of the components to be inserted (for example the BIST components that are not part of the original design) by any of the following methods:

Explicitly supply the description of the file:

read\_file -type hdl lib/sram1d/verilog/bist/BIST9A.v

Specify the description of the components through the y command:

```

set_option libext { .v }

set_option y { lib/bist_lib/verilog lib/memory_support/

verilog/rtl }

```

Specify the description of the components through the v command:

```

set_option v ./BIST_LIB/BIST_COMPONENTS.v

```

The description of such components, supplied through one or more of the above methods, will be picked up by SpyGlass DFT MBIST product during insertion.

### Specify the Methodology and Goal

To run SpyGlass DFT MBIST product, choose the Methodology as 'MBIST\_DFT' and the goal as 'mbist\_dft'

# \$SPYGLASS\_HOME may be conveniently set environment variable # to point to the SPYGLASS\_HOME directory in the software # release tree current\_methodology \$SPYGLASS\_HOME/Methodology/MBIST\_DFT/ current\_goal mbist\_dft -alltop

Once the 'current goal' is specified, it is mandatory to set the 'top level' of the design for the purpose of MBIST insertion. This is especially important in the case of SpyGlass DFT MBIST product because all the BIST components that are not yet part of the design will create a multiple top situation. This is prevented by the following command:

set\_parameter mbist\_top\_level\_name DESIGN

### **Read the Vendor Data**

The user is now required to read the vendor specific data (class definition, connection specification etc.) in the sg\_shell environment. It is often convenient to encapsulate this vendor-specific information in a file and read it.

# As a convenience the vendor specific commands are present # in the file `vendor.data' source vendor.data

### **Controlling the Output Format**

Various aspects of the output format are controlled by the following command:

```

mb_set_prefix_n_suffix

[-module_prefix <string>]

[-file_prefix <string>]

[-file_suffix <string>]

[-wire_prefix <string>]

[-help]

```

**NOTE:** The following two conditions must be satisfied for changing the file name:

The file name and module names must match in the pre-BIST RTL

The file must not contain more than one module

If either or both of the above conditions are not met, the file name is not changed.

Also note that it is the user's responsibility to supply appropriate module and file prefixes so that the module and file names match in the post-BIST RTL.

Prefixes/suffixes are applied only to the modified/added files/modules.

The default values of the user-configurable options are as follows:

```

FILE PREFIX

default value = "atrenta_modified_"

FILE SUFFIX

default_value = "" (null)

MODULE PREFIX

default value = "" (null)

WIRE PREFIX

default value = "Atrenta wire "

```

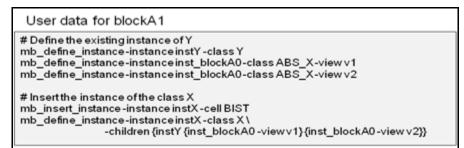

### **Defining the Existing Instances**

The memory instances that already exist in the design must be mapped to the defined 'classes'.

## **Inserting/Replacing and Defining New Instances**

#### **Inserting New Instances**

The user now inserts new instances into the design (typically, BIST related components, for example, BIST engines, controllers, etc.). This requires inserting an instance of a 'cell' or module definition. This is followed by mapping this instance to a predefined class and indicating which instances are its children. A sanity check is in place to ensure that the inserted instance has only 'legal' children (as indicated in the class relationship in the vendor data).

```

# Vendor data: Defines class structure and thereby recommends

# a legal use model

#

# Define two basic memory classes

#

mb_define_class -class MEMO

mb define class -class MEM1

#

# Now define a bist class that can control only memory

# class objects.

# According to this rule the bist class can control none or

# any number of instances belonging to these two memory

# classes

#

mb_define_class -class BIST1 -children {MEM0 MEM1}

#

# ----- End vendor file

# User data: User is now ready to work with the design as per

# the guidelines set in the vendor file

# The following are the two instances of memory classes

#

mb define instance -instance I7 -class MEMO

mb_define_instance -instance I6 -class MEM1

#

# Now insert an instance of bist class (CONTROLLER 1) to

# control I7 and I6. This is permissible in accordance with

```

```

# the guidelines # set in the vendor file.

#

mb_insert_instance -instance CONTROLLER_1 -cell BIST1

mb_define_instance -instance CONTROLLER_1 -class BIST1

-children {17 16}

```

#### **Inserting New Instances of Parameterized Modules**

During the insertion step, use the 'mb\_insert\_instance' command with specific parameter values through the '-parameter\_map' switch. For example

### **Replacing Existing Instances**

The designer can 'replace' an existing instance in the design with a block (maybe a 'wrapper'). As a result of the replacement, every functional connection will be established to at least one pin of the new replacing block. It is expected that every pin of the 'replaced' block be mapped to a pin of the 'replacing' block. However, in case the designer decides to 'ignore' mapping a list of pins of the replaced block, that can be done as we will see later in the illustration. This is accomplished through the basic command:

```

mb_replace_instance -instance

-cell <replacing block name>

[-pin_map {<new_pin old_pin>*}]

[-ignore_pin <old_pin>]

```

Keep in mind that the designer can omit the explicit pin mapping. In that case, the same pin names will be assumed. The following diagram illustrates a replacement and the associated commands.

FIGURE 35. Existing instances replaced during MBIST insertion

Note, there is no need to define a class for the 'replaced' object. Also, note that after the replacement of the instance, the extra pins on the new block are now available for connection to other (BIST) components.

In case there are extra pins on the memory that do not have a corresponding pin map on the wrapper, then such pins can be 'ignored' during replacement with the following command:

The above may be the case where the memory internally drives a scan flop

and the scan flop connections are brought out through one or more pins on the wrapper.

### **Removing the Existing Instances**

Use the 'mb\_remove\_instance' Tcl command for this purpose.

This command can be either part of the vendor or the user data file. The use model is illustrated as follows:

```

# Remove all the instances of the cell where the cell name

# contains the substring "TW"

mb_remove_instance -cell {{*TW*}}

# Remove all the instances of the cell where the cell name

# contains the substring "ABC"

mb_remove_instance -cell {{*ABC*}}

# Remove all the instances of the cell where the cell name

# contains the substring "TERM" and the instance name

# contains the substring "term_return"

mb_remove_instance -cell {{*TERM*}}

-instance {{*term_return*}}

```

Note, this command can be part of the vendor file. However, the design may not instantiate any cell that satisfies string-matching criteria. In this case, a warning message is generated and the user is allowed to move on.

## **Establishing Custom Connections**

Most of the connections will be established by the connection rules specified in the vendor file. If there is a need for custom connections (for example from a pin of an instance to a pin of another instance) then they can be accomplished through the 'mb\_connect\_net' command:

```

mb_connect_net

[-from <pin>*]

[-to <pin>]*

[-tie_extra_receivers <0|1>]

[-through_in_pin <pin> -through_out_pin <pin>]*

[-broadcast | -parallel | -bitwise_broadcast]

[-multiplex -select_enable <string> -active <high|low>]

```

[-id <string>] [-help]

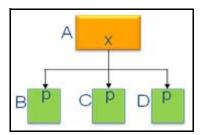

For example, the following diagram represents a broadcast topology where a scalar pin 'x' on the instance A must be connected to each of the pin 'p' of the instances B, C, and D.

This custom connection is accomplished by:

```

mb_connect_net -from A.x -to {B.p C.p D.p} -broadcast

```

Note, the above connection could also be specified as a 'bitwise\_broadcast' connection. However, it is mandatory to use the '-bitwise\_broadcast' switch if the pins are a vector, as follows:

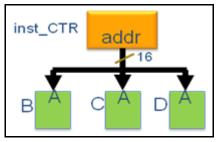

The connection being a bus, one needs to use the command:

```

mb_connect_net -from inst_CTR.addr -to {B.A C.A D.A} -

bitwise_broadcast

```

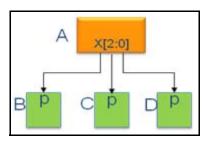

The diagram below, shows a scalar pin'p' on the instances B, C, and D receiving data from a three bit bus. Such connections are established through the following command:

mb\_connect\_net -from A.X -to {B.p C.p D.p} -parallel

Examples of some custom connections are shown below:

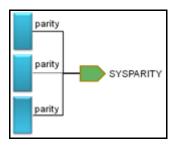

Connecting a pin of an instance (newly inserted or existing) to a primary I/O port

mb\_connect\_net -from { inst1.parity inst2.parity inst3.parity } \ -to SYSPARITY \ -add\_port \ -parallel

■ Connecting a pin of an instance to GND or VCC

Use a command such as:

mb\_connect\_net -from 0 -to FUSE\_inst1/FUSE\_MODE -parallel

• Overriding a vendor-directed connection with a custom connection

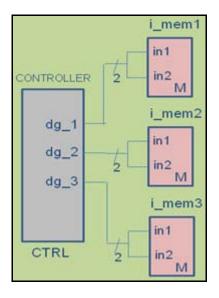

Any connection specified using the *mb\_connect\_net* command will automatically override the default connection configuration specified through *mb\_configure\_command\_net* command.

Consider the vendor rule for connection setup:

```

mb_configure_connect_net -from_class abs_TOP -from_pin 1 \

-to_class BST -to_pin BIST_MODE -broadcast \

-id CCN_BIST_MODE_TO_1

```

By default, all the class objects matching these classes are connected according to this rule. However, you can define the following custom connection in user data file to override the above default vendor connection:

```

mb_connect_net -from sys_logic_inst/TM_OUT \

-to BIST_inst1/BIST_MODE -parallel

```

Another mechanism to override vendor connection is based on skipping connection configuration using connection IDs as defined below:

```

mb_define_instance -instance BIST_inst1 -class BST \

-children mem_inst1 -skip_connection CCN_BIST_MODE_T0_1

```

## Inserting MBIST: The mb\_insert Tcl Command

This tcl command initiates application of vendor commands to useridentified instances and generates the "expanded" commands that will be applied to a design, and will invoke SpyGlass DFT MBIST product for design change.

```

mb_insert

```

```

[-preview]

[-output_control_file <output control data file>]

[-input_control_file <input control data file>]

[-force]

[-report <report file name>]

[-help]

```

It is recommended that the tool is run in 'preview' mode to ensure that the 'expanded' commands are properly generated. This step is analogous to the 'elaboration' step for a compilation activity. This enables the user to review the errors and fix them before undergoing the final step of inserting the BIST logic.

The following command will activate the '-preview' switch:

```

mb_insert -preview

```

The following in the stdout indicates that the expanded commands have been generated successfully without encountering any error from both the vendor file and user file.

#Found 0 error(s) while processing Vendor MBIST configuration

data

#Found 0 error(s) while processing User MBIST configuration

data

:

Generated MBIST control file 'top.mbist.sgdc'

0

sg\_shell>

It also produces useful information about the class hierarchy as depicted in the design, for example

```

#Info: No parent found for instance '<CURRENT MBIST TOP>'

# <CURRENT MBIST TOP> (class: top class)

#

--- TOP CONTROLLER (class: BIST CON FBOX)

#

--- CONTROLLER 1 (class: BIST1)

#

|--- I7 (class: RAM BLOCK BIST1 u sram0)

#

--- I6 (class: RAM BLOCK BIST1 u sram1)

#

#

--- CONTROLLER 2 (class: BIST2)

#

--- I3 (class: RAM BLOCK BIST2 u sram2)

#

#

--- CONTROLLER_3 (class: BIST3)

#

--- I1 (class: RAM BLOCK BIST3 u sram4)

#

--- I2 (class: RAM BLOCK BIST3 u sram3)

#

#

--- CONTROLLER 4 (class: BIST4)

#

--- I4 (class: RAM BLOCK BIST4 u sram6)

--- I5 (class: RAM_BLOCK_BIST4_u_sram5)

#

#

#

#

```

As part of this 'expansion or elaboration' process, a SGDC file is created

(by default it is < top module name>.sgdc or it can be specified through the '-output\_control\_file' switch of this command. This sgdc file contains the expanded version of all the directives that SpyGlass DFT MBIST product will act on.

Run the following command to invoke the design modification process:

mb\_insert

## **Specifying the Location of Modified Design Files**

The modified design files are deposited under a specified directory and can be accessed through the following file:

```

<project name>/mbist_dft/spyglass_reports/rme/mbist-dft/

atrenta_modified_rtl_files/atrenta_generated_design.f

```

The designer has the option to collect all the modified files in a userspecified location with the command 'mb\_collect\_modified\_files':

```

mb_insert

mb_collect_modified_files <user specified directory>

```

```

NOTE: This is a post-insertion step.

```

## Verifying the Post-BIST Design

In this section, we discuss some steps for working with the post-BIST design.

## Viewing the Modified Design

It is useful to view the modified design in the schematic. A convenient way to accomplish this task is through the following steps:

- 1. Read the modified design as part of the standard design read process.

- Synthesize the design by running a pre-defined 'goal', such as GuideWare/New\_RTL/initial\_rtl/lint/synthesis.

- 3. View the synthesized design in SpyGlass Console.

The following two approaches are used to accomplish this:

Project file based

```

Create a project file as follows:

# file: test.prj

##Data Import Section

read_file -type sourcelist <project name>/mbist_dft/

spyglass_reports/rme/mbist-dft/

atrenta modified rtl files/atrenta generated design.f

##Common Options Section

set_option language_mode mixed

set option projectwdir .

set_option projectcwd .

set_option active_methodology $::SPYGLASS_HOME/

GuideWare/New RTL

##Goal Setup Section

current_goal initial_rtl/lint/synthesis -top top

Run spyglass to synthesize the design

spyglass -project test.prj -goal initial rtl/lint/

synthesis -batch

Invoke SpyGlass Console to view the design in the schematic

spyglass -project test.prj &

Tcl script based

Create a Tcl script as follows:

# File: test.tcl

set design top