# SpyGlass<sup>®</sup> Power Verify Rules Reference Guide

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

© 2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

## Contents

| Preface                                                  | 35 |

|----------------------------------------------------------|----|

| About This Book                                          | 35 |

| Contents of This Book                                    |    |

| Typographical Conventions                                |    |

|                                                          |    |

| Using the Rules in the SpyGlass Power Verify Solution    | 39 |

| Introduction to SpyGlass Power Verify                    | 40 |

| Low Power Design                                         | 41 |

| Running the SpyGlass Power Verify Solution               | 42 |

| Prerequisites for Running SpyGlass Power Verify          |    |

| Using Technology Library                                 |    |

| Supported Files in the SpyGlass Power Verify Solution    |    |

| Using Constraints in the SpyGlass Power Verify Solution  |    |

| Using Commands in the SpyGlass Power Verify Solution     |    |

| Using Parameters in the SpyGlass Power Verify Solution   |    |

| Using SpyGlass Power Verify Goals                        |    |

| Using Rule Mnemonics                                     |    |

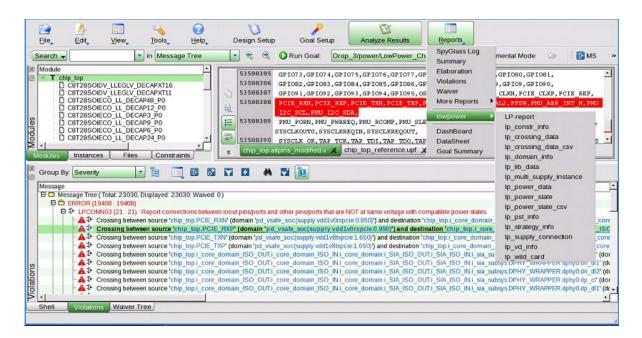

| Evaluating Results in the SpyGlass Power Verify Solution |    |

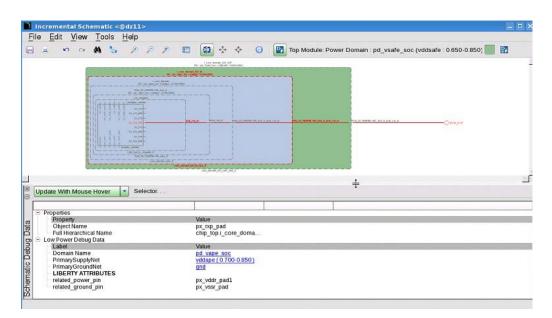

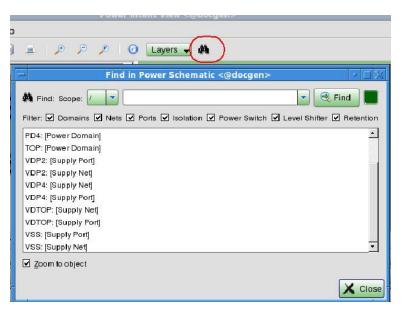

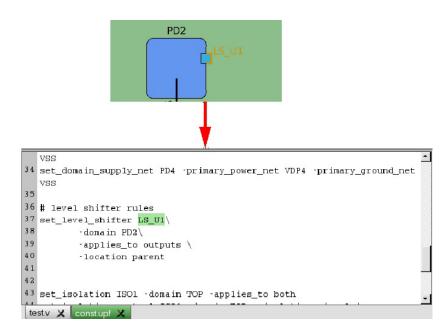

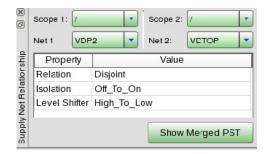

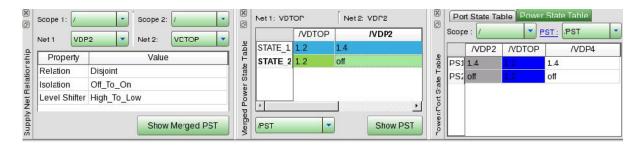

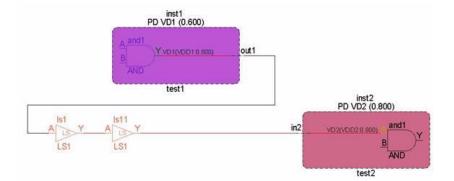

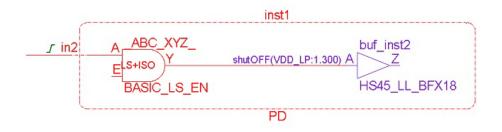

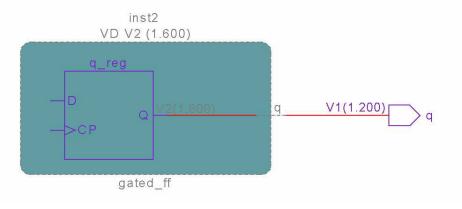

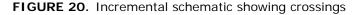

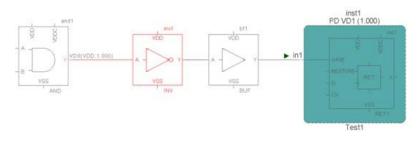

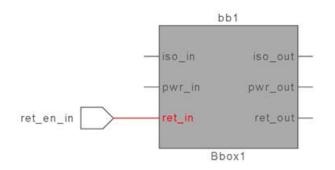

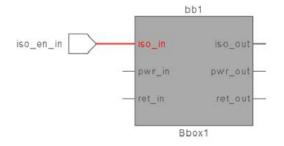

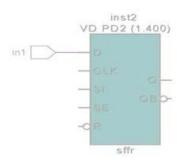

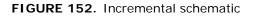

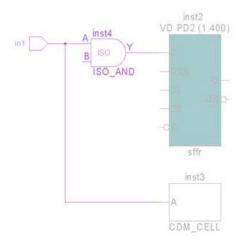

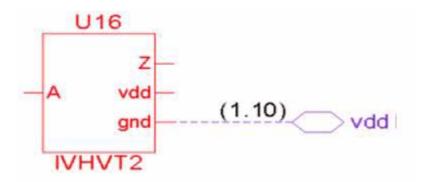

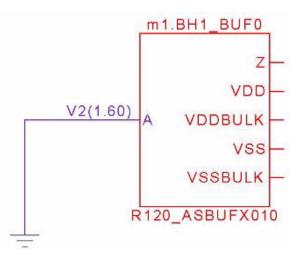

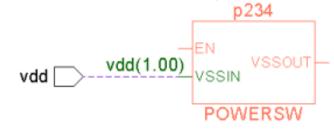

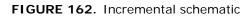

| Viewing Reports<br>Viewing Schematics                    |    |

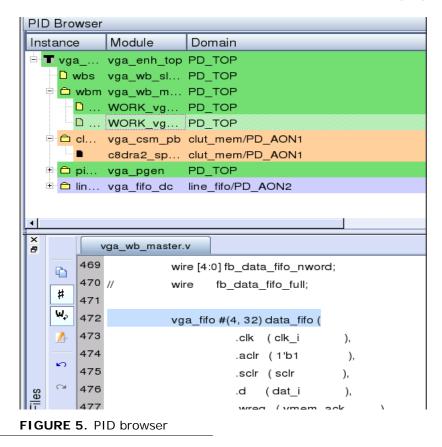

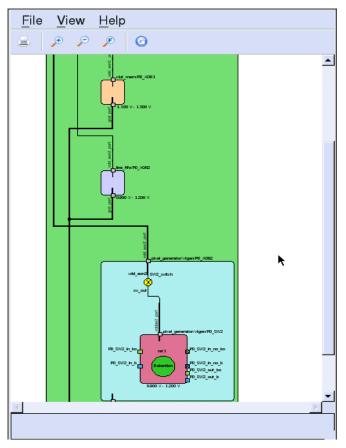

| Using the Power Intent View Window                       |    |

| Parameters in the SpyGlass Power Verify Solution         |    |

| lp_abstraction_config_file                               |    |

| lp_allow_check_name_format                               |    |

| lp_allow_force_shift_in_UPF1                             |    |

| lp_allow_iso_sig_from_equivalent_domain                  |    |

| lp_allow_parent_scope_supply                             |    |

| lp_allow_set_design_attr_in_UPF1                         |    |

| Ip_allow_UPF_21_commands_options                         |    |

| lp_allow_UPF_30_commands_options                         |    |

| Ip_allow_wildcard_in_UPF_2                               |    |

| lp_allow_pin_alias                                       |    |

| lp_apply_strategy_on_pwr_gnd                             |    |

| lp_block_abstraction_dir                                 |    |

| lp_bus_driver                             | .88 |

|-------------------------------------------|-----|

| lp_bus_receiver                           |     |

| lp_check_all_ps_in_daisy_chain            | .89 |

| lp_check_aob_on_control                   | .89 |

| lp_check_aon_buffer                       | .90 |

| Ip_check_control_path_of_fine_grain_psw   | .90 |

| lp_check_csn_on_internal_pg_pin           | .91 |

| lp_check_data_pin_of_els                  |     |

| Ip_check_domain_equivalence               | .92 |

| Ip_check_driver_receiver_supply           | .92 |

| lp_check_dual_enable_psw                  | .93 |

| lp_check_equally_on_supplies_for_aon_pins | .94 |

| lp_check_equivalent_domain_for_main_rail  | .94 |

| Ip_check_internal_pg_pin_connection       | .95 |

| Ip_check_ls_strategy_presence             | .95 |

| Ip_check_ls_supply_at_rtl                 | .96 |

| lp_check_enable_pin                       |     |

| lp_check_feedthrough_path                 | .97 |

| lp_check_hier                             | .98 |

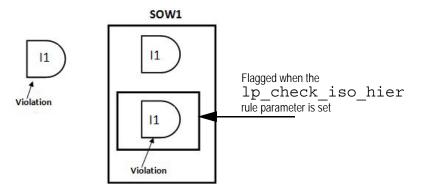

| lp_check_iso_hier                         | .98 |

| Ip_check_map_iso_cmd                      | 100 |

| lp_check_map_ls_cmd                       |     |

| lp_check_name_based_conflict              |     |

| Ip_check_ps_loc                           |     |

| Ip_check_pwr_gnd_to_macro_without_prd     | 102 |

| lp_check_pass_gate_on_pwr_gnd             | 103 |

| Ip_check_relative_aon_buffers             | 103 |

| lp_check_same_biasnet                     | 104 |

| <pre>lp_check_same_srsn_supply</pre>      | 104 |

| lp_check_same_voltage_path                | 105 |

| lp_check_src_driver_supply_name           | 105 |

| lp_check_valid_iso                        | 106 |

| lp_check_with_output                      |     |

| lp_complex_iso_logic                      |     |

| Ip_complex_level_shifter                  |     |

| lp_constant_els_as_iso_cell               |     |

| Ip_consider_inverted_output               |     |

| Ip_csn_on_ground_pg_pin                   |     |

| lp_disable_lib_attr_read                  |     |

| lp_dump_ls_in_multi_supply_rpt            |     |

| lp_dump_ps_in_multi_supply_rpt            | 111 |

| lp_dump_scope_supply_in_domain_info                    | 111 |

|--------------------------------------------------------|-----|

| lp_dump_unrelated_macro_cell_pgpin_in_multi_supply_rpt |     |

| lp_enable_buf_check                                    |     |

| lp_find_objects_match_count                            | 113 |

| lp_flag_iso_cell_in_crossing                           |     |

| lp_flag_iso_ls_strategy_on_domain_sub_hier             | 114 |

| lp_flag_iso_ls_crossing                                |     |

| lp_flag_ls_strategy_for_multi_fanout                   | 115 |

| lp_flag_missing_wildcard_in_set_retention              |     |

| lp_flag_missing_power_switch_lib                       | 116 |

| lp_flag_missing_timing_arc_on_pin                      | 117 |

| lp_flag_multi_elements_in_create_power_domain          | 117 |

| lp_flag_pd_outputs                                     | 118 |

| lp_flag_rtlc_cell                                      | 118 |

| lp_flag_unconnected_nets                               | 119 |

| lp_flag_undriven_nets                                  |     |

| lp_flag_violation_on_antenna_cell                      | 121 |

| lp_gen_block_abstraction_format                        | 121 |

| lp_gen_block_abstraction_in_bit_blasted_way            | 122 |

| lp_generate_missing_csn_violation                      | 122 |

| lp_genvcdfile                                          | 123 |

| lp_hdlin_enable_upf_compatible_naming                  | 123 |

| lp_hdlin_sv_union_member_naming                        | 124 |

| lp_ignore_b2b_ls                                       | 125 |

| lp_ignore_input_isolation_for_inout                    | 125 |

| lp_ignore_isocell                                      |     |

| lp_ignore_same_voltage_error                           | 126 |

| lp_ignore_seqelem_retencell                            | 127 |

| lp_ignore_SGDC_rules                                   |     |

| lp_ignore_tc_commands                                  | 128 |

| Ip_is_common_ground                                    | 128 |

| lp_is_gate_level                                       | 129 |

| lp_islc                                                | 129 |

| lp_iso_module_name                                     |     |

| lp_isologic_in_pd                                      | 130 |

| Ip_match_location_by_domain                            |     |

| lp_match_iso_cell_type_with_clamp_value                |     |

| lp_max_blackbox_percentage                             | 133 |

| lp_max_pins_viol                                       |     |

| lp_max_psw_fanout_count                                |     |

| lp_max_retention_cell_percentage                       | 135 |

|                                                        |     |

| lp_max_viol_count                                           | 135 |

|-------------------------------------------------------------|-----|

| lp_min_number_of_bits_for_latching                          | 136 |

| lp_min_size_of_comparator                                   | 136 |

| lp_output_pg_pin_as_supply_port                             | 138 |

| lp_pg_direction_as_supply_port                              | 139 |

| lp_pg_type_as_supply_port                                   | 139 |

| Ip_pst_merge_no_caching                                     | 140 |

| lp_pst_merge_new                                            | 141 |

| lp_read_powerdata_at_setup                                  | 141 |

| Ip_relative_aon_checking                                    | 142 |

| lp_report_all_wildcards                                     | 142 |

| lp_report_domain_crossing_on_iso_signal                     | 143 |

| lp_report_upf_command_in_source_file                        |     |

| Ip_report_missing_ack_port_option                           | 144 |

| lp_report_drc_blockgroup_for_missing_csn                    |     |

| lp_report_port_state_on_non_supply_port                     | 145 |

| lp_set_abstract_power_model_name                            | 145 |

| lp_set_design_stage                                         | 146 |

| lp_set_sim_val_x                                            | 146 |

| Ip_single_supply                                            | 147 |

| lp_set_upf_attributes                                       | 147 |

| lp_sig_viol_count                                           |     |

| lp_skip_aon_buf                                             | 149 |

| Ip_skip_blackbox_checking                                   |     |

| lp_skip_buf                                                 |     |

| lp_skip_existence_check_for_resolve_parallel_net            |     |

| lp_skip_combo_cell_for_reference_toplevel_isolation_signal  |     |

| lp_skip_existence_check_for_virtual_supply_net_without_srsn |     |

| lp_skip_feedthrough_buffer                                  |     |

| lp_skip_iso_check_on_ground                                 |     |

| lp_skip_lib_buf                                             |     |

| lp_skip_related_pgpin_checking_for_analog_pin               |     |

| lp_skip_same_src_supply_buf                                 |     |

| lp_skip_pwr_gnd                                             |     |

| lp_support_highconn_lowconn                                 |     |

| lp_support_ldo_net                                          |     |

| lp_support_unified_naming_style                             |     |

| Ip_switch_selective_out                                     |     |

| lp_treat_equivalent_psw_output_supplies_different           |     |

| lp_use_equivalence_in_pst                                   |     |

| Ip_use_inferred_clocks                                      | 162 |

| lp_use_inferred_resets                                          |     |

|-----------------------------------------------------------------|-----|

| lp_use_voltage_map_value                                        | 163 |

| lp_vcdendtime                                                   |     |

| lp_vcdminclk                                                    |     |

| lp_vcdstarttime                                                 |     |

| lp_vcdtopname                                                   |     |

| lp_wildcard_report_count                                        |     |

| lp_write_sgdc                                                   | 166 |

| SpyGlass Power Verify Reports                                   | 168 |

| Ip_assertion_info                                               |     |

| lp_autofix_info                                                 | 170 |

| lp_constr_info                                                  |     |

| lp_cons_req                                                     |     |

| lp_crossing_data                                                |     |

| lp_domain_info                                                  |     |

| lp_lib_data                                                     |     |

| lp_multivtreport                                                |     |

| lp_multivt_perblock                                             |     |

| lp_nested_domain_info                                           |     |

| Ip_power_data                                                   |     |

| Ip_power_state                                                  |     |

| lp_pst_merge_message                                            |     |

| lp_psw_info                                                     |     |

| lp_ret_info                                                     |     |

| lp_related_pin_data_for_consistency_check                       |     |

| lp_retention_cell_list                                          |     |

| lp_srsn_info                                                    |     |

| lp_supply_connection                                            |     |

| lp_vd_info                                                      |     |

| lp_wild_card<br>The LP-report Report                            |     |

| lp_strategy_info                                                |     |

| Ip_multi_supply_instance                                        |     |

| Ip_special_pin_connection                                       |     |

|                                                                 |     |

| Rules in SpyGlass Power Verify                                  |     |

| Rule Severity Classes                                           | 219 |

| Rule Categories                                                 |     |

| Level Shifter Rules                                             |     |

| LPPLIB04 : Reports level shifters which are connected to improp |     |

| signals223                                                                          |

|-------------------------------------------------------------------------------------|

| LPPLIB05 : Reports cells connected to level shifters that have incorrect            |

| power connections232                                                                |

| LPPLIB07 : Reports improper ground connection of the level shifters 238             |

| LPPLIB08 : Reports gates of enable signal of level shifters, supplied with a        |

| different voltage domain                                                            |

| <b>LPLSH01</b> : Reports level shifter cells that are not defined properly252       |

| LPLSH02 : Reports voltage range mismatch between level shifter cell and             |

| source/destination domains                                                          |

| LPLSH03 : Reports excluded signals having voltage difference which                  |

| requires level shifter                                                              |

| <b>LPLSH04</b> : Reports redundant level shifter strategy specified on a crossing,  |

| where either a level shifter is not required or more than one                       |

| sufficient level shifter strategies are specified                                   |

| <b>LPLSH05</b> : Reports missing and incorrect level shifter strategies for voltage |

| difference crossings                                                                |

| <b>LPLSH05A</b> : Reports missing and incorrect level shifter strategies for low-   |

| to-high voltage difference crossings                                                |

| LPLSH05B : Reports missing and incorrect level shifter strategies for high          |

| to low voltage difference crossings                                                 |

| LPLSH06 : Checks level shifter compatibility with main rail of cell 290             |

| <b>LPLSH07</b> : Checks the voltage range of level shifter cells with reference to  |

| source and destination domains                                                      |

| LPLSH08 : Checks the level shifter cell location with respect to the                |

| std_cell_main_rail attribute at the RTL level                                       |

| LPSVM04 : Checks for presence of level shifters in all voltage domain               |

| crossings                                                                           |

| <b>LPSVM04A</b> : Reports level shifters in voltage domain crossings from lower     |

| voltage domain to higher voltage domain                                             |

| <b>LPSVM04B</b> : Reports level shifters in voltage domain crossings from higher    |

| voltage domain to lower voltage domain                                              |

| LPSVM04C : Reports inadvertently used level shifters in the design 334              |

| <b>LPSVM04D</b> : Checks location of level shifters based on information specified  |

| in power format files                                                               |

| LPSVM04E : Checks location of level shifters based on main supply rail              |

| specified with 'std_cell_main_rail' attribute                                       |

| LPSVM17 : Reports multiple instances of the same level shifter                      |

| LPSVM24 : Reports enable of a level shifter that does not belong to an              |

| always-on domain357                                                                 |

| LPLIB_check04 : Checks input/output voltage range of                                                 | level-shifter cells. |

|------------------------------------------------------------------------------------------------------|----------------------|

| 362                                                                                                  |                      |

| Isolation Logic Rules                                                                                |                      |

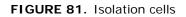

| LPISO01 : Reports unused isolation cells in the design                                               |                      |

| LPISO02 : Checks isolation cell location in the design on                                            | the basis of its     |

| supply pins                                                                                          |                      |

| LPISO03 : Checks the presence of isolation cell at output                                            | t terminals of       |

| power-domain                                                                                         |                      |

| LPISO03A : Reports missing isolation cell at output terr                                             | ninals of power      |

| domain, not having any isolation strategy                                                            |                      |

| LPISO03B : Reports non-existence of isolation cell at ex                                             |                      |

| terminals of power domain                                                                            |                      |

| LPISO04 : Reports missing and incorrect isolation strate                                             |                      |

| <b>LPI SO04A</b> : Reports missing isolation strategy at power                                       | •                    |

| ports                                                                                                | •                    |

| LPISO04B : Reports incorrect isolation strategy at powe                                              |                      |

| ports                                                                                                | •                    |

| <b>LPISO04C</b> : Checks isolation strategy for incorrect isolat                                     |                      |

| isolation_ground_net                                                                                 |                      |

| LPISO04D : Reports standard isolation cell that cannot k                                             |                      |

| 423                                                                                                  |                      |

| <b>LPISO05</b> : Checks for redundant isolation strategy at pov                                      | vor domain output    |

| ports                                                                                                |                      |

| LPISO05A : Checks for cases where isolation is not requ                                              |                      |

| 429                                                                                                  | illeu ior all patris |

| LPI SO05B : Checks for cases where isolation is needed for                                           | rationations nath    |

| but is not required for other paths                                                                  |                      |

| <b>LPISO06</b> : Checks if enable pin of isolation cell is tied to                                   |                      |

| not                                                                                                  |                      |

|                                                                                                      |                      |

| LPISOO6A : Reports an error when the enable pin of an i tied to an isolating value                   |                      |

|                                                                                                      |                      |

| LPISOO6B : Reports an informational message when the<br>isolation cell is tied to an isolating value |                      |

| <b>LPISO07</b> : Checks if the clamp value provided in isolation                                     |                      |

| with the constant value reaching at the eleme                                                        |                      |

| strategy                                                                                             |                      |

| <b>LPSVM08</b> : Checks for the presence of correct isolation of                                     |                      |

|                                                                                                      | •                    |

| domain output crossings                                                                              |                      |

| LPSVM08A : Checks for correct isolation logic of various                                             | power domains in     |

| the design457                                                                        |

|--------------------------------------------------------------------------------------|

| <b>LPSVM08B</b> : Reports missing isolation cell at output terminals of power        |

| domain, not having any isolation strategy                                            |

| LPSVM08C : Reports non-existence of isolation cell at excluded output                |

| terminals of power domain                                                            |

| LPSVM09 : Checks if power domain output attains the specified value in               |

| power down condition                                                                 |

| <b>LPSVM10</b> : Displays values on the output of power domain under shutdown        |

| condition                                                                            |

| LPSVM12 : Isolation signal should be a state signal and in always-on                 |

| domain                                                                               |

| <b>LPSVM12A</b> : Checks that the isolation signal always comes from an always-      |

| on domain                                                                            |

| <b>LPSVM12B</b> : Ensures that the isolation signal is always a state signal 502     |

| <b>LPSVM15</b> : Reports power domains that have multiple enable signals 505         |

| LPSVM22 : Reports inadvertently used isolation cells in the design 508               |

| <b>LPSVM26</b> : Checks whether logic cells in the power domain in feedthrough       |

| between two voltage domain crossings exist                                           |

| <b>LPSVM28</b> : Checks if the net attains the specified value in power down         |

| condition                                                                            |

| <b>LPSVM31</b> : Reports isolation cells that do not receive a steady state value    |

| in the power down condition530                                                       |

| <b>LPSVM47</b> : Reports power domain inputs that do not attain the specified        |

| value in power down condition                                                        |

| <b>LPSVM48</b> : Reports cells other than isolation cells used at the input-side and |

| output-side of the power domain                                                      |

| LPSVM50 : Reports incorrect instances at the input stage of a power domain           |

| 547                                                                                  |

| LPSVM51 : Reports isolation cells that are not transparent in power up               |

| mode                                                                                 |

| <b>LPSVM52</b> : Reports clock nets going into the power domain are feeding an       |

| instance of another domain555                                                        |

| <b>LPSVM55</b> : Reports isolation cells not present at a specific location in the   |

| hierarchy558                                                                         |

| LPSVM60 : Reports power domain inputs that are not isolated                          |

| <b>LPLIB_check01</b> : Reports isolation cells that have ambiguous or undefined      |

| enable pins                                                                          |

| LPLIB_check02 : Checks for missing related_power_pin/                                |

| related_ground_net attribute in library for signal pin576                            |

| LPLIB_c              | check03 : Checks the isolation_enable_condition attribute in library                             |

|----------------------|--------------------------------------------------------------------------------------------------|

|                      | for a signal pin580                                                                              |

|                      | gic Rules584                                                                                     |

| LPAONO               | <b>1</b> : Reports constant values reaching the input pin of always-on buffer                    |

| LPAONO               | <b>12</b> : Reports issues with always-on paths specified using the always_on_path constraint    |

|                      | <b>11</b> : Reports signals that are not connected or incorrectly connected to always-on buffers |

| LPSVM5               | <b>3</b> : Reports the always-on cell pins that are not driven by an always-on domain            |

| LPSVM5               | 4 : Reports always-on cells that are not present in specified domain 602                         |

| LPSVM4               | <b>O</b> : Reports the connectivity of special signals with always-on buffers                    |

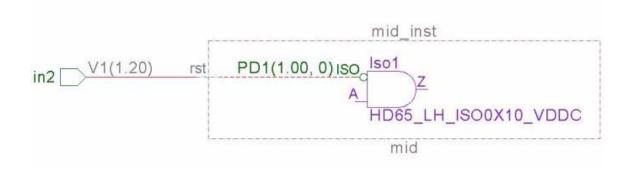

| State Retention      | on Rules612                                                                                      |

| LPPLI B <sup>2</sup> | <b>10</b> : Reports incorrectly connected power pins of SRPG cells 613                           |

| LPSVM3               | <b>8</b> : Checks the presence of SRPG cell in the specified hierarchy 619                       |

| LPSVM5               | 6 : Check for the presence of always-on buffers in the path of sleep signal                      |

| LPSVM5               | <b>6A</b> : Checks for always-on buffers in the always-on domain 629                             |

| LPSVM5               | <b>6B</b> : Check for always-on buffers in the path of retention control signals                 |

| LPSVM5               | <b>7</b> : Reports incorrectly connected control pins of retention cells638                      |

| LPSVM5               | 8 : Generate an OVL assertion file for clock input to retention cells 643                        |

| LPSVM5               | <b>9</b> : Checks whether control pins of retention cells attain the specified value             |

|                      | 1 : Checks if percentage of retention cells in sequential elementsexceeds the set limit          |

|                      | 2 : Checks conflicting values of save/restore signals in retention strategies                    |

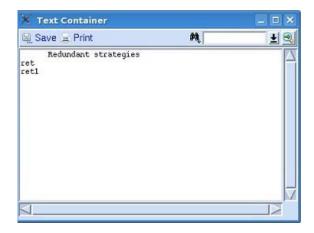

| LPRETO               | <b>3</b> : Reports partially or fully redundant strategies                                       |

| LPRETO               | <b>3A</b> : Reports if a retention strategy is applied on an always-on domain                    |

| LPRETO               | <b>3B</b> : Reports if multiple retention strategies are applied on the same retention element   |

| LPRETO               | 4 : Reports power domains with partially or completely missing retention strategies              |

| <b>LPRET04A</b> : Reports if a switching domain does not have a retention                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| strategy                                                                                                                                                                  |

| Connection Rules                                                                                                                                                          |

| LPCONNO1 : Reports output or input of special cells that are hanging or tied                                                                                              |

| to constant671                                                                                                                                                            |

| LPCONNO2 : Reports domain anomalies                                                                                                                                       |

| LPCONNO3 : Reports connections between inout pins/ports and other pins/<br>ports that are not at the same voltage with compatible power<br>states                         |

| LPCONNO4 : Checks control signals of retention cells, power switches, and                                                                                                 |

| isolation cells                                                                                                                                                           |

| LPCONNO4A : Checks if the source of the control signal is off when                                                                                                        |

| compared to the receiver                                                                                                                                                  |

| <b>LPCONNO4B</b> : Checks the source of control signal and destination of power-                                                                                          |

| switch acknowledge signal                                                                                                                                                 |

| its source                                                                                                                                                                |

| <b>LPCONNO4D</b> : Checks the continuity of the control signals across black                                                                                              |

| boxes and buffers                                                                                                                                                         |

| LPCONNO4E : Checks the connectivity of retention control signals723                                                                                                       |

| LPCONN05 : Checks the supply relationship of source, destination and logic cells (between source and destination) on the clock/reset signal path730                       |

| <b>LPCONN05A</b> : Checks if the primary clock/reset in the SGDC file is not                                                                                              |

| connected to any clock/reset pin                                                                                                                                          |

| LPCONN05B : Checks if the supply of primary source of clock/reset signal<br>is relatively-more or equally-on than the supply of each of the<br>logic cells in the path734 |

| <b>LPCONN05C</b> : Checks if the supply of a logic cell present in clock/reset path                                                                                       |

| is relatively-more or equally-on than the supply of destination                                                                                                           |

| flip-flop                                                                                                                                                                 |

| <b>LPCONNO6</b> : Reports connections from the ON domain to input/inout pins/<br>ports of the OFF domain with the pass-gate attribute741                                  |

| LPCONNO7 : Checks for feedthrough paths                                                                                                                                   |

| <b>LPCONNO7A</b> : Checks of reedth ough paths                                                                                                                            |

| <b>LPCONN07B</b> : Checks for set_related_supply_net on boundary ports in                                                                                                 |

| feedthrough paths749                                                             |

|----------------------------------------------------------------------------------|

| <b>LPCONNO8</b> : Reports presence/absence of lockup latches between two flip-   |

| flops existing in different voltage domains but driven by                        |

| synchronous clocks                                                               |

| <b>LPCONN09</b> : Report presence/absence of charged device model (CDM) cells    |

| in crossings                                                                     |

| <b>LPSVM49</b> : Reports incorrect connections of power or ground signal pins of |

| cells to their supplies                                                          |

| LP_SPECIAL_PIN_CONNECTION : Generates report that shows special                  |

| pin connections to ports                                                         |

| Supply Rules                                                                     |

| <b>LPPLIB06</b> : Reports incorrect connections to power and voltage domains     |

| 771                                                                              |

| LPPLIB13 : Reports supplies associated with special cells are                    |

| inappropriately connected                                                        |

| <b>LPPLIB14</b> : Reports signal pins that have improperly connected supply nets |

|                                                                                  |

| <b>LPPLIB15</b> : Reports incorrect connections of the ground pin to the ground  |

| supply                                                                           |

| <b>LPPLIB16</b> : Ensures connection of tie low/high to correct voltage domain . |

| 804                                                                              |

| <b>LPPLIB17</b> : Checks if all the power switches in the design are correctly   |

| connected                                                                        |

| <b>LPPLIB18</b> : Ensure correct connections of bias power/ground pins to bias   |

| power/ground supply respectively                                                 |

| <b>LPPLIB18A</b> : Ensures correct connections of bias power pin to bias power   |

| supply                                                                           |

| <b>LPPLIB18B</b> : Ensures correct connections of bias ground pin to bias ground |

| supply                                                                           |

| <b>LPPLIB19</b> : Checks whether bias net is always-on with respect to power net |

| 832                                                                              |

| <b>LPPLIB19A</b> : Checks whether the bias_net is less always-on than the power  |

| net                                                                              |

| LPPLIB20 : Checks whether library cell instantiated in design is used out of     |

| place                                                                            |

| <b>LPSUP01 :</b> Reports standard cells that drive supply nets                   |

| <b>LPSUP03</b> : Checks for consistency between supply net specified for leaf    |

| level signal pins and the related power and ground pin 842                       |

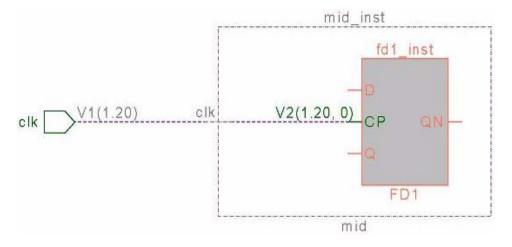

| Automatic Fix Rules                                                              |

|                                                                                  |

| LPSVM23 : AutoFix missing isolation logic                                        |

|----------------------------------------------------------------------------------|

| LPSVM30 : Generates new level shifters for Verilog RTL description 850           |

| Fine Grain Power Gate (MTCMOS) Rules                                             |

| LPSVM33 : Reports non-High VT cell instances in the fan-out cone854              |

| LPSVM33A : Checks for non-high VT cells in a power domain                        |

| LPSVM34 : Reports non-high VT cells identified in the fan-in cone of             |

| retention latch cells860                                                         |

| LPSVM35 : Reports MTCMOS cell instances with outputs that are incorrectly        |

| isolated863                                                                      |

| LPSVM36 : Reports potential sneak leakage paths due to incorrect MTCMOS          |

| cells                                                                            |

| Best Design Practices                                                            |

| LPBUS01 : This rule has been deprecated872                                       |

| LPBUS02 : This rule has been deprecated                                          |

| LPBUS03 : This rule has been deprecated                                          |

| LPFSM01 : This rule has been deprecated                                          |

| LPFSM02 : This rule has been deprecated                                          |

| LPFSM03 : This rule has been deprecated                                          |

| LPFSM04 : This rule has been deprecated                                          |

| LPFSM09 : This rule has been deprecated                                          |

| LPFSM20 : This rule has been deprecated                                          |

| LPGLT01 : This rule has been deprecated                                          |

| LPXFM01 : This rule has been deprecated                                          |

| LPXFM06 : This rule has been deprecated                                          |

| Special Purpose Rules                                                            |

| LPPLIB12 : Reports incorrectly connected RAM switches in RTL and gate-           |

| level netlist                                                                    |

| <b>LPPSW01</b> : Checks the domain of the signal reaching the input enable of a  |

| power switch                                                                     |

| <b>LPPSW02</b> : Checks the connectivity of the signal reaching the input enable |

| of the power switch                                                              |

| enable pin of a power switch                                                     |

| <b>LPPSW04</b> : Ensures that the enable signal of a power switch has only AON   |

| buffers or delay buffers in its path                                             |

| <b>LPSVM29</b> : Generates design-level and hierarchical reports                 |

| <b>LPSVM37</b> : Checks for special cells in specified regions                   |

| <b>LPSVM41</b> : Reports registers that are not in their power down chain927     |

|                                                                                  |

| LP3VIVI42                                                                                                      | : Checks to ensure low power signals coming up correctly out of power on reset |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                                                                                                                | : Reports incorrect power up and power down sequences of power                 |

|                                                                                                                | domains                                                                        |

| LPSVM44                                                                                                        | : Reports user-specified signals that are incorrectly connected                |

|                                                                                                                | 940                                                                            |

| LPSVM45                                                                                                        | : Checks for the correct enable logic in a power switch for the gate           |

|                                                                                                                | level and PG netlist                                                           |

| LPSVM46                                                                                                        | : Reports incorrect connections in a RAM switch                                |

| LPTIE01 :                                                                                                      | Checks the connections of the always-on normal Tie cells in a                  |

|                                                                                                                | design                                                                         |

| LPTIE02 :                                                                                                      | Reports the TIE cells that have isolation cells in their path958               |

| LP_BLACK                                                                                                       | <b>BOX_CHECK</b> : Checks if percentage of black box elements                  |

|                                                                                                                | exceeds the set limit                                                          |

| LP_MULTI                                                                                                       | <b>_DOMAIN_CROSSING_CHECK</b> : Ensures that signal paths do                   |

|                                                                                                                | not have combinational cells in more than two different domains                |

|                                                                                                                | 965                                                                            |

| LP_INTER                                                                                                       | MEDIATE_DOMAIN_CROSSING_CHECK : Checks if a                                    |

|                                                                                                                | crossing between source and destination is going through a                     |

|                                                                                                                | feedthrough less-on domain                                                     |

|                                                                                                                |                                                                                |

| Powerdata Che                                                                                                  | king Rules973                                                                  |

|                                                                                                                | <b>RDATA_CHECK</b> : Reports multiple power formats                            |

| LP_POWE                                                                                                        | 5                                                                              |

| LP_POWE                                                                                                        | <b>RDATA_CHECK</b> : Reports multiple power formats                            |

| LP_POWE<br>LP_POWE                                                                                             | <b>RDATA_CHECK</b> : Reports multiple power formats                            |

| LP_POWE<br>LP_POWE                                                                                             | <b>RDATA_CHECK :</b> Reports multiple power formats                            |

| LP_POWE<br>LP_POWE<br>LP_POWE                                                                                  | <b>RDATA_CHECK :</b> Reports multiple power formats                            |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report                                                               | <b>RDATA_CHECK</b> : Reports multiple power formats                            |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report                                                               | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI                                                   | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS                                       | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS                                       | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D                           | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D                           | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D<br>LPWildCar              | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D<br>LPWildCar              | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D<br>LPWildCan<br>PairWiseV | RDATA_CHECK : Reports multiple power formats                                   |

| LP_POWE<br>LP_POWE<br>LP_POWE<br>Detailed Report<br>LP_DECOI<br>LP_CROSS<br>LP_LIB_D<br>LPWildCan<br>PairWiseV | RDATA_CHECK : Reports multiple power formats                                   |

| LP_ISO_REPORT : Generates spreadsheet for supported rules related to              |

|-----------------------------------------------------------------------------------|

| isolation strategy and isolation cells                                            |

| LP_LSH_REPORT : Generates spreadsheet for supported rules related to              |

| level shifter strategy and level shifter cells                                    |

| Constraints Checking Rules 1011                                                   |

| LP_CHECK_CONSTR : Validates information specified for level shifter,              |

| isolation and retention cells with respect to information specified               |

| in library using attributes                                                       |

| LP_SGDC_CHECKS : Checks the existence of cells specified with                     |

| cell_hookup and aon_buffered_signals                                              |

| LpParamSanityCheck : Performs syntactic checks on parameters 1025                 |

| <b>SGDC_lowpower05</b> : Reports the voltage_domain constraints specified         |

| without the required arguments                                                    |

| <b>SGDC_lowpower06 :</b> Reports instances that are not separated by space . 1030 |

| SGDC_lowpower07 : Reports inconsistent specification of isoval or inisoval        |

| in voltage_domain1032                                                             |

| SGDC_lowpower09 : Reports when same instance is used in more than                 |

| one voltage_ domain constraint                                                    |

| <b>SGDC_lowpower12</b> : Reports redundant arguments in the voltage_domain        |

| constraints                                                                       |

| <b>SGDC_lowpower15</b> : Reports power domains with at least one of the three     |

| arguments, isosig, inisosig, and noisosig, missing                                |

| the generate_iso_logic argument for power domains 1043                            |

| SGDC_lowpower18 : Reports when the outputs argument is defined with               |

| a value that does not match any of the defined domain_outputs                     |

| names                                                                             |

| SGDC_lowpower19 : Reports supply names not defined through the                    |

| supply constraint                                                                 |

| SGDC_lowpower23 : Reports incomplete -value argument specification in             |

| domain_outputs1051                                                                |

| SGDC_lowpower24 : Reports incorrect voltage domains specified with to/            |

| from arguments of the levelshifter constraint                                     |

| SGDC_lowpower30 : Reports signal names repeated in the signal list of             |

| value argument of domain_outputs                                                  |

| SGDC_lowpower31 : Reports incorrectly defined tops                                |

| SGDC_lowpower32 : Performs an existence check of the power-out and                |

| power-in terminal of power switch                                                 |

| SGDC_lowpower40 : Performs sanity check for the existence of the                     |

|--------------------------------------------------------------------------------------|

| domains argument of retention_cell                                                   |

| SGDC_lowpower47 : Reports non-existent pins specified with vddpin/                   |

| vddcpin arguments of retention cell                                                  |

| SGDC_lowpower48 : Reports incorrect values specified in the sequalue                 |

| argument of domain_signal 1070                                                       |

| SGDC_lowpower52 : Flags if -noisosig have been specified with -isosig or             |

| -inisosig field for the power domain                                                 |

| SGDC_lowpower59 : Reports non-existent terminals specified with                      |

| enableports of voltage_domain 1076                                                   |

| SGDC_lowpower60 : Reports non-existent objects specified with                        |

| ram_switch 1079                                                                      |

| <b>SGDC_lowpower61 :</b> Reports incorrectly defined input_isocell constraint . 1083 |

| SGDC_lowpower62 : Reports incorrectly defined cell_pin_info                          |

| specification 1086                                                                   |

| <b>SGDC_lowpower65</b> : Reports incorrect supply values                             |

| <b>SGDC_lowpower66</b> : Reports existence of the en_inv_in, en_inv_out and          |

| en_buf_in terminals of power switch 1092                                             |

| <b>SGDC_lowpower67</b> : Performs sanity checks for the terminals of a level         |

| shifter 1095                                                                         |

| <b>SGDC_lowpower68</b> : Reports incorrectly defined special_cell 1098               |

| SGDC_lowpower69 : Reports constraints specifications with multiple                   |

| design units defined as current designs 1101                                         |

| <b>SGDC_lowpower71</b> : Reports missing inTerm and outTerm for level shifter        |

|                                                                                      |

| SGDC_lowpower72 : Reports incorrect arguments specified for                          |

| pin_voltage                                                                          |

| SGDC_lowpower75 : Reports non-existent pins specified with '-names'                  |

| argument of pin_voltage constraint 1109                                              |

| <b>SGDC_lowpower77</b> : Reports repetition of cells specified in the                |

| always_on_pin constraint                                                             |

| <b>SGDC_lowpower78</b> : Reports incorrectly specified cell_tie_class 1115           |

| <b>SGDC_lowpower82</b> : Reports incorrect sleep, save, and restore signal           |

| specifications                                                                       |

| <b>SGDC_lowpower85</b> : Reports incorrectly specified stopclockval of               |

| voltage_domain                                                                       |

| <b>SGDC_lowpower86</b> : Reports incorrectly specified clkval argument of            |

| retention_cell 1127                                                                  |

| <b>SGDC_lowpower87</b> : Reports incorrect arguments of the supply constraint 1129     |

|----------------------------------------------------------------------------------------|

| <b>SGDC_lowpower89</b> : Reports incorrect voltage domain specified in the -to         |

| or -from argument of ignore_crossing 1134                                              |

| SGDC_lowpower90 : Checks the usage of voltage_domain and                               |

| retention_cell while running the LPSVM58 rule 1138                                     |

| SGDC_lowpower91 : Reports if steady-state condition names is not                       |

| correctly specified 1142                                                               |

| SGDC_lowpower92 : Performs an existence check of power down                            |

| condition name 1144                                                                    |

| SGDC_lowpower93 : Checks incorrectly defined level shifter 1147                        |

| SGDC_lowpower94 : Reports incorrectly specified power_state 1151                       |

| <b>SGDC_lowpower95</b> : Checks the validity of the -tie1 and -tie0 arguments          |

| of cell_tie_class1156                                                                  |

| SGDC_lowpower96 : Reports non-existent modules specified in level                      |

| shifter                                                                                |

| SGDC_lowpower97 : Reports incorrectly defined constraints when the                     |

| LPSVM59 rule is run 1161                                                               |

| SGDC_lowpower98 : Reports incorrectly specified pin in the -pin                        |

| argument of input_isocell                                                              |

| <b>SGDC_lowpower99</b> : Reports invalid power domain specified by the -               |

| belongsto argument of isolation_cell                                                   |

| SGDC_lowpower100 : Reports incorrectly specified domain name in the                    |

| power_down constraint                                                                  |

| SGDC_lowpower101 : Reports if the -vddcpin argument is not specified in retention_cell |

|                                                                                        |

| SGDC_lowpower103 : Checks for missing arguments in domain_outputs constraint           |

| SGDC_lowpower104 : Reports incorrectly specified VDDC pin in                           |

| always_on_buffer                                                                       |

| SGDC_lowpower105 : Reports if the –names argument is not specified in                  |

| isolation_cell                                                                         |

| SGDC_lowpower107 : Checks the existence of pins specified in the -                     |

| inTerm, -outTerm, and -enableTerm arguments of level shifter                           |

| 1180                                                                                   |

| <b>SGDC_lowpower108</b> : Checks if pins specified with the arguments of               |

| isolation_cell exist in the design                                                     |

| <b>SGDC_lowpower109</b> : Reports when the number of values specified in the           |

| -signame and -value arguments of power_down are not same                               |

1188

| <b>SGDC_lowpower110</b> : Checks to ensure retention_instance lies in the hierarchy of a power domain                                 |

|---------------------------------------------------------------------------------------------------------------------------------------|

| SGDC_lowpower112 : Checks the -vddcpin and -vddpin arguments of<br>retention_cell                                                     |

| SGDC_lowpower113 : Reports missing inisosig argument of voltage_domain                                                                |

| SGDC_lowpower114 : Reports power or ground bias nets of                                                                               |

| voltage_domain not specified as the power or ground supply<br>1198                                                                    |

| SGDC_lowpower115 : Reports when pins specified by using the                                                                           |

| arguments of power_switch are of improper types 1201                                                                                  |

| SGDC_lowpower116 : Reports the missing -name and -value arguments<br>of the voltage_domain constraint                                 |

| SGDC_lowpower118 : Performs the sanity check in the associate_lib                                                                     |

| constraint                                                                                                                            |

| <b>SGDC_lowpower119</b> : Performs the sanity checking for the                                                                        |

| disallow_upf_command and                                                                                                              |

| make_mandatory_upf_commands_options SGDC constraints<br>1209                                                                          |

| <b>SGDC_lowpower_RuleReq</b> : Reports missing constraints required by the                                                            |

| specified rules                                                                                                                       |

| SGDC_powerdomainoutputs01 : Reports non-existent signal names                                                                         |

| specified through domain_outputs                                                                                                      |

| SGDC_powerdomainoutputs02 : Reports incorrect value specification in                                                                  |

| domain_outputs 1216                                                                                                                   |

| <b>SGDC_supply01</b> : Reports supply constraint defined with a negative value 1218                                                   |

| SGDC_voltagedomain01 : Reports non-existent instances                                                                                 |

| <b>SGDC_voltagedomain02</b> : Reports non-existent modname                                                                            |

| SGDC_voltagedomainO3 : Reports non-existent port name                                                                                 |

| SGDC_voltagedomain04 : Reports non-existent signals specified in the                                                                  |

| isosig field 1226                                                                                                                     |

| <b>SGDC_voltagedomain05 :</b> Reports incorrect isoval specification 1228                                                             |

| <b>SGDC_voltagedomain06 :</b> Reports incorrect value specification 1230                                                              |

| <b>SGDC_voltagedomain07</b> : Reports incorrect value specification for power                                                         |

| domain                                                                                                                                |

| <b>SGDC_voltagedomain08</b> : Performs existence check of the clock signal specified by the clkdomain argument of voltage_domain 1235 |

| Electrical Checks Rules 1237                                                          |

|---------------------------------------------------------------------------------------|

| LPERC01 : Checks incompatibility between supply nets of driver and                    |

| receiver                                                                              |

| LPERC01A : Checks if supply net of the driver is operating at a different             |

| voltage than the supply net of the receiver                                           |

| <b>LPERC01B</b> : Checks if supply net of the driver is less-on than the supply net   |

| of the receiver                                                                       |

| <b>LPERCO1C</b> : Checks if supply net of driver is different or working at different |

| voltage than supply net of receiver and is less on than receiver                      |

| supply net                                                                            |

| switch and level shifters                                                             |

| <b>LPERCO2A</b> : Checks if the input supply net of the power switch is operating     |

| at a different voltage than the output supply net                                     |

| <b>LPERCO2B</b> : Checks if input supply net of level-shifter or power switch is      |

| less-on than the output supply net                                                    |

| <b>LPERCO3</b> : Checks incompatibility between backup power and primary              |

| power of a library cell                                                               |

| <b>LPERCO3A</b> : Checks relationship between supply nets connected to                |

| backup_power pin and primary_power pin                                                |

| <b>LPERC04</b> : Checks for connectivity in supply and signal pins of library cells   |

| in design                                                                             |

| LPERC04A : Checks power/ground supply pin connection with supply nets                 |

| 1269                                                                                  |

| LPERC04B : Checks if driver is an unconnected net, hanging net or is a                |

| supply net undefined in power intent                                                  |

| LPERC05 : Reports Analog signals which are driving or getting driven by               |

| digital logic                                                                         |

| <b>LPERCO6</b> : Reports power/ground nets that are connected to multiple inout/      |

| output power/ground pins                                                              |

| CPF Check Rules                                                                       |

| checkCPF_existence : Reports design objects, specified with CPF                       |

| commands, which do not exist                                                          |

| CPF_lowpower01 : Reports if a valid voltage value is not inferred for a power domain  |

| <b>CPF_lowpower03</b> : Reports unsupported unary expressions specified in            |

| CPF commands                                                                          |

| <b>CPF_lowpower04</b> : Reports the unavailability of switchable pin type             |

| information in define_power_switch_cell                                               |

| —, <b>—</b> —                                                                         |

| <b>CPF_lowpower05</b> : Reports if set_design is not specified or is specified   |

|----------------------------------------------------------------------------------|

| incorrectly for the top design unit 1304                                         |

| <b>CPF_lowpower07</b> : Reports create_isolation_rule commands that do not       |

| have either '-from' or '-to' 1307                                                |

| <b>CPF_lowpower09</b> : Checks to ensure that 'supply' is inferred properly from |

| CPF commands1309                                                                 |

| <b>CPF_lowpower10</b> : Checks the power switch mentioned in                     |

| update_power_switch_rule                                                         |

| <b>CPFSEM_2</b> : Checks the presence of the power domain in scope 1320          |

| <b>CPFSEM_3</b> : Checks if the default power domain is already present in scope |

| 1322                                                                             |

| <b>CPFSEM_4</b> : Checks if default power domain is not present in scope 1324    |

| <b>CPFSEM_5</b> : Checks the name conflict in the same scope                     |

| <b>CPFSEM_6</b> : Checks the presence of the nominal condition 1328              |

| <b>CPFSEM_7</b> : Checks the presence operating corner 1330                      |

| <b>CPFSEM_8</b> : Checks if library set is defined                               |

| <b>CPFSEM_10 :</b> Checks if a ground net is defined 1334                        |

| <b>CPFSEM_11 :</b> Checks the presence of power net                              |

| CPFSEM_12 : Checks the presence of bias net 1338                                 |

| <b>CPFSEM_13 :</b> Checks the presence of isolation rule 1340                    |

| <b>CPFSEM_14</b> : Checks the presence of level shifter rule 1342                |

| <b>CPFSEM_15</b> : Checks the presence of power mode 1344                        |

| <b>CPFSEM_17</b> : Checks the presence power switch rule                         |

| <b>CPFSEM_19</b> : Checks if set_design is preceded by a set_instance command    |

| 1348                                                                             |

| <b>CPFSEM_21</b> : Checks if set_design is specified for the current instance    |

| 1350                                                                             |

| <b>CPFSTX_1</b> : Checks if mutually exclusive options are specified 1352        |

| <b>CPFSTX_2</b> : Checks if at least one mandatory argument is specified 1354    |

| <b>CPFSTX_4</b> : Checks the presence of an invalid domain condition 1356        |

| <b>CPFSTX_5</b> : Checks the presence of a wrong array naming style 1358         |

| <b>CPFSTX_6</b> : Checks the presence of a wrong hierarchy delimiter 1360        |

| <b>CPFSTX_7</b> : Checks the presence of an invalid value                        |

| <b>CPFSTX_8</b> : Checks the presence of an invalid register naming style . 1364 |

| <b>CPFSTX_9</b> : Checks if the arguments are specified together 1366            |

| <b>CPFSTX_10</b> : Checks if wrong number of arguments are specified 1368        |

| <b>CPFSTX_11</b> : Checks if the specified value is out of range                 |

| <b>CPFSTX_13</b> : Checks if an invalid option is specified for command 1372     |

| CPFSTX_14 : Checks if no value is specified for argument                              |

|---------------------------------------------------------------------------------------|

| CPFSTX_15 : Checks if an invalid value type is specified                              |

| <b>CPFSTX_16</b> : Checks if an invalid value is specified for argument 1378          |

| CPFSTX_17 : Checks if a mandatory argument is missing                                 |

| <b>CPFSTX_19</b> : Checks the presence of a wildcard reference                        |

| <b>CPFSTX_20</b> : Checks the presence of hierarchical separator                      |

| CPFSTX_22 : Checks the presence of top design                                         |

| <b>CPFSTX_23</b> : Checks the presence of control group                               |

| CPFSTX_24 : Checks the presence of invalid commands in macro model                    |

| 1390                                                                                  |

| CPFSTX_25 : Checks the presence of macro model                                        |

| <b>CPFSTX_26</b> : Checks the presence of the specified file                          |

| <b>CPFSTX_27</b> : Checks the presence of the specified design                        |

| <b>CPFSTX_28</b> : Checks if an invalid command is specified in control group         |

| 1398                                                                                  |

| CPFSTX_29 : Checks if an invalid object name is specified                             |

| <b>CPFSTX_30</b> : Checks if an invalid group view is specified                       |

| <b>CPFSTX_31</b> : Checks the presence of an analysis view                            |

| <b>CPFSTX_32</b> : Checks if an incorrect argument format is specified in some        |

| switch of command                                                                     |

| <b>CPFSTX_33</b> : Checks if an incorrect design name is specified in end_design 1408 |

| <b>CPFSTX_34</b> : Checks if an incorrect model name is specified in                  |

| end_macro_model                                                                       |

| <b>CPFSTX_35</b> : Checks if set_macro_model is specified for the current block       |

| 1412                                                                                  |

| CPFSTX_36 : Checks if an unknown command is specified                                 |

| <b>CPFSTX_38</b> : Checks if power domain is visible inside control group 1416        |

| <b>CPFSTX_39</b> : Checks if control group is visible inside control group 1418       |

| <b>CPFSTX_40</b> : Checks if set_instance without instance name contains              |

| parameters1420                                                                        |

| <b>CPFSTX_41</b> : Checks the presence of a command outside set_macro_model           |

| and end_macro_model block 1422                                                        |

| CPFSTX_42 : Checks if power net is specified as power supply net to an                |

| always on power domain1424                                                            |

| UPF Check Rules 1426                                                                  |

| checkUPF_existence : Reports non-existent design objects specified with               |

| UPF commands                                                                          |

| UPF_lowpower01 : Reports if top design unit specified with the                        |

| set_design_top command does not match with current_design in SGDC               |

|---------------------------------------------------------------------------------|

| <b>UPF_lowpower02</b> : Checks relationship of power nets between               |

| set_domain_supply_net, connect_supply_net, and                                  |

| add_port_state commands                                                         |

| <b>UPF_lowpower03</b> : Reports unspecified default power domain for the top    |

| design unit                                                                     |