# SpyGlass<sup>®</sup> Lint Turbo Structural User Guide

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

© 2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at https://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

# Contents

| SpyGlass Lint Turbo Structural                                       | 7 |

|----------------------------------------------------------------------|---|

| Using the Turbo Flow                                                 | 8 |

| Turbo Initiatives                                                    |   |

| Rule-wise Initiatives                                                |   |

| erc1                                                                 |   |

| latch                                                                |   |

| lint1                                                                | 6 |

| miscellaneous2                                                       | 7 |

| morelint2                                                            | 9 |

| openmore                                                             | 0 |

| simulation4                                                          | 3 |

| starc                                                                |   |

| starc20024                                                           |   |

| starc2005                                                            |   |

| timing5                                                              |   |

| Turbo Parameter Settings 53                                          | 3 |

| Smart Rule Execution                                                 | 6 |

| Waiving Primary Messages in the Turbo Mode                           | 6 |

| Defining the Preferred Waiver Behavior5                              | 7 |

| The moresimple_turbo Report                                          | 9 |

| Known Problems                                                       | 2 |

| SauClass Functional Lint                                             | - |

| SpyGlass Functional Lint6                                            |   |

| Prerequisites for Using Turbo Functional Rules                       |   |

| Turbo Capabilities                                                   | 7 |

| Functional Lint to Lint Rule Mapping6                                | 7 |

| Generating Waivers for Structural Rules                              | 8 |

| The SpyGlass Functional Lint Rules                                   |   |

| Av_width_mismatch_assign : LHS width is less than RHS width of       | _ |

| assignment (Truncation)                                              | 3 |

| Av_width_mismatch_case : A case expression width does not match case |   |

| select expression width7                                             |   |

| Av_width_mismatch_port : An instance port connection has different   |   |

| width compared to the port definition                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Av_signed_unsigned_mismatch : Mixed signed and unsigned types93                                                                                    |

| Av_width_mismatch_expr : Bit-width of operands of a logical operator do not match                                                                  |

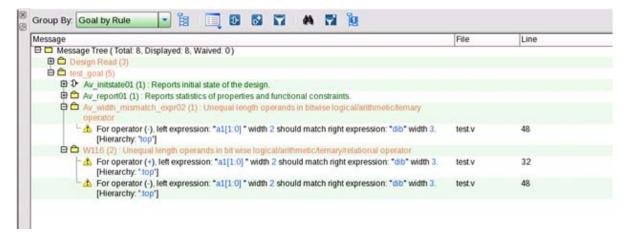

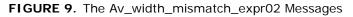

| Av_width_mismatch_expr02 : Av_width_mismatch_expr03 :                                                                                              |

| Reports an arithmetic comparison operator with unequal length                                                                                      |

| Av_case_default_redundant : Ensure that a case statement marked<br>full_case or a priority/unique case statement does not have a<br>default clause |

| Av_case_default_missing : Ensure that a case statement or a selected signal assignment has a default clause                                        |

| Av_dontcare_mismatch : Use of don't-care except in case labels may lead                                                                            |

| to simulation/synthesis mismatch                                                                                                                   |

| SauClass List Abstraction Flow                                                                                                                     |

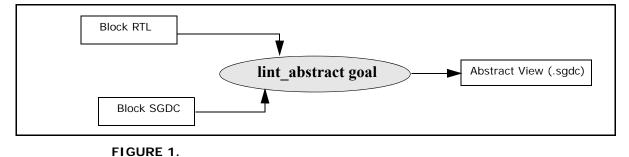

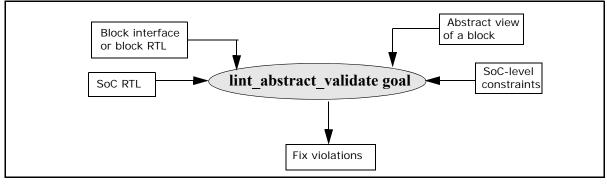

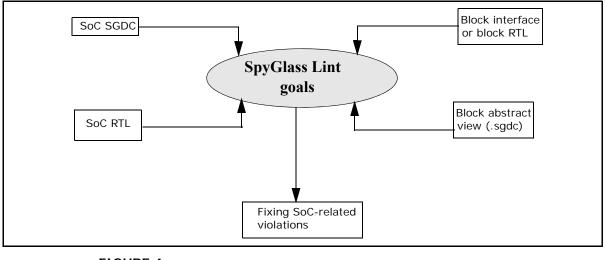

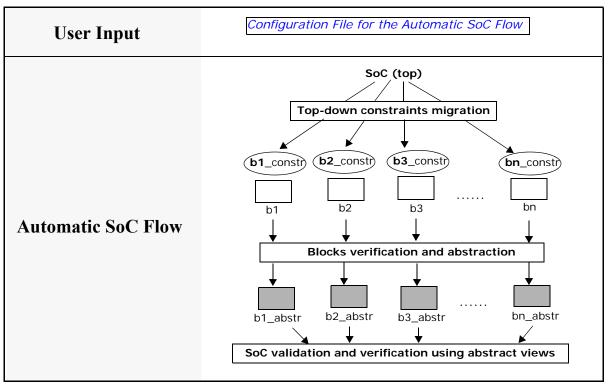

| SpyGlass Lint Abstraction Flow                           | 129 |

|----------------------------------------------------------|-----|

| Overview                                                 | 129 |

| Generating an Abstract View in SpyGlass Lint             |     |

| Validating Assumptions on Abstract View in SpyGlass Lint |     |

| Using the Abstract View in SpyGlass Lint                 |     |

| Using the Automatic SoC Flow in SpyGlass Lint            |     |

# SpyGlass Lint Turbo Structural

The SpyGlass Lint Turbo Structural solution enables you to consolidate and better manage the violations reported by the SpyGlass Lint rules.

#### Prerequisite:

Make sure you have the turbo struct license, to run this solution.

This user guide covers the following topics:

- Using the Turbo Flow

- Turbo Initiatives

- Rule-wise Initiatives

- Turbo Parameter Settings

- Smart Rule Execution

- The moresimple\_turbo Report

- Known Problems

# **Using the Turbo Flow**

To use the **turbo** mode, set the following parameter:

set\_option turbo yes

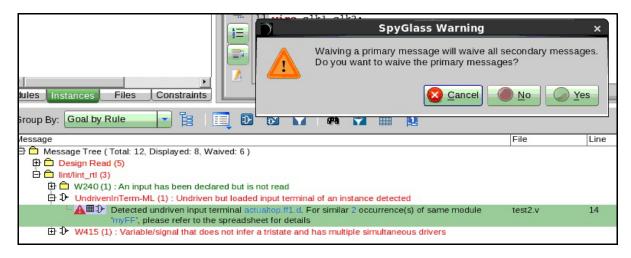

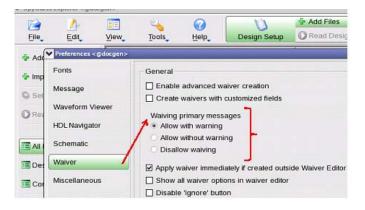

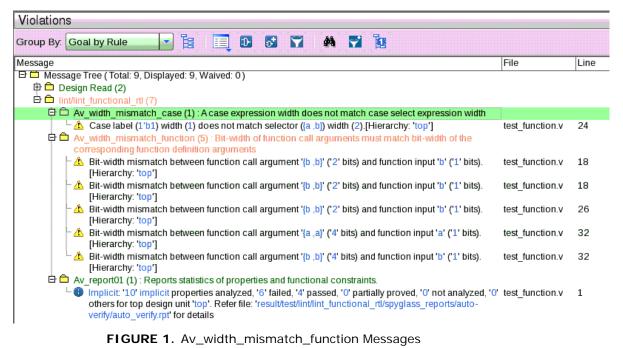

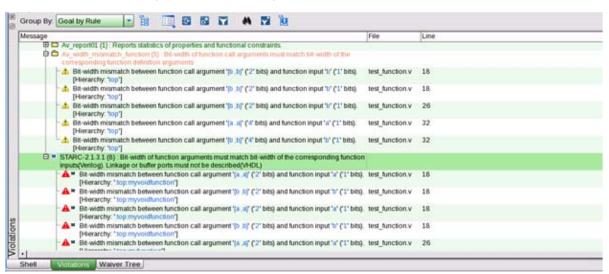

When the **turbo** option is set, the violations are classified into Primary and Secondary violations. If you click on a Primary violation, a spreadsheet is opened. This spreadsheet contains secondary violations for each primary violation. You can apply the desired waivers for the violations present in the spreadsheet. You can also use the old waivers. Waivers created in turbo mode are waived in non-turbo mode.

# **Turbo Initiatives**

The following table provide details about various initiatives/enhancements introduced in the rules that lead to consolidation and better management of the violations by classifying them into primary and secondary violations.

| Initiative                                 | Performs                                                                                                                                                                                                                                       |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TURBO_BUS_MERGE                            | Enables bus merging.                                                                                                                                                                                                                           |

| TURBO_CONSOLIDATE_DESIGN_SCOPE             | Consolidates and reports violations,<br>in a spreadsheet, based on block<br>(always/ process)/task/ function/<br>assignment/ signed-variable/expr/<br>package/macro/typdef/`define/per<br>case statement/port/signal/<br>variable declaration. |

| TURBO_CONSOLIDATE_IO_PAIR                  | Consolidates and reports violations,<br>in a spreadsheet, for connections<br>between the same set of input and<br>output ports of a module.                                                                                                    |

| TURBO_CONSOLIDATE_MODULE                   | Consolidates and reports violations,<br>in a spreadsheet, based on module<br>name.                                                                                                                                                             |

| TURBO_CONSOLIDATE_MODULE_CON<br>FIGURATION | Consolidates and reports violations,<br>in a spreadsheet, from different<br>configurations of a module.                                                                                                                                        |

| TURBO_CONSOLIDATE_PER_SOURCE               | Consolidates and reports violations,<br>in a spreadsheet, based on the<br>source (clock, reset, and signal<br>name, etc.).                                                                                                                     |

| TURBO_CONSOLIDATE_PORT                     | Consolidates and reports violations,<br>in a spreadsheet, based on the<br>module instance offending port.                                                                                                                                      |

| TURBO_DISABLE_ON_RTL                       | Disables a rule on RTL stage of design.                                                                                                                                                                                                        |

| Initiative                          | Performs                                                                                                                                                                                 |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TURBO_GROUP_MESSAGE                 | This is a global initiative that<br>modifies messages and indicates<br>the count of violating signals. All<br>violations are reported in a<br>spreadsheet.                               |

| TURBO_IGNORE_INTERNAL_OBJECTS       | Disables reporting violations if any cells/nets/instances (combo/<br>multiplexes/tristate) are generated internally.                                                                     |

| TURBO_IGNORE_PADDING                | Disables reporting violations for extensions of bits or constant integers (like 32'h45).                                                                                                 |

| TURBO_IGNORE_PARTIAL_BUS            | Disables reporting violations if any bit of vector/multi-bit is set/read/ used.                                                                                                          |

| TURBO_IGNORE_REDUNDANT_RULE         | Enables the smart rule execution.<br>See the <i>Smart Rule Execution</i><br>section for more details.                                                                                    |

| TURBO_IGNORE_STATIC_CONSTANTS       | Disables reporting violations on<br>expressions which contain a static/<br>constant operand, for example,<br>based numbers, parameters,<br>unsized based numbers, and<br>initialization. |

| TURBO_REMOVE_DUP_MSG                | Removes the duplicate messages.                                                                                                                                                          |

| TURBO_SET_RECOMMENDED_PARAM<br>ETER | Sets a parameter to the best fit value. See the <i>Turbo Parameter Settings</i> section for details.                                                                                     |

# **Rule-wise Initiatives**

The following tables present the list of rules in each product where message-consolidation initiatives are available:

- erc

- Iatch

- lint

- miscellaneous

- morelint

- openmore

- simulation

- starc

- starc2002

- starc2005

- timing

### erc

| Rule                          | Lang.                | Rule<br>Title                                                                                                                     | Parent<br>Message                                                                                                                                                                                                                               | Turbo<br>Initiatives                                                      |

|-------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| checkMultipleDrivers          | Verilog<br>+<br>VHDL | Only tristate<br>pins may be<br>WORed<br>(multiple<br>drivers only<br>allowed, if all<br>driving pins<br>are of type<br>tristate) | Not applicable                                                                                                                                                                                                                                  | TURBO_IGNORE_RE<br>DUNDANT_RULE                                           |

| checkPinConnectedT<br>oSupply | Verilog<br>+<br>VHDL | IO-ports or<br>Output ports<br>of cells/<br>modules may<br>not be<br>connected to<br>supply signals                               | Pin of <count> cell<br/><cell-name><br/>(instance <instance-<br>name&gt;) of module<br/><module-name><br/>connected to supply<br/>signals. Please refer<br/>to the spreadsheet<br/>for details</module-name></instance-<br></cell-name></count> | TURBO_CONSOLIDA<br>TE_DESIGN_SCOPE<br>TURBO_GROUP_MES<br>SAGE             |

| DisabledAnd                   | Verilog<br>+<br>VHDL | And/Nand<br>gate is<br>disabled                                                                                                   | Input pin of <count><br/>(comb-and/comb-<br/>nand) gates<br/>(instance <instance-<br>name&gt;) of module<br/><module-name></module-name></instance-<br></count>                                                                                 | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION<br>TURBO_GROUP_MES<br>SAGE |

|                               |                      |                                                                                                                                   | tiedlow.                                                                                                                                                                                                                                        | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only)   |

| Rule              | Lang.                | Rule<br>Title                                           | Parent<br>Message                                                                                                                                                                       | Turbo<br>Initiatives                                                    |

|-------------------|----------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| DisabledOr        | Verilog<br>+<br>VHDL | Or/Nor gate is disabled                                 | Input pin of <count><br/>(comb-or/comb-nor)<br/>gates (instance<br/><instance-name>)</instance-name></count>                                                                            | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   |                      |                                                         | of module <module-<br>name&gt; tiedlow.</module-<br>                                                                                                                                    | TURBO_GROUP_MES<br>SAGE                                                 |

|                   |                      |                                                         |                                                                                                                                                                                         | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| FlopClockConstant | Verilog<br>+<br>VHDL | Flip-flop clock<br>pin driven by<br>a constant<br>value | Clock pin of '10' flop<br>(instance ' <inst-<br>name'&gt; of module<br/>'<module-name>'</module-name></inst-<br>                                                                        | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   |                      | tie to constant                                         |                                                                                                                                                                                         | TURBO_GROUP_MES<br>SAGE                                                 |

|                   |                      |                                                         |                                                                                                                                                                                         | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| FlopDataConstant  | Verilog<br>+<br>VHDL | Flip-flop data<br>pin driven by<br>a constant<br>value  | Data pin of <count><br/>Flops (instance<br/><instance-name>)<br/>of module <module-< td=""><td>TURBO_CONSOLIDA<br/>TE_MODULE_CONFI<br/>GURATION</td></module-<></instance-name></count> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   | value                | name> tie to<br>constant.                               | TURBO_GROUP_MES<br>SAGE                                                                                                                                                                 |                                                                         |

|                   |                      |                                                         |                                                                                                                                                                                         | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| Rule              | Lang.                | Rule<br>Title                                                                              | Parent<br>Message                                                                                                                                                                         | Turbo<br>Initiatives                                                    |

|-------------------|----------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| FlopEConst        | Verilog<br>+<br>VHDL | Flip-flop<br>enable pin is<br>permanently<br>disabled or                                   | Enable pin of<br>' <count>' flop<br/>(instance '<inst-<br>name'&gt; of module</inst-<br></count>                                                                                          | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   |                      | enabled ' <module-name>'<br/>tie to constant</module-name>                                 |                                                                                                                                                                                           | TURBO_GROUP_MES<br>SAGE                                                 |

|                   |                      |                                                                                            |                                                                                                                                                                                           | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| FlopSRConst       | Verilog<br>+<br>VHDL | Flip-flop set<br>or reset pin is<br>permanently<br>enabled                                 | Set or reset pin of<br><count> Flops<br/>(instance <instance-<br>name&gt;) of module</instance-<br></count>                                                                               | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   |                      | <pre>enabled name&gt;) of module<br/><module-name> tie<br/>to constant</module-name></pre> | <module-name> tie</module-name>                                                                                                                                                           | TURBO_GROUP_MES<br>SAGE                                                 |

|                   |                      |                                                                                            |                                                                                                                                                                                           | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| LatchDataConstant | Verilog<br>+<br>VHDL | Latch data pin<br>driven by a<br>constant<br>value                                         | Data pin of <count><br/>Latches (instance<br/><instance-name>)<br/>of module <module-< td=""><td>TURBO_CONSOLIDA<br/>TE_MODULE_CONFI<br/>GURATION</td></module-<></instance-name></count> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                   | n                    | name> tie to<br>constant                                                                   | TURBO_GROUP_MES<br>SAGE                                                                                                                                                                   |                                                                         |

|                   |                      |                                                                                            |                                                                                                                                                                                           | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| Rule                | Lang.                | Rule<br>Title                                                                           | Parent<br>Message                                                                                        | Turbo<br>Initiatives                                                    |

|---------------------|----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| LatchEnableConstant | Verilog<br>+<br>VHDL | Latch enable<br>pin driven by<br>a constant<br>value                                    | Enable pin of<br><count> Latches<br/>(instance <instance-<br>name&gt;) of module</instance-<br></count>  | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                     |                      |                                                                                         | <module-name> tie<br/>to constant</module-name>                                                          | TURBO_GROUP_MES<br>SAGE                                                 |

|                     |                      |                                                                                         |                                                                                                          | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| MuxSelConst         | Verilog<br>+<br>VHDL | Mux select is constant.                                                                 | Select pin of<br><count> Mux<br/>(instance <instance-<br>name&gt;) of module</instance-<br></count>      | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                     |                      |                                                                                         | <module-name> tie<br/>to constant</module-name>                                                          | TURBO_GROUP_MES<br>SAGE                                                 |

|                     |                      |                                                                                         |                                                                                                          | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>(applicable to<br>spreadsheet only) |

| NoContAssign        | Verilog              | Continuous<br>assignment<br>statement<br>present in<br>technology-<br>mapped<br>netlist | Not applicable                                                                                           | TURBO_DISABLE_O<br>N_RTL                                                |

| TristateConst       | Verilog<br>+<br>VHDL | Tristate gate<br>enable is<br>constant                                                  | Enable pin of<br><count> Tristate<br/>(instance <instance-<br>name&gt;) of module</instance-<br></count> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION                          |

|                     |                      |                                                                                         | <module-name> tie to constant</module-name>                                                              | TURBO_GROUP_MES<br>SAGE                                                 |

## latch

| Rule            | Lang.                | Rule<br>Title                                                                | Parent<br>Message                                                                                                                                                                               | Turbo<br>Initiatives                                                      |

|-----------------|----------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| W336L           | Verilog              | Blocking<br>assignment to<br>latch output<br>should be<br>avoided            | Signal ' <signal-<br>name&gt;' is assigned<br/>using blocking<br/>assignment. For<br/>'<count>' similar<br/>case(s), please refer<br/>to the spreadsheet<br/>for details</count></signal-<br>   | TURBO_GROUP_MES<br>SAGE<br>TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION |

| LatchGatedClock | Verilog<br>+<br>VHDL | Do not use<br>gated/<br>internally<br>generated<br>clock to drive<br>latches | <count> latch(es)<br/>(output variable<br/>'<variable-name>')<br/>with gated or<br/>internally generated<br/>clock. Please refer to<br/>the spreadsheet for<br/>details</variable-name></count> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION<br>TURBO_BUS_MERGE         |

# lint

|      | 3       |                                             |                                                                                                                                                                           |                                                                |

|------|---------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Rule | Lang.   | Rule<br>Title                               | Parent<br>Message                                                                                                                                                         | Turbo<br>Initiatives                                           |

| W111 | Verilog | Not all<br>elements of an<br>array are read | Not all element of array<br>' <array-name>' are<br/>read. For <count><br/>similar occurrence(s),<br/>please refer to the<br/>spreadsheet for details</count></array-name> | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_REMOVE_DUP_<br>MSG |

| W111 | VHDL    | Not all<br>elements of an<br>array are read | Not all element of array<br>' <array-name>' are<br/>read. For <count><br/>similar occurrence(s),<br/>please refer to the<br/>spreadsheet for details</count></array-name> | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_REMOVE_DUP_<br>MSG |

| Rule | Lang.   | Rule<br>Title                                                                                     | Parent<br>Message                                                                                                                                                                | Turbo<br>Initiatives                                                           |

|------|---------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| W116 | Verilog | Unequal<br>length<br>operands in<br>bitwise<br>logical/<br>arithmetic/<br>ternary<br>operator     | Not applicable                                                                                                                                                                   | TURBO_REMOVE_DUP_<br>MSG                                                       |

| W116 | VHDL    | Unequal<br>length<br>operands in<br>bit wise<br>logical/<br>arithmetic/<br>relational<br>operator | Not applicable                                                                                                                                                                   | TURBO_REMOVE_DUP_<br>MSG                                                       |

| W120 | Verilog | A signal/<br>variable has<br>been declared<br>but is not used                                     | Variable ' <variable-<br>name&gt;' declared but not<br/>used. For <count><br/>similar occurrence(s),<br/>please refer to the<br/>spreadsheet for details.</count></variable-<br> | TURBO_IGNORE_PARTIA<br>L_BUS<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

|      |         |                                                                                                   |                                                                                                                                                                                  | TURBO_REMOVE_DUP_<br>MSG                                                       |

| W120 | VHDL    | A signal/<br>variable has<br>been declared                                                        | Variable ' <variable-<br>name&gt;' declared but not<br/>used. For <count></count></variable-<br>                                                                                 | TURBO_IGNORE_PARTIA<br>L_BUS                                                   |

|      |         | but is not used                                                                                   | similar occurrence(s),<br>please refer to the<br>spreadsheet for details.                                                                                                        | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON                                 |

|      |         |                                                                                                   |                                                                                                                                                                                  | TURBO_REMOVE_DUP_<br>MSG                                                       |

| Rule  | Lang.   | Rule<br>Title                                                           | Parent<br>Message                                                                                                    | Turbo<br>Initiatives                           |

|-------|---------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| W121  | Verilog | A variable<br>names collides<br>with and may<br>shadow                  | Name ' <variable-<br>name&gt;' is not unique at<br/><count> places and<br/>may shadow another</count></variable-<br> | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

|       |         | another<br>variable                                                     | variable. Please refer to the spreadsheet for details                                                                | TURBO_GROUP_MESSA<br>GE                        |

| W123  | Verilog | A variable has<br>been read but<br>is not set                           | Not applicable                                                                                                       | TURBO_REMOVE_DUP_<br>MSG                       |

| W123  | VHDL    | A signal or<br>variable has<br>been read but<br>is not set              | Not applicable                                                                                                       | TURBO_REMOVE_DUP_<br>MSG                       |

| W154  | Verilog | Do not declare<br>nets implicitly                                       | <count> more implicit<br/>declaration(s) of the net<br/>detected in the design.<br/>Please refer to the</count>      | TURBO_GROUP_MESSA<br>GE                        |

|       |         |                                                                         | spreadsheet for details                                                                                              | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

| W159  | Verilog | Condition<br>contains a<br>constant                                     | Constant expression<br>' <expression>' in<br/>condition. For <count></count></expression>                            | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE             |

|       |         | expression                                                              | similar occurrence(s),<br>please refer to the<br>spreadsheet for details                                             | TURBO_GROUP_MESSA<br>GE                        |

| W164a | Verilog | LHS width is<br>less than RHS<br>width of<br>assignment<br>(Truncation) | <pre>'<count>' occurrences of width mismatch on assignment '<assignment-node>'</assignment-node></count></pre>       | TURBO_GROUP_MESSA<br>GE                        |

| W164a | VHDL    | LHS width is<br>less than RHS<br>width of<br>assignment<br>(Truncation) | Not applicable                                                                                                       | TURBO_REMOVE_DUP_<br>MSG                       |

| Rule  | Lang.   | Rule<br>Title                                                             | Parent<br>Message                                                                                                                                                                                                                                                   | Turbo<br>Initiatives                                                                                            |

|-------|---------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| W164b | Verilog | LHS width is<br>greater than<br>RHS width of<br>assignment<br>(Extension) | ' <count>' occurrences<br/>of width mismatch on<br/>assignment<br/>'<assignment-node>'</assignment-node></count>                                                                                                                                                    | TURBO_GROUP_MESSA<br>GE                                                                                         |

| W164b | VHDL    | LHS width is<br>greater than<br>RHS width of<br>assignment<br>(Extension) | Not applicable                                                                                                                                                                                                                                                      | TURBO_REMOVE_DUP_<br>MSG                                                                                        |

| W164c | Verilog | LHS width is<br>greater than<br>RHS width of<br>assignment<br>(Extension) | LHS width ' <widthi>' is<br/>greater than RHS width<br/>'<widthi>' [Hierarchy:<br/>'<hier-path>'], <count><br/>occurrences of width<br/>mismatch on same<br/>assignment. Please refer<br/>to the spreadsheet for<br/>details.</count></hier-path></widthi></widthi> | TURBO_GROUP_MESSA<br>GE                                                                                         |

| W171  | Verilog | Case label is not constant                                                | <count> non constant<br/>Case-labels in a case<br/>statement. Please refer<br/>to the spreadsheet for<br/>details.</count>                                                                                                                                          | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_GROUP_MESSA<br>GE                                                   |

| W175  | Verilog | A parameter/<br>generic has<br>been defined<br>but is not used            | Module ' <module-<br>name&gt;' has '<count>'<br/>unused Parameter.<br/>Please refer to the<br/>spreadsheet for details.</count></module-<br>                                                                                                                        | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE |

| Rule | Lang.   | Rule<br>Title                                    | Parent<br>Message                                                                                   | Turbo<br>Initiatives                           |

|------|---------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------|

| W175 | VHDL    | A parameter/<br>generic has<br>been defined      | Entity ' <entity-name>'<br/>has '<count>' unused<br/>generic. Please refer to</count></entity-name> | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE             |

|      |         | but is not used                                  | the spreadsheet for details.                                                                        | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

|      |         |                                                  |                                                                                                     | TURBO_GROUP_MESSA<br>GE                        |

| W190 | Verilog | Task or<br>procedure<br>declared but<br>not used | Not applicable                                                                                      | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE             |

| W190 | VHDL    | Task or<br>procedure<br>declared but<br>not used | Not applicable                                                                                      | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE             |

| W240 | Verilog | An input has<br>been declared<br>but is not read | Input ' <input-port-<br>name&gt;' declared but not<br/>read. For <count></count></input-port-<br>   | TURBO_IGNORE_PARTIA<br>L_BUS                   |

|      |         |                                                  | similar occurrence(s),<br>please refer to the<br>spreadsheet for details.                           | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

|      |         |                                                  |                                                                                                     | TURBO_REMOVE_DUP_<br>MSG                       |

| W240 | VHDL    | An input has<br>been declared<br>but is not read | Input ' <input-port-<br>name&gt;' declared but not<br/>read. For <count></count></input-port-<br>   | TURBO_IGNORE_PARTIA<br>L_BUS                   |

|      |         |                                                  | similar occurrence(s),<br>please refer to the<br>spreadsheet for details                            | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

|      |         |                                                  |                                                                                                     | TURBO_REMOVE_DUP_<br>MSG                       |

| Rule  | Lang.   | Rule<br>Title                                                                         | Parent<br>Message                                                                                                                                                                                                                                                           | Turbo<br>Initiatives                                                                         |

|-------|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| W263  | Verilog | A case<br>expression<br>width does not<br>match case<br>select<br>expression<br>width | <pre>'<count>' case label width does not match case selector width of module '<module- name="">' at line '<line- number="">'</line-></module-></count></pre>                                                                                                                | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_REMOVE_DUP_<br>MSG                               |

| W280  | Verilog | A delay has<br>been specified<br>in a non-<br>blocking<br>assignment                  | <block-type> has<br/><count> non-blocking<br/>assignment(s) where<br/>intra-assignment delay<br/>is used. Please refer to<br/>the spreadsheet for<br/>details</count></block-type>                                                                                          | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE                                                           |

| W287b | Verilog | Output port of<br>an instance is<br>not connected                                     | Instance output port<br>' <output-port-name>' is<br/>not connected. For<br/>similar '<count>'<br/>violations of module<br/>'<module-name>',<br/>please refer to the<br/>spreadsheet for details</module-name></count></output-port-name>                                    | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON                                               |

| W287b | VHDL    | Output port of<br>an instance is<br>not connected                                     | Instance output<br>' <instance-name>' not<br/>used. [Elaborated<br/>Module Name:<br/><module-name>], for<br/>the similar '<count>'<br/>violation(s) of the<br/>elaborated module,<br/>please refer to the<br/>spreadsheet for details</count></module-name></instance-name> | TURBO_CONSOLIDATE_<br>PORT<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON TURBO_BUS_MERGE |

| W362  | Verilog | Unequal<br>length in<br>arithmetic<br>comparison<br>operator                          | Not applicable                                                                                                                                                                                                                                                              | TURBO_REMOVE_DUP_<br>MSG                                                                     |

| Rule  | Lang.                | Rule<br>Title                                                                                | Parent<br>Message                                                                                                                                                                                                            | Turbo<br>Initiatives                                                                                                                                            |

|-------|----------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W401  | Verilog<br>+<br>VHDL | Clock signal is<br>not an input to<br>the design<br>unit                                     | Clock ' <clock-name>' is<br/>not an input to design<br/>unit '<design-unit-<br>name&gt;'. For similar<br/>'<count>' violation(s),<br/>please refer to the<br/>spreadsheet for details</count></design-unit-<br></clock-name> | TURBO_CONSOLIDATE_<br>PER_SOURCE<br>TURBO_GROUP_MESSA<br>GE                                                                                                     |

| W402b | Verilog              | Asynchronous<br>set/reset<br>signal is not<br>an input to the<br>module                      | 'signal-name' to flop<br>' <flip-flop-name>' is<br/>gated or internally<br/>generated. For similar<br/>'<count>' violation(s),<br/>please refer to the<br/>spreadsheet for details</count></flip-flop-name>                  | TURBO_CONSOLIDATE_<br>PER_SOURCE<br>TURBO_GROUP_MESSA<br>GE                                                                                                     |

| W415a | Verilog              | Signal may be<br>multiply<br>assigned<br>(beside<br>initialization)<br>in the same<br>scope. | Signal <signal-name> is<br/>being assigned <count><br/>times inside module<br/>'<module-name>'.<br/>Please refer to the<br/>spreadsheet for details</module-name></count></signal-name>                                      | TURBO_SET_RECOMMEN<br>DED_PARAMETER<br>TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_CONSOLIDATE_<br>PER_SOURCE<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON |

| W443  | Verilog              | 'X' value used                                                                               | <pre>'<count>' occurrence of<br/>'X' state used in '<block-<br>name&gt;' block of module<br/>'<module-name>' at<br/>line '<line-number>'</line-number></module-name></block-<br></count></pre>                               | TURBO_IGNORE_STATIC<br>_CONSTANTS<br>TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_GROUP_MESSA<br>GE                                                              |

| W443  | VHDL                 | 'X' value used                                                                               | <pre>'<count>' occurrence of<br/>'X' state used in '<block-<br>name&gt;' block of module<br/>'<module-name>' at<br/>line '<line-number>'</line-number></module-name></block-<br></count></pre>                               | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE                                                                                       |

| Rule  | Lang.   | Rule<br>Title                                                                                                                                    | Parent<br>Message                                                                                                                                                       | Turbo<br>Initiatives                                                                                             |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| W456a | Verilog | A signal is<br>included in the<br>sensitivity list<br>of a<br>combinational<br>always block<br>but none of its<br>bits is read in<br>that block  | ' <count>' signals/<br/>variables are not<br/>required in sensitivity<br/>list of module '<module-<br>name'&gt; at line &lt;'line-<br/>number'&gt;</module-<br></count> | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_REMOVE_DUP_<br>MSG                                                   |

| W456a | VHDL    | A signal is<br>included in the<br>sensitivity list<br>of a<br>combinational<br>process block<br>but none of its<br>bits is read in<br>that block | Not applicable                                                                                                                                                          | TURBO_REMOVE_DUP_<br>MSG                                                                                         |

| W464  | Verilog | Unrecognized<br>synthesis<br>directive used<br>in the design                                                                                     | <count> more<br/>unrecognized synthesis<br/>directive(s) used in the<br/>design. Please refer to<br/>the spreadsheet for<br/>details</count>                            | TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE                                        |

| W464  | VHDL    | Unrecognized<br>synthesis<br>directive used<br>in the design                                                                                     | <count> more<br/>unrecognized synthesis<br/>directive(s) used in the<br/>design. Please refer to<br/>the spreadsheet for<br/>details</count>                            | TURBO_SET_RECOMMEN<br>DED_PARAMETER<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE |

| W481a | Verilog | Possibly<br>unsynthesizab<br>le loop: step<br>variable<br>differs from<br>variable used<br>in condition                                          | Not applicable                                                                                                                                                          | TURBO_REMOVE_DUP_<br>MSG                                                                                         |

| Rule | Lang.   | Rule<br>Title                                                                       | Parent<br>Message                                                                                                                                                                                                                                                                                                                                                                                                 | Turbo<br>Initiatives                                                                                            |

|------|---------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| W484 | Verilog | Possible loss<br>of carry or<br>borrow due to<br>addition/<br>subtraction           | Possible assignment<br>overflow: Ihs width<br><widthl> (Expr:<br/>'<lexpr>') should be<br/>greater than rhs width<br/><widthr> (Expr:<br/>'<rexpr>') to<br/>accommodate carry/<br/>borrow bit, [Hierarchy:<br/>'<hierpath>'], <count><br/>occurrences of<br/>assignment overflow on<br/>same assignment.<br/>Please refer to the<br/>spreadsheet for details</count></hierpath></rexpr></widthr></lexpr></widthl> | TURBO_GROUP_MESSA<br>GE                                                                                         |

| W528 | Verilog | A signal or<br>variable is set<br>but never read                                    | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                    | TURBO_IGNORE_PARTIA<br>L_BUS<br>TURBO_REMOVE_DUP_<br>MSG                                                        |

| W528 | VHDL    | A signal or<br>variable is set<br>but never read                                    | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                    | TURBO_IGNORE_PARTIA<br>L_BUS<br>TURBO_REMOVE_DUP_<br>MSG                                                        |

| W553 | Verilog | Different bits<br>of a bus are<br>driven in<br>different<br>combinational<br>blocks | net/bus ' <signal-<br>name&gt;' is driven<br/>'<count>' times inside<br/>more than one<br/>combinational block.<br/>Please refer to the<br/>spreadsheet for details</count></signal-<br>                                                                                                                                                                                                                          | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE |

| Rule  | Lang.   | Rule<br>Title                                                                                                  | Parent<br>Message                                                                                                                                                                                                                                                                                                          | Turbo<br>Initiatives                                                                                            |

|-------|---------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| W563  | Verilog | Reduction of a<br>single-bit<br>expression is<br>redundant                                                     | Unary reduction<br>operator used <count><br/>times on single bit<br/>usage of variable<br/>'<variable-name>'.<br/>Please refer to the<br/>spreadsheet for details</variable-name></count>                                                                                                                                  | TURBO_GROUP_MESSA<br>GE<br>TURBO_REMOVE_DUP_<br>MSG                                                             |

| W71   | Verilog | A case<br>statement (or<br>selected signal<br>assignment)<br>does not have<br>a default or<br>OTHERS<br>clause | Not applicable                                                                                                                                                                                                                                                                                                             | TURBO_REMOVE_DUP_<br>MSG                                                                                        |

| W287a | Verilog | Some inputs<br>to instance<br>are not driven<br>or<br>unconnected                                              | Input ' <input-name>' of<br/>instance '<instance-<br>name&gt;' is unconnected<br/>or Undriven.[Hierarchy:<br/>'<hier-path>']. For<br/>similar <count><br/>violation(s) of module<br/><module-name>,<br/>please refer to the<br/>spreadsheet for details</module-name></count></hier-path></instance-<br></input-name>      | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_GROUP_MESSA<br>GE |

| W287a | VHDL    | Some inputs<br>to instance<br>are not driven<br>or<br>unconnected                                              | Input Signal ' <input-<br>name&gt;' of instance<br/>'<instance-name>' not<br/>driven. [Elaborated<br/>Module Name: <hier-<br>name&gt;], for the similar<br/>'<count>' violation(s) of<br/>the corresponding<br/>master, please refer to<br/>the spreadsheet for<br/>details</count></hier-<br></instance-name></input-<br> | TURBO_CONSOLIDATE_<br>PORT<br>TURBO_CONSOLIDATE_<br>MODULE_CONFIGURATI<br>ON<br>TURBO_BUS_MERGE                 |

| Rule  | Lang.   | Rule<br>Title                                                                    | Parent<br>Message                                                                                                                                                           | Turbo<br>Initiatives                                          |

|-------|---------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| W191  | Verilog | Function<br>declared but<br>not used                                             | NA                                                                                                                                                                          | TURBO_REMOVE_DUP_<br>MSG                                      |

| W191  | VHDL    | Function<br>declared but<br>not used                                             | NA                                                                                                                                                                          | TURBO_REMOVE_DUP_<br>MSG                                      |

| W490  | Verilog | A control<br>expression/<br>sub-<br>expression is a<br>constant                  | NA                                                                                                                                                                          | TURBO_IGNORE_STATIC<br>_CONSTANTS                             |

| W552  | Verilog | Different bits<br>of a bus are<br>driven in<br>different<br>sequential<br>blocks | Bus ' <signal-name>' is<br/>driven '<count>' times<br/>inside more than one<br/>sequential block. Please<br/>refer to the spreadsheet<br/>for details</count></signal-name> | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_GROUP_MESSA<br>GE |

| W494a | VHDL    | Input port is<br>not used                                                        | <count> input port(s) of<br/>same entity not used.<br/>Please refer to the<br/>spreadsheet for details</count>                                                              | TURBO_CONSOLIDATE_<br>DESIGN_SCOPE<br>TURBO_GROUP_MESSA<br>GE |

## miscellaneous

| Rule     | Lang.            | Rule<br>Title                                                                     | Parent<br>Message                                                                                                                                                                                                       | Turbo<br>Initiatives                                                      |

|----------|------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ConstSig | Verilog+<br>VHDL | Signal has a<br>constant<br>value or can<br>only switch<br>to a constant<br>value | Signal ' <signal-name>'<br/>has a constant value or<br/>can only switch to a<br/>constant value. For<br/>'<count>' similar<br/>occurrence(s), please<br/>refer to the<br/>spreadsheet for details</count></signal-name> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION<br>TURBO_GROUP_MES<br>SAGE |

| Rule     | Lang.            | Rule<br>Title                                                       | Parent<br>Message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Turbo<br>Initiatives                                                                              |

|----------|------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| DeadCode | Verilog+<br>VHDL | Code does<br>not<br>contribute to<br>functionality<br>of the design | <ol> <li>The net '<net-<br>name&gt;' does not<br/>drive anything, for<br/>the similar <count><br/>occurrence(s),<br/>please refer to the<br/>spreadsheet for<br/>details</count></net-<br></li> <li>The net '<net-<br>name&gt;' is not driven<br/>by anything, for the<br/>similar <count><br/>occurrence(s),<br/>please refer to the<br/>spreadsheet for<br/>details</count></net-<br></li> <li>Change on net<br/>'<net-name>' has<br/>no effect on any of<br/>the outputs, for the<br/>similar <count><br/>occurrence(s),<br/>please refer to the<br/>spreadsheet for<br/>details</count></net-name></li> <li>Change on net<br/>'<net-name>' has<br/>no effect on any of<br/>the outputs, for the<br/>similar <count><br/>occurrence(s),<br/>please refer to the<br/>spreadsheet for<br/>details</count></net-name></li> <li>None of the inputs<br/>have any effect on<br/>net '<net-name>',<br/>for the similar<br/><count><br/>occurrence(s),<br/>please refer to the<br/>spreadsheet for<br/>details</count></net-name></li> </ol> | TURBO_CONSOLIDA<br>TE_MODULE_CONFI<br>GURATION<br>TURBO_GROUP_MES<br>SAGE<br>TURBO_BUS_MERGE      |

| Mux01    | Verilog+<br>VHDL | Connected<br>muxes<br>should not<br>have a<br>common<br>select.     | Some inputs of mux<br>' <mux1-name>' do not<br/>propagate to connected<br/>mux '<mux2-name>',<br/>due to common select.<br/>For '<count>' similar<br/>occurrence(s), please<br/>refer to the<br/>spreadsheet for details</count></mux2-name></mux1-name>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TURBO_CONSOLIDA<br>TE_PER_SOURCE<br>TURBO_IGNORE_IN<br>TERNAL_OBJECTS<br>TURBO_REMOVE_DU<br>P_MSG |

## morelint

| Rule              | Lang.   | Rule<br>Title                                                                         | Parent<br>Message                                                                                                                                                                                | Turbo<br>Initiatives                                                      |

|-------------------|---------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| AsgnToOneBit-ML   | Verilog | Assigning a 0<br>or 1(32-bits)<br>to a 1 bit is<br>not allowed                        | 1-bit is assigned a 0<br>or 1 (32 bits) in<br>module ' <module-<br>name&gt;' at '<count>'<br/>place(s). Please refer<br/>to the spreadsheet<br/>for details</count></module-<br>                 | TURBO_CONSOLIDAT<br>E_DESIGN_SCOPE                                        |

| BitOrder-ML       | Verilog | Bit order<br>specification<br>should follow<br>recommended<br>convention              | Bit order<br>specification(s) at<br><count> more<br/>places do not follow<br/>the recommended</count>                                                                                            | TURBO_CONSOLIDAT<br>E_DESIGN_SCOPE<br>TURBO_GROUP_MESS<br>AGE             |

|                   |         |                                                                                       | convention. Please<br>refer to the<br>spreadsheet for<br>details                                                                                                                                 | TURBO_CONSOLIDAT<br>E_MODULE_CONFIGU<br>RATION                            |

| ChkUndefMacro-ML  | Verilog | Macro is not<br>defined<br>before<br>undefining it                                    | <count><br/>occurrence(s) of<br/>improper usage of<br/>'undef' for macro<br/>detected in the file<br/>'<file-name>'.<br/>Please refer to the<br/>spreadsheet for<br/>details</file-name></count> | TURBO_CONSOLIDAT<br>E_DESIGN_SCOPE                                        |

| ConstDrivenNet-ML | Verilog | All internal<br>nets of<br>module<br>should not be<br>assigned a<br>constant<br>value | Please refer to the<br>'ConstDrivenNet-<br>ML_Ve_001.csv' for<br>rest <count><br/>violations of Verilog<br/>cases</count>                                                                        | TURBO_CONSOLIDAT<br>E_MODULE_CONFIGU<br>RATION<br>TURBO_GROUP_MESS<br>AGE |

| VHDL                 | All internal                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | nets of<br>module<br>should not be                               | Please refer to the<br>'ConstDrivenNet-<br>ML_Vh_001.csv' for<br>rest <count></count>                                                                                                             | TURBO_CONSOLIDAT<br>E_MODULE_CONFIGU<br>RATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | assigned a<br>constant<br>value                                  | violations of Verilog<br>cases                                                                                                                                                                    | TURBO_GROUP_MESS<br>AGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Verilog              | Design should<br>not use casez<br>constructs                     | Not applicable                                                                                                                                                                                    | TURBO_CONSOLIDAT<br>E_MODULE_CONFIGU<br>RATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |