# SpyGlass<sup>®</sup> DFT ADV Rules Reference Guide

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

© 2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **Trademarks**

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at https://www.synopsys.com/company/legal/trademarks-brands.html.

All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

### Report an Error

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to <a href="mailto:spyglass\_support@synopsys.com">spyglass\_support@synopsys.com</a>.

## **Contents**

| Preface                                                        | 31  |

|----------------------------------------------------------------|-----|

| About This Book                                                |     |

| Contents of This Book                                          |     |

| Typographical Conventions                                      |     |

| Typographical conventions                                      |     |

| Understanding the SpyGlass DFT ADV Product                     | 35  |

| Key Concepts                                                   | 36  |

| RTL Design for Test                                            | 37  |

| SpyGlass DFT ADV Design Constraints                            |     |

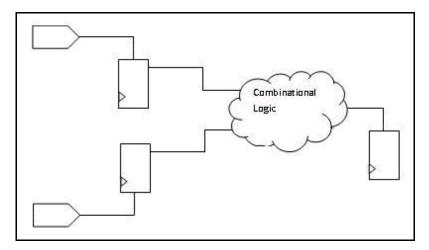

| Operating Modes                                                |     |

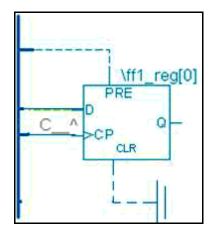

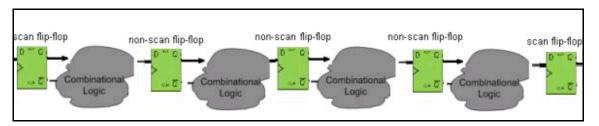

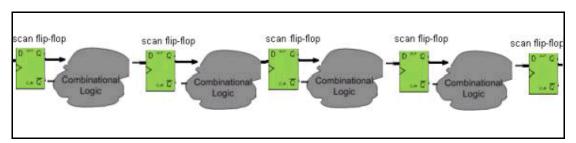

| Types of Flip-Flops                                            |     |

| Types of Latches                                               | 68  |

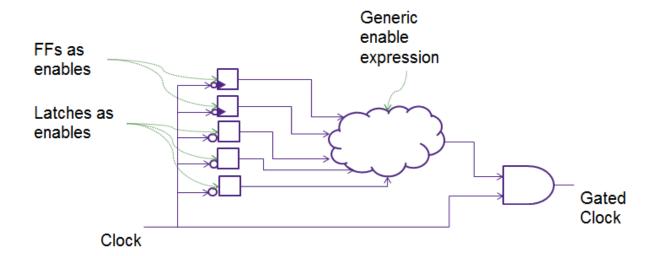

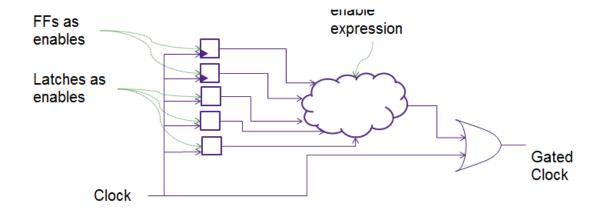

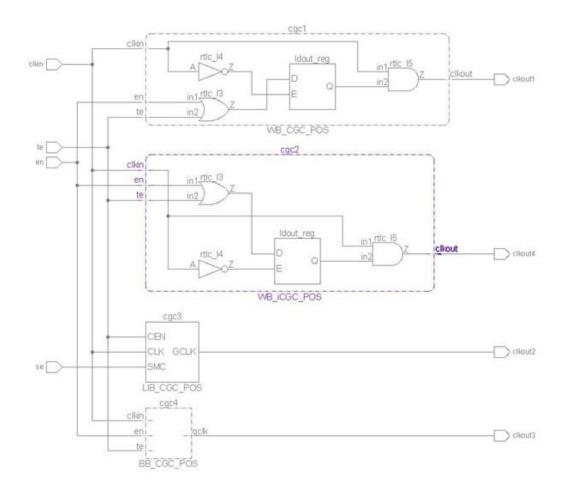

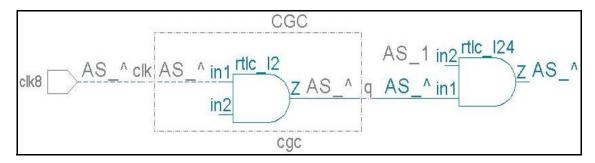

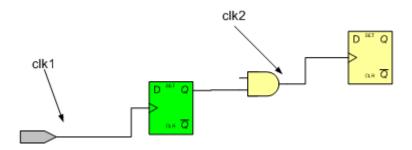

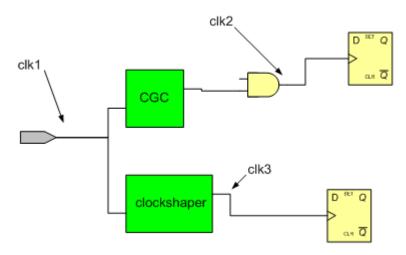

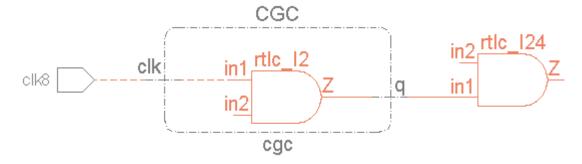

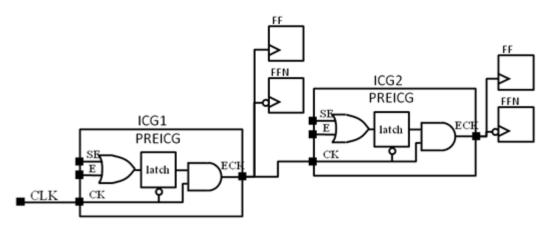

| Identifying Clock Gating Cells                                 | 74  |

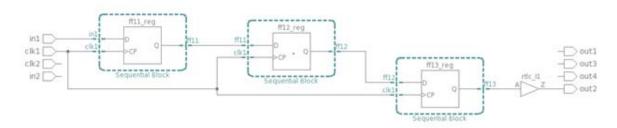

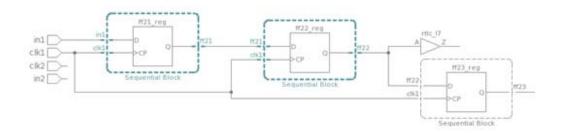

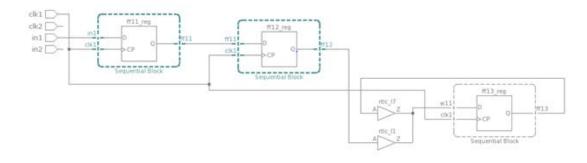

| Identifying Synchronizer                                       |     |

| Types of Faults                                                |     |

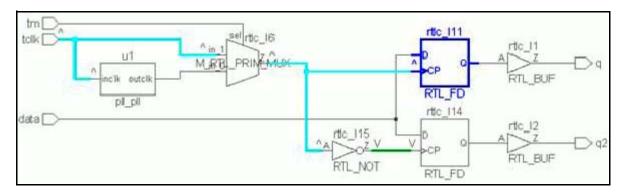

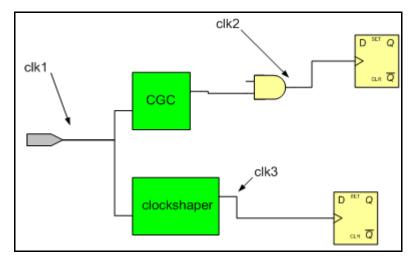

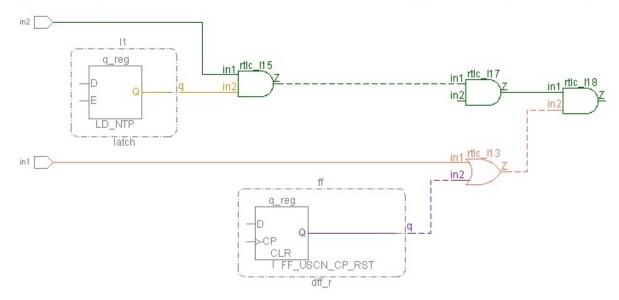

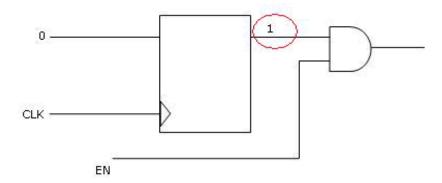

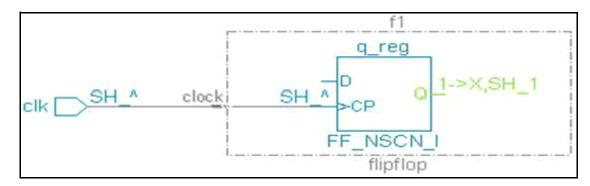

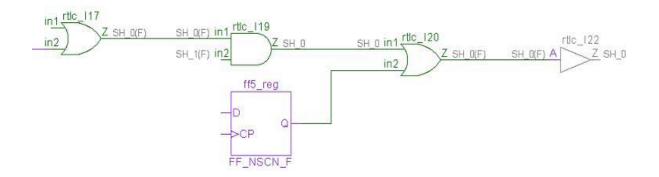

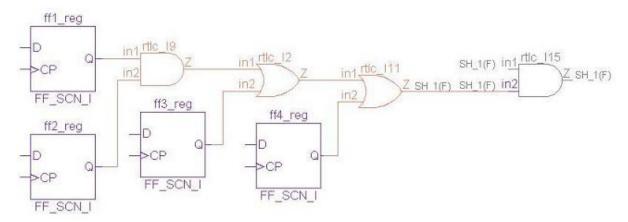

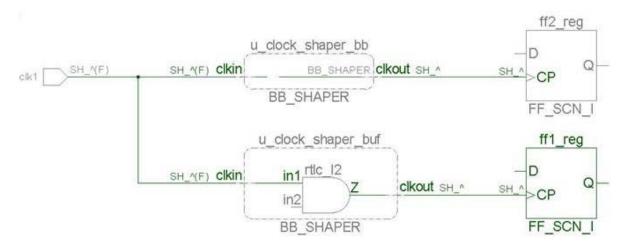

| Support For Clock Shaper with Scannable Flip- Flops            |     |

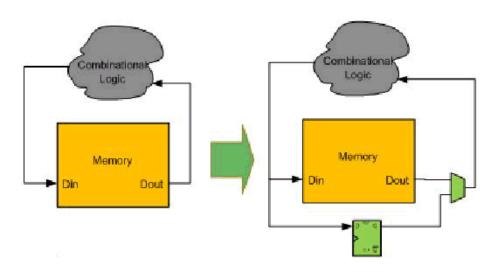

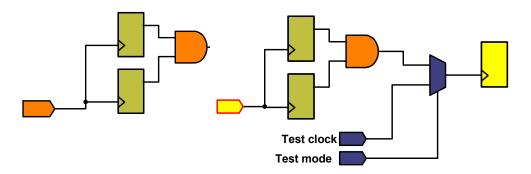

| Inserting RTL Testpoints                                       |     |

| Impact of Different Path Types on Fanin/Fanout Cone Traversal. |     |

| Design Impact                                                  |     |

| Scannability                                                   |     |

| Improvements to Fault and Test Coverage                        |     |

| Detecting Structures Leading to Non-Robust Tests               |     |

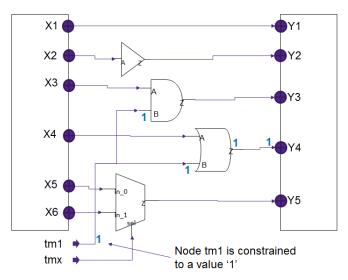

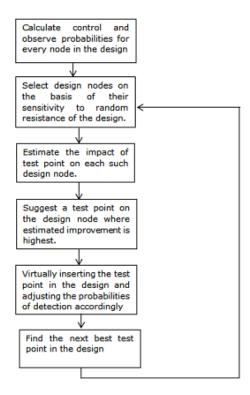

| Identifying Test Points To Reduce Random Resistance            |     |

| Using AutoFix and Selective AutoFix                            |     |

| Suggested SpyGlass DFT ADV Operation                           |     |

| Using the Design Constraints                                   |     |

| Making the RTL scan ready                                      |     |

| Complying with the SpyGlass DFT ADV Best Practices             |     |

| Adding Test Points                                             |     |

| Working with Scan Chains                                       |     |

| Checking Block-level Test Requirements                         |     |

| Making the RTL Ready for Atspeed Test                          |     |

| Performing Conditional Connectivity Checks                     | 143 |

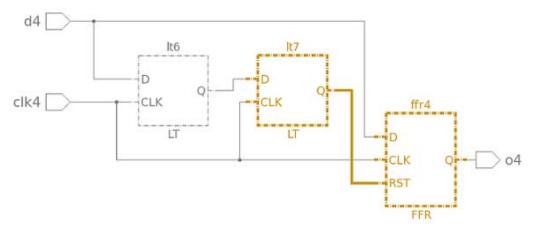

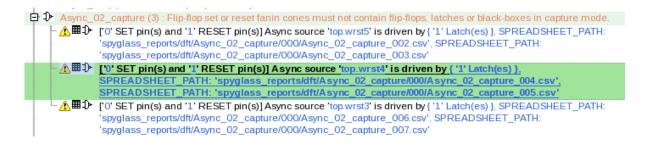

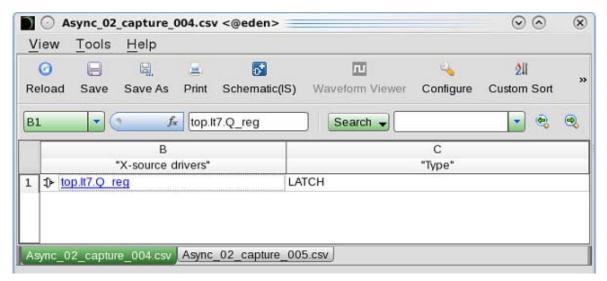

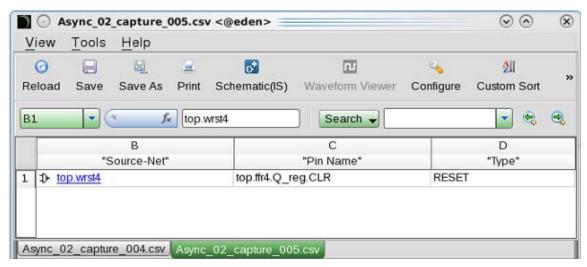

| Asynchronous F | <b>DFT ADV</b>                                                                                                                                                                                           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

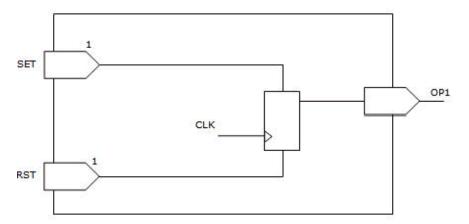

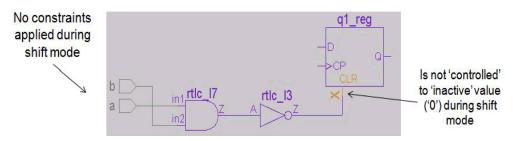

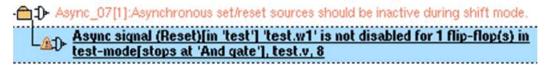

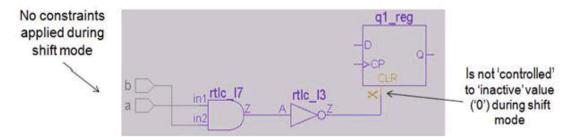

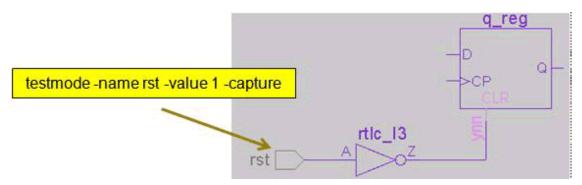

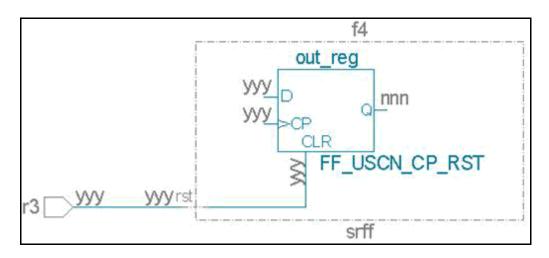

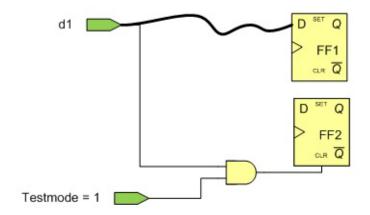

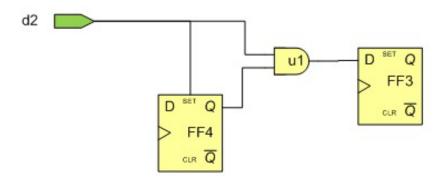

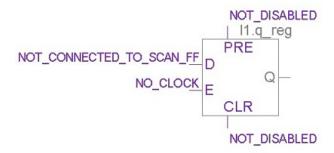

| Async_01       | : Do not use flip-flops with asynchronous set or reset unless disabled in shift mode                                                                                                                     |

| Async_02       | not contain -flip-flops, latches, or black boxes in capture mode.  161  _shift: Ensure that the flip-flop set or reset fan-in cones do not contain flip-flops, latches, or black boxes in shift mode 171 |

| _              | : Ensure that the active phase of all set and reset pins connected to the same root level pin are at the same level                                                                                      |

| • –            | : Ensure that the flip-flops are not used with both asynchronous set AND reset                                                                                                                           |

| _              | flop set or reset pin                                                                                                                                                                                    |

| _              | simultaneously active                                                                                                                                                                                    |

|                | Lssd: Ensure that the asynchronous set/reset sources are inactive during shift mode                                                                                                                      |

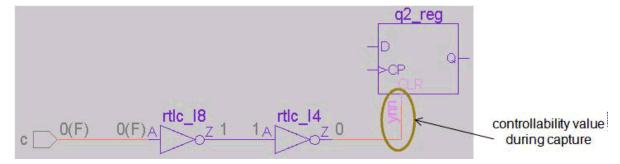

| _              | are fully controllable during capture                                                                                                                                                                    |

| Async_10       | controllable when circuit is in capture mode210: Ensure that the user designated pins control all sets and resets. 214                                                                                   |

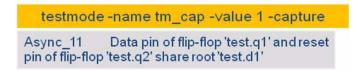

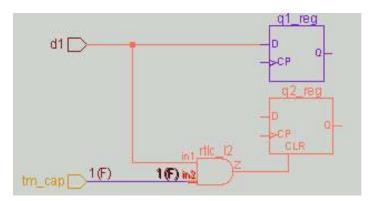

| • –            | <ul><li>: Avoid using set/reset signal as data signal in capture mode</li><li>219</li><li>: Reports flip-flops with data pins connected to the set/reset pins</li></ul>                                  |

| _              | of the same flip-flops during capture mode                                                                                                                                                               |

| Async_15       | are controllable to their inactive state during capture                                                                                                                                                  |

| _              | : Ensure that the set or reset sources are disabled or controllable by PI                                                                                                                                |

| Async_17       | : Report all the sources, which drive asynchronous preset, clear                                                                                                                                         |

| and clock pins                                                                                                           | 246               |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|

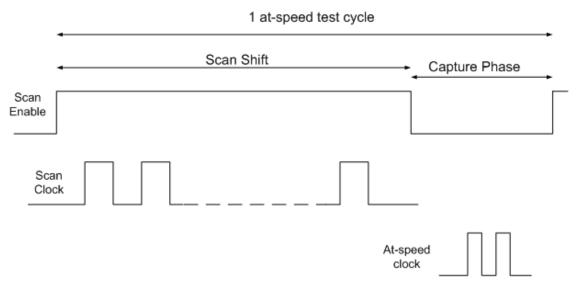

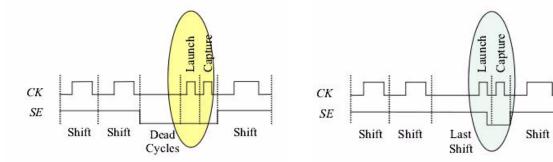

| Atspeed Test Rules                                                                                                       | 250               |

| Overview                                                                                                                 |                   |

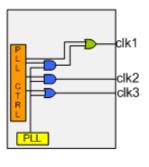

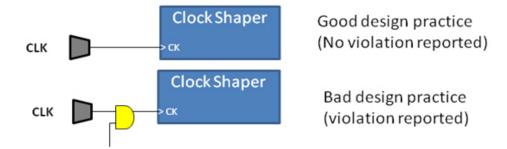

| Atspeed_01: Ensure that the source clock for all scannable flip-through a PLL                                            | 252               |

| Atspeed_03: Ensure that asynchronous logic in the functional r<br>not interact synchronously in the capture at-speed m   | ode 257           |

| Atspeed_04: Do not clock the synchronously interacting logic i functional mode by asynchronous clocks in the captur mode | e at-speed<br>264 |

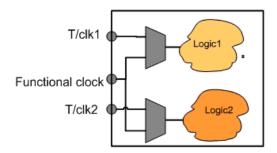

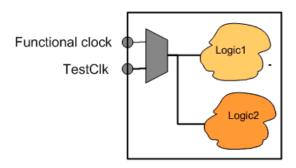

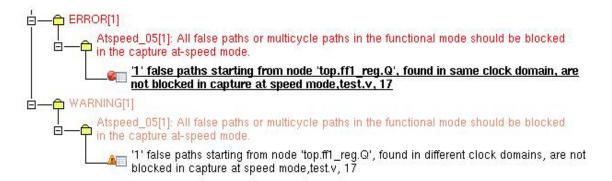

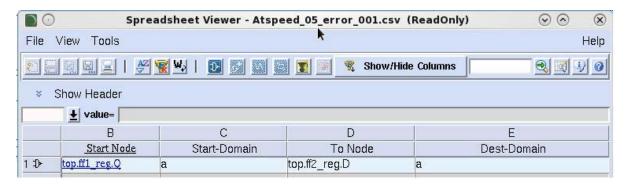

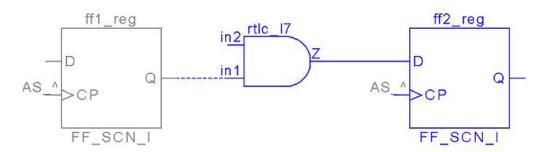

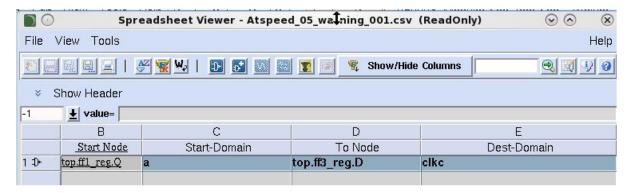

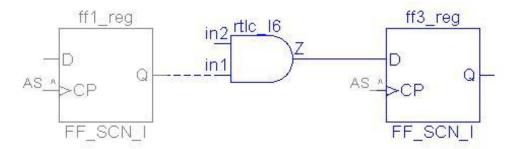

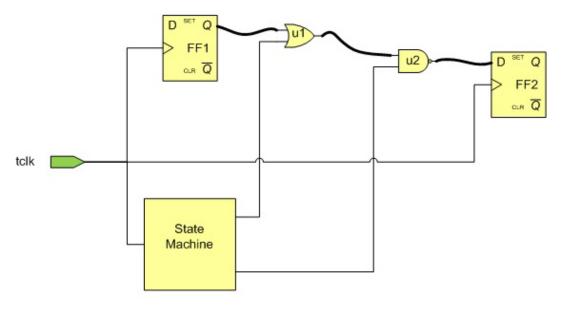

| Atspeed_05: Ensure that all false paths or multi-cycle paths in functional mode are blocked in the capture at-speed      | mode 269          |

| Atspeed_06 : Ensure that all paths crossing asynchronous clock           are blocked                                     | 277               |

| Atspeed_07: Use a separate signal, such as scan_enable, for cl<br>each domain in the capture at-speed mode               | 283               |

| Atspeed_08: Clock tree in the clock generation logic should no different logic along paths which need to be balanced     | 287               |

| Atspeed_09: Ensure that the data pin of scan flip-flop is fully c<br>291                                                 |                   |

| Atspeed_10: Only valid clock sources allowed                                                                             |                   |

| Atspeed_11: Ensure that all clock sources are controlled by an clock                                                     | 300               |

| Atspeed_12: A clock-pin receiving no frequency or multiple free a violation.                                             | 305               |

| Atspeed_13: Expected frequencies must be achieved                                                                        |                   |

| Atspeed_14: Test clocks must not be used as data signals                                                                 |                   |

| Atspeed_15: Combinational loops are not allowed in capture m                                                             |                   |

| Atspeed_16: This rule has been deprecated                                                                                |                   |

| Atspeed_17_capture: clockshaper cell must be enabled in cap 318                                                          |                   |

| Atspeed_17_captureatspeed : Clockshaper cell must be enab captureatspeed mode                                            | 320               |

| Atspeed_17_shift: clockshaper cell must be enabled in scansh 322                                                         |                   |

| Atspeed_19: Latches should be transparent in capture mode                                                                |                   |

| Atspeed_20: Asynchronous set/reset pins of all the flip-flops sl fully controllable during capture atspeed mode          | 331               |

| Atspeed_22: No "ANDing" (Merging) of atspeed test clocks in a                                                            | apture            |

|      | atspeed mode 3                                                                                                                | 33         |

|------|-------------------------------------------------------------------------------------------------------------------------------|------------|

|      | Atspeed_23: The clock pin of memories must pass through a pll 3                                                               | 35         |

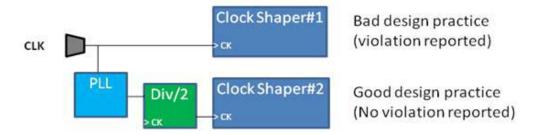

|      | Atspeed_24: Clock should not be shaped more than once                                                                         | 41         |

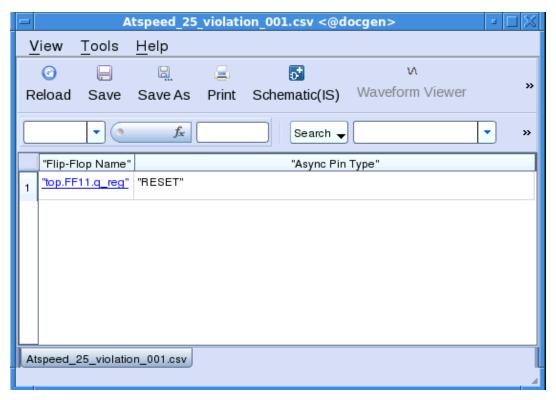

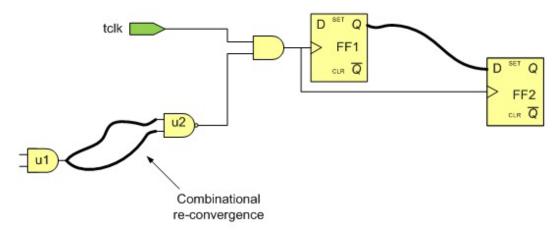

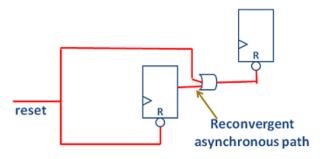

|      | Atspeed_25: Reports the presence of combinational re-convergence to                                                           |            |

|      | flip-flops asynchronous pins                                                                                                  | 44         |

|      | Atspeed_26: Reports if an atspeed clock is applied on the sensitized far                                                      | ۱-         |

|      | out cone of another atspeed clock                                                                                             | 50         |

|      | Atspeed_27: Reports if there is a convergence at the async pins of a flip                                                     | ე-         |

|      | flop3                                                                                                                         |            |

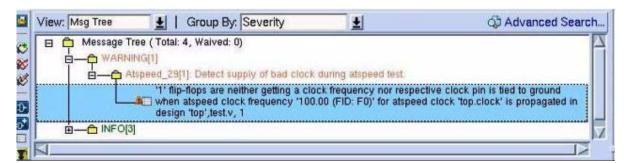

|      | Atspeed_29: Detects supply of bad clock during atspeed test                                                                   | 59         |

|      | <b>Atspeed_30</b> : Reports the presence of combinational re-convergence to                                                   |            |

|      | flip-flop clock pin                                                                                                           |            |

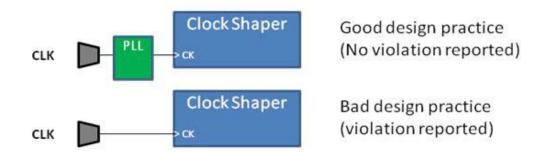

|      | Atspeed_31: Ensure that each clock shaper clock pin is directly controlled                                                    |            |

|      | via PLL in the capture atspeed mode                                                                                           |            |

|      | Atspeed_32: Reports the presence of cascaded reset re-convergence to                                                          |            |

|      | asynchronous pins of flip-flop                                                                                                |            |

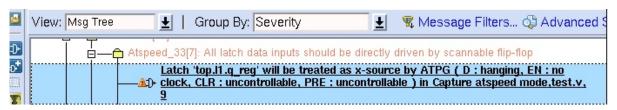

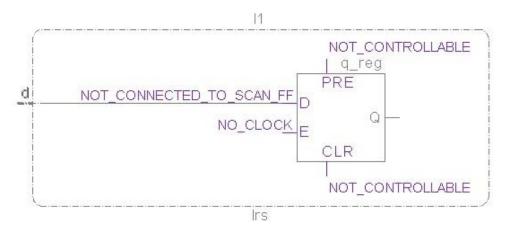

|      | Atspeed_33: All latch inputs should be driven by controllable sources in the                                                  |            |

|      | capture-atspeed mode                                                                                                          | 78         |

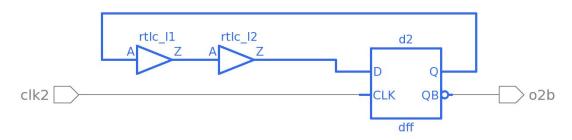

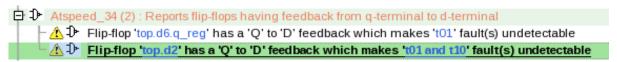

| 4    | Atspeed_34: Reports flip-flops having feedback from q-terminal to d-                                                          | ~ 4        |

|      | terminal                                                                                                                      |            |

|      | Rules                                                                                                                         |            |

|      | erview                                                                                                                        |            |

|      | BIST_01 : Restrict input cone width for BIST                                                                                  |            |

|      | BIST_02: Limit the number of gate inputs                                                                                      |            |

|      | BIST_03: Checks for unknown state after initialization sequence3                                                              |            |

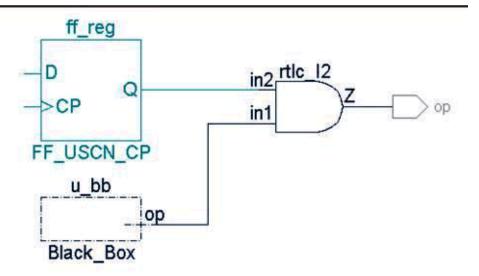

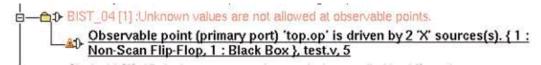

|      | BIST_04: Ensure that fan-in cones of the scannable flip-flops do not have                                                     |            |

|      | unknown values at observable points                                                                                           | 78         |

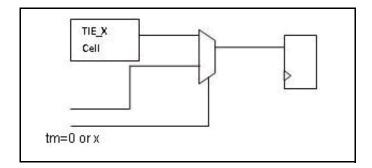

| l    | BIST_05: Ensure that in scan capture mode TIE-X cells outputs are bypassed4                                                   | <b>^</b> 2 |

| 011- | 51                                                                                                                            |            |

|      | Rules 40                                                                                                                      |            |

|      | erview                                                                                                                        |            |

| ,    | Clock_01: Ensure that only one clock is specified and that clock is drived from a top-level pin4                              |            |

|      | Clock_02: Ensure that both the edges of a clock are not switched on4                                                          |            |

|      | Clock_03: Reports multiple clock domains4                                                                                     |            |

|      | Clock_04: Do not use clock signals as data signals4                                                                           |            |

|      | Clock_04: Do not use clock signals as data signals4.  Clock_05: Ensure that all opposite edge flip-flops are used as retiming | ۷٤         |

| ,    | flip-flops4                                                                                                                   | 21         |

|      | Clock_06 : Ensure that only one clock port is available for each block4                                                       |            |

| ,    | CIUCK_UO. ETISUTE THAT OTHY OTHE CIUCK POLL IS AVAILABLE TO TEACH DIOCK 4.                                                    | SO         |

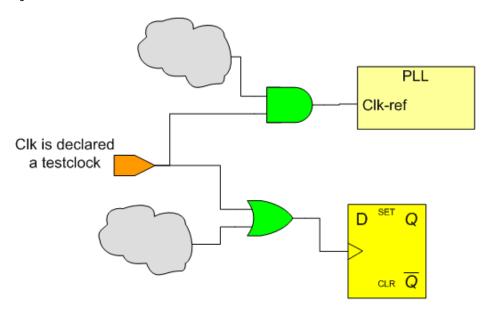

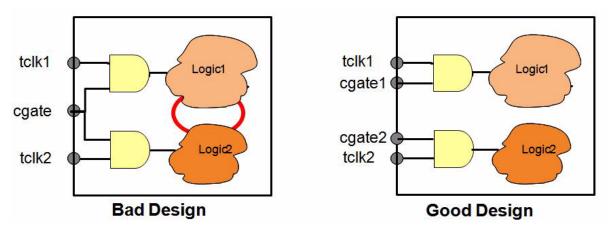

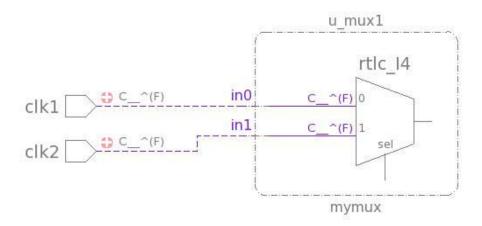

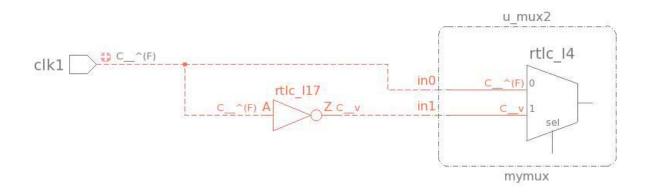

| Clock_08 | : Ensure that merged testclocks are not present in the design 440                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock_09 | : Ensure that the clock and data pins do not have common logic 446                                                                                                                             |

| Clock_10 | : Ensure that each clock domain has a dedicated test clock 449                                                                                                                                 |

|          | : Ensure that all clock sources are testclock controlled in shift                                                                                                                              |

|          | mode                                                                                                                                                                                           |

|          | _capture : Ensure that all clock sources are testclock controlled in capture mode                                                                                                              |

|          | : This rule has been deprecated                                                                                                                                                                |

|          | : Ensure that the negedge registers are only driving primary outputs and no other flip-flop                                                                                                    |

|          | : Ensure that the flip-flops capturing on the falling (rising) edge must not have any data paths from flip-flops capturing on the rising (falling) edge of the same rtz (rto) clock source 484 |

|          | : Ensure that the capture clocks are not gated by flip-flops capturing on the same clock                                                                                                       |

| Clock_18 | : Ensure that the flip-flops are not triggered on the negative edge of their clocks                                                                                                            |

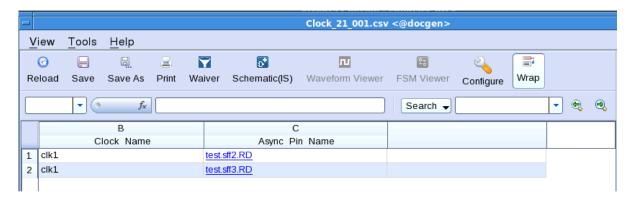

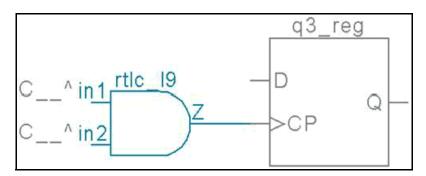

| Clock_21 | : Ensure that clocks do not drive flip-flop set or reset pins $\dots$ 498 $$                                                                                                                   |

| Clock_22 | : Ensure that each clock source should be combinationally driven                                                                                                                               |

|          | by one testclock only502                                                                                                                                                                       |

| Clock_23 | : Ensure that the scan flip-flops must only trigger on the positive edge                                                                                                                       |

| Clock_24 | : Ensure that the test clocks do not change shift mode signals 509                                                                                                                             |

| Clock_25 | : Ensure that the test clock must not drive flip-flops greater than that specified in -fflimit or -fflimit_percentage field(s) of the clock constraint                                         |

| Clock_26 | : Reports if a test clock is applied on the sensitized fan-out cone of another test clock                                                                                                      |

| Clock_27 | : Detects edge inconsistency between CGC and driven flip-flops. 523                                                                                                                            |

| Clock_28 | : Reports the presence of combinational re-convergence to flip-flop clock pin                                                                                                                  |

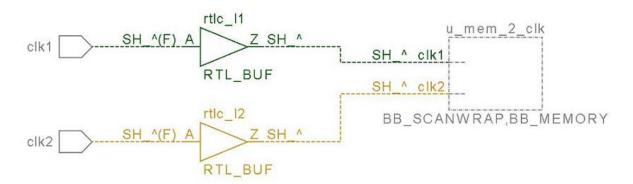

| Clock_29 | : Ensure that all clock sources of memories/hard macros are testclock controlled in shift/capture mode                                                                                         |

| Clock_30 | : All clock pins in a memory / hard macro should get the same                                                                                                                                  |

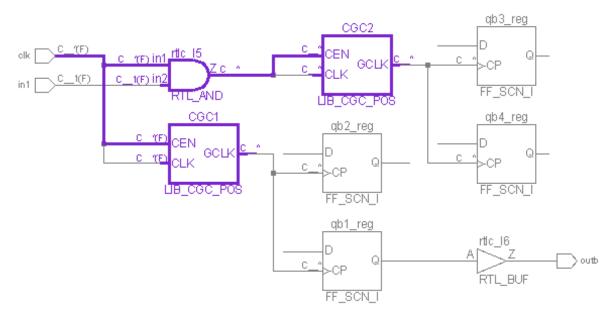

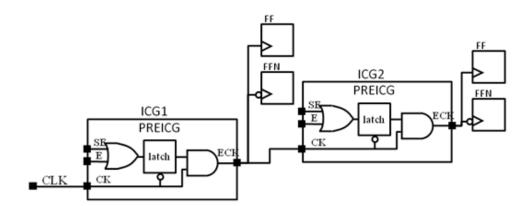

| Clock Gating Rules542                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------|

| Overview                                                                                                                        |

| CG_01_atspeed: Ensure that the clock gating cell enables are controllable to on state in atspeed mode                           |

| CG_01_capture: Ensure that the clock gating cell enables are controllable to on state in capture mode                           |

| CG_01_shift: Ensure that the clock gating cells are enabled in shift mode  552                                                  |

| CG_02_atspeed: Ensure that the CGC enables are controllable to off state in atspeed mode555                                     |

| CG_O2_capture: Ensure that the CGC enables are controllable to off state in capture mode                                        |

| CG_03_atspeed: Ensure that the system enable pins on clock gating cell are observable in atspeed mode                           |

| CG_03_capture: Ensure that the system enable pins on clock gating cell are observable in capture mode                           |

| CG_04: Test enable pins of clock gating cells should be driven by the specified gatingcell_enable ports                         |

| CG_05: Test enable pins of clock gating cells in the same level should be driven by the same test enable ports                  |

| CG_06: Flip-flops in the fan-in cone of a CGC may adversely affect coverage if they capture wrong value                         |

| CG_07: Detects edge inconsistency between CGC and driven flip-flops 576                                                         |

| CG_08: System enable pin of a CGC, which is driving the clock pin of a flip-flop, should not be driven by the same flip-flop582 |

| CG_consistency: Behavior model of clock gating cell should be consistent with the constraint applied on it                      |

| CG_generateReport: Generate a text report with details of all clock gating cells in design                                      |

| Connection Rules 592                                                                                                            |

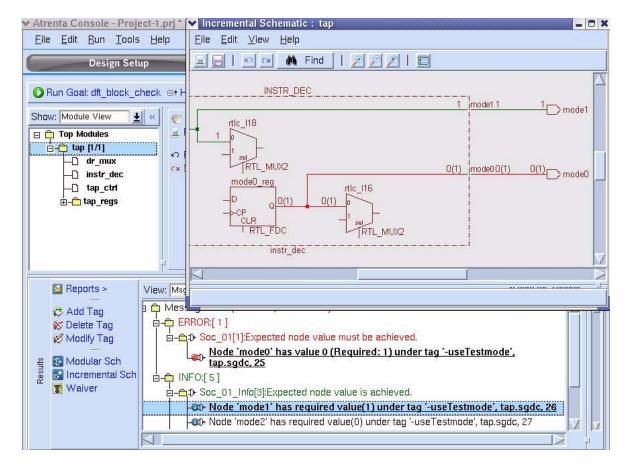

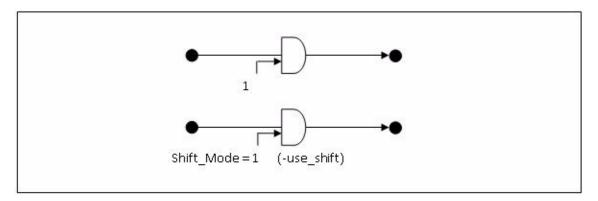

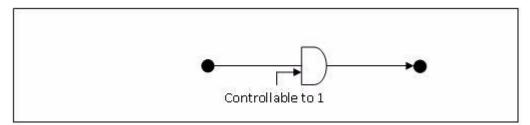

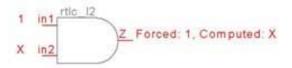

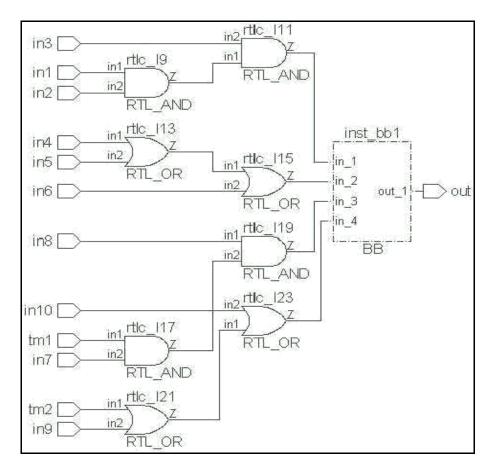

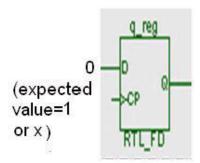

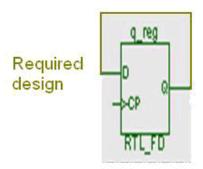

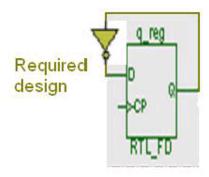

| Conn_01: Ensure that the expected node value is achieved 593                                                                    |

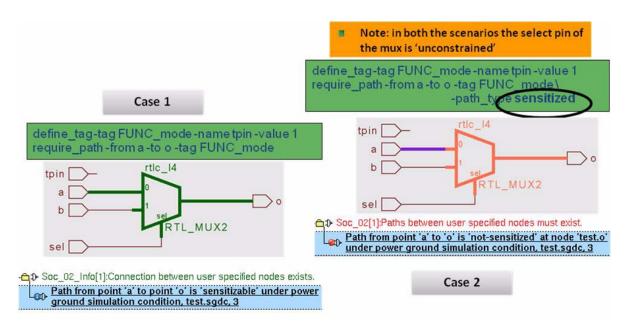

| Conn_02: Ensure that the paths between user-specified nodes exist 598                                                           |

| Conn_07: Checks the structure between the user-specified nodes 612                                                              |

| Conn_08: Checks the path between the user-specified nodes 619                                                                   |

| Conn_09: Path between user-specified nodes should not exist637                                                                  |

| Conn_10: Reports nets with illegal node values643                                                                               |

| Conn_11 : Node must satisfy the specified constraint message tag expression                                                     |

| Conn_12 : Node must not have the specified constraint message tag                                                               |

|                       | expression                                                                                                                        | 657    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| Conn_14               | : Ensure that specified nets are having stable values under                                                                       |        |

|                       | specified condition                                                                                                               |        |

| Conn_15               | : Check required pulse pattern at specified node                                                                                  | 671    |

| Diagnostic Rule       | s                                                                                                                                 | 676    |

|                       |                                                                                                                                   |        |

| Diagnose <sub>.</sub> | _02 : Ensure that the at-speed paths are not blocked by testm signals                                                             |        |

| Diagnose <sub>.</sub> | _O3: Ensure that the faults are not blocked by false paths or multi-cycle paths                                                   | -      |

| Diagnose <sub>.</sub> | _04 : Identifies the faults in paths crossing clock domains the cannot be tested                                                  | at     |

| Information Ru        | les                                                                                                                               | 686    |

|                       |                                                                                                                                   |        |

|                       | _audit : Analyze coverage for circuit                                                                                             | 690    |

| CreateDel             | bugSGDC : Create an SGDC file for all the user-specified instances                                                                | 695    |

| Diagnose <sub>.</sub> | _testclock : Display instances that block the testclock propagation                                                               | 699    |

| Diagnose <sub>.</sub> | _testmode : Display instances that block the testmode propagation                                                                 |        |

| Info atpo             | <b>conflict</b> : Reports testpoints to reduce ATPG conflicts                                                                     |        |

|                       | Fault: Reports all the ports and pins which are specified as a                                                                    | add    |

|                       | fault                                                                                                                             |        |

|                       | <b>beedClock</b> : Displays at-speed test clock propagation <b>beedClockSynchronization</b> : Provides information on interaction |        |

| imo_atsp              | atspeed clock domain pairs and                                                                                                    | tii ig |

|                       | non-interacting atspeed clock domain groups                                                                                       | 718    |

| Info atSp             | peedCoverage: This rule has been deprecated                                                                                       |        |

|                       | peedDomain: Displays at-speed test clock domain propagation 724                                                                   |        |

| Info atSp             | peedFrequency: Displays at-speed frequency propagation                                                                            | 726    |

|                       | peedFrequency_EnableConflict : This rule has been                                                                                 |        |

|                       | deprecated. Use the <u>dftDsmConstraintCheck_08</u> rule as a                                                                     |        |

|                       | replacement for the Info_atSpeedFrequency_EnableConflict r 728                                                                    | ʻule.  |

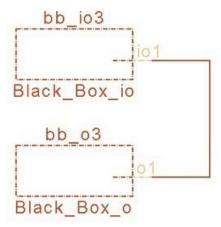

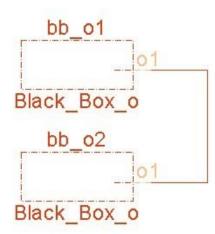

| Info_blac             | kboxDriver : Reports black box drivers                                                                                            | 729    |

| Info_cove             | erage: Estimate fault and test coverage                                                                                           | 735    |

| Info dBis             | t: Display simulation values of design in DBIST mode                                                                              | 745    |

| Info_define_tag: Show system state for a given tag748                                                  |

|--------------------------------------------------------------------------------------------------------|

| Info_dft_deprecated: Displays info messages for all the rules,                                         |

| parameters and constraints which will be deprecated future but                                         |

| are enabled/used in current run752                                                                     |

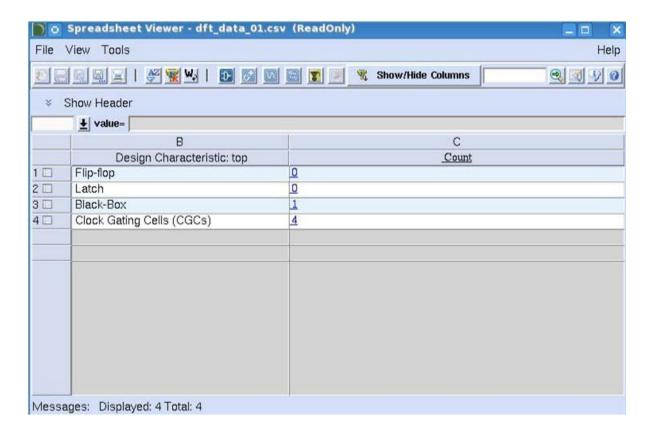

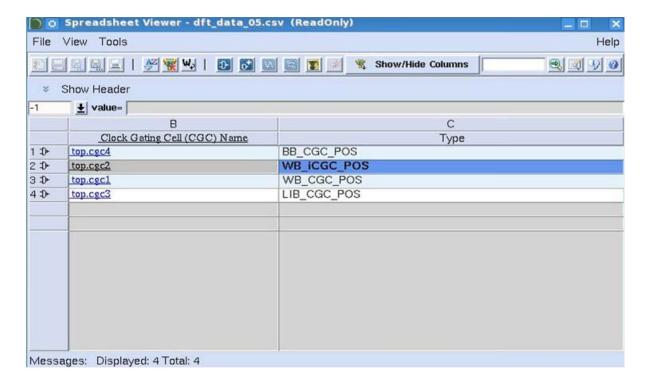

| Info_DftDebugData: Reports dft debug data (schematic and excel sheet)                                  |

| 758                                                                                                    |

| Info_dftmax_configuration: Enables the planning and configuration of                                   |

| DFTMAX Ultra in an SoC767                                                                              |

| Info_enabledFlops: Reports the flip-flops in the design, sorted by their                               |

| respective clock domains781                                                                            |

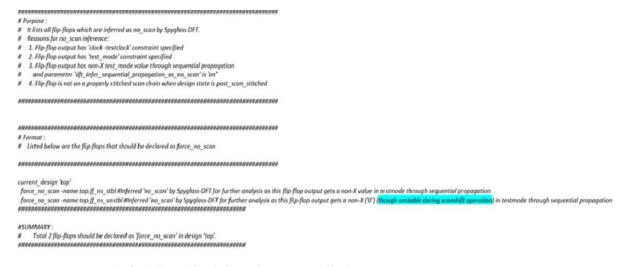

| Info_forcedScan: Displays all registers and flip-flops specified as                                    |

| 'force_scan'784                                                                                        |

| Info_freqAssignTable : Generates a frequency assignment report 790                                     |

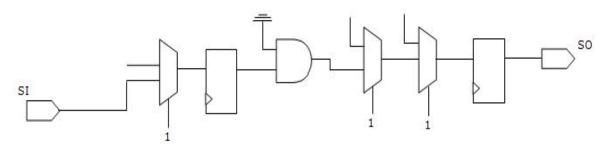

| Info_inferredNoScan: Displays all flip-flops that have been inferred as no                             |

| scan by SpyGlass DFT ADV792                                                                            |

| Info_IP_Report : Generates boundary report on the IPs specified using                                  |

| ip_block SGDC command798                                                                               |

| Info_Latch: Reports status of latches in the design802                                                 |

| Info_latchMapping: Reports the transparency and lockup status of all                                   |

| latches along with their respective test clock domain in the shift                                     |

| and capture mode806                                                                                    |

| Info_logicalRedundant: Displays logically redundant faults 809                                         |

| Info_memories: Reports on memory instances present in a design815                                      |

| Info_memoryforce : Back annotate the memoryforce simulation results                                    |

| onto the structural view820                                                                            |

| Info_memorywritedisable: Displays memorywritedisable propagation                                       |

| data824                                                                                                |

| Info_noAtspeed: Displays all registers and flip-flops specified as                                     |

| 'no_atspeed'828                                                                                        |

| Info_noFault: Reports all the ports and pins which are specified as no                                 |

| fault830                                                                                               |

| Info_noScan: Display all registers and flip-flops specified as                                         |

| 'force_no_scan'834                                                                                     |

| Info_noscanFlopsTextReport: The Info_noscanFlopsTextReport rule has                                    |

| been deprecated. Use the <a href="Info_inferredNoScan">Info_inferredNoScan</a> rule instead of         |

| this rule841                                                                                           |

| Info_path: Display blocked path information842                                                         |

| $\textbf{Info\_potDetectable:} \ \ \text{Display faults that are potentially detectable.} \ \dots 846$ |

| Info_pwrGndSim : Display the power-ground simulation results 849                                       |

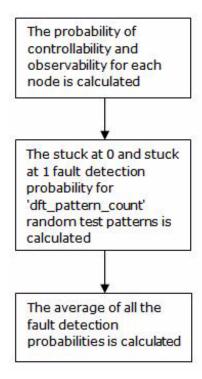

| Info_random_resistance : Estimates random pattern fault and test                                             |

|--------------------------------------------------------------------------------------------------------------|

| coverage for design852                                                                                       |

| Info_scanchain: Displays all properly stitched scan chains                                                   |

| Info_scanwrap: Reports scanwrap related information                                                          |

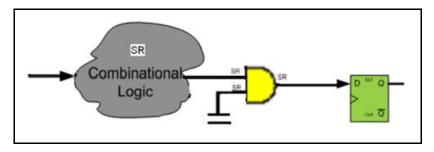

| Info_self_gating_logic: Recognizes self-gating cells and identifies the                                      |

| test-points in self-gating logic                                                                             |

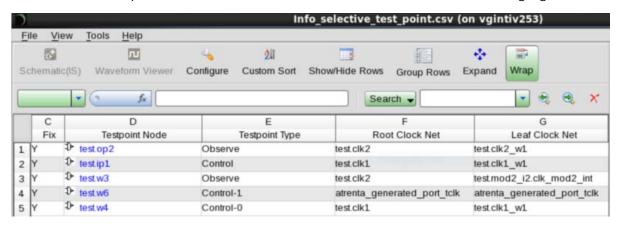

| Info_selective_testpoint: Inserts selective testpoints                                                       |

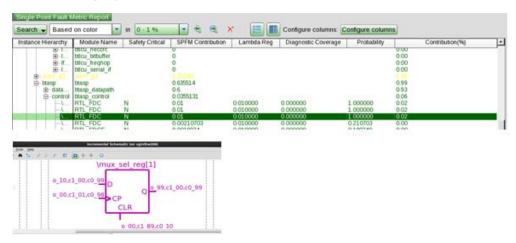

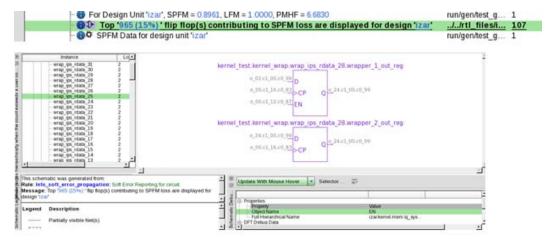

| Info_soft_error_propagation: Generates the Soft Error related metrics 883                                    |

| Info_stilFile : Generates a STIL file                                                                        |

| Info_stil_to_sgdc : Generates an SGDC file corresponding to a Stil file 893                                  |

| Info_synthRedundant: Displays pins (for an RTL design) that are likely to be absent in an optimized netlist. |

| Displays faults (for a netlist design) which fall in either TIED or BLOCKED category                         |

| Info_testclock : Display test clock propagation                                                              |

| Info_testCounts: This rule has been deprecated                                                               |

| Info_testmode: Display testmode simulation results                                                           |

| Info_testmode_conflict_01: Displays conflict in user specified testmode                                      |

| with respect to simulation result of fan-in cone920                                                          |

| Info_Top_SGDC_Report: This rule does bottom up hierarchical migration of block level constraints             |

| Info_transitionCoverage: Evaluate upper bound of transition coverage                                         |

| for design                                                                                                   |

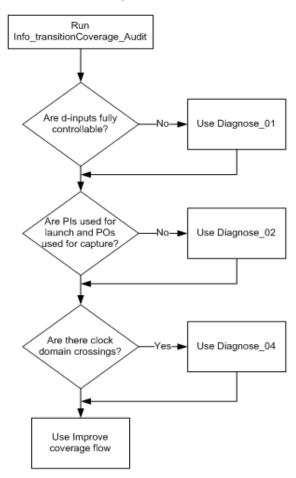

| Info_transitionCoverage_audit : Analyze transition coverage for circuit. 938                                 |

| Info_uncontrollable: Show nets with imperfect controllability 943                                            |

| Info_undetectCause: Display undetectable fault information 948                                               |

| Info_unobservable : Show all unobservable pins                                                               |

| Info_untestable: Display untestable faults caused by test mode 958                                           |

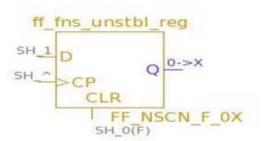

| Info_unstable_testmode_registers: Report flip-flops, intended to be                                          |

| used as a configuration register, which are unable to retain their                                           |

| respective initialized 0/1 value during scan shift operation and                                             |

| create unstable test mode conditions                                                                         |

| Info_unused: Display faults having no effect on system function 969                                          |

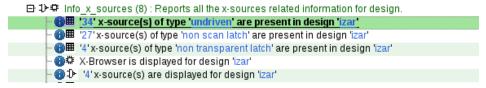

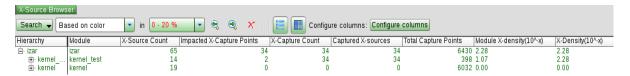

| Info_x_sources: Reports all the x-sources related information for the design                                 |

| 3                                                                                                            |

| Latch Rules                                                                                                  |

| Overv | /iew   | 978                                                                                                                                             |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

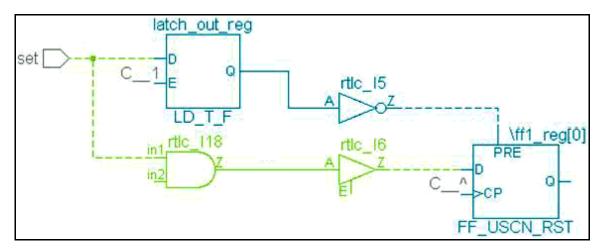

| La    | tch_01 | : Do not use latches unless transparent during power ground                                                                                     |

|       |        | mode979                                                                                                                                         |

|       | _      | : Ensure that no combinational loops exist from transparent latches                                                                             |

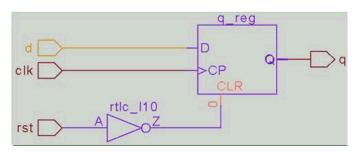

| La    | tch_04 | : Ensure that there are no synchronous latches in the design $987$                                                                              |

|       |        | : This rule has been deprecated990                                                                                                              |

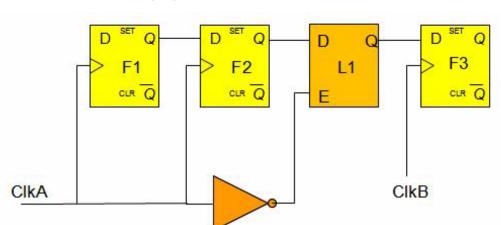

| La    | tch_06 | : Ensure that the cascaded latches have clock phase inversion 991                                                                               |

|       | _      | : Ensure that the latches are transparent                                                                                                       |

|       | _      | : Ensure that all latch enables must only be combinationally driven through primary ports 1003                                                  |

|       | _      | : Ensure that all slave LSSD latches are fed directly by only one master LSSD Latch                                                             |

|       | _      | : Ensure that all latches except retiming ones are transparent in Logic DBIST mode                                                              |

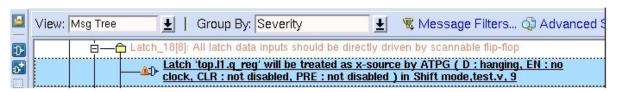

| La    | tch_18 | : All latch inputs should meet scannability criterion in scan-shift<br>and should be driven by controllable sources in the capture mode<br>1013 |

| La    | tch_19 | : Ensure that all non-transparent and non-shadow latches meet the scannability criterion 1016                                                   |

|       |        |                                                                                                                                                 |

|       |        |                                                                                                                                                 |

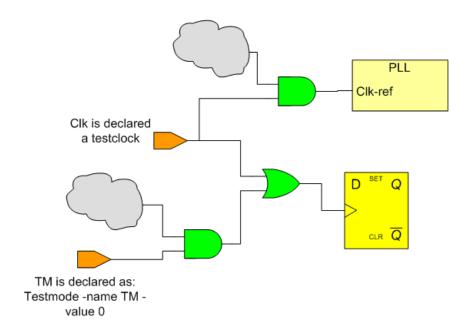

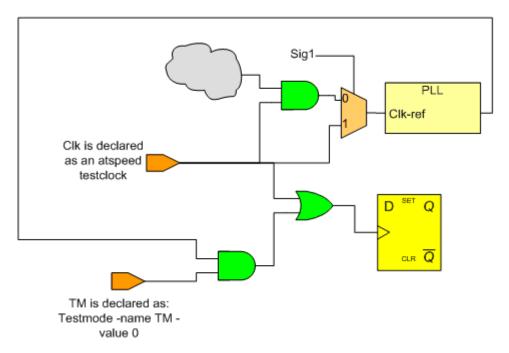

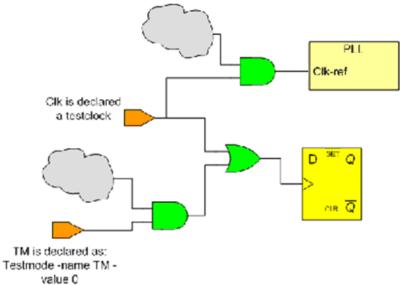

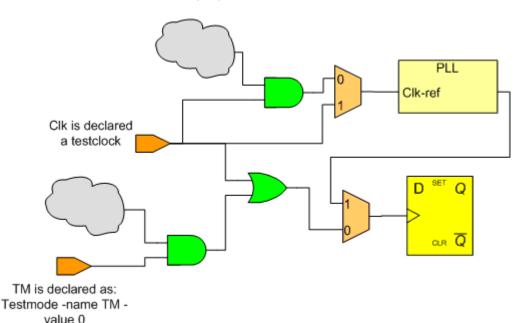

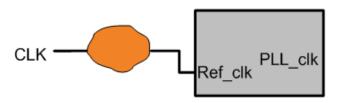

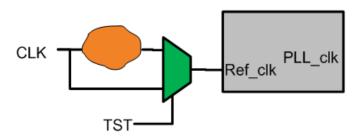

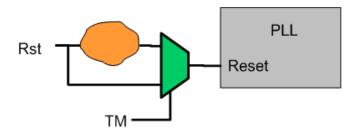

|       |        | Ensure that the reference clock of PLL is directly controlled by external signal1021                                                            |

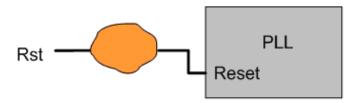

|       | _      | Ensure that the reset pin of a PLL is directly controlled by external signal 1027                                                               |

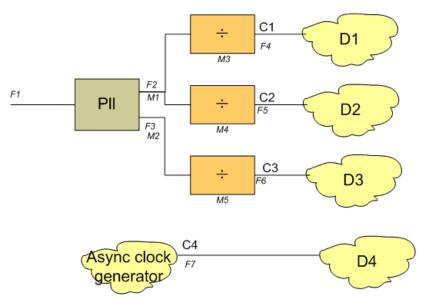

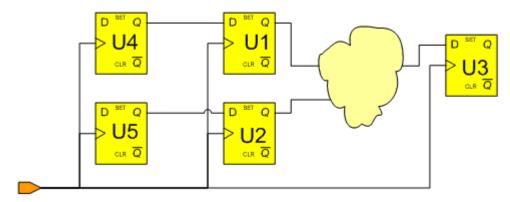

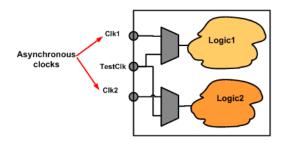

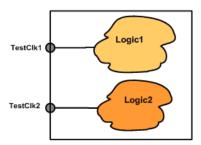

|       | _      | PLL reference clocks should not directly reach to any flip-flop 1034                                                                            |

|       |        |                                                                                                                                                 |

|       |        |                                                                                                                                                 |

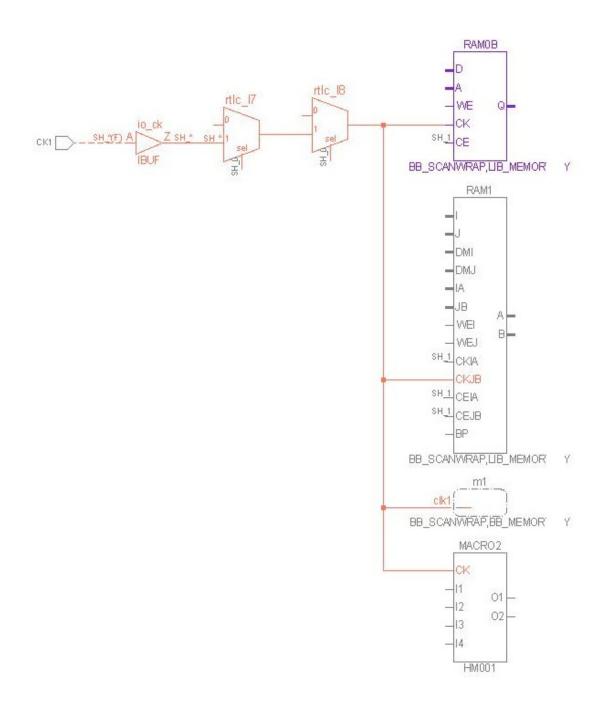

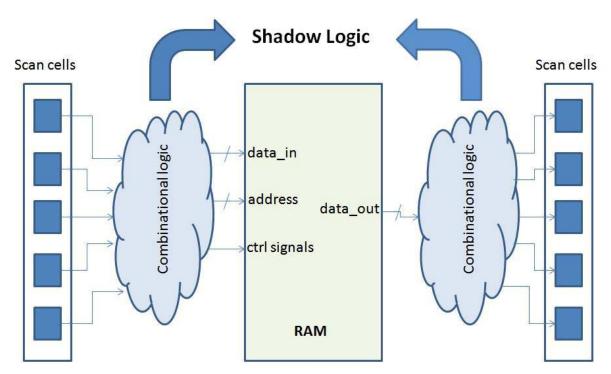

|       |        | Memory shadow logic must be less than a user specified %1037                                                                                    |

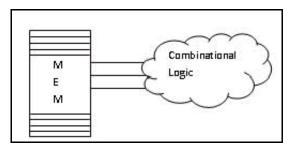

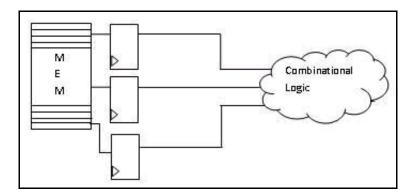

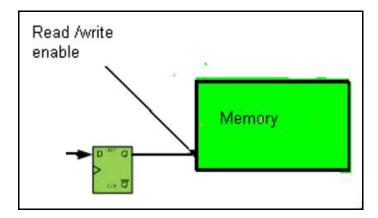

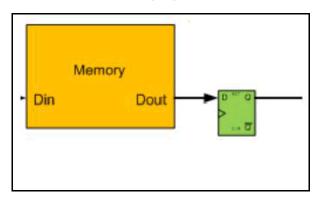

|       | _      | Ensure that the memory outputs are registered to scannable flip-flops                                                                           |

|       |        | Memory inputs should be scannable                                                                                                               |

|       |        | Memory outputs must be forced to known values in shift mode . 1049                                                                              |

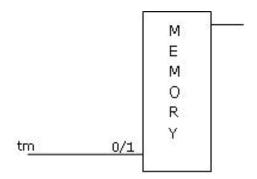

|       | _      | Disable RAM write enables                                                                                                                       |

| R/A   | M 06:  | Ensure that the Top level pins must drive memory read/write pins                                                                                |

|      |            | 1057                                                                    |

|------|------------|-------------------------------------------------------------------------|

|      | RAM_07     | : Ensure that the memory outputs must not affect scannable flip-        |

|      |            | flops during capture                                                    |

|      | RAM_08     | : Ensure that the write controls to register files/memories are         |

|      |            | ATPG controlled during capture mode 1065                                |

|      | RAM_09     | : Ensure that the Memory inputs must feed scannable flip-flops          |

|      |            | during capture                                                          |

|      | RAM_10     | : Ensure that the memory or black box input and output terminals        |

|      | DAM 11     | are scanwrapped or bypassed                                             |

|      | KAIVI_ I I | 1078                                                                    |

| Scan | Dules      | 1082                                                                    |

|      |            |                                                                         |

|      |            | : All scan chains should operate in parallel 1084                       |

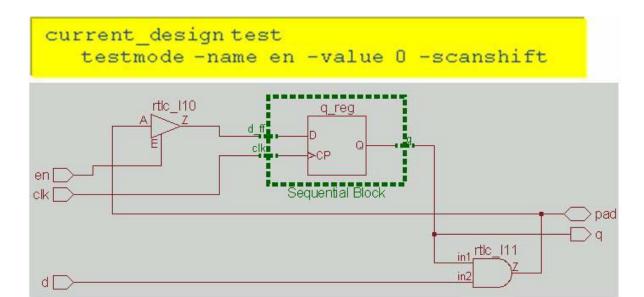

|      |            | : Ensure that there are no internal test_mode signals 1087              |

|      |            | : Ensure that all registers and flip-flops are scannable 1096           |

|      |            | : Ensure that the scan ratio must exceed threshold 1101                 |

|      | _          | : Ensure that all flip-flops, except retiming flip-flops, are scannable |

|      | _          | 1104                                                                    |

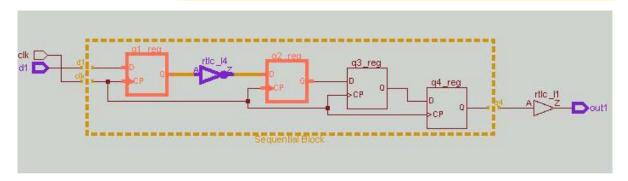

|      | Scan_17    | : Ensure that the sequential depth does not exceed limit between        |

|      |            | any two scan points 1109                                                |

|      |            | : Ensure that all top level inputs are registered 1114                  |

|      |            | : All top level outputs must be controlled by scan flip-flops 1118      |

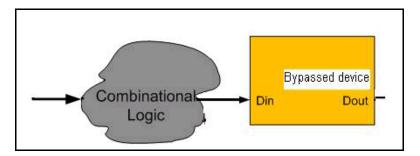

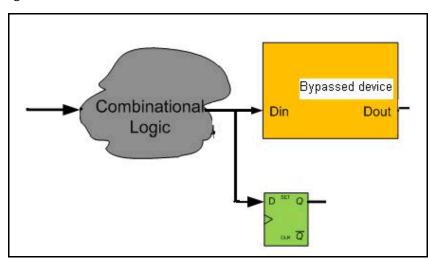

|      | Scan_20    | : Ensure that outputs of bypassed devices do not affect any scan        |

|      | 0 01       | flip-flop data & inputs are observable                                  |

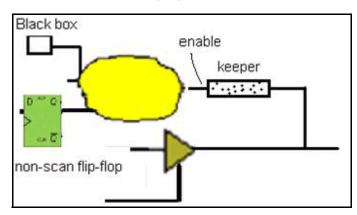

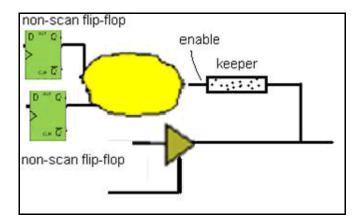

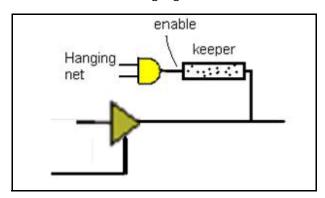

|      | Scan_21    | : Keeper, pullUp, and pullDown enables must be controlled by            |

|      | Soon 22    | scan flip-flops                                                         |

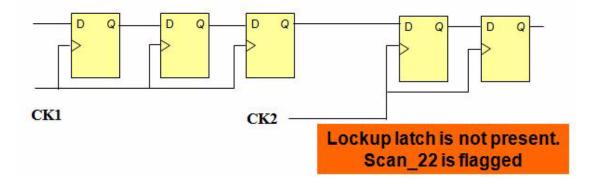

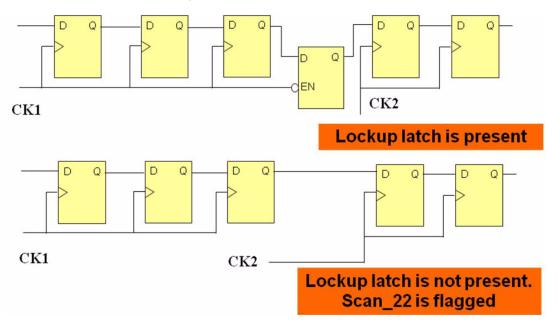

|      | Scan_22    | crossing                                                                |

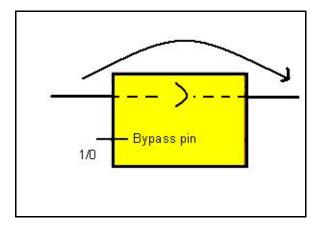

|      | Scan 23    | : Ensure that the module bypass conditions are satisfied 1140           |

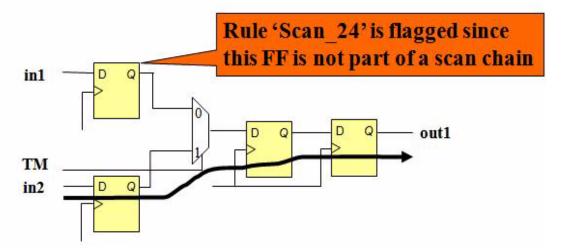

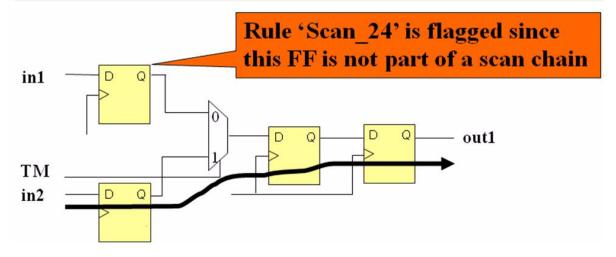

|      |            | : Ensure that all flip-flops are part of some scan chain 1143           |

|      |            | : Ensure that the scan chains do not contain inverters in scan path.    |

|      |            | 1149                                                                    |

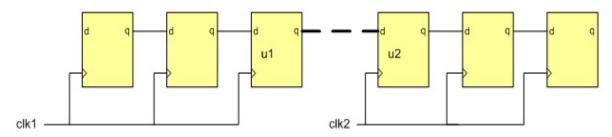

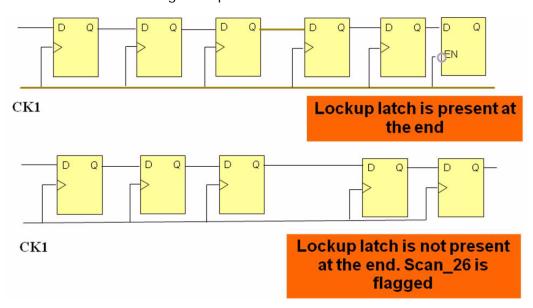

|      | Scan_26    | : Ensure that the scan chains contain lockup latch at chain end         |

|      |            | 1152                                                                    |

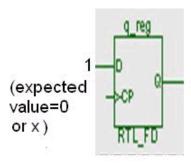

|      | Scan_27    | : Validate the connectivity of scan data input pin of a scan flip-flop  |

|      |            | 1156                                                                    |

|      | Scan_28    | : Validate the desired value at scan enable pin of scan flip-flop       |

|      |            | 1163                                                                    |

| Scan_29 :       | Ensure that the scan chains do not have inversions in scan path 1166                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Scan 30         | Reports observable flip-flop list1169                                                                                                |

|                 | Reports flip-flops with constant value data pin1171                                                                                  |

|                 | Reports scanout ports that are not output ports during scan                                                                          |

| _               | mode                                                                                                                                 |

| Scan_33 :       | : Reports scanin ports that are not inputs during scan mode 1177                                                                     |

| Scan_34 :       | Reports top test signals not named as per dedicated parameters 1180                                                                  |

| Scan_35 :       | Ensure that the scan chains do not exceed maximum specified length1183                                                               |

| Scan_36 :       | Ensure that the scan chains are balanced in length, that is, they should not deviate more than allowed from the expected length 1187 |

|                 | Ensure that the scan chains start with a positive edge flip-flop 1191                                                                |

| Scan_39 :       | Ensure that each scan flip-flop in a design is part of only one scan chain1195                                                       |

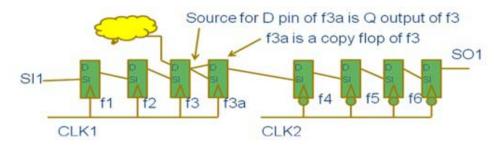

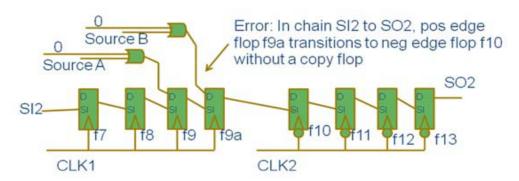

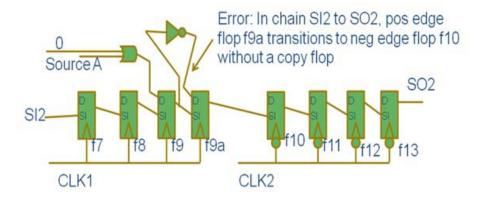

| Scan_40 :       | Ensure that the scan chains have a 'copy flip-flop' at positive to negative clock edge crossing1198                                  |

| Scan_41 :       | : Scanout port should be driven by pad terminal of pad cells 1202                                                                    |

| Sanity Check Ru | ules 1209                                                                                                                            |

|                 |                                                                                                                                      |

| dftParam        | <b>Check_02</b> : Sanity check to ensure that parameter rme_selection                                                                |

|                 | points to a valid directory                                                                                                          |

| dsmParar        | mSanity_00: Performs sanity checks on the defined parameter                                                                          |

| ISID O .        | values                                                                                                                               |

| attusmuo        | <pre>instraintCheck_01 : Performs sanity checks on the<br/>'atspeed_clock_frequency' and 'clock_shaper constraints 1214</pre>        |

| dftDcmCo        | enstraintCheck_02: Performs SGDC sanity check on the clock                                                                           |

| ditDsilico      | constraint                                                                                                                           |

| dftDsmCo        | enstraintCheck_04 : Performs a sanity check as to whether the                                                                        |

| uitD3iii00      | expect_frequency constraint is specified on a module that is a                                                                       |

|                 | clock_shaper1218                                                                                                                     |

| dftDsmCo        | onstraintCheck_05: Performs a sanity check as to whether the                                                                         |

|                 | expect_frequency constraint is specified on a module that is a clock_shaper                                                          |

| dftDsmCo        | onstraintCheck_06 : gating_cell constraint should have equal                                                                         |

|                 | width for -clkoutTerm, -enTerm and -obsTerm                                                                                          |

| dftDsmConstraintCheck_07 : Do not apply the abstract_port constraint                       |   |

|--------------------------------------------------------------------------------------------|---|

| on non-black box cells                                                                     |   |

| dftDsmConstraintCheck_08 : Report conflict of simulation value with                        |   |

| enabling value given in the constraint file 122                                            | 6 |

| dftDsmConstraintCheck_ComplexCell : Constraint complex_cell is                             |   |

| obsolete and should be replaced by the clock_shaper constraint                             | t |

| 1227                                                                                       |   |

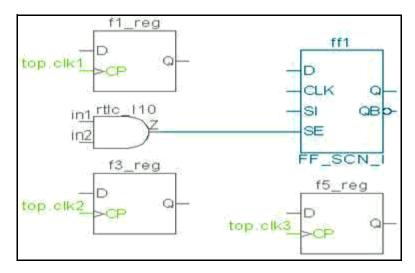

| Scan Enable Rules1228                                                                      | 3 |

| Overview                                                                                   | 8 |

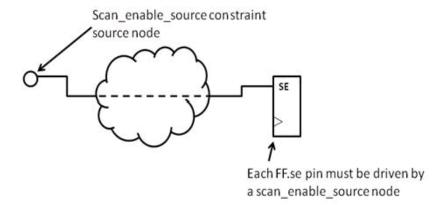

| SE_Sanity_01: User specified scan_enable_source must feed scan enable                      | į |

| pin of a scan flip-flop122                                                                 | 9 |

| SE_Sanity_02: When -active_value is applied on user specified                              |   |

| scan_enable_source, it must bring all scan flip-flop in mask-                              |   |

| mode (scan chain mode) 123                                                                 | 1 |

| SE_Sanity_03: In atspeed mode, user specified scan_enable_source                           |   |

| should not get a value other than specified -active_value in                               | , |

| atspeed mode                                                                               |   |

| SE_Sanity_04: Avoid specifying scan_enable_source in fan-out of another scan_enable_source |   |

| SE_Sanity_05 : scan_enable_source with -clock should be actually driven                    |   |

| by logic clocked on specified clock                                                        |   |

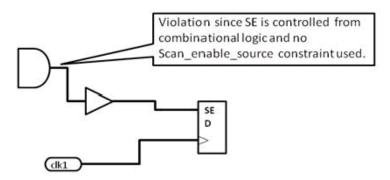

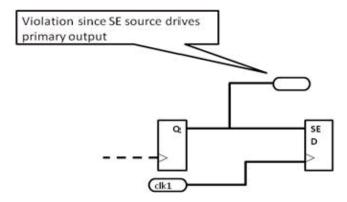

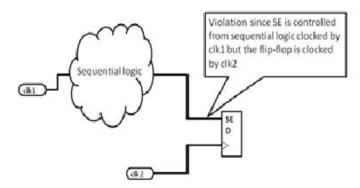

| SE_01 : Scan Enable cannot be driven by combinational logic                                |   |

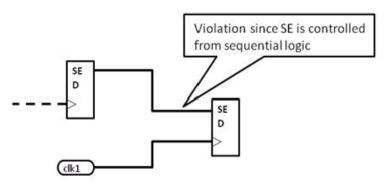

| SE_02 : Scan Enable cannot be driven by sequential logic                                   |   |

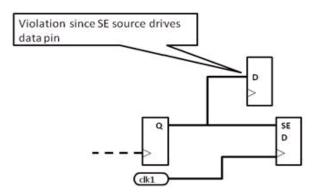

| SE_03 : Scan Enable cannot be used as data input to a flip-flop 124                        |   |

| SE_04 : Scan Enable cannot feed primary output                                             |   |

| SE_05 : Scan enable source must feed flip-flops with the same clock as is                  |   |

| specified in the -clock field                                                              |   |

| SE_06 : All scannable flip-flops must have their scan enable pins driven by                |   |

| a designated scan_enable_source                                                            |   |

| Scan Power Rules1263                                                                       | 3 |

| Overview                                                                                   | 3 |

| SP_01: No voltage domain crossing in a scan chain                                          | 4 |

| SP_02: A PMU Test Control cell (PMUWR) must be inserted directly in the                    |   |

| fan-in of the PMU (Power Management Unit) 126                                              |   |

| SP_03: Control signal of the ISO cells, Power Switches and Retention cells                 |   |

| must be driven by a PMU Test Control cell (PMUWR) 126                                      |   |

| SP_04: A PMU Test Control Cell (PMUWR) should only drive control signal                    |   |

| of ISO cells, Power Switches and Retention cells 1270                                      |   |

| SP 05 · A scan chain containing flin-flons in nower management test contro                 | 1 |

| modules should be stand alone                                                 | 1272  |

|-------------------------------------------------------------------------------|-------|

| SoC Rules 1                                                                   | 273   |

| Overview                                                                      | 1273  |

| Soc_00 : Generates an abstract view of a design                               | 1274  |

| Soc_04 : Show system state for a given tag                                    |       |

| Soc_05 : Performs IP verification for mode, clock, controllability and        |       |

| observability in the SoC flow                                                 | 1284  |

| Soc_06: Provides the hierarchical names of all instances appended with        | ו pin |

| name                                                                          | 1292  |

| Testability Analysis Rules1                                                   | 296   |

| Overview                                                                      | 1296  |

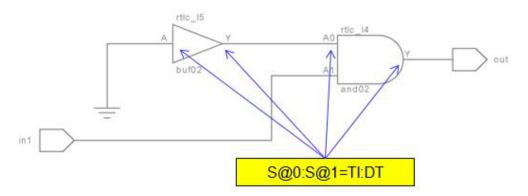

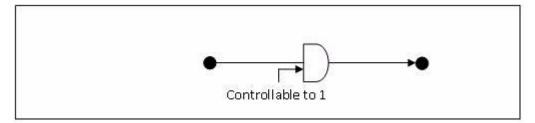

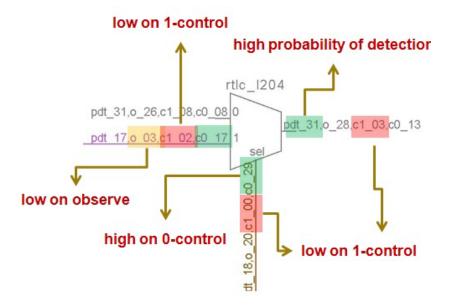

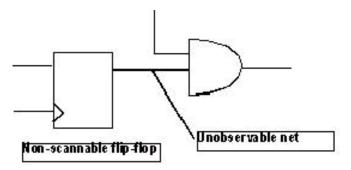

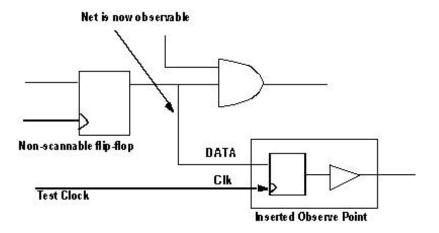

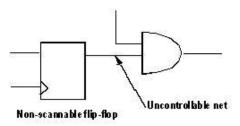

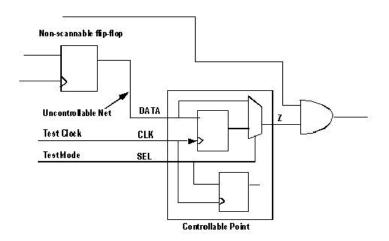

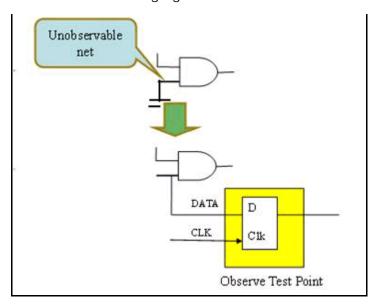

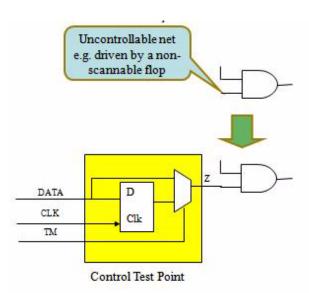

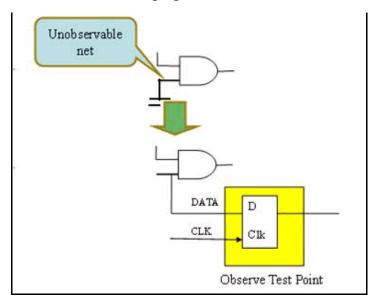

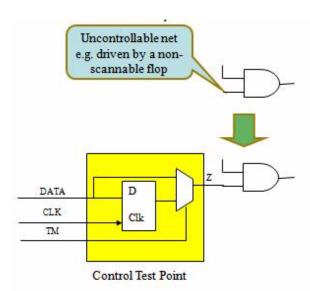

| TA_01: Add test points to improve controllability                             | 1297  |

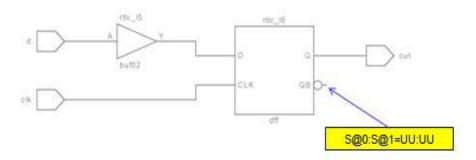

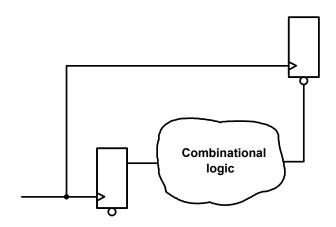

| TA_02 : Select test points to improve observability                           | 1307  |

| TA_05: This rule has been deprecated                                          | 1315  |

| TA_06: Generate testcoverage when all SpyGlass DFT ADV suggested              | test  |

| points are selected                                                           | 1316  |

| TA_07: Ensure that the testmode signals that only control asynchronic         | ous   |

| set or reset pins are unrestricted during capture                             | 1324  |

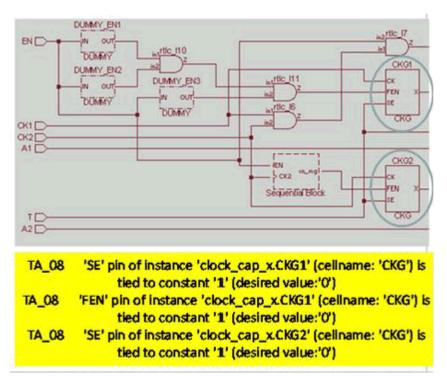

| TA_08: Reports test enable/enable pins of clock gating cells that are tie     | ed to |

| an undesired value                                                            |       |

| TA_09: Reports cause of uncontrollability or unobservability and estim        | ates  |

| the number of nets whose controllability/ observability is                    |       |

| impacted                                                                      |       |

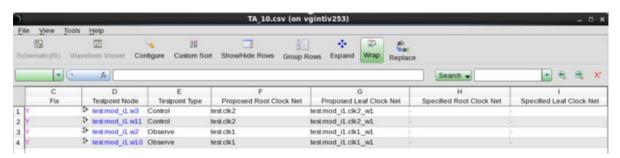

| <b>TA_10:</b> Add test points to improve controllability and observability    |       |

| Test Compression Rules 1                                                      |       |

| Overview                                                                      |       |

| TC_01: Pipeline depth for head registers should equal head_register_c 1352    | lepth |

| TC_02: Head registers must be driven by unique primary inputs                 |       |

| TC_03: Head registers to the same decompressor must use the same of and edge. |       |

| TC_04 : Pipeline depth for tail registers should equal tail_register_dep 1358 | th    |

| TC_05: Tail registers from the same compressor must be driven by the          |       |

| same clock and edge                                                           | 1360  |

| Topology Rules1                                                               |       |

| Overview                                                                      |       |

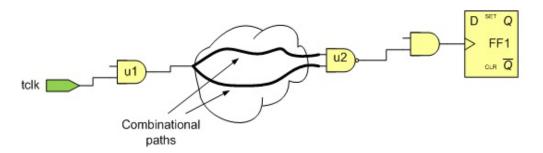

| <b>Topology_01:</b> Ensure that the design does not contain combinational le  |       |

| in the capture mode                                                           | 1262  |

| Topology_      | _02 : No asynchronous pin to pin paths                                 | 1369    |

|----------------|------------------------------------------------------------------------|---------|

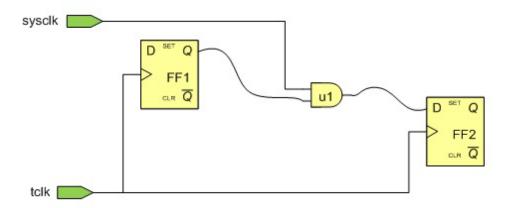

| Topology_      | <b>_03</b> : Avoid sequentially derived asynchronous signals with      |         |

|                | common clock                                                           |         |

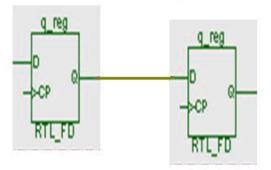

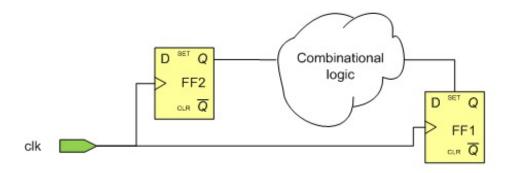

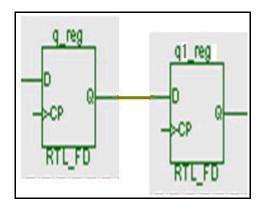

| Topology_      | _04 : Reports direct connection between two registers                  | 1378    |

| Topology_      | _05: Ensure that the design does not have a Wire-OR and \              | Wire-   |

|                | AND                                                                    | 1382    |

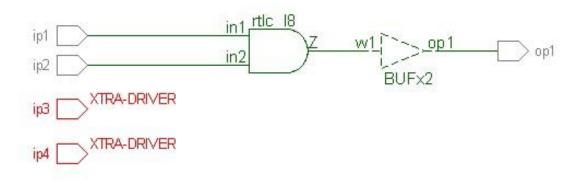

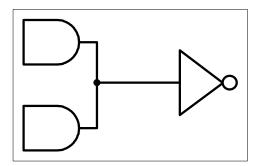

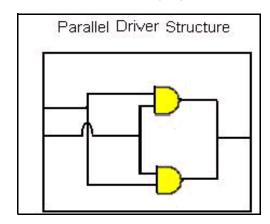

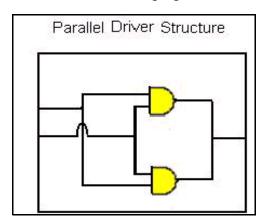

| Topology_      | _07_flat : Do not use parallel drivers                                 | 1390    |

| Topology_      | _07_rtl : Do not use parallel drivers                                  | 1394    |

|                |                                                                        |         |

| . 33-          | out                                                                    |         |

| Topology_      | _10 : Avoid long logic paths                                           | 1401    |

| Topology       | <b>_11</b> : Ensure that there are no combinational paths from a c     | clock   |

| . 33-          | pin to a root level port in the capture mode                           |         |

| Topology_      | _12: Ensure that all top level inputs are connected to a pullu         | up or   |

| . 35-          | pulldown device                                                        | 1409    |

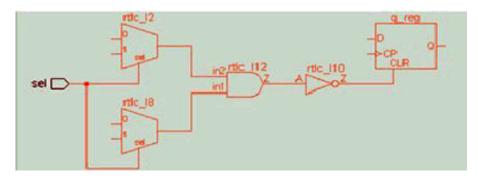

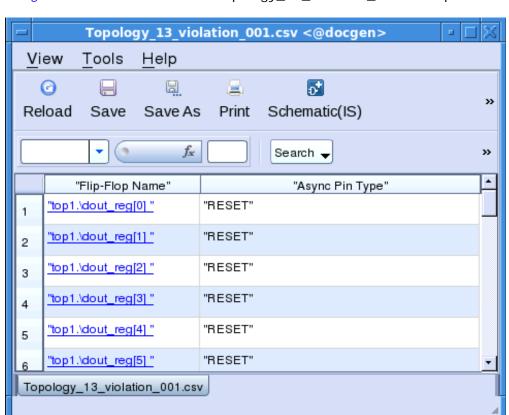

| Topology_      | _13: Reports the presence of combinational re-convergence              | e to    |

|                | flip-flops asynchronous pins                                           | 1412    |

| Topology_      | _14: Reports if there is a convergence at the async pins of a          | a flip- |

|                | flop                                                                   | 1418    |

| Topology_      | <b>_15</b> : Ensure that the top-level output/inout ports, except sca  | nout    |

|                | ports, are controllable                                                |         |

| Topology_      | <b>_16</b> : <b>Topology_17</b> : Reports undriven terminals and nets. | 1429    |

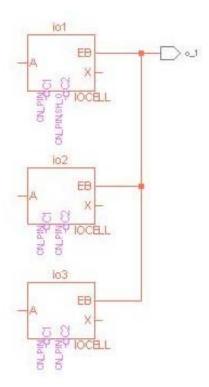

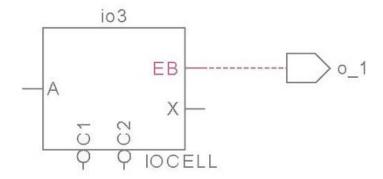

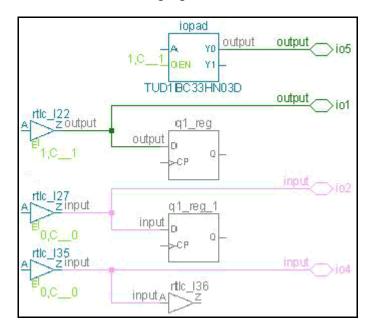

| Tristate Rules | 1                                                                      | 1431    |

| Overview       |                                                                        | 1431    |

| Tristate_0     | O1: Reports inferred tristate components                               | 1433    |

| Tristate_0     | 03 : Tri-state enables should be disabled during scan shifting         | g       |

|                | 1436                                                                   |         |

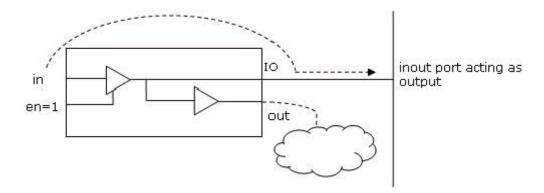

| Tristate_0     | <b>D4_capture</b> : Ensure that inout ports are forced to outputs of   | only    |

|                | in capture mode                                                        | 1440    |

| Tristate_0     | <b>D4_shift</b> : Ensure that the inout ports are forced to outputs    |         |

|                | in shift mode                                                          | 1445    |

| Tristate_0     | <b>D5</b> : Tristate buses should have a pull-up or pull-down conne    | ection  |

|                | 1450                                                                   |         |

| Tristate_0     | <b>26</b> : Ensure that the tristate bus enables are fully decoded so  |         |

|                | exactly one driver is active at any time                               | 1454    |

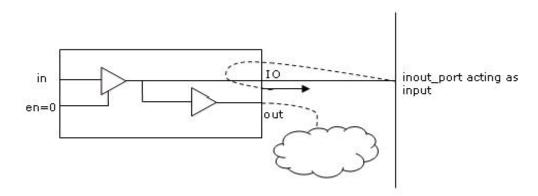

| Tristate_0     | <b>D7_capture</b> : Ensure that all Inout ports are inputs only in     |         |

|                | capture mode                                                           |         |

| Tristate_0     | <b>D7_shift</b> : All Inout ports are inputs only in shift mode        | 1465    |

| Tristate (     | <b>O8</b> capture: Reports input ports not forced to only input or     | only    |

| output direction in the capture mode                                                                              |

|-------------------------------------------------------------------------------------------------------------------|

| Tristate_08_shift: Reports inout ports not forced to only input or only                                           |

| output mode in the shift mode1473                                                                                 |

| Tristate_09: Ensure that the tristate buses are designed to prevent bus contention and floating during scan shift |

| Tristate_10: Reports tristate bus enables that are driven by flip-flops                                           |

| where capture clock causes x-condition                                                                            |

| <b>Tristate_11:</b> Ensure that only one tri-state enable is active in shift mode. 1487                           |

| Tristate_12: Bus enables should not be forced in scan shift 1490                                                  |

| Tristate_13: Generates bus width report                                                                           |

| Tristate_14: Ensure that the testclock are not connected to the enable pin of tristate buffer                     |

| Tristate_15: Ensure that the primary bidirectional pin is only driven by a tristate gate                          |

| Tristate_16: Associate a bus keeper to each tri-state                                                             |

| Tristate_17: Reports bidirectional ports that do not have fixed direction in DBIST mode                           |

| Tristate_18: Reports pins of bus keeper that are not fitted with a                                                |

| controllable pullup1508                                                                                           |

| Integrity Checks 1512                                                                                             |

| Overview                                                                                                          |

| BlackBoxDetection: This rule has been deprecated                                                                  |

| dftMandatory_Constraint_Check: Reports inadequacy of the user-<br>specified mandatory constraints                 |

| dftMultiplyDrivenPowerRail: Reports all the power rails that have external drivers as well                        |

| dftOptional_Constraint_Check : Reports whether or not the optional                                                |

| constraint requirements of SpyGlass DFT ADV rules are met 1521                                                    |

| dftSetup: Performs some pre-DFT run initial setup                                                                 |

| dftParamCheck_01: Ensure that the dftSetLatchFedByTClkAsT parameter                                               |

| is not used along with the dft_scannable_latches parameter 1525                                                   |

| dftSGDCExistence_00: Ensures that constraints are specified for all top                                           |

| modules 1527                                                                                                      |

| dftSGDCSTX_000: Performs implementation level sanity checks on the                                                |

| SGDC constraints                                                                                                  |

| dftSGDCSTX_051: Ensure that there is no duplicate declaration of a node                                           |

| for the same scalar tag153                                               | 2 |

|--------------------------------------------------------------------------|---|

| dftSGDCSTX_053: Reports incorrectly merged tags                          | 4 |

| dftSGDCSTX_054: Ensure that the merge tag specification do not span      |   |

| multiple lines 153                                                       | 7 |

| dftSGDCSTX_055: Ensure that there are no conflicting values for the same | 9 |

| node when used in a merged tag 153                                       | 9 |

| dftSGDCSTX_057: Reports mismatches in node widths                        | 1 |

| dftSGDCSTX_058: Ensure that the testmode and testclock are separate      |   |

| ports                                                                    | 3 |

| dftSGDCSTX_059: Ensure that the testmode and testclock are separate      |   |

| ports                                                                    | 5 |

| dftSGDCSTX_060: Reports memory_type constraint defined for a module      | 9 |

| which is not a black box154                                              |   |

| dftSGDCSTX_061: Reports gating_cell constraint having different width    |   |

| for -clkoutTerm, -enTerm and -obsTerm 154                                | 9 |

| dftSGDCSTX_062: Checks for the existence of the 'module_pin' constrain   | t |

| in the design                                                            |   |

| dftSGDCSTX_064: Performs sanity checks for macros                        | 4 |

| dftSGDCSTX_069: Ensure that the user-specified design state and          |   |

| scan_chain constraint are consistent 155                                 | 9 |

| dftSGDCSTX_070: Ensure that the user-specified set_case_analysis and     |   |

| test_mode                                                                |   |

| -functional are consistent 156                                           | 1 |

| dftSGDCSTX_071: User-specified 'clock_shaper' 'complex_cell' and 'pll'   |   |

| should apply to at least an instance, in case of 'clock_shaper -         |   |

| register, or to a module156                                              | 3 |

| dftSGDCSTX_072: Performs sanity check for the require_structure          |   |

| constraint 156                                                           | 6 |

| dftSGDCSTX_073: Performs sanity checks for module_bypass 156             | 8 |

| dftSGDCSTX_074: Performs sanity checks for -constraint_message_tag       |   |

| field of the require_constraint_message_tag and                          |   |

| illegal_constraint_message_tag constraints 157                           | 1 |

| dftSGDCSTX_075: Performs sanity check for the clock_shaper constrain     | t |

| 1574                                                                     |   |

| dftSGDCSTX_076: Performs sanity check for the missing required fields o  | f |

| the require_path, illegal_path, require_strict_path,                     |   |

| require_value, illegal_value, require_frequency,                         |   |

| require_constraint_message_tag and                                       |   |

| illegal_constraint_message_tag constraints 157                           | 6 |

| ditsGDCSTX_0//: Performs sanity check for usages of instance based    |    |

|-----------------------------------------------------------------------|----|

| macros in require_path, illegal_path, require_strict_path,            |    |

| require_value, illegal_value, require_frequency, and                  |    |

| require_pulse constraint                                              | 78 |

| dftSGDCSTX_078: Sanity check for usage of macros in require_value an  |    |

| illegal_value constraints when -value_type field is used 158          |    |

| dftSGDCSTX_080 : Performs sanity checks on design-object-type/        | -  |

| conditional-checks(filtering) based fields                            | ຊາ |

| dftSGDCDefineMacroCheck_01 : The define_macro constraint sanity       | 02 |

| checks15                                                              | O1 |

|                                                                       | 91 |

| dftSGDCDefineMacroCheck_02 : The define_macro constraint sanity       |    |

| checks                                                                |    |

| dftUserMacroSanityCheck_01 : Performs sanity check for usages of use  | er |

| macros in the require_path, illegal_path, require_strict_path,        |    |

| require_value, illegal_value, require_frequency, and                  |    |

| require_pulse constraints159                                          |    |

| dftVSTOPDUSetup: This is a set up rule                                |    |

| Diagnose_ScanChain: Ensure that the scan chain must exist between the | ne |

| user-specified scanin and scanout points                              | 00 |

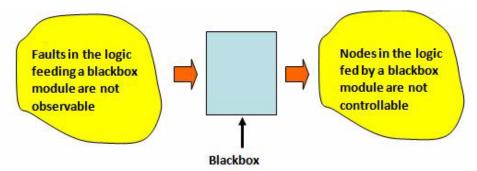

| dumpBlackBox: Identify black boxes in a design and dump corresponding | ng |

| 'scan_wrap' constraints in a file                                     | 06 |

|                                                                       |    |

| Reports in the SpyGlass DFT ADV Product160                            | ١0 |

|                                                                       |    |

| add_fault16                                                           |    |

| atpg_conflict_testpoints16                                            |    |

| bist_ready_summary16                                                  |    |

| dft_connectivity_check_summary16                                      |    |

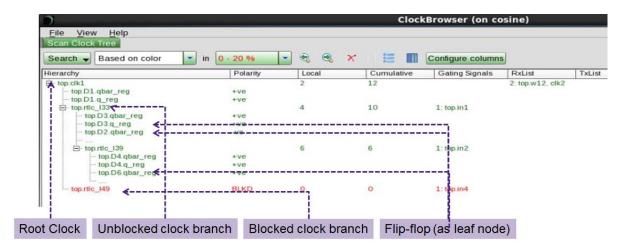

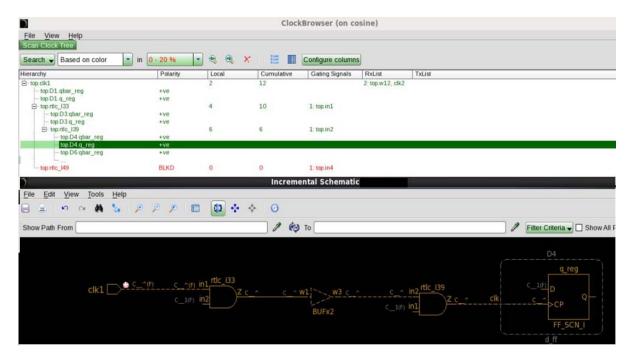

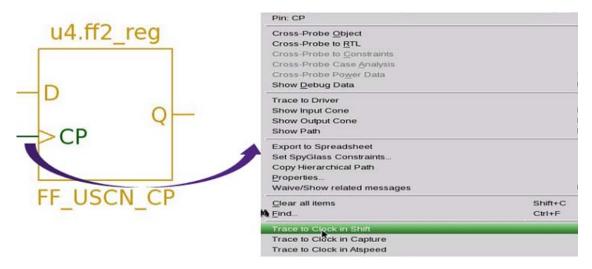

| Scan Clock Tree Report                                                |    |

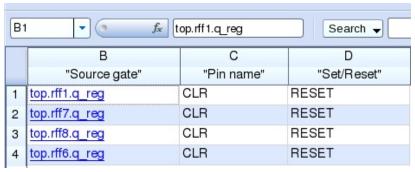

| dft_ff_set_reset_active162                                            |    |

| dft_ff_set_reset_sequential_in_capture162                             |    |

| dft_ff_set_reset_sequential_in_shift162                               |    |

| dft_ff_X_source_for_tristate_enable162                                | 26 |

| dft_latch_enable163                                                   | 29 |

| dft_mandatory_sgdc 163                                                | 31 |

| dft_memory_report16                                                   | 35 |

| dft_multibit_flipflops16                                              |    |

| dftmax_ultra_configuration 163                                        | 37 |

| dftmax_ultra_configuration_command 163                                | 39 |

| dft_self_gating_logic_summary                                         | 39 |

|                                                                       |    |

| dft_self_gating_ff            | 1641 |

|-------------------------------|------|

| dft_self_gating_test_points   | 1643 |

| no_fault                      |      |

| dft_optional_sgdc             | 1647 |

| dft_summary                   | 1649 |

| dft_tristate                  |      |

| dft_initialized_ffs           | 1652 |

| forced_scan                   |      |

| inferred_no_scan_ffs          | 1655 |

| dft_x_source_report           |      |

| dft_x_capture_report          | 1658 |

| no_scan                       |      |

| observable_ffs                |      |

| potentially_detected_faults   |      |

| scan_chain                    |      |

| scan_wrap                     | 1664 |

| soc_06_rpt                    |      |

| soft_error_metrics            |      |

| soft_error_registers_spfm     |      |

| stil_file                     |      |

| stuck_at_faults               |      |

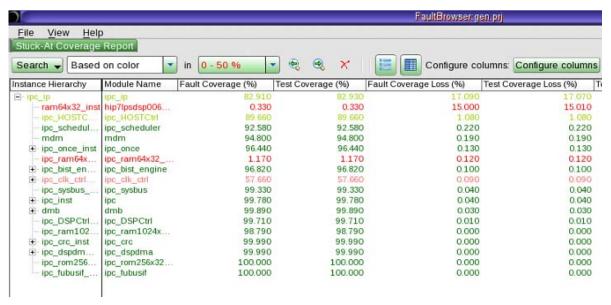

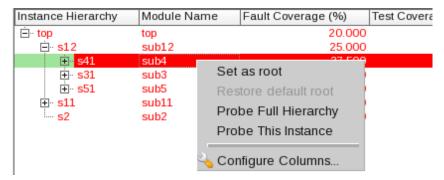

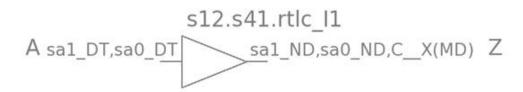

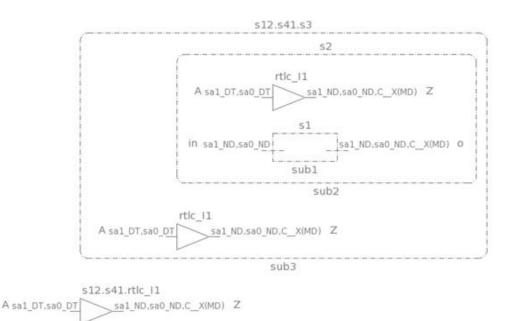

| stuck_at_coverage             |      |

| stuck_at_coverage_audit       |      |

| stuck_at_coverage_collapsed   |      |

| test_points_selected          |      |

| test_points_selected_2        |      |

| undetected_faults             |      |

| atspeed_03_rpt                |      |

| atspeed_04_rpt                |      |

| atspeed_07_rpt                |      |

| atspeed_08_rpt                |      |

| atspeed_clock_synchronization |      |

| dft_dsm_clock_frequency       |      |

| dft_dsm_clock_gating_cell     |      |

| dft_dsm_constr-err-file       |      |

| dft_dsm_enabled_flipflops     |      |

| dft_dsm_ip_report             |      |

| ff_async_reconvergence        |      |

| ff_clock_reconvergence        |      |

| no_atspeed                    |      |

| random nattern coverage       | 1722 |

| random_pattern_dc_testpoints                                   | 1729 |

|----------------------------------------------------------------|------|

| random_pattern_node_distribution                               |      |

| random_pattern_testpoints                                      |      |

| transition_coverage                                            |      |

| transition_coverage_audit                                      |      |

| transition_coverage_clockdomain                                |      |

| transition_coverage_collapsed                                  |      |

| transition_faults                                              |      |

| Customizing the SpyGlass DFT ADV Product                       | 1761 |

| Common SpyGlass DFT ADV Rule Parameters                        | 1761 |

| SpyGlass DFT ADV Rule Parameters                               | 1765 |