# Atrenta Console User Guide

Version N-2017.12-SP2, June 2018

## **Copyright Notice and Proprietary Information**

©2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

#### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

## Contents

| Preface                                                        | 17 |

|----------------------------------------------------------------|----|

| About This Book                                                | 17 |

| Contents of This Book                                          |    |

| Typographical Conventions                                      |    |

|                                                                |    |

| Introducing Atrenta Console                                    |    |

| Overview                                                       |    |

| Introducing Goals                                              |    |

| Introducing Methodologies                                      |    |

| Methodology Used by Atrenta Console                            |    |

| Before You Begin<br>Specifying Optional Environment Variables  |    |

| Invoking Atrenta Console Graphical User Interface              |    |

| Starting a New Session                                         |    |

| Loading the Previous Session                                   |    |

| Invoking Atrenta Console on a 64-bit Machine                   |    |

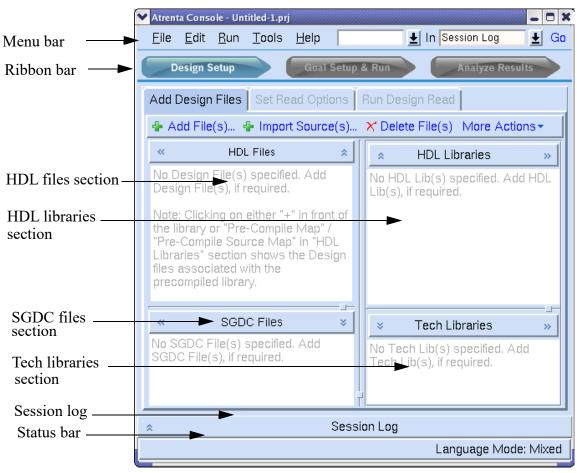

| GUI Details                                                    |    |

| Atrenta Console Flow                                           | 28 |

| Design Setup Stage                                             | 28 |

| Goal Setup and Run Stage                                       |    |

| Analyze Results Stage                                          |    |

| Files/Directories Created in Atrenta Console                   |    |

| Project File                                                   |    |

| Project Working Directory<br>Project Current Working Directory |    |

| File Generated in GUI                                          |    |

| Files/Directories Generated by Default                         |    |

| Files Generated to Support Special Features                    |    |

| Using Atrenta Console Graphical User Interface                 | 35 |

| Överview                                                       |    |

| Stage 1: Setting up the Design (Design Setup)                  |    |

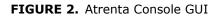

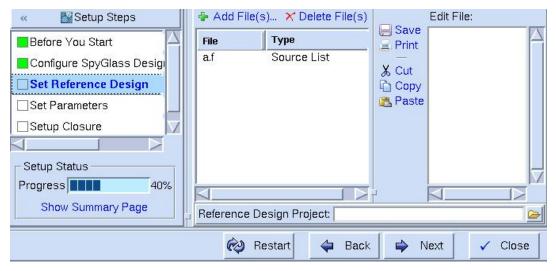

| Adding Design Files                                            |    |

| Adding Files in GUI                                  | 36   |

|------------------------------------------------------|------|

| Specifying Functionality Information of Gate Cells   | 42   |

| Specifying a List of .sglib Files                    | 44   |

| Specifying Compressed Verilog Designs                | 44   |

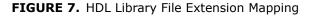

| Mapping File Extensions                              |      |

| Rearranging HDL Files                                |      |

| Performing Version Control                           |      |

| Editing Files                                        | 47   |

| Setting Stop Files                                   |      |

| Ignoring Files from SpyGlass Analysis                | 50   |

| Waiving Messages by File                             | 51   |

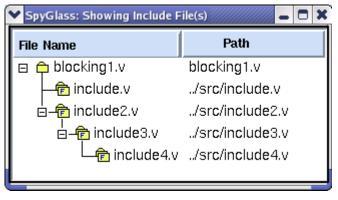

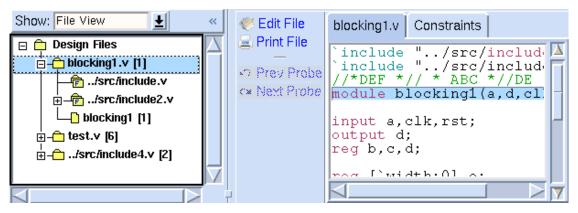

| Viewing Include Files                                |      |

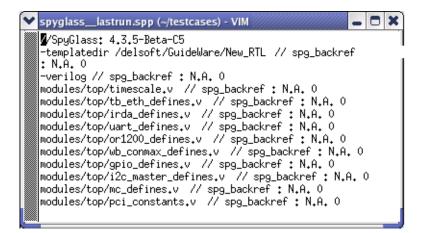

| Configuring Columns                                  |      |

| Viewing and Changing Design Read Options             | 52   |

| Using Verilog Constructs                             | 54   |

| Running Design Read                                  | 55   |

| Running Design Read in GUI                           | 55   |

| Running Design Read in Batch                         | 58   |

| Checks Performed During the Design Read Process      | 58   |

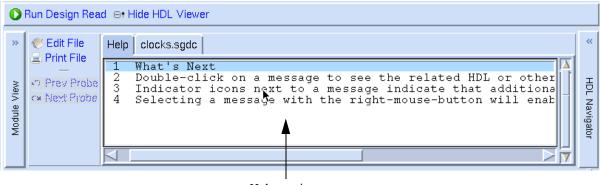

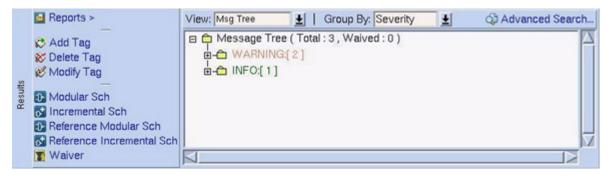

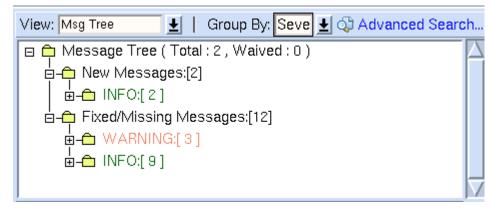

| Viewing Messages after Running Design Read           | 59   |

| Identifying Common Syntax Errors and Issues          | 59   |

| Tips for Debugging Syntax Errors                     |      |

| Viewing Reports                                      |      |

| Viewing Source Files                                 |      |

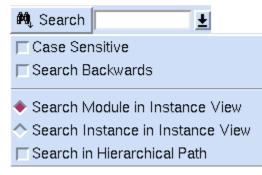

| Searching Instances                                  | 62   |

| Stage 2: Selecting a Goal (Goal Setup & Run)         | . 64 |

| Selecting a Goal                                     | 65   |

| Modifying a Goal                                     | 67   |

| Running Custom Goals                                 | 72   |

| Running Goals in Parallel                            |      |

| Viewing Directories Created After Goal Run           | 81   |

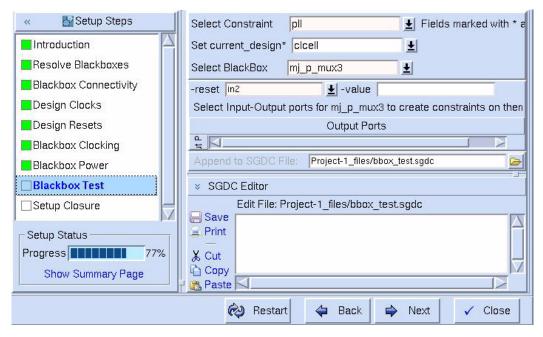

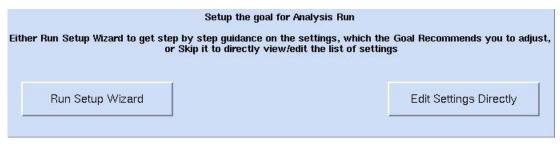

| Setting up the Goal                                  | 93   |

| Determining Parameter Precedence                     |      |

| Setting Parameters and Constraints for Selected Goal |      |

| Performing Sanity Checks for Parameters              |      |

| Using the Dual Design Read (DDR) Flow                |      |

| Incremental Mode Analysis                            |      |

| Setting Up the Goal in Batch Mode                    |      |

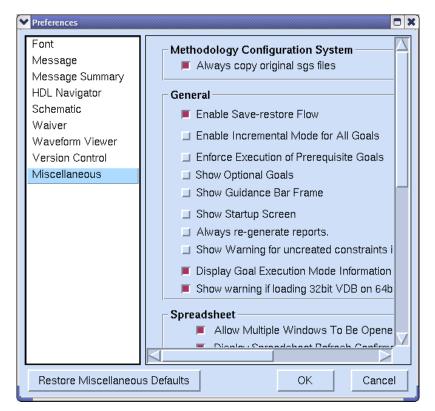

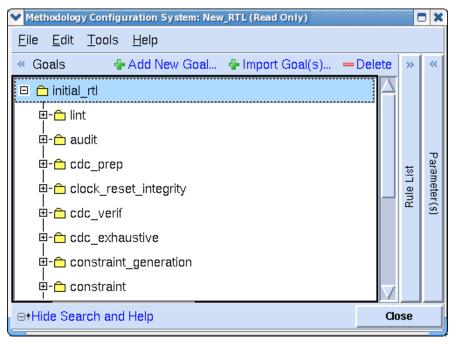

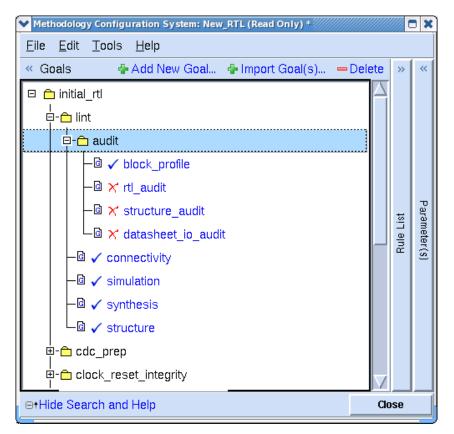

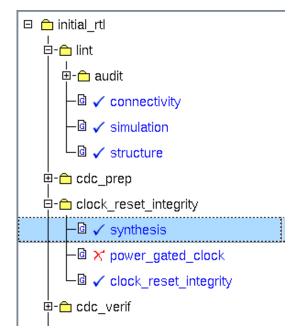

| The Methodology Configuration System                 |      |

| Running Prerequisite Goals                           |      |

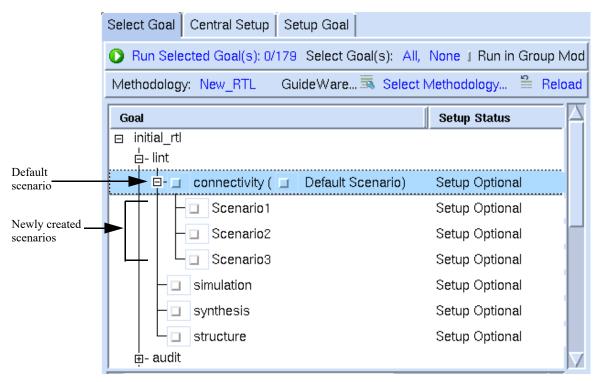

| Working with Scenarios                               |      |

| Creating Scenarios                                   |  |

|------------------------------------------------------|--|

| Modifying and/or Deleting Scenarios                  |  |

| Running Scenarios                                    |  |

| Directory Structure Created After Running a Scenario |  |

| Stage 3: Analyzing a Design (Analyze Results)        |  |

| Editing Source Files                                 |  |

| Viewing Goal Summary                                 |  |

| Comparing Results of Multiple SpyGlass Runs          |  |

| Introducing the Incremental Mode Feature             |  |

| Using the Incremental Mode Feature                   |  |

| Comparison Reported in Batch                         |  |

| Viewing Different Type of Results                    |  |

| Design Results                                       |  |

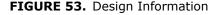

| SpyGlass CDC Solution Results                        |  |

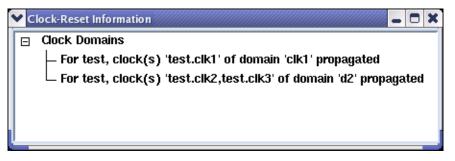

| SpyGlass Constraints Solution Results                |  |

| SpyGlass TXV Solution Results                        |  |

| SpyGlass DFT Solution Results                        |  |

| Power Results                                        |  |

| Viewing Results of Different Scenarios and Goals     |  |

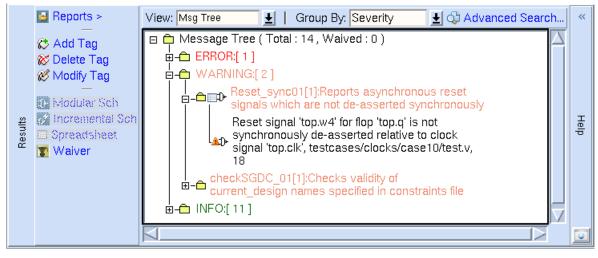

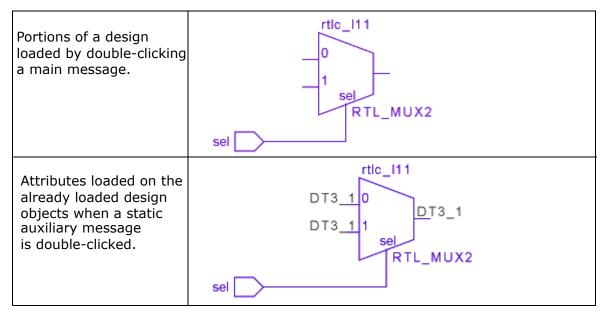

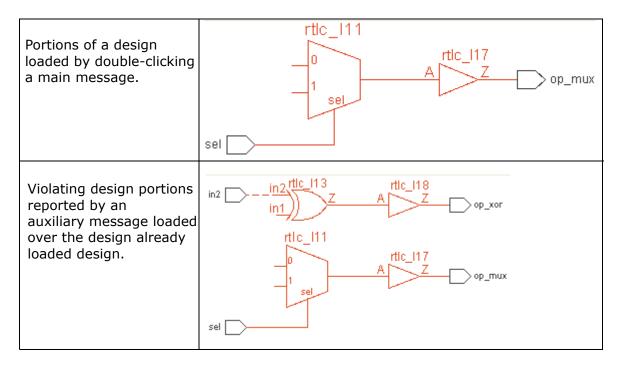

| Cross-probing from the Msg Tree Page                 |  |

|                                                      |  |

## Working with Input Design and Libraries ......129

| Overview                                                | 129 |

|---------------------------------------------------------|-----|

| Working with Precompiled Libraries                      |     |

| Advantages of Using Precompiling Libraries              |     |

| Specifying Modes in Which Libraries Should be Compiled  |     |

| Compiling HDL Files into a Library                      |     |

| Defining a Logical Library                              |     |

| Including HDL Files in the Logical Library              |     |

| Generating a Precompiled Library                        |     |

| Automatically Compiling Gate Libraries                  |     |

| Using the GUI to Automatically Compile Libraries        |     |

| Using the enable_gateslib_autocompile Option            |     |

| Using the force_gateslib_autocompile Option             |     |

| Using the AUTOENABLE_GATESLIB_AUTOCOMPILE Key           |     |

| Specifying a Cache Directory                            |     |

| Conditions for Auto-Compilation of Gate Libraries       |     |

| Built-in VHDL Libraries That Do Not Require Any Mapping |     |

| Precompiling Verilog Libraries                          |     |

| Naming and Mapping Verilog Libraries                    | 141 |

|                                                         |     |

| Structure of Precompiled Verilog Libraries                        | 142 |

|-------------------------------------------------------------------|-----|

| Library Searching Mechanism                                       | 142 |

| Working with Precompiled Verilog Libraries in Mixed Language Mode | 143 |

| Specifying Verilog Libraries by Using the 'uselib Statement       | 146 |

| Compiling Libraries in Mixed-Language Designs                     | 146 |

| VHDL Library Design Units Instantiated in Verilog Modules         | 147 |

| Verilog Modules Instantiated in VHDL Design Units                 |     |

| Searching Master Instance in Mixed-Language Mode                  | 147 |

| Debugging Issues in Gate Libraries                                | 148 |

| Specifying Precompiled Libraries for SpyGlass Analysis            | 149 |

| Specifying Multiple Technology Libraries of the Same Name         | 150 |

| Using Intermediate Logical Library Name Support in VHDL           | 151 |

| Working with Compressed Gate Library Files                        | 153 |

| Working with Encrypted Compiled Libraries                         | 154 |

| Creating Encrypted Library Dump                                   | 154 |

| Using Encrypted Library Dump                                      | 155 |

| Viewing Built-In Messages for Precompiled Libraries               | 156 |

| Impact of the addrules Option While Using Pre-compiled Dump       |     |

| Impact of the ignorerules Option While Using Pre-compiled Dump    |     |

| Mapping a File Extension with a Compilation Language              |     |

| Inferring Language from File Extension During Compilation         |     |

| Specifying Compilation Options in a Source File                   | 165 |

| Specifying Files in the Order of Their Dependencies               |     |

| Compiling Verilog Files Containing SystemVerilog Keywords         |     |

| Compiling the Set of Verilog and SystemVerilog Files Separately   |     |

| Using File Extension Based Compilation Flow                       |     |

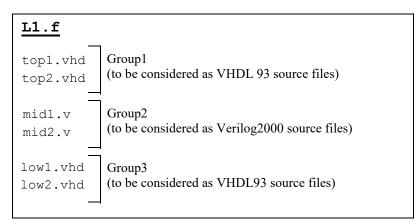

| Working with Encrypted Design Files                               |     |

| Introducing the Use Model for IP Encryption in SpyGlass           |     |

| Encrypting IPs by Using the spyencrypt Utility                    |     |

| Arguments of the spyencrypt Utility                               |     |

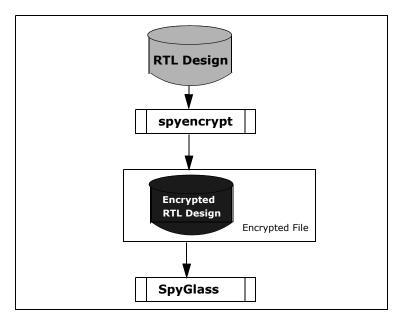

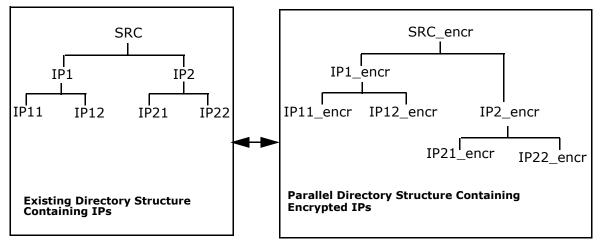

| Encrypting IPs Spread Across a Hierarchical Directory Structure   |     |

| Viewing Encryption Summary in a Report                            |     |

| Specifying Encrypted Files for SpyGlass Analysis                  |     |

| Specifying Encrypted Files through GUI                            |     |

| Specifying Encrypted Files through a Project File                 |     |

| Working with Mixed-Language Designs                               |     |

| Instantiating Verilog Modules in VHDL Architectures               |     |

| Instantiating as Component Instance                               |     |

| Instantiating as Entity Instance                                  |     |

| Instantiating VHDL Design Units In Verilog Modules                |     |

| Examples of Instantiating VHDL Design Units in Verilog Modules    | 187 |

|          | Mapping Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 189                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|          | Mapping between VHDL Generics and Verilog Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 189                                                                                                                               |

|          | Current Limitation with Mixed-language Designs in SpyGlass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 190                                                                                                                               |

| Wo       | orking with DesignWare® Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 192                                                                                                                               |

|          | Prerequisites for Enabling DesignWare Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 192                                                                                                                               |

|          | Specifying Path of DesignCompiler Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 192                                                                                                                               |

|          | Enabling the DesignWare Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|          | Reusing Netlist of DesignWare Modules during SpyGlass Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

|          | List of DesignWare Modules Supported in SpyGlass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 195                                                                                                                               |

|          | Using DesignWare Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198                                                                                                                               |

| Sp       | ecifying Pragmas in HDL Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 199                                                                                                                               |

| -        | Supported Pragmas for Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 199                                                                                                                               |

|          | Supported Pragmas for VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 199                                                                                                                               |

| Wo       | orking with Black Boxes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 200                                                                                                                               |

|          | Inferring Black Boxes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|          | Understanding the Black Box Inference Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 201                                                                                                                               |

|          | Using the Black Box Inference Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|          | Checking the Inferred Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 202                                                                                                                               |

|          | Using the Corrected Inferred Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|          | Stopping Black Box Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 204                                                                                                                               |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| На       | ndling Out of Memory Situations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 205                                                                                                                               |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

|          | ndling Out of Memory Situations<br>porting Messages at Module Boundary<br>Identifying Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 206                                                                                                                               |

|          | porting Messages at Module Boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>206</b><br>206                                                                                                                 |

|          | porting Messages at Module Boundary<br>Identifying Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>206</b><br>206<br>207                                                                                                          |

| Re       | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>206</b><br>206<br>207<br>207                                                                                                   |

| Re       | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 206<br>207<br>207<br>207<br>208                                                                                                   |

| Re       | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 206<br>207<br>207<br>207<br>208<br>208                                                                                            |

| Re       | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 206<br>207<br>207<br>207<br>208<br>208<br>209                                                                                     |

| Re       | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206<br>207<br>207<br>207<br>208<br>208<br>209<br>209                                                                              |

| Re<br>Co | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design<br>Interpreting Synthesis Pragmas                                                                                                                                                                                                                                                                                                                                                                                                             | 206<br>207<br>207<br>207<br>208<br>208<br>209<br>209<br>210                                                                       |

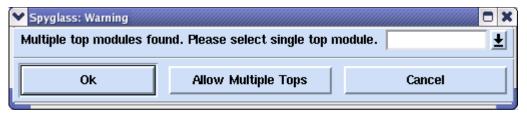

| Re<br>Co | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Specifying a Top-level Design Unit                                                                                                                                                                                                                                                                                                                                     | 206<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212                                                                |

| Re<br>Co | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas                                                                                                                                                                                                                                                                                                                                         | 206<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212                                                                |

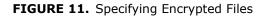

| Re<br>Co | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Specifying a Top-level Design Unit                                                                                                                                                                                                                                                                                                                                     | 206<br>207<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212<br>212                                                  |

| Re<br>Co | porting Messages at Module Boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212<br>212<br>212<br>213<br>214                                    |

| Re<br>Co | porting Messages at Module Boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212<br>212<br>212<br>213<br>214<br>215                             |

| Re<br>Co | porting Messages at Module Boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206<br>207<br>207<br>208<br>209<br>209<br>210<br>212<br>212<br>212<br>212<br>213<br>214<br>215<br>216                             |

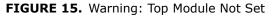

| Re<br>Co | porting Messages at Module Boundary<br>Identifying Modules<br>Enabling the Feature<br>Impact of the Feature<br>ntrolling the RTL Synthesis Engine<br>Limiting Analysis of Memories<br>Preserving all instances and nets in a design<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Interpreting Synthesis Pragmas<br>Specifying a Top-level Design Unit<br>Advantage of Specifying a Top-Level Design Unit<br>Setting a Top-Level Design Unit<br>Multiple Top-Level Design Units<br>Language-Specific Behavior While Specifying a Top-Level Module<br>Stopping Design Units<br>Implications After Stopping Design Units | 206<br>207<br>207<br>207<br>208<br>208<br>209<br>209<br>209<br>210<br>212<br>212<br>212<br>212<br>213<br>214<br>215<br>216<br>217 |

| Re<br>Co | porting Messages at Module Boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 206<br>207<br>207<br>207<br>208<br>208<br>209<br>209<br>210<br>212<br>212<br>212<br>212<br>213<br>214<br>215<br>216<br>217<br>218 |

| Ignoring Files and Design Units From SpyGlass Analysis                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Difference between Ignored and Stopped Design Units                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |

| Ignoring Files Containing Design Units                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                               |

| Ignoring Individual Design Units                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

| Analyzing Selective Design Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                               |

| Working with 'celldefine Modules                                                                                                                                                                                                                                                                                                                                                                                                                           | 226                                                                                                                                                           |

| Performing Rule-Checking on 'celldefine Modules                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |

| Performing Hierarchical Rule-Checking in 'celldefine Modules                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                               |

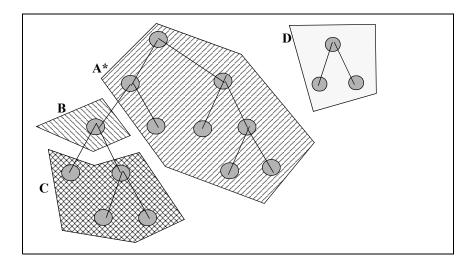

| Working with Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                 | 229                                                                                                                                                           |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                               |

| Goal Files                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                               |

| Naming Convention of a Goal File                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

| Details Present in a Goal File                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                               |

| Selection of Goal Files based on Language Mode                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                               |

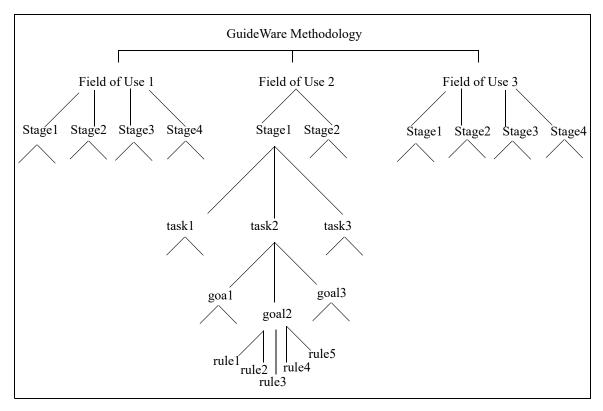

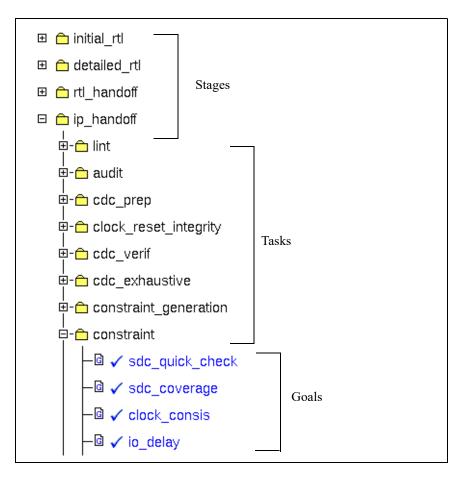

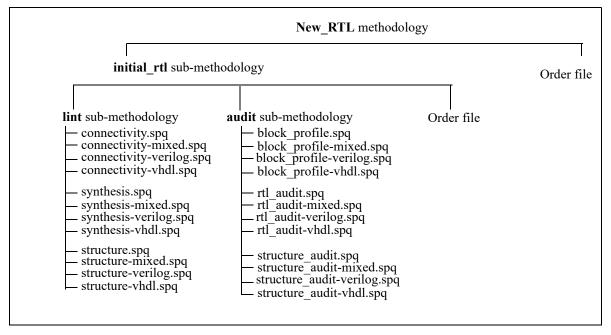

| GuideWare Reference Methodology                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |

| Structure of the GuideWare Reference Methodology                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

| Specifying an Active Methodology                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

| Specifying a Current Methodology                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |

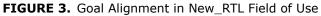

| Configuring a Methodology<br>Creating a Methodology                                                                                                                                                                                                                                                                                                                                                                                                        | 244                                                                                                                                                           |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology                                                                                                                                                                                                                                                                                                                                                                             | <b>244</b><br>246<br>248                                                                                                                                      |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology                                                                                                                                                                                                                                                                                                                                 | <b>244</b><br>246<br>248<br>249                                                                                                                               |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology                                                                                                                                                                                                                                                                                                   | <b>244</b><br>246<br>248<br>249<br>249                                                                                                                        |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology                                                                                                                                                                                                                                                                    | <b>244</b><br>246<br>248<br>249<br>249<br>249<br>251                                                                                                          |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals                                                                                                                                                                                                                                                  | <b>244</b><br>246<br>248<br>249<br>249<br>249<br>251<br>251                                                                                                   |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog                                                                                                                                                                                                               | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>251<br>253                                                                                            |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog                                                                                                                                                                  | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>251<br>253<br>253                                                                                     |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals.                                                                                                                                              | <b>244</b><br>246<br>248<br>249<br>249<br>249<br>251<br>251<br>251<br>253<br>253<br>253<br>255                                                                |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals                                                                                                                             | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>251<br>253<br>253<br>253<br>255<br>256                                                                |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals.<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog.<br>Importing Goals.<br>Deleting Goals.<br>Copying Goals                                                                                                        | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>253<br>253<br>253<br>255<br>256<br>256                                                                |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals.<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog.<br>Importing Goals.<br>Deleting Goals.<br>Copying Goals.<br>Modifying Goals.                                                                                   | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>253<br>253<br>253<br>255<br>256<br>256<br>256<br>256                                                  |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals<br>Modifying Goals<br>Modifying Goal Properties                                                                             | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>253<br>253<br>253<br>255<br>256<br>256<br>256<br>256<br>256<br>257                                    |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals<br>Modifying Goals<br>Modifying Goals<br>Enabling/Disabling a Goal                                                          | <b>244</b><br>246<br>248<br>249<br>249<br>251<br>251<br>251<br>253<br>253<br>255<br>256<br>256<br>256<br>256<br>256<br>256<br>257<br>259                      |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals<br>Copying Goals<br>Modifying Goals<br>Modifying Goal Properties<br>Enabling/Disabling a Goal                               | <b>244</b> 246 248 249 249 249 251 251 253 253 255 256 256 256 256 256 257 259 259                                                                            |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals<br>Modifying Goals<br>Modifying Goals<br>Enabling/Disabling a Goal                                                          | 244<br>246<br>248<br>249<br>249<br>249<br>251<br>251<br>251<br>253<br>253<br>255<br>256<br>256<br>256<br>256<br>256<br>256<br>257<br>259<br>259<br>259<br>261 |

| Configuring a Methodology<br>Creating a Methodology<br>Modifying a Methodology<br>Creating and Modifying a Sub-methodology<br>Creating a Sub-Methodology<br>Modifying a Sub-Methodology<br>Creating Goals<br>Displaying the New Goals Dialog<br>Specifying Details in the New Goal Dialog<br>Importing Goals<br>Deleting Goals<br>Modifying Goals<br>Modifying Goals<br>Modifying Goal Properties<br>Enabling/Disabling a Goal<br>Updating Rules of a Goal | <b>244</b> 246 248 249 249 249 251 251 253 253 255 256 256 256 256 256 256 257 259 261 263                                                                    |

| Customizing Goals                                                                                                                                                                                                                         |                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

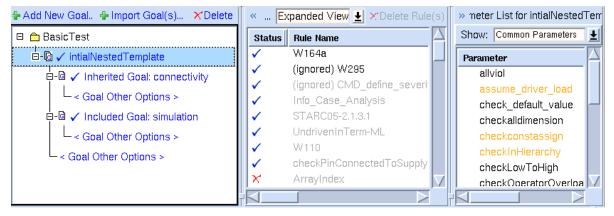

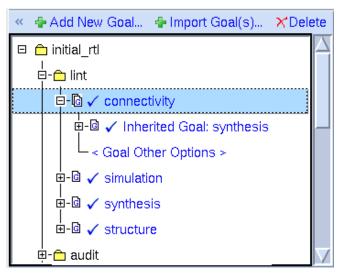

| Including and Inheriting GuideWare Goals                                                                                                                                                                                                  |                                               |

| Including/Inheriting Goals in a Goal File                                                                                                                                                                                                 |                                               |

| Including/Inheriting Goals in the MCS Window                                                                                                                                                                                              |                                               |

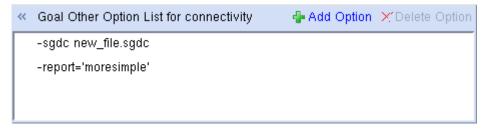

| Viewing and Adding Options for an Included or Inherited Goal                                                                                                                                                                              |                                               |

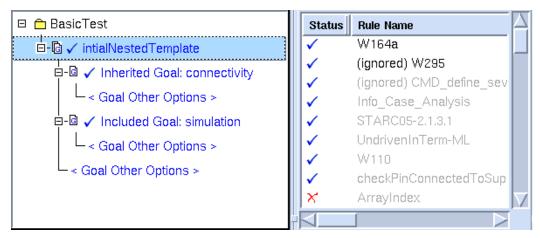

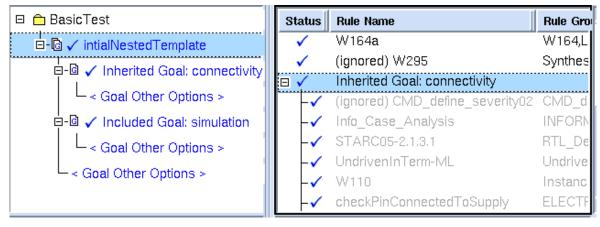

| Viewing Rules and Parameters of Included/Inherited Goals                                                                                                                                                                                  |                                               |

| Enabling/Disabling Rules of a Parent Goal                                                                                                                                                                                                 | 280                                           |

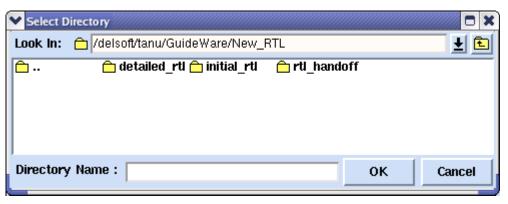

| Selecting a Custom Methodology                                                                                                                                                                                                            | 281                                           |

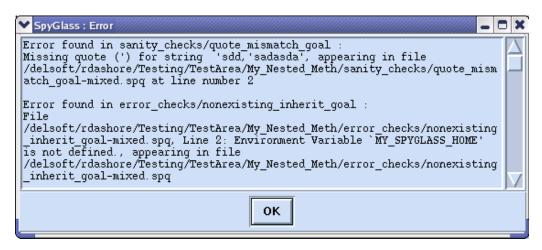

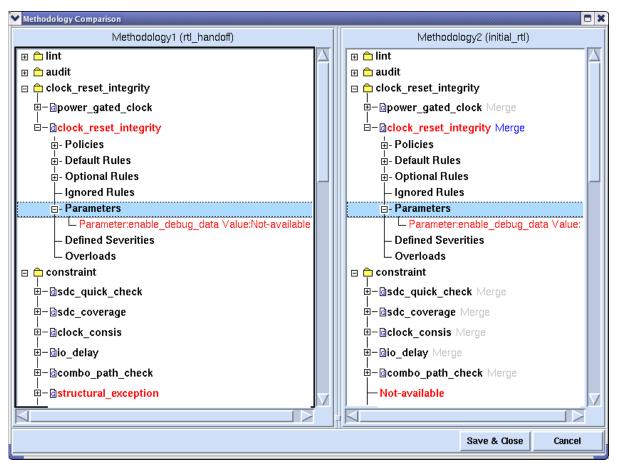

| Comparing Methodologies                                                                                                                                                                                                                   | 284                                           |

| Merging the Differences                                                                                                                                                                                                                   | 286                                           |

| Copying and Inheriting Methodologies                                                                                                                                                                                                      | 287                                           |

| Copying a Methodology                                                                                                                                                                                                                     | 287                                           |

| Inheriting a Methodology                                                                                                                                                                                                                  | 288                                           |

| Specifying a Reference Environment Variable                                                                                                                                                                                               | 289                                           |

| Specifying an Additional Path                                                                                                                                                                                                             | 289                                           |

| Migrating Custom Goals                                                                                                                                                                                                                    | 291                                           |

| Comparing Goals                                                                                                                                                                                                                           |                                               |

| Viewing the HTML Report for Comparison                                                                                                                                                                                                    |                                               |

| Migrating Goals                                                                                                                                                                                                                           |                                               |

| Order File                                                                                                                                                                                                                                |                                               |

| Viewing Order of Goals Defined in an Order File                                                                                                                                                                                           |                                               |

| Format of an Order File                                                                                                                                                                                                                   |                                               |

| Map File                                                                                                                                                                                                                                  | 302                                           |

|                                                                                                                                                                                                                                           |                                               |

| Working with SpyGlass Design Constraints                                                                                                                                                                                                  | 303                                           |

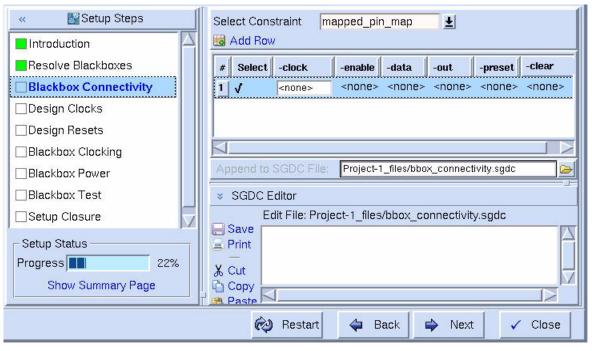

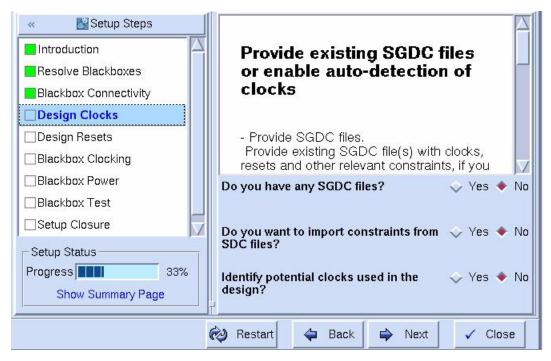

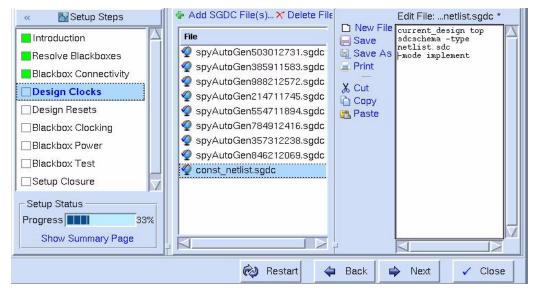

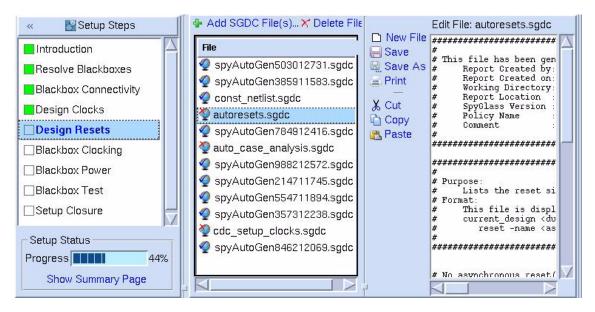

| Overview                                                                                                                                                                                                                                  |                                               |

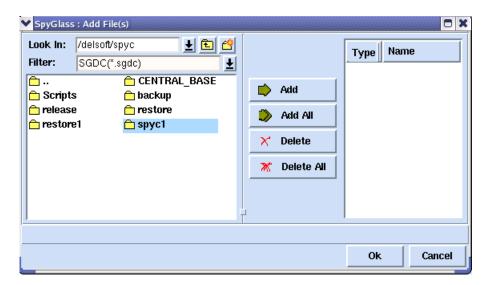

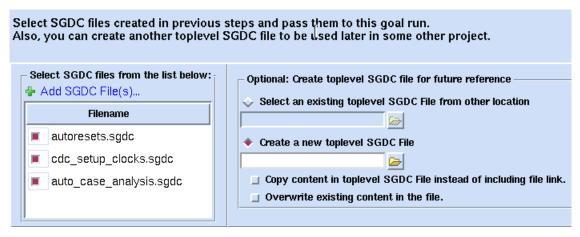

| Specifying SGDC Files to SpyGlass                                                                                                                                                                                                         |                                               |

|                                                                                                                                                                                                                                           |                                               |

| Creating an SGDC File                                                                                                                                                                                                                     |                                               |

| Adding Comments in an SGDC File<br>SGDC Convention for Packed Arrays                                                                                                                                                                      |                                               |

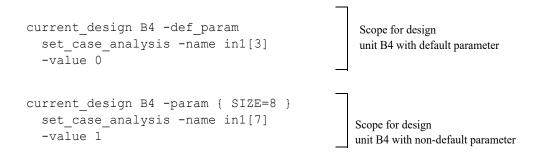

| Specifying Multiple current_design Specifications for a Design Unit                                                                                                                                                                       |                                               |

|                                                                                                                                                                                                                                           |                                               |