# **Atrenta Console Reference Guide**

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

©2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### **Disclaimer**

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **Trademarks**

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html.

All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

## **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to <a href="mailto:spyglass\_support@synopsys.com">spyglass\_support@synopsys.com</a>.

# **Contents**

| Preface                                            | 19 |

|----------------------------------------------------|----|

| About This Book                                    |    |

| Contents of This Book                              | _  |

| Typographical Conventions                          |    |

| SnyClass Consonts                                  | 22 |

| SpyGlass Concepts                                  |    |

| SpyGlass Features                                  |    |

| SpyGlass Operations                                |    |

| How SpyGlass Analyzes Your Design                  |    |

| SpyGlass Built-in Checking                         |    |

| Processing the HDL Designs                         | 29 |

| SpyGlass Rule Environment                          |    |

| Understanding SpyGlass Rule Definitions            |    |

| Rule Types and Order of Execution                  |    |

| SpyGlass Standard Products                         |    |

| Customizing SpyGlass Rules                         |    |

| Processing Messages and Displaying Reports         |    |

| About Rule Severity                                |    |

| Predefined Rule Severity-Classes                   |    |

| SpyGlass Results Summary                           |    |

| SpyGlass Exit Status                               |    |

| Messages Printed When SpyGlass Run is Complete     |    |

| Messages Printed When SpyGlass Run is not Complete |    |

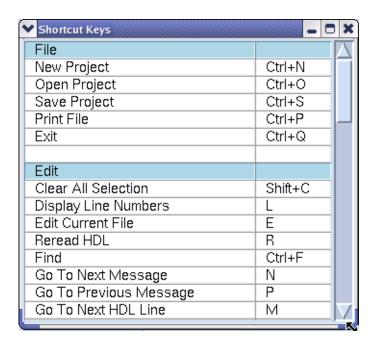

| The Menu Bar in Atrenta Console                    | 51 |

| Overview                                           | 51 |

| The Menu Bar                                       |    |

| File Menu                                          |    |

| Edit Menu                                          |    |

| View Menu                                          |    |

| Run Menu                                           | 63 |

|    | Tools Menu                                         | 64  |

|----|----------------------------------------------------|-----|

|    | Help Menu                                          | 98  |

|    | The Methodology Configuration System Menu Bar      | 103 |

|    | File Menu                                          |     |

|    | Edit Menu                                          |     |

|    | Tools menu                                         | 108 |

|    | Help Menu                                          | 116 |

| Wi | indows and Panes in Atrenta Console                | 119 |

|    | Overview                                           | 119 |

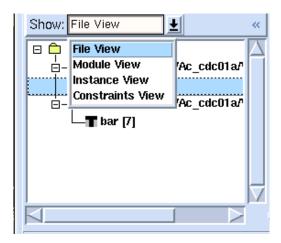

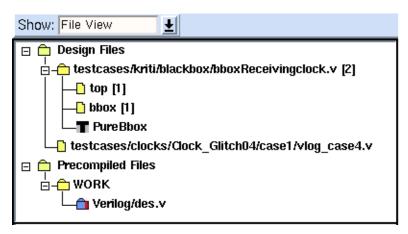

|    | The File/Module/Instance/Constraints Pane          |     |

|    | File View Page                                     |     |

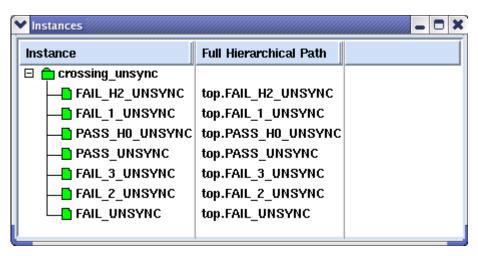

|    | Instance View Page                                 |     |

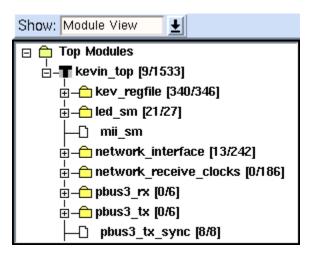

|    | Module View Page                                   |     |

|    | Constraints View Page                              |     |

|    | HDL Viewer Pane                                    | 141 |

|    | Color-Coding Scheme in HDL Viewer                  |     |

|    | Searching in HDL Viewer                            | 142 |

|    | Inactive Code Display                              |     |

|    | Interaction with Other Windows                     |     |

|    | Right-Click Options in the HDL Viewer Pane         |     |

|    | Navigation Bar                                     | 149 |

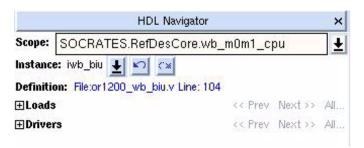

|    | HDL Navigator Pane                                 |     |

|    | Information for Signals                            |     |

|    | Information for Instances                          |     |

|    | Information for Macros                             |     |

|    | Viewing Declarations of Signals as Loads/Drivers   |     |

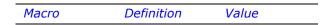

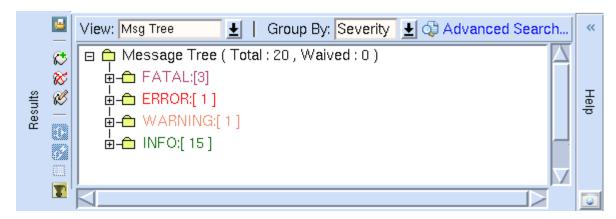

|    | Results Pane                                       |     |

|    | Message Help Section                               |     |

|    | Message Grouping                                   |     |

|    | Message Display Formats                            |     |

|    | Right-Click Options of the Results Pane            |     |

|    | Interaction with Other Windows                     |     |

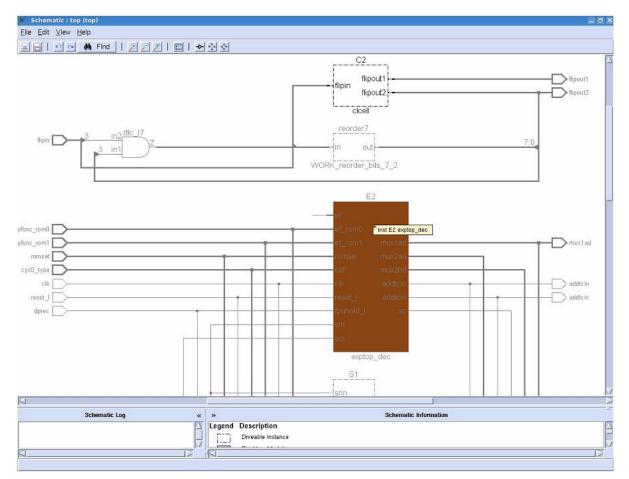

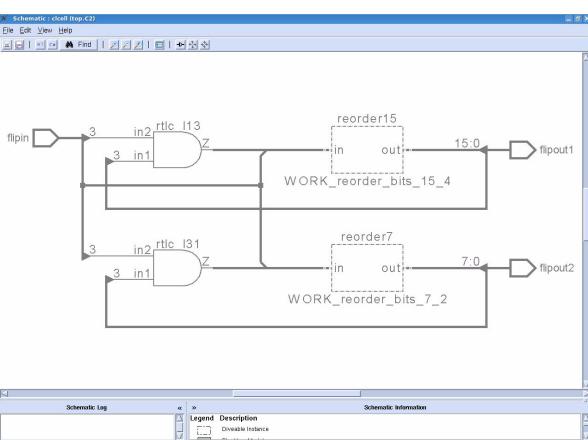

|    | The Modular Schematic Window                       |     |

|    | Using the Back Annotation Support                  |     |

|    | Creating RTL Groups Interaction with Other Windows |     |

|    | Using the Cursor                                   |     |

|    | Modular Schematic Window Menu Bar                  |     |

|    |                                                    |     |

|     | The Incremental Schematic Window                                  | 230 |

|-----|-------------------------------------------------------------------|-----|

|     | Interaction with Other Windows                                    | 231 |

|     | Creating IS Probes                                                |     |

|     | Using the Cursor                                                  |     |

|     | Highlighting Path Between Two Reference Points                    |     |

|     | Incremental Schematic Window Menu Bar                             |     |

|     | The Session Log Window                                            |     |

|     | Waveform Viewer Window                                            |     |

|     | Cross-Probing in Waveform Viewer                                  |     |

|     | Right-Click Menu Options of the Waveform Viewer Window            |     |

|     | Legend Window                                                     |     |

|     | Probing Modes                                                     |     |

|     | Probe or Message Details                                          |     |

|     | Viewing Sinks and Sources                                         |     |

|     | Spreadsheet Viewer Window                                         |     |

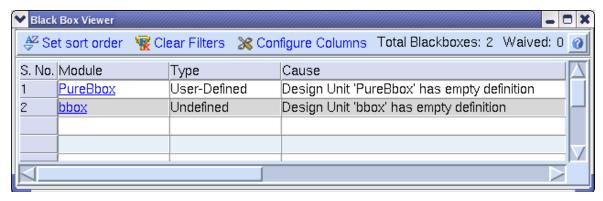

|     | Black Box Viewer Window                                           |     |

|     | Toolbar Options in the Black Box Viewer Window                    |     |

|     | Right-Click Menu Options in the Black Box Viewer Window           |     |

|     | Waiver Editor Window                                              |     |

|     | Details of the Waiver Editor Window                               |     |

|     | Right-Click Menu Options in the Waiver Window                     |     |

|     | Search Capability  Waiver Settings Affecting the Msg Tree Results |     |

|     |                                                                   |     |

|     | Hierarchy Traversal across Atrenta Console Windows                | 291 |

|     | a Configuration File in Atronta Concela                           | 202 |

| ıne | e Configuration File in Atrenta Console                           |     |

|     | Overview                                                          |     |

|     | Structure of SpyGlass Configuration File                          |     |

|     | General Configuration Settings                                    | 297 |

|     | Product and Rules Configuration Settings                          |     |

|     | Configuration Settings for VHDL Designs                           |     |

|     | Configuration Settings for Verilog Designs                        |     |

|     | Other Configuration Settings                                      | 30/ |

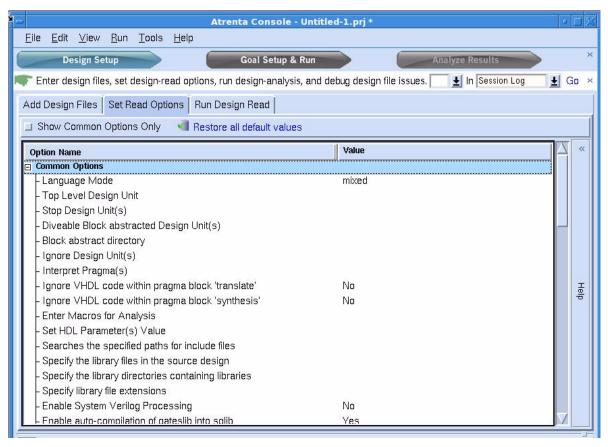

| Des | sign-Read Options in Atrenta Console                              | 315 |

|     | Overview                                                          |     |

|     | Common Design-Read Options                                        |     |

|     | Language Mode                                                     |     |

|     |                                                                   |     |

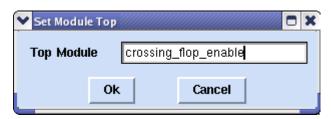

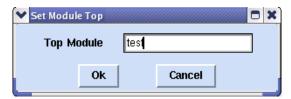

|    | Top Level Design Unit                                 | 318   |

|----|-------------------------------------------------------|-------|

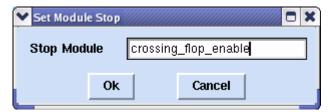

|    | Stop Design Unit(s)                                   |       |

|    | Making Project File Read Only                         | .321  |

|    | Diveable Block Abstracted Design Unit(s)              | 322   |

|    | Block Abstract Directory                              | 325   |

|    | Ignore Design Unit(s)                                 | 325   |

|    | Interpret Pragma(s)                                   |       |

|    | Ignore VHDL code within pragma block 'translate'      |       |

|    | Ignore VHDL code within pragma block 'synthesis'      |       |

|    | Enter Macros for Analysis                             |       |

|    | Set HDL Parameter(s) Value                            |       |

|    | Searches the specified paths for include files        |       |

|    | Specify the library files in the source design        |       |

|    | Specify the library directories containing libraries  |       |

|    | Specify library file extensions                       |       |

|    | Enable SystemVerilog Processing                       |       |

|    | Enable auto-compilation of gateslib into sglib        |       |

|    | Allow Duplicate Module Names in Verilog Designs       |       |

|    | Disable Verilog 2k Processing                         |       |

|    | Run in VHDL87 Compatibility Mode                      |       |

|    | Automatically Sort VHDL File(s)                       |       |

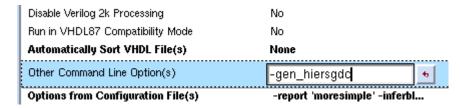

|    | Other Command Line Option(s)                          |       |

|    | Options from Configuration File(s)                    | 342   |

| Ad | vanced Design-Read Options                            | 343   |

|    | Define Verbosity Level for Log File                   | 343   |

|    | Enable Abstract Blocks Schematic                      | 343   |

|    | Enable Save Restore Flow                              | 344   |

|    | Enable Save Restore for BuiltIn Rules                 | 344   |

|    | Dump BuiltIn Rules in Precompile Flow                 | 344   |

|    | Ignore SpyGlass BuiltIn Rules                         |       |

|    | Directory Path Containing Ignore BuiltIn Files        | 345   |

|    | design-read Synthesis Flavor                          | 346   |

|    | Goal Run Synthesis Flavor                             |       |

|    | Enable Incremental Mode for All Goals                 | 349   |

|    | Logical Working Directory                             | 349   |

|    | Stop Directory(s)                                     |       |

|    | Upper Threshold for Compiling Memories                |       |

|    | Enable Handle Memories                                |       |

|    | Enable HDL Encryption                                 |       |

|    | Disable Encrypted HDL Checks                          |       |

|    | Disable Entrypted HDL Checks                          | . ၁၁၁ |

|    | Enable Analysis of Instantiated DesignWare Components |       |

|       | Hierarchical SGDC Modes                                              |       |

|-------|----------------------------------------------------------------------|-------|

|       | Maximum Messages Per Rule                                            |       |

|       | Cache Directory                                                      |       |

|       | Exit on Detecting Blackboxes in the Design                           |       |

|       | Enable RTL Checking of Precompiled HDL Libraries                     | . 356 |

|       | Check IP                                                             | . 357 |

|       | Check DU                                                             | . 358 |

|       | Enable SDC-to-SGDC translation                                       | . 360 |

|       | Specify the mode of the SDC file to be translated to SGDC            | . 360 |

|       | Specify the file to save output of SDC-to-SGDC translation           | . 361 |

|       | Dump SDC Generated Clocks in SGDC                                    | . 361 |

|       | Define a Mode to Infer Domains from SDC                              |       |

|       | Changing the Default Hierarchy Separator of the SDC2SGDC Constraints | . 365 |

|       | Handling False Paths                                                 | . 366 |

|       | Handling Multi-cycle Paths                                           | . 366 |

|       | Handling Mutually Exclusive Clocks                                   | . 368 |

|       | Handling of Directional Clocks                                       | . 368 |

|       | Translating set_clock_sense command                                  | . 369 |

|       | Translating set_disable_timing command                               | . 369 |

|       | Translating set_mode command                                         | . 369 |

|       | Specify the manner in which virtual-to-real clock mapping to be done | . 370 |

|       | Specify parameter to give the list of suffix strings                 |       |

|       | Specify parameter to give the list of prefix strings                 |       |

|       | Enable the physical aware power estimation flow                      | . 371 |

|       | Path (physical_dbdir) where design database is saved                 | . 371 |

|       | Is the current design a netlist design                               |       |

|       | Reports Max Count Size                                               |       |

|       | Reports Name                                                         |       |

|       | Report File                                                          |       |

|       | Report Style                                                         | . 374 |

|       | Aggregated Report(s) Name                                            | . 375 |

|       | Specify Configuration File to be Used to Create the Report           | . 375 |

|       | Report Output Directory Path                                         | . 376 |

|       | Disable HTML Reports generation                                      | . 376 |

|       |                                                                      |       |

| Sneci | al Features in Atrenta Console                                       | 377   |

| -     | Memory Reduction Feature                                             |       |

|       | Impact of Using this Feature                                         |       |

|       | Limitations                                                          |       |

|       |                                                                      |       |

|       | Pattern Matching Across Features                                     | .380  |

| Wildcard Mode                                                      |     |

|--------------------------------------------------------------------|-----|

| Regular Expression Mode                                            |     |

| Normal Mode                                                        |     |

| Hierarchy Separator                                                |     |

| Design Save and Restore Feature                                    |     |

| Incremental Save and Restore                                       |     |

| Restoring From Multiple Databases                                  |     |

| Examples                                                           |     |

| Save Restore Sensitive Options                                     |     |

| Handling Built-in Messages during Save-Restore Flow                |     |

| SpyGlass DFT Solution Back Annotation Feature                      |     |

| Support for Verilog Configuration                                  | 397 |

| Record-Mapping to Flattened Bus                                    | 399 |

| Handling Complex VHDL Records                                      | 399 |

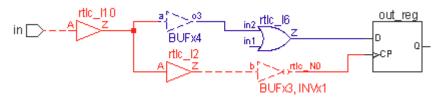

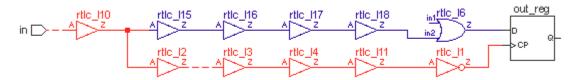

| Incremental Schematic Abstraction Feature                          | 403 |

| Combinational Logic Abstraction                                    |     |

| Buffer Chains Abstraction                                          |     |

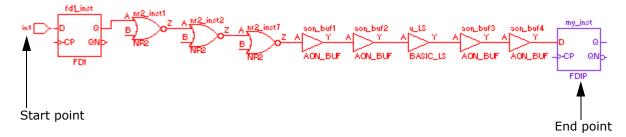

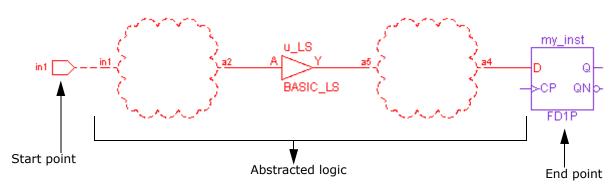

| Abstraction between Start and End Points                           |     |

| Viewing Logic within an Abstract Group                             |     |

| Viewing or Hiding Pins of an Abstracted Group                      |     |

| Removing All Abstract Groups                                       | 409 |

| The Batch Mode in Atrenta Console                                  | 411 |

| Overview                                                           | 411 |

| Atrenta Console-Specific Options                                   |     |

| Console Batch, Goal, and Source File List Command-Line Options     |     |

| Specifying Source Files through Command-Line                       |     |

| Specifying Rule Parameters through Command-Line                    |     |

| Classic Batch Command-Line Options and their Corresponding Project |     |

| Commands                                                           |     |

| Other Command-Line Options                                         |     |

| Command-Line Utilities                                             |     |

| The spyexplain Utility                                             | 449 |

| The spydocviewer utility                                           |     |

| The spyhelpviewer utility                                          | 454 |

| Reports Generated in Atrenta Console                               | 457 |

| Overview                                                           |     |

| • · · · · · · · · · · · · · · · · · · ·                            | 757 |

| Generating Reports                                 |     |

|----------------------------------------------------|-----|

| General Reports                                    | 459 |

| count report                                       |     |

| inline report                                      |     |

| moresimple_filesort report                         |     |

| moresimple_rulesort report                         |     |

| moresimple_sevclass report                         |     |

| score report                                       |     |

| sign_off report                                    |     |

| sign_off_sevlabel report                           |     |

| simple report                                      |     |

| summary report                                     |     |

| summary_sevlabel report                            |     |

| Default Reports                                    |     |

| ignore_summary report                              |     |

| moresimple report                                  |     |

| moresimple_warning report                          |     |

| moresimple_error report                            |     |

| no_msg_reporting_rules report                      |     |

| spyglass_violations report                         |     |

| stop_summary reportelab summary report             |     |

| waiver report                                      |     |

| •                                                  |     |

| Custom Reports  The count sevsort Report           |     |

| The moresimple csv Report                          |     |

| The score detail Report                            |     |

| Block Dependency Report                            |     |

| Directory Structure of Generated Reports           |     |

| Directory Structure of Generated Reports           |     |

| Directory Structure Generated After a Goal Run     |     |

| Directory Structure Generated After a Scenario Run | 470 |

| Grouping in Standard SpyGlass Reports              |     |

| Grouping in Standard Spydiass Reports              |     |

| Grouping in GUI Reports                            |     |

| , ,                                                |     |

| Sorting Messages in SpyGlass Reports               |     |

| User-Defined Message Sorting in SpyGlass Reports   | 483 |

| Appendix                                             | 487                    |

|------------------------------------------------------|------------------------|

| Supported Options of the set_option and/or set_487   | _goal_option Commands. |

| Deprecated Command Names and Their Correspondent 529 | onding New Commands    |

| <b>Project File Commands in Atrenta Console</b>      | 531                    |

| Overview                                             | 531                    |

| Project File Commands                                | 532                    |

| 87                                                   |                        |

| abstract_file_name_style                             |                        |

| abstract_searchpath                                  |                        |

| active_design                                        |                        |

| addrules                                             |                        |

| allow_celldefine_as_top                              | 534                    |

| allow_fatal_downgrade                                |                        |

| allow_incr_save_restore                              | 535                    |

| allow_module_override                                | 535                    |

| allow_non_Irm                                        | 535                    |

| allow_pre_packaged_goals                             | 538                    |

| allow_recursion_limit                                | 538                    |

| aggregate_report                                     | 538                    |

| aggregate_report_config_file                         | 538                    |

| aggregate_reportdir                                  | 539                    |

| auto_restore                                         | 540                    |

| auto_save                                            | 540                    |

| block_abstract                                       |                        |

| block_abstract_directory                             | 540                    |

| cachedir                                             | 541                    |

| cell_library                                         |                        |

| check_celldefine                                     | 541                    |

| checkip                                              |                        |

| checkdu                                              |                        |

| checkTopDu                                           |                        |

| configfile                                           |                        |

| consolidate_reportdir                                |                        |

| convert_udp_to_latch                                 |                        |

| debug_comments                                       |                        |

| decompile block constraints                          | 544                    |

| default_waiver_file                   |     |

|---------------------------------------|-----|

| define                                | 544 |

| define_cell_sim_depth                 | 545 |

| define_incr_dirmap                    | 546 |

| define_regression                     | 546 |

| define_severity                       | 548 |

| designread_disable_flatten            | 548 |

| designread_enable_synthesis           | 549 |

| designread_synthesis_mode             | 549 |

| disable_auto_migrate_waiver           |     |

| disable_encrypted_hdl_checks          |     |

| disable_hdllibdu_lexical_checks       |     |

| disable_hdlin_synthesis_off_skip_text | 550 |

| disable_hdlin_translate_off_skip_text |     |

| disable_html_report                   |     |

| disable_report                        | 551 |

| disable_infer_async_rst_latch         | 552 |

| disable_sgdc_dump                     | 552 |

| disable_Vlog2005_lrm_naming           | 553 |

| disallow_view_delete                  |     |

| dnc_param                             |     |

| dump_all_modes                        | 554 |

| dump_report_dir                       |     |

| dump_inactive_rules                   | 554 |

| dw                                    | 555 |

| dw_options                            |     |

| elab_precompile                       | 555 |

| enable_amg                            |     |

| enable_abstract_blocks_schematic      |     |

| enable_const_prop_thru_seq            | 556 |

| enable_fpga                           |     |

| enable_non_sgdc_naming                |     |

| enable_gateslib_autocompile           |     |

| enable_hbo                            |     |

| enable_hdl_encryption                 |     |

| enable_inactive_rtl_checks            |     |

| enablePackaging                       |     |

| enable_pass_exit_codes                |     |

| enable_pgnetlist                      |     |

| enable_module_based_reporting         | 560 |

| enable power platform flow            | 561 |

| enable_precompile_vlog               |     |

|--------------------------------------|-----|

| enable_physical_aware_pe             |     |

| enable_rule_category_in_moresimple   |     |

| enable_rule_mnemonic                 | 562 |

| enable_save_restore                  | 562 |

| enable_save_restore_builtin          | 562 |

| enable_sgdc_debug                    |     |

| enable_unused_param_reporting_in_spq |     |

| enable_sglib_debug                   |     |

| enable_vlog_config                   |     |

| enableSV                             |     |

| enable SVA                           |     |

| enableSV09                           |     |

| filter_block_violation               | 566 |

| force_gateslib_autocompile           |     |

| gen_block_options                    |     |

| gen_block_expand_lib_sources         |     |

| gen_blk_sgdc                         |     |

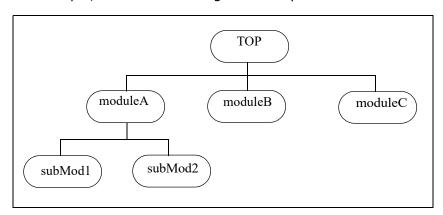

| gen_hiersgdc                         |     |

| generate_run_stat                    |     |

| generate_violations_report           |     |

| generate_rules_report                |     |

| gensys_compatible_dump               |     |

| handlememory                         |     |

| hdlin_synthesis_off_skip_text        |     |

| hdlin_translate_off_skip_text        |     |

| hdllibdu                             |     |

| higher_capacity                      |     |

| hw_variant_name                      |     |

| include_block_interface              |     |

| include_opt_data                     |     |

| ignore_builtin_rule                  |     |

| ignore_case_analysis                 |     |

| ignoredir <dir-name></dir-name>      |     |

| ignoredu                             |     |

| ignore_builtin_spqdir                |     |

| ignorefile                           |     |

| ignorelibs                           |     |

| ignore_reference_project_sgdc        |     |

| ignorerules                          |     |

| ignorewaivers                        | 580 |

| ignore_undefined_rules      |     |

|-----------------------------|-----|

| incdir                      |     |

| inferblackbox               |     |

| inferblackbox_iterations    | 581 |

| infer_enabled_flop          | 581 |

| ipdbdir                     | 582 |

| ianguage_mode               | 582 |

| lib                         |     |

| libhdl_extmap               | 584 |

| libmap                      | 586 |

| libext                      |     |

| library_gen_clock_naming    |     |

| LICENSEDEBUG                |     |

| lvpr                        | 588 |

| macro_synthesis_off         |     |

| mapSuffixList               |     |

| mapPrefixList               |     |

| mapVirtualClkByName         | 590 |

| mthresh                     |     |

| net_osc_count_limit         | 590 |

| netlist                     |     |

| netlist_clock_polarity      |     |

| nobb                        | 592 |

| noelab                      |     |

| nodefparam                  |     |

| nopreserve                  |     |

| noreport                    |     |

| norules                     |     |

| nosavepolicy/nosavepolicies |     |

| overload                    |     |

| overloadpolicy              |     |

| overloadrules               |     |

| overload_rule_category      |     |

| ovl_verilog                 |     |

| ovl_vhdl                    |     |

| param                       | 604 |

| perflog                     |     |

| physical                    |     |

| physical_dbdir              |     |

| physical_lib_config_file    | 605 |

| nhysical target             | 606 |

| portparam                       | .606  |

|---------------------------------|-------|

| pragma                          |       |

| prefer_tech_lib                 | . 607 |

| preserve_mux                    |       |

| print_sortorder_only            |       |

| prohibit_waiver                 |       |

| projectcwdprojectcwd            |       |

| projectwdir                     |       |

| project_read_only               | .611  |

| elab_summary_include_localparam | .612  |

| honor_spq_parameter_with_turbo  |       |

| read_file                       |       |

| read_protected_envelope         |       |

| reference_design_projectfile    | .618  |

| reference_design_sgdc           |       |

| reference_design_sources        |       |

| relax_hdl_parsing               |       |

| remove_file                     |       |

| remove_work                     |       |

| report                          |       |

| report_adjustment_waiver        |       |

| reportfile                      |       |

| report_incr_messages            |       |

| report_inst_backref             |       |

| report_ip_waiver                |       |

| report_max_inst                 |       |

| report_max_size                 |       |

| report_per_policy               |       |

| report_style                    | .628  |

| report_unreachable_default_case |       |

| resetall                        |       |

| rules                           |       |

| sca_on_net                      | .630  |

| savepolicy/savepolicies         |       |

| sdc2sgdc                        |       |

| sdc2sgdcfile                    |       |

| sdc2sgdc_mode                   |       |

| sfcu                            |       |

| sgdc_check_severity             |       |

| sgdc_validate                   |       |

| sasyn clock gating              | . 636 |

|   | sgsyn_clock_gating_threshold       |       |

|---|------------------------------------|-------|

|   | sgsyn_enable_latch_removal         | 637   |

|   | sgsyn_loop_limit                   | 637   |

|   | show_all_sdc_violations            | 638   |

|   | show_lib                           | 638   |

|   | show_sdc_progress                  |       |

|   | skip rules for fast restore        |       |

|   | skip_sanity_on_blocks_nonhier_nets |       |

|   | sort                               |       |

|   | sortrule                           |       |

|   | stop                               |       |

|   | stopdir                            |       |

|   | stopfile                           |       |

|   | support_sdc_style_escaped_name     |       |

|   | target                             |       |

|   | top                                |       |

|   | treat_priority_pin_as_obs          |       |

|   | treat rtl macro as lib cell        |       |

|   | unify sdc2sqdc                     |       |

|   | use block interface                |       |

|   | use_du_sch_hier                    |       |

|   | use generate index style           |       |

|   | use_generate_separator             |       |

|   | use_goal_rule_sort                 |       |

|   | use_scan_flops                     |       |

|   | use hier sep slash                 |       |

|   | V                                  |       |

|   | validate_hiersgdc                  |       |

|   | verbosity                          |       |

|   | W                                  |       |

|   | waivers_translate_generate_name    |       |

|   | work                               |       |

|   | write sdc                          |       |

|   | write_vlog_config_report           |       |

|   | strict vlog config                 |       |

|   | y                                  |       |

|   | vlog2001_generate_name             |       |

|   | vlog2005_lrm_naming                |       |

| _ |                                    |       |

| • | tions Not Recommended              |       |

|   | Ţ                                  | n 5 / |

| xviii | s | ynopsys, Inc. |  |

|-------|---|---------------|--|

|       |   |               |  |

# **Preface**

# **About This Book**

The Atrenta® Console Reference Guide describes various features, menus, and windows. In addition, this guide describes the configuration file that can be used to change the configuration settings of Atrenta Console.

# **Contents of This Book**

The Atrenta Console Reference Guide has the following sections:

| Section                                   | Description                                     |

|-------------------------------------------|-------------------------------------------------|

| SpyGlass Concepts                         | About various SpyGlass® concepts                |

| The Menu Bar in Atrenta Console           | About various menu options in GUI               |

| Windows and Panes in Atrenta Console      | About various windows and panes                 |

| The Configuration File in Atrenta Console | About SpyGlass configuration file               |

| Design-Read Options in Atrenta Console    | About various design read and run options       |

| Project File Commands in Atrenta Console  | About project file commands                     |

| The Batch Mode in Atrenta Console         | About various command-line options              |

| Reports Generated in Atrenta Console      | About various reports                           |

| Special Features in Atrenta Console       | About various SpyGlass features                 |

| Appendix                                  | About various Atrenta Console-specific commands |

|                                           |                                                 |

# **Typographical Conventions**

This document uses the following typographical conventions:

| To indicate                           | Convention Used                                                   |

|---------------------------------------|-------------------------------------------------------------------|

| Program code                          | OUT <= IN;                                                        |

| Object names                          | OUT                                                               |

| Variables representing objects names  | <sig-name></sig-name>                                             |

| Message                               | Active low signal name ' <sig-name>' must end with _X.</sig-name> |

| Message location                      | OUT <= IN;                                                        |

| Reworked example with message removed | OUT_X <= IN;                                                      |

| Important Information                 | NOTE: This rule                                                   |

The following table describes the syntax used in this document:

| Syntax                | Description                                           |

|-----------------------|-------------------------------------------------------|

| [ ] (Square brackets) | An optional entry                                     |

| { } (Curly braces)    | An entry that can be specified once or multiple times |

| (Vertical bar)        | A list of choices out of which you can choose one     |

| (Horizontal ellipsis) | Other options that you can specify                    |

Typographical Conventions

# **SpyGlass Concepts**

# **SpyGlass Features**

SpyGlass® provides the following features:

- Full language support for Verilog (IEEE 1364, Verilog 2001, and SystemVerilog) and VHDL, that is VHDL (IEEE Std 1987) and VHDL (IEEE Std 1993).

- A rich suite of in-built rules, including:

- ☐ File checks, such as file names, design units per file and headers

- □ Naming checks on signals, ports, parameters, constants, clocks and other constructs

- ☐ Style and related checks

- ☐ Coding for synthesis and related checks

- lacktriangle Design practice and related checks

- ☐ Area, timing, and synchronization checks

- ☐ Clock and reset checks

- ☐ SpyGlass DFT solution, SpyGlass Power Verify solution, SpyGlass Constraints solution, SpyGlass ERC solution, and similar checks (cost options)

- ☐ Support for several industry standard HDL analysis and assessment programs, including OpenMORE<sup>TM</sup> and STARC<sup>TM</sup>

- A variety of report format options so you can set up your own reports

- Built-in engines, including RTL synthesis and flattening, to enable detailed implementation tests including clocking, reset and synchronization of asynchronous signals

- A Graphical User Interface (GUI) called Atrenta Console

- A batch execution program for integration in corporate design flows

Additional features enable you to customize SpyGlass to meet your company's unique requirements. Refer to the *SpyGlass Policy Customization Guide* for more details. Customization features include:

- A Perl interface that provides extensive programmability, and customization of error messages, error severity, and other parameters

- User-created rules built as dynamically linked C libraries

- User-programmable reporting that enables you to generate message reports as screen displays, hard copies, files, e-mail, Web pages, and other formats

SpyGlass top-level is a full Perl interpreter that allows extensive integration, enabling you to take advantage of the open-source libraries for Web programming, GUI management, and many other capabilities.

# **SpyGlass Operations**

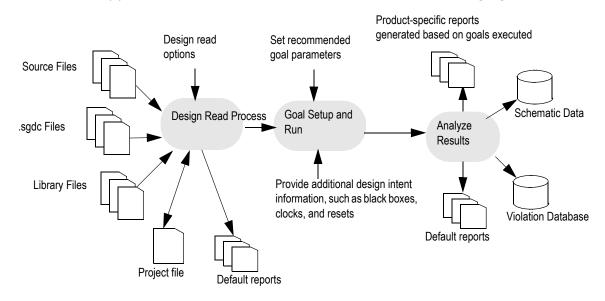

SpyGlass functional model is summarized in the following figure:

FIGURE 1. SpyGlass Functional Model

# How SpyGlass Analyzes Your Design

SpyGlass analyzes your design in various steps, depending upon the goals executed. SpyGlass invokes the analysis tools that meet your request, in order to give you the fastest runtime.

Following are the phases of SpyGlass analysis:

SpyGlass interprets precompiler directives.

SpyGlass first reads and interprets all precompiler directives and translate on/translate off pragmas.

**NOTE:** Pragmas are runtime commands embedded as comments in your source code, and used with specific electronic design automation tools.

2. SpyGlass checks style/linting rules.

SpyGlass performs checks for standard style and linting rules. It then logs rule messages and location of each message in the violation database for processing by the report generator. For each unit in the design, SpyGlass first checks for HDL syntax and structural errors and then reports violation of different levels of severity (see section below on SpyGlass error messages).

3. SpyGlass checks inference rules.

If SpyGlass detects no syntax messages in step 2, it transparently invokes its RTL synthesis engine. This creates an internal gate-level, hierarchical design built around generic gates that allows SpyGlass to detect inferred logic, such as latches, flip-flops, and counters. The gate-level logic naming is controlled within SpyGlass so any messages found in inferred logic can easily be mapped back to the RTL code that caused it, which simplifies debugging.

4. SpyGlass checks connectivity rules.

Once SpyGlass has checked the inferred logic, SpyGlass transparently flattens your design so it can check complex connectivity rules. These include issues such as correct synchronization logic at clock domain crossings, reset rules, combinational loop detection, and SpyGlass DFT solution and cone analysis. In effect, this phase can encompass any form of netlist checking. As in the synthesis phase, controlled naming maps any errors SpyGlass detects back to your source code.

5. SpyGlass uses additional analysis engines

Depending on the complexity of a given rule, SpyGlass will also make use of its internal cycle simulator and/or testability analyzer. This enables advanced connectivity and behavior checking.

SpyGlass identifies and removes duplicate rules in case of multiple selected goals.

If you select multiple goals, the same rule might be present in such goals. In such cases, SpyGlass removes duplicate rules and then runs the rules.

# SpyGlass Built-in Checking

While analyzing or synthesizing RTL designs, SpyGlass performs checks on the HDL syntax and structure. These checks are always performed automatically, independently of which SpyGlass rules are requested to be checked.

If any syntax or structure issues are found, SpyGlass generates the corresponding standard error or warning messages (known as *built-in messages*). These built-in messages are different from the rule messages generated during rule-checking.

There are the following classes of such built-in messages:

| TABLE 1 | Built-in | Messages | Classes |

|---------|----------|----------|---------|

|---------|----------|----------|---------|

| Message Type                               | Message Prefix |

|--------------------------------------------|----------------|

| Syntax errors                              | STX_           |

| Language Warnings                          | WRN_           |

| Synthesis warnings                         | SYNTH_         |

| Synthesis errors                           | SYNTH_         |

| Post-elaboration syntax errors (VHDL only) | ELAB_          |

Syntax Errors and Language Warning messages are language-specific, that is, there are separate message sets for Verilog, VHDL, and Mixed-Language respectively. Synthesis warnings and errors are language-neutral for the most part. See the *SpyGlass Built-In Messages Reference* for details of these message sets.

The ELAB\_ messages may appear when a VHDL design is being processed after elaboration. These messages relate to syntax issues and have the same number and content as the syntax messages except they have the ELAB\_ prefix.

**NOTE:** Some of the rules in SpyGlass products are mapped to the SpyGlass built-in messages. Thus, when you run SpyGlass with rule-checking, some of the standard warning and error messages are suppressed and equivalent rule messages are generated in their place.

**NOTE:** If SpyGlass detects an internal software error, it reports the error as a WARNING message. These errors are normally associated with a specific implementation of a

rule. Any such error messages should be reported to Atrenta Customer Support.

# **Processing the HDL Designs**

When you run SpyGlass on a design, the following process is followed:

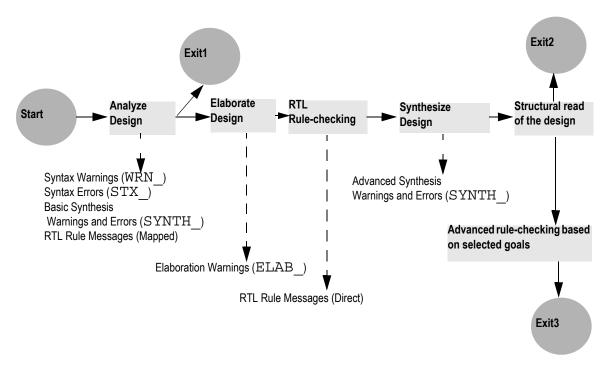

FIGURE 2. SpyGlass Run Process

SpyGlass processing occurs in the following steps:

- 1. SpyGlass analyzes the design and generates the following types of standard built-in messages:

- ☐ Syntax warning messages (WRN\_ messages)

- ☐ Syntax error messages (STX\_ messages)

- ☐ Basic synthesis error and warning messages (SYNTH messages)

SpyGlass also generates rule messages (instead of built-in messages mapped to the rules in the selected products)

- 2. If the design has syntax errors (STX\_ messages) after initial processing, SpyGlass exits (shown as **Exit1**).

- 3. If the design does not have any syntax errors, SpyGlass may perform elaboration of the RTL design and generate elaboration time errors or warnings (ELAB messages)

- 4. SpyGlass performs RTL rule-checking and generates rule messages as applicable.

- 5. SpyGlass synthesizes the design and generates the advanced synthesis error and warning messages (SYNTH messages).

- 6. SpyGlass performs structural read of the design and then SpyGlass exits (shown as **Exit2**) if no goals are selected.

- 7. If you have selected goals, SpyGlass runs the rules of the goals, and reports appropriate violation messages.

- 8. SpyGlass exists (shown as **Exit3**).

# **SpyGlass Rule Environment**

## **Understanding SpyGlass Rule Definitions**

Each SpyGlass product whether standard or custom, is a PERL source file that has the rule definition, the rule group definitions, and PERL subroutines, if any.

Each rule has a number of attributes that decide how the rule will function. Some of the important attributes are as follows:

- Rule name, which you use to specify that the particular rule should be run

- Language applicable for a rule. This attribute enables you to know if the rule works on Verilog, VHDL, or mixed-language designs.

- Severity of the rule, which indicates how important it is to fix your source code

- *Message* displayed if your source code violates the rule

- Rule primitive that is called for the rule

#### **Rule Primitives**

Rule primitives are C functions that are present either in SpyGlass core or in a shared library. They perform the real work of checking rules against your design and can be parameterized to produce different checks. The primitive called for each rule is specified in the product. However, in normal use, the rule primitives and the rule attributes are transparent to the user. The rule primitive extracts object data from the design database, runs checks as defined by the parameters, and generates a message as defined in the rule, if an error is found.

# **Rule Types and Order of Execution**

SpyGlass rules are categorized to work on a particular design view of your source file. There are rules that work on the source RTL description, rules that work on the synthesized hierarchical netlists, and rules that work on the flattened netlists. Consequently, the rules work in the same order in which the corresponding design becomes available.

The SpyGlass rule types by their order of execution are as follows:

1. SETUP type rules

The SETUP type rules are checked just before design analysis phase.

This category contains rules that are independent of HDL source code (Verilog or VHDL) or rules that are checked inside the analysis/synthesis engine.

The SETUP type rules are as follows:

| Rules that check for commands (including the product-specific rule |

|--------------------------------------------------------------------|

| parameters) and existence of different custom data requirements.   |

☐ Rules that check for liberty library files (.lib files)

■ Rules that check for SGDC files

☐ Enabling of analyzer built-in rules and synthesis built-in rules.

**NOTE:** The analyzer built-in rules and synthesis built-in rules are only enabled by standard built-in rule-primitives. Actual checking and rule message generation occurs during actual analysis or synthesis.

#### 2. RTLALLDULIST type rules

The RTLALLDULIST type rules operate on all RTL design unit including those from precompiled libraries. For Verilog, a design unit is a module, UDP, or macro-module. For VHDL, a design unit is an entity, architecture, configuration, package, or package body.

An RTLALLDULIST type rule is checked once on each RTL/Library design unit in the design. These rules can access only the local design unit data. They cannot access hierarchy information.

#### 3. RTLDU type rules

The RTLDU type rules operate on a single RTL design unit. For Verilog, a design unit is a module, UDP, or macro-module. For VHDL, a design unit is an entity, architecture, configuration, package, or package body.

An RTLDU type rule is checked once on each design unit in the design. These rules can access only the local design unit data. They cannot access hierarchy information.

By default, the RTLDU type rules do not run on precompiled design units instantiated in a design. To enable rule checking on such design units, specify the following command in a project file:

set\_option *hdllibdu* yes

### 4. RTLDULIST type rules

The RTLDULIST type rules work on the complete RTL design (not including the precompiled library design unit), without elaboration.

An RTLDULIST type rule is checked once on the complete design. These rules can access only the local design unit data. They cannot access hierarchy information.

By default, the RTLDULIST type rules do not run on precompiled design units instantiated in a design. To enable rule checking on such design units, specify the following command in a project file:

set option *hdllibdu* yes

#### 5. ELABDU type rules

The ELABDU type rules work on the elaborated design units.

An ELABDU type rule is checked once on each design unit, elaborated with unique set of parameters/generics with which it has been instantiated. For example, if a module is instantiated 4 times with a parameter value of 5 and 2 times with a parameter value of 7, the module would be elaborated only twice, (instead of 4+2) once with 5 as the parameter value and once with 7 as the parameter value.

#### 6. RTLTOPDU type rules

The RTLTOPDU type rules are run on the top design unit, determined by SpyGlass after design elaboration.

### 7. LEXICAL type rules

The LEXICAL type rules check on each design file, one at a time. This category generally contains non-electronic and text-based rules, such as line-length, tabs, indentation, naming conventions, etc. By default, the LEXICAL type rules do not run on precompiled RTL files.

To enable rule checking on such design units, specify the following command in a project file:

set\_option hdllibdu yes

### 8. VSDU type rules

The VSDU type rules check upon a synthesized object model of a design unit.

A VSDU type rule is checked once on each synthesized design unit.

### 9. VSTOPDU type rules

The VSTOPDU type rules are run on the synthesized object model for each top module hierarchy.

Since the RTL view is not available, such rules' checking is limited to only the synthesized object model.

#### 10.BLOCKDU\_CD type rules

The BLOCKDU\_CD type rules run on user-specified design units flattened down to the specified flattened partitions (called *blocks*) and the blocks themselves.

In this case, design units are flattened only till block boundaries and each block in turn is flattened till boundaries of its sub-blocks, if any.

The BLOCKDU\_CD type rules run on each specified design unit and each block once.

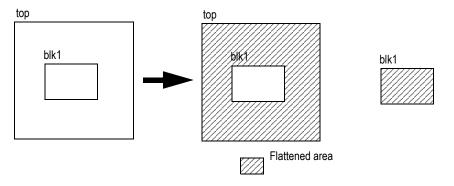

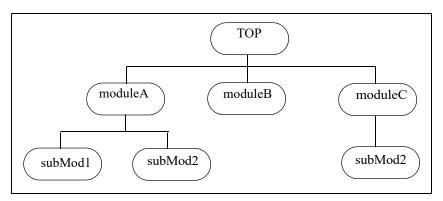

Consider the following example where the design unit top has a partition named blk1:

FIGURE 3. Processing with BLOCKDU\_CD type rules

In this case, each BLOCKDU\_CD type rule is run once on the design unit top flattened up to the block blk1 boundary and once on the flattened block blk1.

### 11. FLATBLOCKDU type rules

The FLATBLOCKDU type rules run on user-specified flattened design units and only the specified flattened partitions (or blocks) within these design units.

In this case, design units and blocks are completely flattened until leaf-level.

The FLATBLOCKDU type rules run on each user-specified flattened

design unit and each specified block under the design unit once.

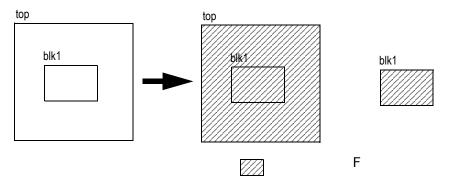

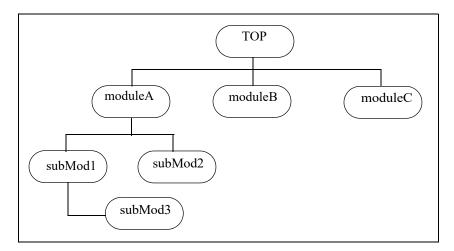

Consider the following example where the design unit top has a partition named blk1:

FIGURE 4. Processing with FLATBLOCKDU type rules

In this case, each FLATBLOCKDU type rule is run on the design unit top flattened down to leaf-level and on block blk1 flattened down to leaf-level.

### 12.FLATDU type rules

The FLATDU type rules run on the Flat Object Model for each top module in design.

### 13.FLATDU2\_WOL type rules

**NOTE:** The FLATDU2\_WOL type has been deprecated. Rules registered with this view are internally moved to the FLATDU2\_WL view.

### 14.FLATDU2\_WL type rules

The FLATDU2\_WL type rules are designed to work with SpyGlass Logic Evaluator.

In this view, .lib instances are not flattened. In addition, .lib functionality is not visible to these rules. Unlike the FLATBLOCKDU type rules, flattening of such rules is applied to the top-level design units only.

SpyGlass ERC solution has rules of this type, which just use electrical information of a cell but not cell functionality.

### 15.ALLVIEWS\_WL type rules

The ALLVIEWS\_WL type rule category is a special deprecated case. The rules of this category require all design views (RTL, Synthesized, and Flattened) in memory and are run after FLATDU2\_WL type of rules and before FLATDU type of rules. From flattening point of view, they are similar to FLATDU2\_WL type of rules.

#### 16.ALLVIEWS type rules

The ALLVIEWS type rule category is a special deprecated case. The rules of this category require all design views (RTL, Synthesized, and Flattened) in memory and are run only after rules of all other categories have been run.

# **SpyGlass Standard Products**

SpyGlass analyzes HDL source files using pre-defined rules contained in product files. A number of SpyGlass Standard products are installed with SpyGlass.

The SpyGlass Base products that are available with SpyGlass are:

- **SpyGlass lint solution**, which is based on the commonly accepted set of HDL rules for detecting syntax errors and common connectivity errors such as unused signals and undriven inputs.

- **SpyGlass OpenMore solution**, which is based on the OpenMORE standard developed by Synopsys and Mentor Graphics, and which sets forth certain coding styles and practices that enhance the reusability of HDL design modules.

- SpyGlass STARC/STARC02/STARC05 solution, which is based on IP Reuse guidelines compiled by Semiconductor Technology Academic Research Center (STARC).

- **SpyGlass area solution**, which includes rules used to identify HDL that may cause potential problems in silicon area downstream.

- **SpyGlass latch solution**, which includes rules related to latch based designs

- **SpyGlass miscellaneous solution**, which includes useful rules that cannot be classified in any other default products.

- **SpyGlass timing solution**, which includes rules to identify potential timing issues in the design.

■ **SpyGlass ERC solution**, which checks a design for correct electrical connectivity at the gate level.

In addition, there are Atrenta Advanced products available that can be purchased separately:

- **SpyGlass DFT Solution**, which checks a design for testability issues at the RT level.

- **SpyGlass Constraints Solution**, which checks the suitability of the Synopsys Design Constraints files

- **SpyGlass Power Verify Solution**, which checks the design for the structural, architectural, and system level issues in order to reduce power.

- **SpyGlass CDC Solution**, which include rules to check clocks, resets, and clock-domain-crossings in the design

- **SpyGlass Power Estimate Solution**, which include rules for power estimation and power reduction

- **SpyGlass TXV Solution**, which is used to verify correctness of timing exceptions and/or check if critical paths can be ignored or relaxed during timing sign-off.

# **Customizing SpyGlass Rules**

SpyGlass allows you to customize a number of its functions to meet your company's needs. For example:

- Add your own rules or modify the pre-defined rules making use of the pre-defined primitives.

- See the SpyGlass Policy Customization Guide for more details.

- Modify the SpyGlass defaults for rule severities, messages, allowed name syntax, or other parameters.

- See the SpyGlass Policy Customization Guide for more details.

- Create custom reports

# **Using Rule Mnemonics**

Rule mnemonics refer to the custom rule names assigned to the SpyGlass

rule. These custom rule names are more descriptive and convey additional details about a rule.

This section describes the following topics:

- Enabling the Support for Rule Mnemonics

- Converting the Rule Names

- Viewing the Rule Help

# **Enabling the Support for Rule Mnemonics**

By default, the support for rule mnemonics is disabled. To enable this feature, specify the *enable\_rule\_mnemonic* option in the project file, as shown below:

```

set option enable rule mnemonic <yes | no | 0 | 1>

```

When this option is enabled, SpyGlass uses the custom names specified in the rules\_mapping.csv file, throughout the SpyGlass run.

The mapping of the existing SpyGlass rules and the rule mnemonics is specified in the rules\_mapping.csv file, which is available at the following location:

```

SPYGLASS HOME/auxi/rules mapping.csv

```

**NOTE:** If the enable\_rule\_mnemonic option is enabled, you must only specify the rule mnemonic throughout the SpyGlass run. That is, you must use the rule mnemonics in all the input files, such as, project files, Tcl files, and so on. Otherwise, SpyGlass will not process the rule.

Following is the format for a rules\_mapping.csv file:

```

<existing_rule_name>, <descriptive_rule_name>, , product_name>,

"<comment>"

```

# **Converting the Rule Names**

To ease the process of replacing SpyGlass rule names with the corresponding rule mnemonics in the input files, you can use convert rule names.pl file, which is available at the following location:

```

SPYGLASS HOME/auxi/convert rule names.pl

```

This script uses the rules\_mapping.csv file to check the existing rule mapping and replaces the SpyGlass rule names with the rule mnemonics accordingly.

Specify the following command to run the convert\_rule\_names.pl script:

```

perl SPYGLASS_HOME/auxi/convert_rule_names.pl -i

<input_file> -o <output_file>

```

#### Where,

- <input\_file> refers to any input file in the SpyGlass run, such as,

.prj file.

- <output\_file> refers to the output file, containing the converted rule names.

For more information on the covert\_rule\_names.pl script, specify the following command:

```

perl SPYGLASS_HOME/auxi/convert_rule_names.pl --help

```

# Viewing the Rule Help

You can view the help of the SpyGlass rules and the corresponding rule mnemonics using the following ways:

- HTML Help: Enables you to search for a rule mnemonic and displays the help for the corresponding rule

- The spyexplain Utility: Enables you to view the short and long help for both the SpyGlass rules and rule mnemonics

# **Processing Messages and Displaying Reports**

Based on the selected goals, SpyGlass reports appropriate violation messages to indicate various design issues. These messages are written to in report files and SpyGlass log file.

# **About Rule Severity**

SpyGlass supports two levels of rule severities - severity label and severity class.

Each SpyGlass rule has a severity label and each severity label is classified under one of the predefined severity classes. Severity labels are product-specific and severity classes are predefined for SpyGlass.

After SpyGlass analysis run, a rule-checking summary is printed that reports total rule messages found under each rule severity-label and total rule messages found under each predefined rule severity-class that is, the sum of total rule messages found under each rule severity-label classified under that rule-severity class.

# **Predefined Rule Severity-Classes**

SpyGlass supports the following five rule severity-classes:

# **FATAL Rule Severity-Class**

The FATAL rule severity-class is primarily used for a stopper situation related to design rule-checking. Occurrence of a rule message of this class aborts further rule-checking by SpyGlass and requires immediate attention from the user so that rule-checking can be resumed.

Examples of messages of the FATAL rule severity-class are as follows:

1. Syntax Error in the input design source

Almost all syntax errors cause immediate termination of further rule-checking by SpyGlass since syntax error indicates inability to create a consistent design view that is required by later stages of rule-checking by SpyGlass. Hence, such messages are identified as FATAL class messages. However, certain simulation-related syntax errors may be

classified as non-FATAL messages because such errors do not affect the synthesis-oriented design view that is required by SpyGlass even when the constructs are syntactically incorrect as per LRM specifications.

2. Custom product assumptions about the design that are found to be invalidated at runtime

One example of such assumption is when a custom product requires that assign statements are not used in the Verilog design source. Then, there would be a rule in the product that will run first and flag all uses of assign statements. If this rule is violated, that is, if such statement are actually found in a design, further rule-checking cannot be performed because all subsequent rules do not take the Verilog assign statement functionality into account.

In a large majority of SpyGlass runs, FATAL rule severity-class messages are not expected. Occurrence of such messages indicates an interrupted run and would normally require re-run of SpyGlass after the reported problem has been fixed.

A rule of FATAL rule severity-class is always run completely. However, if a rule message is found for a rule of FATAL rule severity-class, no further rule-checking is performed.

# **ERROR Rule Severity-Class**

The ERROR rule severity-class is normally used to indicate a design error that would cause design functionality to be compromised. Normally, such messages indicate an immediate bug in the design from the perspective of design-integrity aspect being analyzed by the SpyGlass run. Presence of such ERROR rule severity-class messages require user to fix the design after suitable analysis. Applying waiver on an ERROR rule severity-class message may require detailed justification and approval in the SpyGlass use-model adopted by a typical user.

In contrast, other lower-precedence messages indicate only a potential error situation or non-compliance with design development guidelines that do not directly affect design functionality.

Normally a few of these ERROR rule severity-class messages would be expected on a typical in-development design. For a known good design, ERROR rule severity-class messages will be few and typically report only those design errors that are not verifiable by traditional simulation and

other verification procedures.

# **WARNING Rule Severity-Class**

The WARNING rule severity-class is the next less-severe message class after the ERROR rule severity-class. As described earlier, a key characteristic of such messages is that these messages indicate only a potential error situation or non-compliance with design development guidelines that do not directly affect design functionality.

Therefore, you can apply selective waivers on such messages with relatively more freedom (and confidence) than say, an ERROR rule severity-class message.

However, from SpyGlass perspective, such messages still carry a hint of caution. Therefore, you should not ignore such messages without proper analysis.

# **INFO Rule Severity-Class**

The INFO rule severity-class represents all SpyGlass rule-checking output that is of informative nature. Such output either may be general design statistics or may represent any kind of design query that a user/product may wish to perform.

Hence, while the count of FATAL, ERROR, or WARNING rule severity-class messages can be used as a measure of design quality, reporting of INFO rule severity-class output is not expected to be a measure of design quality. Instead, it will depend on the design size and amount of design statistics and guery data that a user is intending to extract.

# **DATA Rule Severity-Class**

The DATA rule severity-class represents SpyGlass output not belonging to any of other rule severity-classes. Such cases may be secondary data to debug any of preceding rule messages or may represent information that is not reported as part of usual SpyGlass message reports or GUI display.

Typically, you would not be aware of this output. Such output is intended for better diagnostics and usability support within SpyGlass environment. You should not assume anything about the existence or other details of this

data.

Rule messages of DATA severity class are not displayed in SpyGlass reports except in the Session Log Page of The Message Window, where the total reported messages are categorized according to the above-predefined rule severity classes (a category is shown in the Session Log Page only if any message is reported for that category).

# SpyGlass Results Summary

At the end of SpyGlass analysis run, a results summary is generated as shown in the following example:

```

_____

Results Summary:

_____

Goal Run : spyglass cmdline goal

(Rules from above goal(s) have been changed)

Command-line read : 0 error, 1 warning, 0 information message

Design Read : 0 error, 0 warning, 3 information messages

Found 2 top modules: cdc (file: ../../Ac cdc08/cdc.v)

ovl (file: ../../Ac cdc08/ovl.v)

** black box Resolution: 50 errors, 0 warning, 0 information message

SGDC Checks : 0 error, 3 warnings, 0 information message

Policy clock-reset : 1 error, 4 warnings, 0 information message

Total

: 51 errors, 8 warnings, 3 information messages

Total Number of Generated

: 63 (51 errors, 8 warnings, 4 Infos)

Messages

Number of Waived Messages : 1 (0 error, 0 warning, 1 Info)

Number of Reported Messages: 62 (51 errors, 8 warnings, 3 Infos)

NOTE: It is recommended to first fix/reconcile fatals/errors

reported on lines starting with ** as subsequent issues might be

related to it.

Please re-run SpyGlass once ** prefixed lines are fatal/error

clean.

SpyGlass Exit Code 0 (Rule-checking completed with errors)

```

The results summary contains the following information:

■ Count of FATAL, ERROR, WARNING, and INFO severity class messages.

The count of FATAL severity class message is displayed first in the results summary. This column is not printed if there are no FATAL severity-class messages.

If there is no message for any of the ERROR, WARNING, and INFO severity classes, the corresponding count set is reported as zero.

■ Count of total number generated messages, the waived messages, and the reported messages is displayed as in the following example:

```

Total Number of Generated Messages : 3 (2 errors, 0 warning, 1 Info)

Number of Reported Messages : 3 (2 errors, 0 warning, 1 Info)

Number of Waived Messages : 1 (0 errors, 1 warning, 0 Info)

```

If you have set a rule message-reporting limit by using the *lvpr* command and some messages are suppressed, the count of suppressed messages is reported. An example is shown below:

```

Number of Overlimit Messages: 25 (2 errors, 11 warnings, 12 Infos ...

```

■ SpyGlass exit status

For details, see *SpyGlass Exit Status*.

# **SpyGlass Exit Status**

For better integration with other stream tools, SpyGlass generates exit status code that gives you the exact status of SpyGlass run.

By default, SpyGlass reports an exit code of 0 for a successful run and prints one of the following messages:

- SpyGlass Exit Code 0 (Rule-checking completed without errors or warnings)

- SpyGlass Exit Code 0 (Rule-checking completed with warnings)

- SpyGlass Exit Code 0 (Rule-checking completed with errors)

- SpyGlass Exit Code 0 (Informational command executed, rule-checking not done)

You can set the <code>enable\_pass\_exit\_codes</code> command to yes in a project file to report different exit codes for each of the above cases depending on the type of message generated in the current run. For details, see <code>Messages Printed When SpyGlass Run is Complete</code>.

**NOTE:** Waived messages are not considered while deciding the exit status. Only reported messages are considered.

SpyGlass may exit abruptly if it is unable to set the stack size to unlimited.

By default, Spyglass internally sets the stack size to unlimited. However, if it is unable to do so due to insufficient permissions then the following warning message appears:

**WARNING:** Stacksize could not be set as unlimited through ulimit command. This may lead to nondeterministic tool behavior

In such cases, contact system administrator to check for permissions to change stack size.

# Messages Printed When SpyGlass Run is Complete

This section describes the exit codes when the SpyGlass run is complete.

These exit codes appear when you set the <a href="mailto:enable\_pass\_exit\_codes">exit\_codes</a> command

to yes. If you set this command to no, SpyGlass reports the default exit code of 0 in place of these exit codes, as described below.

- SpyGlass Exit Code 0 (Rule-checking completed without errors or warnings)

- The above message appears when a SpyGlass run is complete without any error or warning messages.

- Typically, this situation indicates that your design is clean with respect to the executed goals.

- SpyGlass Exit Code 11 (Rule-checking completed with warnings)

- The above message appears when a SpyGlass run is complete without any error message but with warning messages.

- This status indicates that some rules of the warning severity are reported. See *WARNING Rule Severity-Class* for understanding and handling warning messages.

- SpyGlass Exit Code 12 (Rule-checking completed with errors)

- The above message appears when a SpyGlass run is complete with error messages (and possibly warning messages).

- This status indicates that some rules of the error severity are reported. See *ERROR Rule Severity-Class* for understanding and handling error messages.

- SpyGlass Exit Code 20 (Informational command executed, rule-checking not done)

- The above message appears if you have executed an informational option of SpyGlass.

- Typically, no further action is required for this exit status.

# Messages Printed When SpyGlass Run is not Complete

This section describes the exit codes when the SpyGlass run is not complete.

SpyGlass reports these exit codes irrespective of the value of the *enable pass\_exit\_codes* command.

■ SpyGlass Exit Code 1 (Abnormal termination - termination not trapped by software)

The above message appears when SpyGlass run is terminated because of an abnormal error that is not trapped by SpyGlass.

This exit status indicates some operating system-related problem, such as sack overflow and out of memory issue.

In such cases, the SpyGlass log file may also be incomplete as SpyGlass was not able to trap an error signal and report suitably in the log file.

In such cases, check available machine resources and do the required correction. If the problem persists, report the problem to Atrenta Support.

■ SpyGlass Exit Code 3 (Abnormal termination trapped by software)

The above message appears when SpyGlass run is terminated because of an error that is trapped by SpyGlass.

This exit status indicates that some operating system-related problem, such as segmentation fault or memory corruption has occurred but SpyGlass was able to trap the error signal and report suitably in log file.

In such cases, check the gdb trace and stack trace printed in the SpyGlass log file and take corrective action.

After SpyGlass traps the error signal, it tries to generate the moresimple report that contains error messages and/or rule violations reported before the end of run. If the moresimple report is generated, it may contain useful information, which may help in debugging the situation. Along with the error details given in the SpyGlass log file, send the moresimple report to Atrenta Support.

■ SpyGlass Exit Code 4 (License failure, rule-checking aborted)

The above message appears when a SpyGlass run is terminated because of a license failure.

Check the license status and take a corrective action.

■ SpyGlass Exit Code 5 (Rule-checking interrupted by User)

The above message appears when you forcibly terminate a SpyGlass

run by killing the corresponding process.

In this case, SpyGlass-generated results may be incomplete and should not be used.

■ SpyGlass Exit Code 6 (Rule-checking terminated due to FATAL errors - design syntax error)

The above message appears when a SpyGlass run is terminated because of a fatal design error (syntax errors). See *FATAL Rule Severity-Class* for understanding and handling fatal messages.

In this case, check design inputs and take a corrective action.

■ SpyGlass Exit Code 7 (Rule-checking terminated due to FATAL errors - usage or run error)

The above message appears when a SpyGlass run is terminated because of incorrect usage and incorrect/incomplete inputs. See *FATAL Rule Severity-Class* for understanding and handling fatal messages.

In this case, check the specified inputs and take a corrective action.

■ SpyGlass Exit Code 8 (Design database save failure, rule-checking aborted)

The above message appears when a design cannot be saved because of reasons, such as incorrect save database directory.

In this case, rectify the save and restore-related commands.

■ SpyGlass Exit Code 137 (run killed by user, or by system due to lack of resources like memory etc.)

The above message appears when a signal is sent to SpyGlass process to terminate the session immediately.

The signal is sent either by the user or by the operating system because of lack of resources, such as memory.

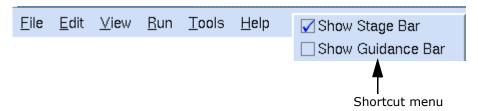

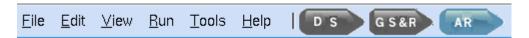

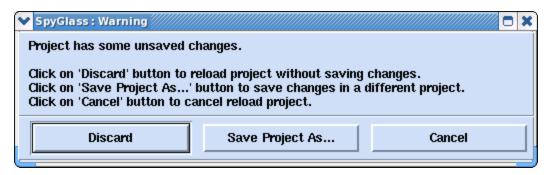

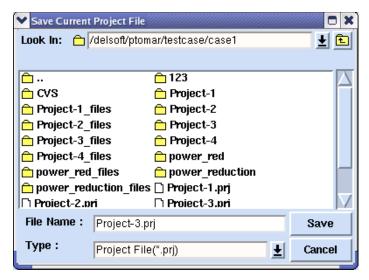

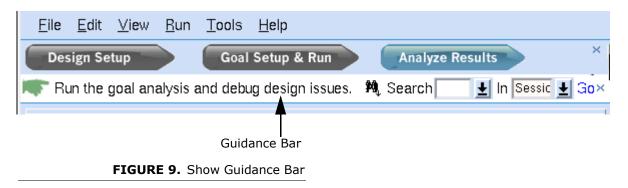

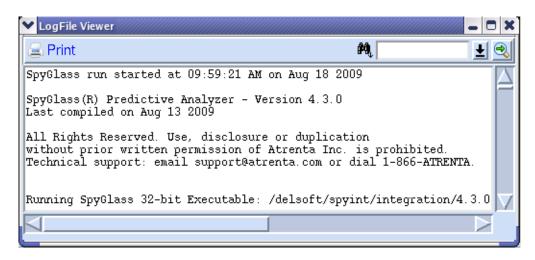

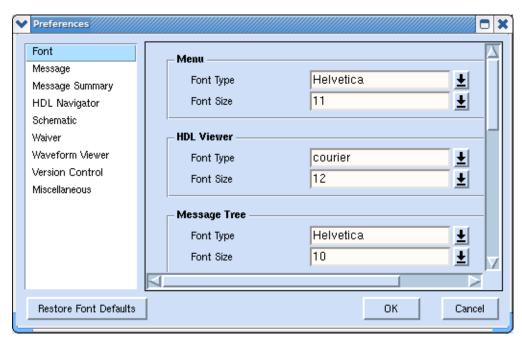

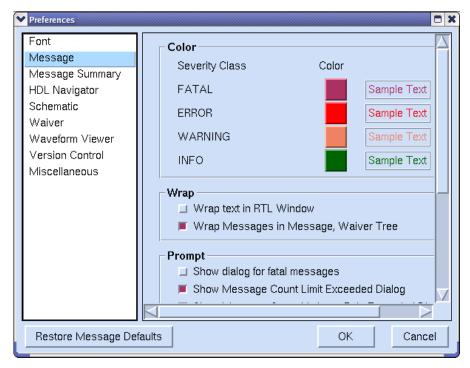

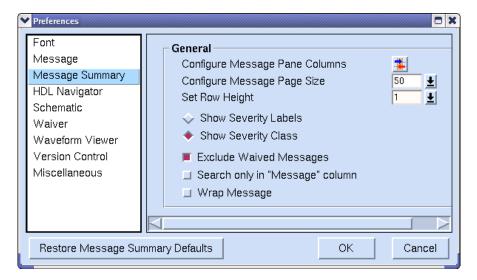

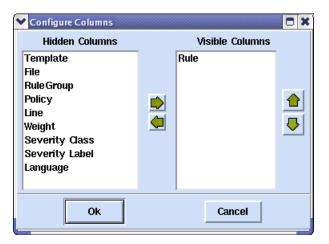

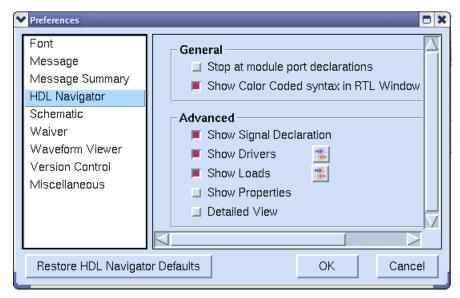

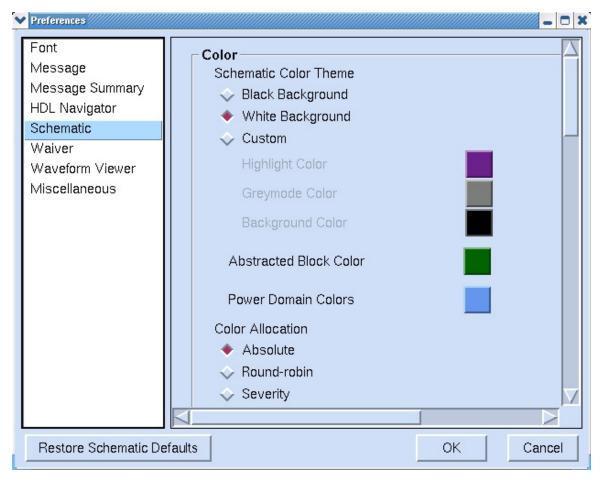

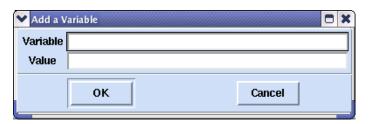

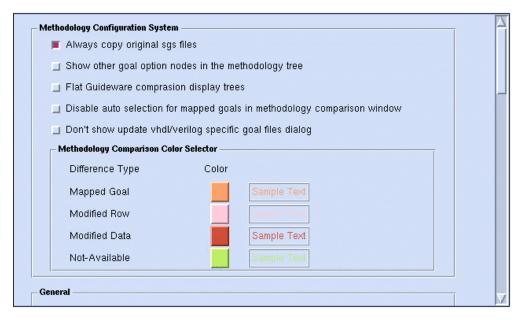

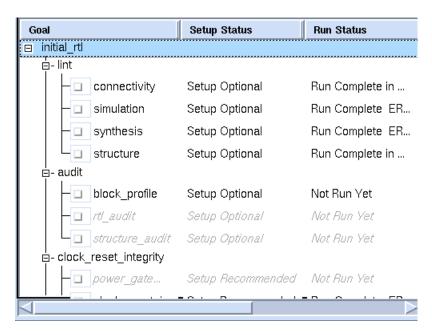

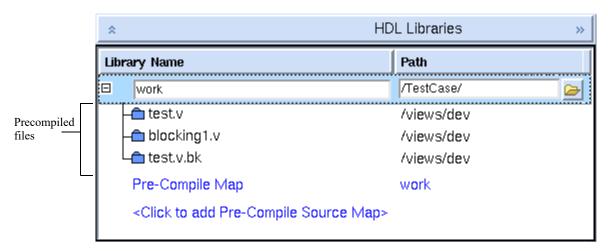

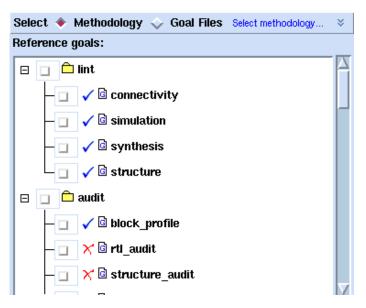

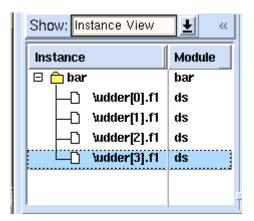

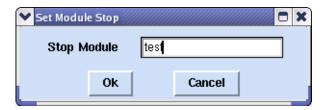

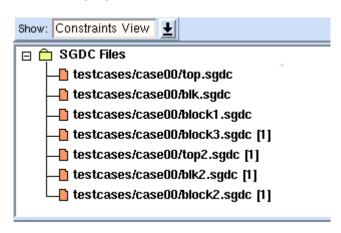

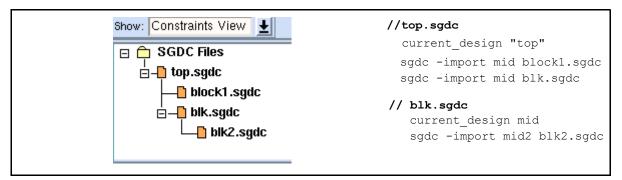

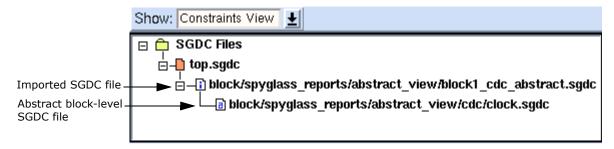

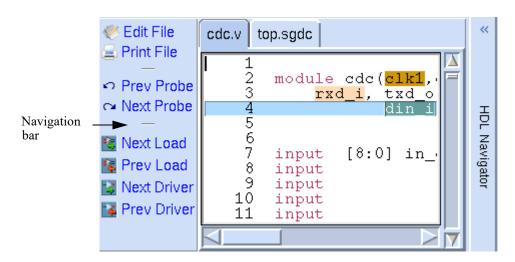

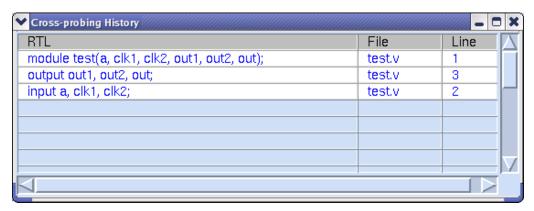

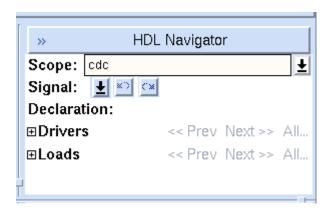

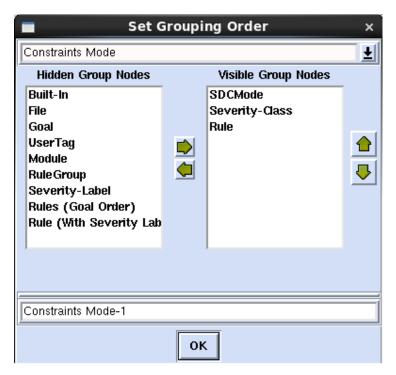

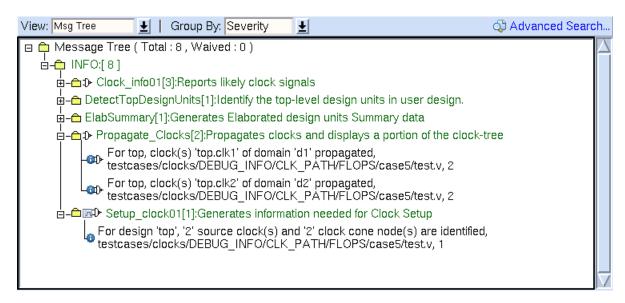

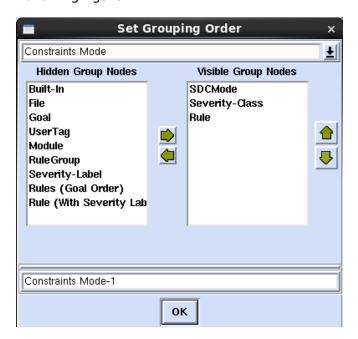

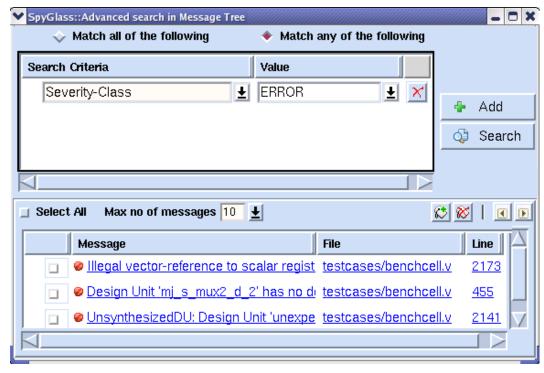

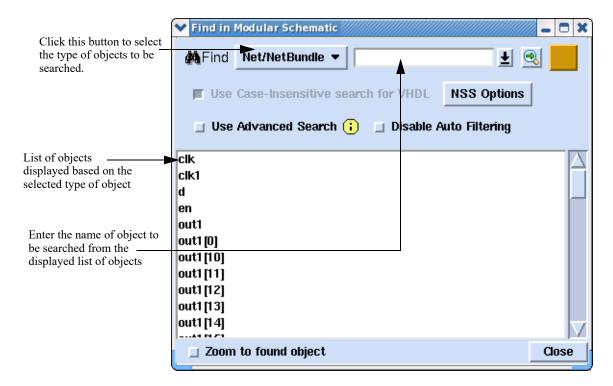

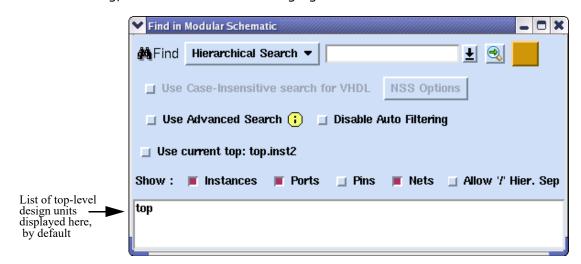

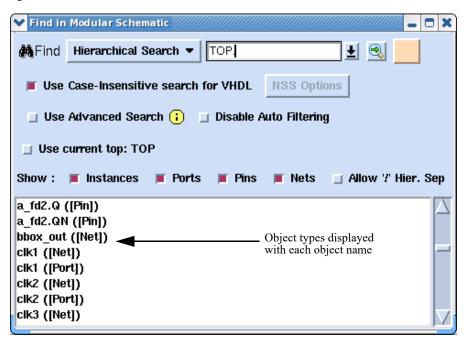

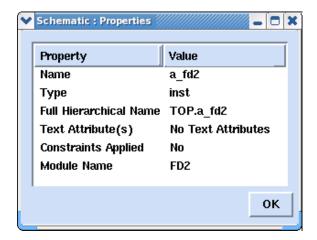

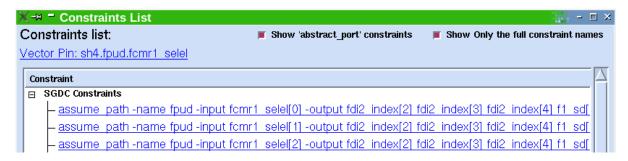

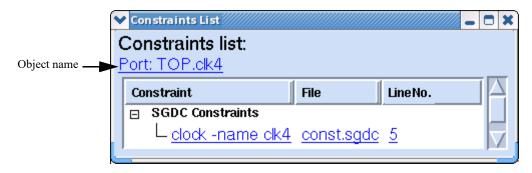

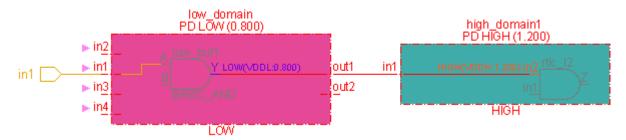

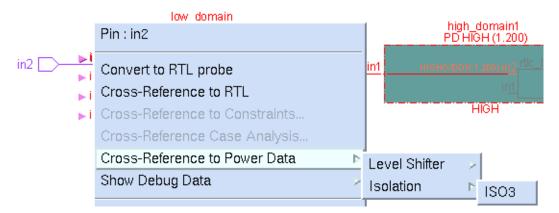

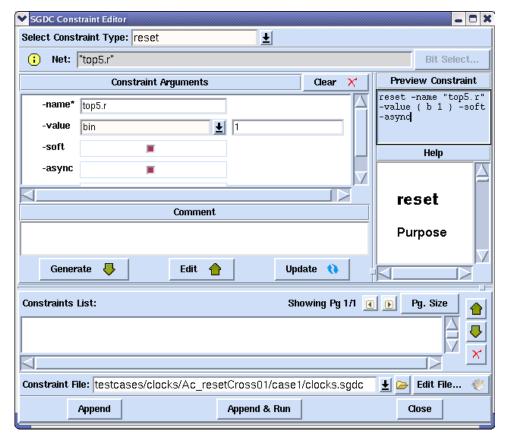

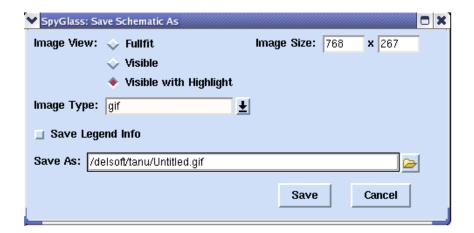

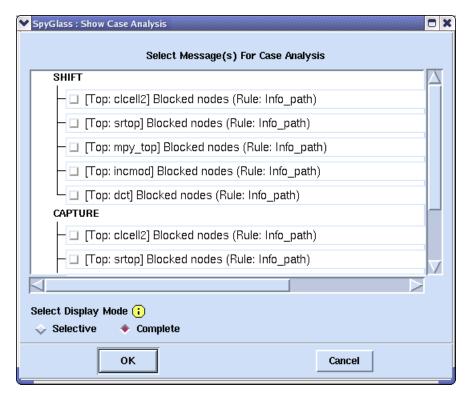

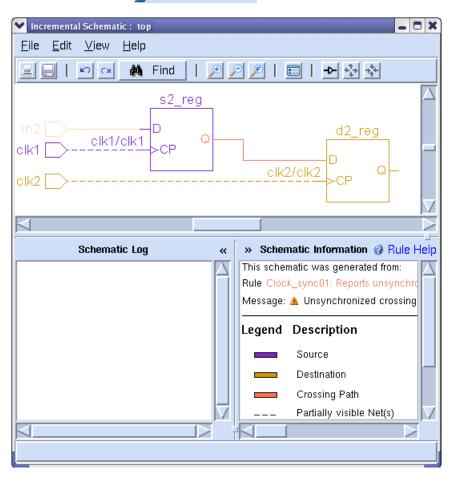

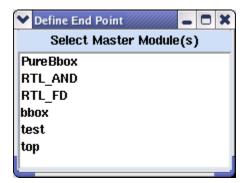

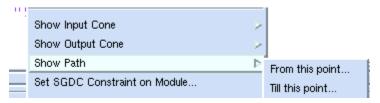

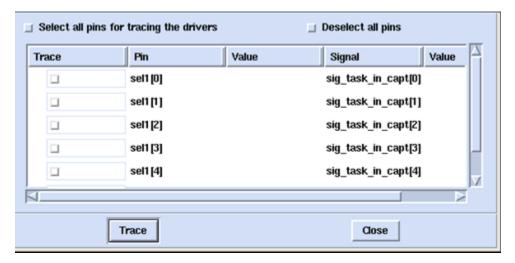

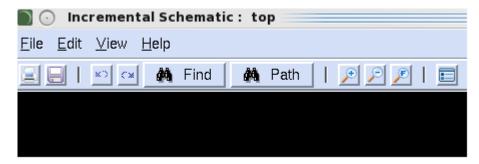

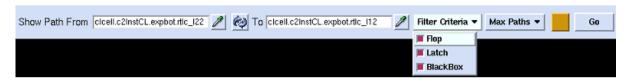

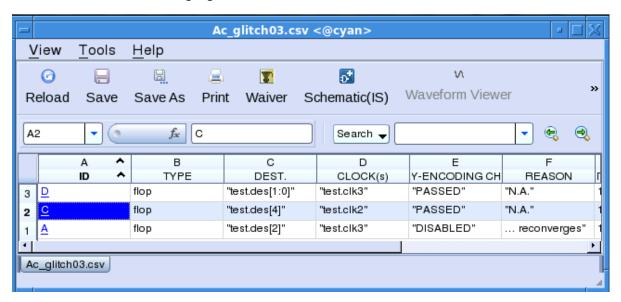

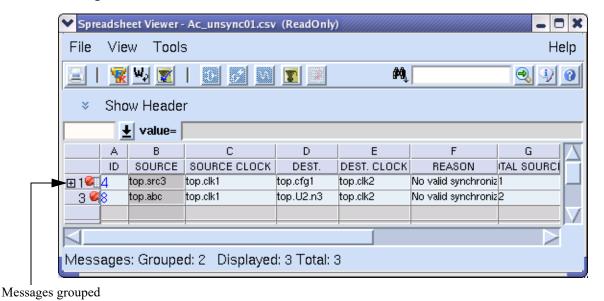

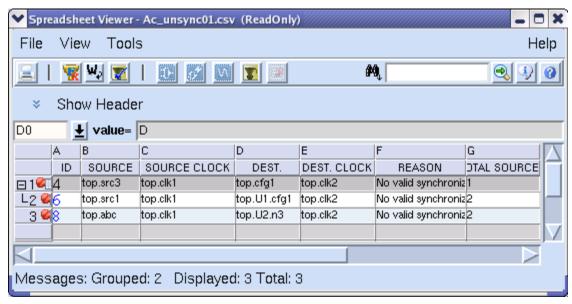

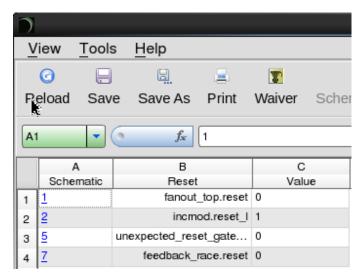

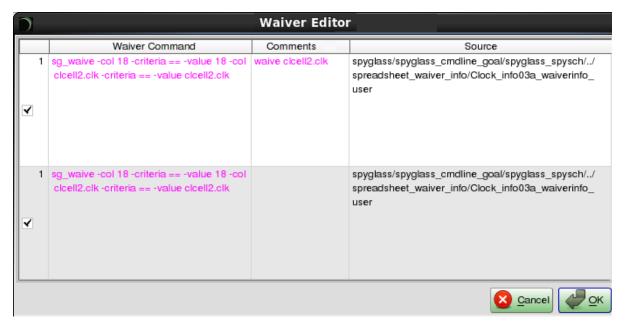

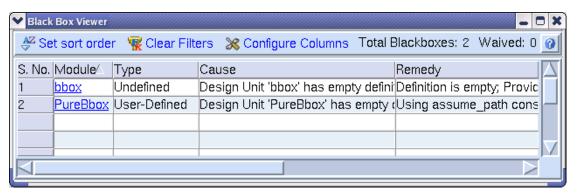

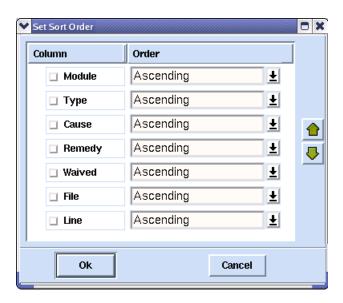

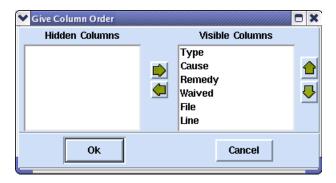

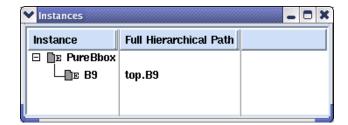

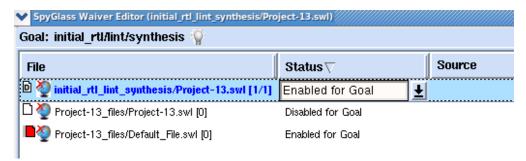

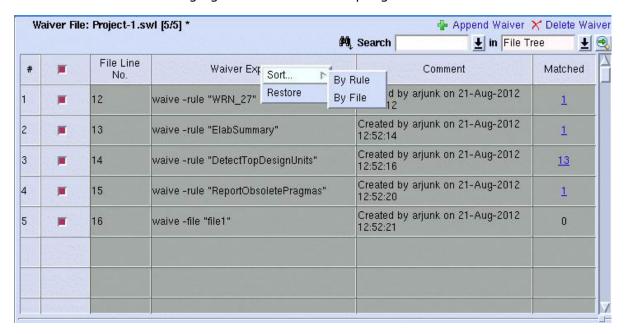

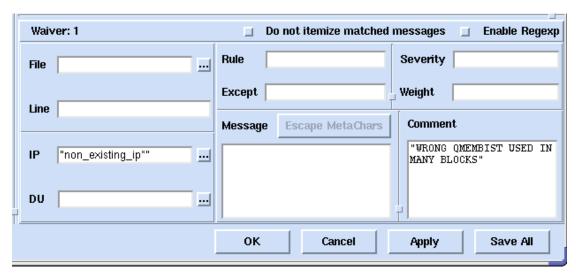

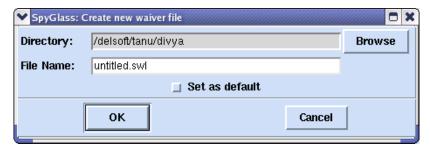

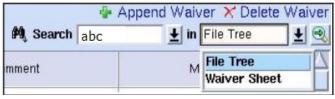

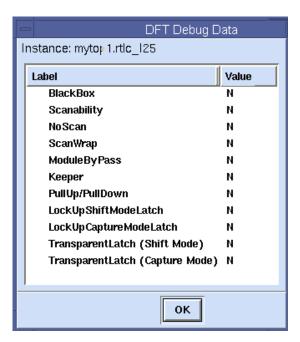

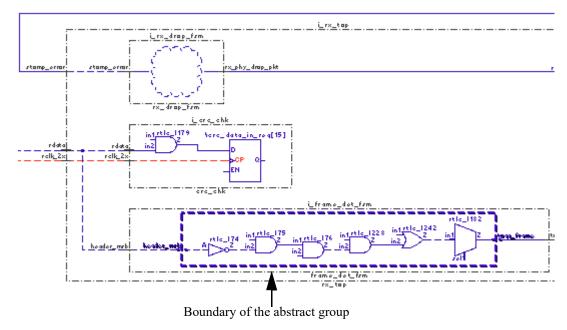

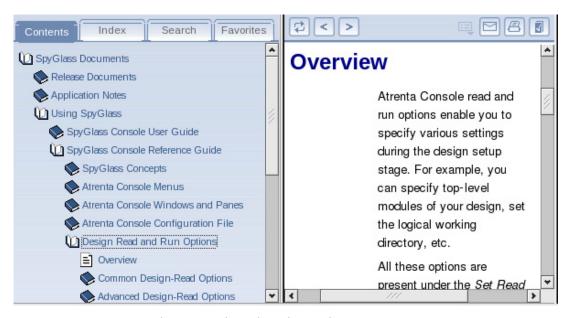

In this case, run SpyGlass on a machine that has higher memory.