# SpyGlass<sup>®</sup> Connectivity Verify Rules Reference Guide

Version N-2017.12-SP2, June 2018

#### **Copyright Notice and Proprietary Information**

© 2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at https://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

#### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

#### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

## Contents

| Preface                                                                  | 7  |

|--------------------------------------------------------------------------|----|

| About This Book                                                          | 7  |

| Contents of This Book                                                    |    |

| Typographical Conventions                                                |    |

| · ) / · · · · · · · · · · · · · · · · ·                                  |    |

| Using the Rules in the SpyGlass Connectivity Verify Product              | 11 |

| Overview                                                                 |    |

| Features of SpyGlass Connectivity Verify product                         | 12 |

| Types of Connectivity Verification Checks                                | 13 |

| Require Value Checks                                                     |    |

| Connectivity Checks                                                      |    |

| Conditional Connectivity Checks                                          |    |

| Licensing Requirements                                                   |    |

| Goals in the SpyGlass Connectivity Verify Product                        | 18 |

| SpyGlass Connectivity Verify Rule Parameters                             | 19 |

| dftAllowNonXValueAtStartOfSensitizedPathInSoc_02                         |    |

| dft_allow_path_from_enable_to_cgc_clkout                                 |    |

| dft_conn_check_allow_non_x_value_on_sensitizable_path                    | 20 |

| dft_conn_check_allow_trace                                               |    |

| dft_conn_check_handle_rtl_negedge                                        |    |

| dft_infer_clock_gating_cell                                              |    |

| dft_max_files_in_a_directory                                             |    |

| dft_require_path_fail_limit                                              |    |

| dft_require_path_invalid_limit                                           |    |

| dft_require_path_pass_limit                                              |    |

| dft_require_path_stop_check_on_pass_count                                |    |

| dft_soc_unstable_value_sources                                           |    |

| dftShowForcedValues                                                      |    |

| dftShowWaveForm                                                          |    |

| dft_treat_latches_with_X_on_enable_as_combinational_for_soc_path_c<br>27 |    |

| dftUseOffStateOfClockInClockPropagation                                  |    |

| showPowerGroundValue                                                     |    |

| Reports in SpyGlass Connectivity Verify Product                          | 30 |

| dft_connectivity_check_summary31                                                            |

|---------------------------------------------------------------------------------------------|

| Rules in SpyGlass Connectivity Verify                                                       |

| Overview                                                                                    |

| Soc_01 : Ensure that the expected node value is achieved                                    |

| <b>Soc_02</b> : Ensure that the paths between user-specified nodes exist42                  |

| Soc_04 : Show system state for a given tag                                                  |

| <b>Soc_07</b> : Checks the structure between the user-specified nodes55                     |

| Soc_08 : Checks the path between the user-specified nodes61                                 |

| Soc_09 : Path between user-specified nodes should not exist                                 |

| Soc_01_Info : Displays information for node whose expected node value is achieved74         |

| Soc_02_Info : Displays information for the connected user-specified                         |

| nodes79<br>Soc_07_Info : Reports the existence of structure between user-specified<br>nodes |

| Soc_10 : Reports nets with illegal node values                                              |

| <b>Soc_11</b> : Node must satisfy the specified constraint message tag expression 99        |

| Soc_12 : Node must not have the specified constraint message tag<br>expression              |

| Soc_14 : Ensure that specified nets are having stable values under specified condition      |

| Atspeed_21 : Check required pulse pattern at specified node                                 |

| Info_Atspeed_21 : Expected pulse pattern at the specified node achieved.<br>115             |

| Diagnose_testmode : Display instances that block the testmode<br>propagation                |

| Info_testmode : Display testmode simulation results                                         |

| Appendix:                                                                                   |

| SGDC Constraints            |     |

|-----------------------------|-----|

| SGDC Concepts               | 125 |

| SpyGlass Design Constraints | 126 |

## **About This Book**

The SpyGlass® Connectivity Rules Reference describes the SpyGlass rules that check the designs for point to point connectivity and required values on signals with enabling conditions and different modes of operation.

## **Contents of This Book**

The SpyGlass  $\ensuremath{\mathbb{B}}$  Connectivity Rules Reference consists of the following sections:

| Section                                                        | Description                                                                                 |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Using the Rules in the SpyGlass Connectivity<br>Verify Product | How to use the rules in the SpyGlass<br>Connectivity Verify product.                        |

| Rules in SpyGlass Connectivity Verify                          | Detailed description of the rules in the SpyGlass<br>Connectivity Verify product.           |

| Appendix: SGDC Constraints                                     | Tabular list of Constraints required for rules in the SpyGlass Connectivity Verify product. |

## **Typographical Conventions**

This document uses the following typographical conventions:

| To indicate                              | Convention Used                                                   |

|------------------------------------------|-------------------------------------------------------------------|

| Program code                             | OUT <= IN;                                                        |

| Object names                             | OUT                                                               |

| Variables representing objects names     | <sig-name></sig-name>                                             |

| Message                                  | Active low signal name ' <sig-name>' must end with _X.</sig-name> |

| Message location                         | OUT <= IN;                                                        |

| Reworked example<br>with message removed | OUT_X <= IN;                                                      |

| Important Information                    | NOTE: This rule                                                   |

The following table describes the syntax used in this document:

| Syntax                | Description                                           |

|-----------------------|-------------------------------------------------------|

| [ ] (Square brackets) | An optional entry                                     |

| { } (Curly braces)    | An entry that can be specified once or multiple times |

| (Vertical bar)        | A list of choices out of which you can choose one     |

| (Horizontal ellipsis) | Other options that you can specify                    |

# Using the Rules in the SpyGlass Connectivity Verify Product

The SpyGlass Connectivity Verify product contains a variety of connectivity-related rules. The rules in SpyGlass Connectivity Verify product assist in verifying required connections, logic values, frequencies, and structures.

This guide covers guidelines, parameter, and rule descriptions for using the Connectivity Verify Product effectively. Please refer to the *SpyGlass Explorer User Guide* for details on using the SpyGlass GUI.

This section explains the following topics:

- Overview

- Types of Connectivity Verification Checks

- Licensing Requirements

- Goals in the SpyGlass Connectivity Verify Product

- SpyGlass Connectivity Verify Rule Parameters

- Reports in SpyGlass Connectivity Verify Product

#### **Overview**

Assembling large structures from existing sub-blocks is a fundamental aspect of contemporary Soc designs. This requires large number of connections from top-level blocks to lower-level blocks. This includes connections between control signals, clock signals, and test logic.

The large amount of connections involved poses challenges in connectivity verification.

In such cases, the SpyGlass Connectivity Verify product enables you to verify:

- Connections between sub-blocks as well as connections from upperlevel blocks to lower-level blocks

- Confirmation that logic values on particular pins can be achieved with the proper setup of values on connecting pins

- Verification that values defined on the sgdc files for sub-blocks are achieved when sgdc files for the Soc are applied

- Verification that different frequencies can be achieved at required pins

This section explains the following topics:

- Features of SpyGlass Connectivity Verify product

- Types of Connectivity Verification Checks

#### Features of SpyGlass Connectivity Verify product

The SpyGlass Connectivity Verify product provides following features:

- Easy capture of connectivity-intent across IP/SoC: The product allows you to:

- **use compact & portable constraints**

- verify one-to-one, one-to-many, many-to-one connections

- □ Check for illegal conditions

- Verify conditional connectivity-checks

- Validate design methodology consistency across blocks and reuse at SoC level

- Static Checks Supplements Simulation Based Verification:

- □ Fast performance to quickly find basic connectivity bugs

- □ Supports regression use model

- □ Violations clearly state the failure root-cause

- GUI based design analysis

#### **Types of Connectivity Verification Checks**

The connectivity verification checks can be classified under the following categories:

- Require Value Checks

- Connectivity Checks

- Conditional Connectivity Checks

#### **Require Value Checks**

The require values checks enables you to verify logic values at different design locations.

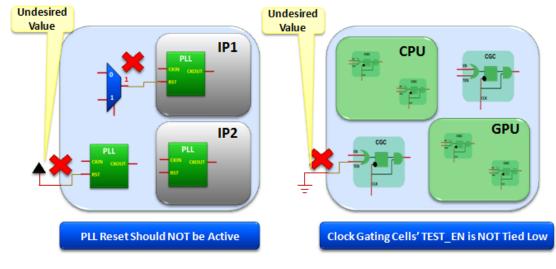

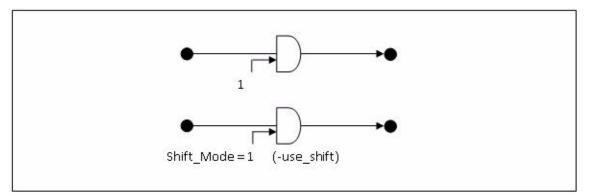

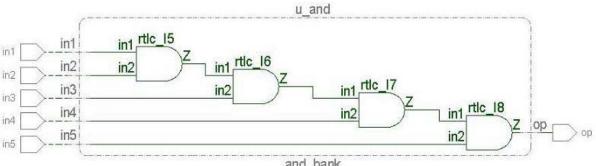

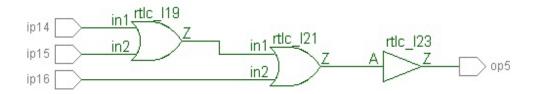

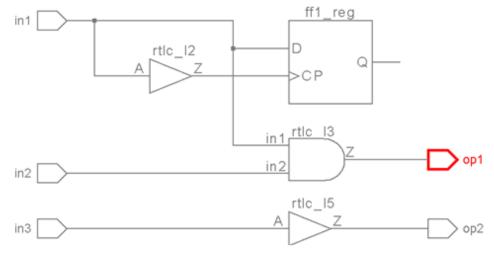

*Figure 1* illustrates require value checks under different enabling conditions:

FIGURE 1. Require Value Checks

In the above example, the SpyGlass Connectivity Verify product enables you to verify:

- PLL resets are at inactive value

- Clock gating cell (CGC) test enable pins are not tied off

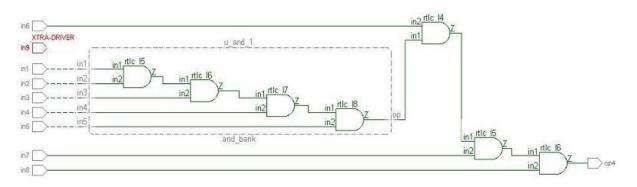

#### **Connectivity Checks**

The connectivity checks enables you to verify that a path exists for specified setup conditions.

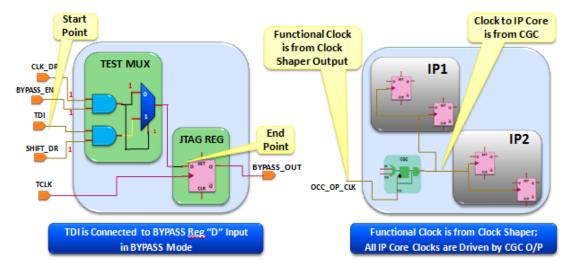

Figure 2 illustrates point to point connectivity checks:

FIGURE 2. Connectivity Checks

In the above example, the connectivity checks ensure:

- Connectivity from point A to point B across hierarchies

- All Functional clocks are driven from the clock shaper Output

- Core clocks are driven by Clock Gating Cells (CGCs)

#### **Conditional Connectivity Checks**

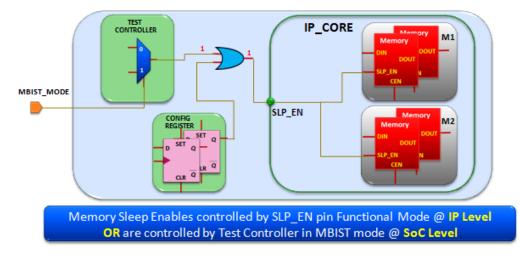

Conditional connectivity checks enables you to verify complex connections. *Figure 3* illustrates conditional connectivity checks:

FIGURE 3. Conditional Connectivity Checks

In the above example, the conditional checks validate that the memory sleep enables are controlled by:

- SLP\_EN pin at IP-level

- Configuration register in the functional mode at the SoC level

## **Licensing Requirements**

The SpyGlass Connectivity Verify product requires **soc\_conn\_adv** license.

# Goals in the SpyGlass Connectivity Verify Product

The SpyGlass Connectivity Verify product uses the connectivity\_verification goal. The connectivity\_verification goal enables easy capture of connectivity intent across IPs/SoCs and performs static checks to supplement simulation-based verification.

For details, refer to the GuideWare User Guide.

## **SpyGlass Connectivity Verify Rule Parameters**

This section provides explains all the parameters that are used by the rules of the SpyGlass Connectivity Verify product.

You can set these parameters by using the following command in SpyGlass Explorer and Tcl Shell Interface:

set\_parameter <parameter\_name> <parameter\_value>

For more information on setting the parameters, refer to the SpyGlass *Tcl Interface User Guide* and *SpyGlass Explorer User Guide*.

#### dftAllowNonXValueAtStartOfSensitizedPathInSoc\_02

The *dftAllowNonXValueAtStartOfSensitizedPathInSoc\_02* parameter is deprecated.

The non-x nodes are now always allowed as start point for the sensitized *require\_path* check. Therefore, the

dftAllowNonXValueAtStartOfSensitizedPathInSoc\_02 parameter is ignored.

#### dft\_allow\_path\_from\_enable\_to\_cgc\_clkout

Use this parameter to allow a connectivity path from enable (data and test) to CGC clock-out pin.

| Used by                    | Soc_02, Soc_02_Info, Soc_08, Soc_09                          |

|----------------------------|--------------------------------------------------------------|

| Options                    | on, off                                                      |

| Default value              | off                                                          |

| Example                    |                                                              |

| Console/Tcl-based usage    | set_parameter<br>dft_allow_path_from_enable_to_cgc_clkout on |

| Usage in goal/source files | -dft_allow_path_from_enable_to_cgc_clkout=on                 |

#### dft\_conn\_check\_allow\_non\_x\_value\_on\_sensitizable\_path

Allows non-x value (0 or 1) on a sensitizable path.

By default, the value of the parameter is on. Therefore, the *Soc\_02* and *Soc\_02\_Info* rules allow non-x value on the path while performing checks on the sensitizable paths.

Set the value of the parameter to off to ignore non-X value on the path while performing checks on the sensitizable paths.

| Used by       | Soc_02, Soc_02_Info |

|---------------|---------------------|

| Options       | on, off             |

| Default value | on                  |

| Example       |                     |

| Console/Tcl-based<br>usage            | set_parameter<br>dft_conn_check_allow_non_x_value_on_sensitizab<br>le path off |

|---------------------------------------|--------------------------------------------------------------------------------|

| <i>Usage in goal/source<br/>files</i> | <br>dft_conn_check_allow_non_x_value_on_sensitizab<br>le_path=off              |

#### dft\_conn\_check\_allow\_trace

Use this parameter to allow combinational traversal through the asynchronous pins of a flip-flop while performing the checks for require path (*require\_path* constraint) or illegal path (*illegal\_path* constraint).

| Used By                        | Conn_02, <i>Soc_02</i> , <i>Soc_02_Info</i> , Conn_08,<br>Conn_09, <i>Soc_08</i> , <i>Soc_09</i> |

|--------------------------------|--------------------------------------------------------------------------------------------------|

| Options                        | on, off                                                                                          |

| Default Value                  | off                                                                                              |

| Example                        |                                                                                                  |

| Console/Tcl-<br>based Usage    | set_parameter<br>dft_conn_check_allow_trace_through_async on                                     |

| Usage in goal/<br>source files | -dft_conn_check_allow_trace_through_async=on                                                     |

#### dft\_conn\_check\_handle\_rtl\_negedge

Considers the input to the inverter, in front of the CP/CLR/PRE pin, as the start/end point of the connectivity check.

By default the value of the parameter is off. In this case, the CP/CLR/PRE pin of the flip-flop remains the start/end point of the connectivity check.

Set the value of the parameter to yes to consider the input to the inverter, in front of the CP/CLR/PRE pin, as the start/end point of the connectivity check.

| Used by                           | <b>DFT</b> : Conn_01, Conn_02, Conn_08, Conn_09,                                         |

|-----------------------------------|------------------------------------------------------------------------------------------|

|                                   | Conn_10                                                                                  |

|                                   | Connectivity Verify: Soc_01, Soc_01_Info, Soc_02,<br>Soc_02_Info, Soc_08, Soc_09, Soc_10 |

| Options                           | on, off                                                                                  |

| Default value                     | off                                                                                      |

| Example                           |                                                                                          |

| Console/Tcl-based                 | set_parameter                                                                            |

| usage                             | dft_conn_check_handle_rtl_negedge off                                                    |

| <i>Usage in goal/source files</i> | -dft_conn_check_handle_rtl_negedge = off                                                 |

#### dft\_infer\_clock\_gating\_cell

Selects the behavior of automatic clock gating cell (CGC) inference.

By default, the value of this parameter is set to on and the cells similar to Clock Gating Cells (CGCs) are treated as CGCs.

Set the value of the parameter to off to turn off CGC inference.

See Identifying Clock Gating Cells section for more information on the ways to infer CGCs.

For more information on identifying CGCs, refer to the *Identifying Clock Gating Cells* section of the *SpyGlass DFT Rules Reference Guide*.

| Used by                       | All SpyGlass Connectivity Verify Rules           |

|-------------------------------|--------------------------------------------------|

| Options                       | on, off                                          |

| Default value                 | on                                               |

| Example                       |                                                  |

| Console/Tcl-based usage       | set_parameter dft_infer_clock_gating_cell<br>off |

| Usage in goal/source<br>files | -dft_infer_clock_gating_cell=off                 |

#### dft\_max\_files\_in\_a\_directory

Specifies maximum number of csv files in a single directory.

| Used by                           | All SpyGlass Connectivity Verify Rules                     |

|-----------------------------------|------------------------------------------------------------|

| Options                           | <any natural="" number=""></any>                           |

| Default value                     | 2000                                                       |

| Example                           |                                                            |

| Console/Tcl-based usage           | <pre>set_parameter dft_max_files_in_a_directory 5000</pre> |

| <i>Usage in goal/source files</i> | -dft_max_files_in_a_directory=5000                         |

#### dft\_require\_path\_fail\_limit

Selects the number of violations reported by the *Soc\_02* and *Soc\_08* rules for the *require\_path* and *require\_strict\_path* constraints failure when either the -from\_one\_of or -to\_one\_of arguments of the constraints are not specified.

| Used by                                   | Soc_02, Soc_08                               |

|-------------------------------------------|----------------------------------------------|

| Options                                   | <any natural="" number=""></any>             |

| Default Value                             | 10                                           |

| Example                                   |                                              |

| Console/Tcl-<br>based usage               | set_parameter dft_require_path_fail_limit -1 |

| <i>Usage in<br/>goal/source<br/>files</i> | -dft_require_path_fail_limit=-1              |

|                                           |                                              |

#### dft\_require\_path\_invalid\_limit

Limits the number of invalid path violations reported by the Soc\_08 rule for the *require\_strict\_path* constraint failure.

| Used by                          | Soc_08                                          |

|----------------------------------|-------------------------------------------------|

| Options                          | <any natural="" number=""></any>                |

| Default Value                    | 10                                              |

| Example                          |                                                 |

| Console/Tcl-<br>based usage      | set_parameter dft_require_path_invalid_limit -1 |

| Usage in<br>goal/source<br>files | dft_require_path_invalid_limit=-1               |

#### dft\_require\_path\_pass\_limit

Limits the number of violations reported by the *Soc\_02\_Info* and *Soc\_08* rules for the *require\_path* and *require\_strict\_path* constraints success when either the -from\_one\_of or -to\_one\_of arguments of the constraints are specified.

| Used by                          | Soc_02_Info, Soc_08                         |

|----------------------------------|---------------------------------------------|

| Options                          | <any natural="" number=""></any>            |

| Default Value                    | -1                                          |

| Example                          |                                             |

| Console/Tcl-<br>based usage      | set_parameter dft_require_path_pass_limit 1 |

| Usage in<br>goal/source<br>files | -dft_require_path_pass_limit=1              |

#### dft\_require\_path\_stop\_check\_on\_pass\_count

Limits the number of violations reported by the *Soc\_02\_Info* rule when both the conditions are true:

SpyGlass Connectivity Verify Rule Parameters

- Either the -from\_one\_of or -to\_one\_of arguments for the require\_path constraint is specified

- The *require\_path* constraint check is successful

| Used by                                   | Soc_02_Info                                                  |

|-------------------------------------------|--------------------------------------------------------------|

| Options                                   | <any natural="" number=""></any>                             |

| Default Value                             | -1                                                           |

| Example                                   |                                                              |

| Console/Tcl-<br>based usage               | set_parameter<br>dft_require_path_stop_check_on_pass_count 1 |

| <i>Usage in<br/>goal/source<br/>files</i> | -dft_require_path_stop_check_on_pass_count=1                 |

#### dft\_soc\_unstable\_value\_sources

Specifies unstable value sources, other than scannable flip-flops and latches, that needs to be reported by the *Soc\_14* rule.

| Used by                                   | Soc_14                                                       |  |

|-------------------------------------------|--------------------------------------------------------------|--|

| Options                                   | none, all, blackbox, hanging_net, port                       |  |

| Default Value                             | none                                                         |  |

| Example                                   |                                                              |  |

| Console/Tcl-<br>based usage               | <pre>set_parameter dft_soc_unstable_value_sources none</pre> |  |

| <i>Usage in<br/>goal/source<br/>files</i> | -dft_soc_unstable_value_sources=none                         |  |

#### dftShowForcedValues

Use the dftShowForcedValues rule parameter to differentiate between the values enforced by the user and values that have been propagated automatically by the rule.

The dftShowForcedValues rule parameter controls the display of

signals in the schematic view. When the dftShowForcedValues is set, signals forced onto specific nodes by the test\_mode constraints appear as O(F) or 1(F). Signals that result or are implied from these forced signals appear as 0 or 1 (without the (F) suffix).

This provides clear differentiation between causal signals and result signals. For example, in a design where the output of an AND gate is set to 1 by a test\_mode constraint and where other constraints on nodes in the fan-in cone for AND cause a 0 on one of the AND gate inputs, the output of the AND will retain its forced value. Therefore, the inconsistency of a 0 on an AND input and a 1 on the AND output may be resolved.

When the dftShowForcedValues is not set, the (F) suffix does not appear.

| Used by                               | Info_testmode                         |

|---------------------------------------|---------------------------------------|

| Options                               | off, on                               |

| Default value                         | on                                    |

| Example                               |                                       |

| Console/Tcl-based usage               | set_parameter dftShowForcedValues off |

| <i>Usage in goal/source<br/>files</i> | -dftShowForcedValues=off              |

#### dftShowWaveForm

Use this parameter to select whether or not to display the waveform information for the *Info\_testmode* rule.

| Used by                           | Info_testmode                    |

|-----------------------------------|----------------------------------|

| Options                           | on, off                          |

| Default value                     | off                              |

| Example                           |                                  |

| Console/Tcl-based usage           | set_parameter dftShowWaveForm on |

| <i>Usage in goal/source files</i> | -dftShowWaveForm=on              |

### dft\_treat\_latches\_with\_X\_on\_enable\_as\_combinational\_fo r\_soc\_path\_checks

Defines the treatment of latches, that is, whether to consider them as combinational or sequential, where enable pin does not get either 0 or 1, when running Soc path check rules.

| Used by                           | Soc_02, Soc_02_Info, Soc_08, Soc_09                                                                  |

|-----------------------------------|------------------------------------------------------------------------------------------------------|

| Options                           | on, off                                                                                              |

| Default value                     | off                                                                                                  |

| Example                           |                                                                                                      |

| Console/Tcl-based usage           | <pre>set_parameter dft_treat_latches_with_X_on_enable_as_combin ational_for_soc_path_checks on</pre> |

| <i>Usage in goal/source files</i> | -<br>dft_treat_latches_with_X_on_enable_as_combin<br>ational_for_soc_path_checks = on                |

#### dftUseOffStateOfClockInClockPropagation

Specifies the treatment of the off state of the clocks during shift, capture, or atspeed mode.

By default, the dftUseOffStateOfClockInClockPropagation parameter is set to on to simulate the off state of the test clock, that is, 0 for rtz and 1 for rto. It also keeps functional clocks to unknown state during the shift mode.

Set this parameter to off to keep all clocks, including functional and test clocks to unknown state. See the table below to view the list of other possible values.

The following table lists the clock state and the corresponding event applied on it during scanshift mode simulation:

| Clock State | Event Applied       |  |

|-------------|---------------------|--|

| Unknown     | No event is applied |  |

| Clock State  | Event Applied        |  |

|--------------|----------------------|--|

| off          | 0X (rtz) or 1X (rto) |  |

| free running | 0X1X                 |  |

An 'X' is always simulated at the end is that clock line is free during clock propagation. You can use this parameter when ICGs are used to drive constant value.

| Used by                               | All rules in the SpyGlass Connectivity Verify product                                                                                                                                                                                                                   |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Options                               | off, on, fclk_unknown_n_tclk_unknown,<br>fclk_unknown_n_tclk_off_state,<br>fclk_unknown_n_tclk_free_running,<br>fclk_off_state_n_tclk_off_state,<br>fclk_off_state_n_tclk_free_running,<br>fclk_free_running_n_tclk_off_state,<br>fclk_free_running_n_tclk_free_running |

| Default value                         | on                                                                                                                                                                                                                                                                      |

| Example                               |                                                                                                                                                                                                                                                                         |

| Console/Tcl-based usage               | set_parameter<br>dftUseOffStateOfClockInClockPropagation off                                                                                                                                                                                                            |

| <i>Usage in goal/source<br/>files</i> | -dftUseOffStateOfClockInClockPropagation=<br>fclk_free_running_n_tclk_off_state                                                                                                                                                                                         |

|                                       |                                                                                                                                                                                                                                                                         |

#### showPowerGroundValue

Use this parameter to control the schematic display for power/ground simulation.

When the value of the parameter is set to on, the simulation value of a net due to power/ground is displayed. To hide the power/ground simulation values of a net, set this switch to 'off'.

| Example       |               |  |

|---------------|---------------|--|

| Default value | on            |  |

| Options       | on, off       |  |

| Used by       | Info_testmode |  |

SpyGlass Connectivity Verify Rule Parameters

| Console/Tcl-based usage       | <pre>set_parameter showPowerGroundValue off</pre> |

|-------------------------------|---------------------------------------------------|

| Usage in goal/source<br>files | -showPowerGroundValue=off                         |

## Reports in SpyGlass Connectivity Verify Product

The SpyGlass Connectivity Verify product generates the rules and reports that you can view from the *Reports* menu in SpyGlass Explorer or by using the set\_option report <report-name> command followed by the report name.

The SpyGlass Connectivity Verify product generates *dft\_connectivity\_check\_summary* report that contains a summary of the Soc\_01, Soc\_02, Soc\_07, Soc\_08, Soc\_09, Soc\_01\_Info, Soc\_02\_Info, and Soc\_07\_Info rules.

#### dft\_connectivity\_check\_summary

The dft\_connectivity\_check\_summary.rpt file is generated by the *Soc\_01*, *Soc\_02*, *Soc\_07*, *Soc\_08*, *Soc\_09*, *Soc\_01\_Info*, *Soc\_02\_Info*, and *Soc\_07\_Info* rules. This report contains a summary of these rules.

```

# Purpose :

#

The report summarizes all the connectivity check results

#

#

require value:

Checked by Soc 01, Soc 01 Info

Reports the number of 'require_value' constraints

#

#

passed and failed

#

#

require_path: Checked by Soc_02, Soc_02_Info

#

Reports the number of 'require path' constraints passed

and failed

#

#

#

require structure: Checked by Soc 07, Soc 07 Info

Reports the number of 'require structure' constraints

#

#

passed and failed

#

#

require strict path: Checked by Soc 08

#

Reports the number of 'require_strict_path' constraints

#

passed and failed

#

#

illegal path: Checked by Soc 09

#

Reports the number of 'illegal_path' constraints passed

#

and failed

#

#

NOTE : For more details, refer to the corresponding

#

rule violations

```

```

# Format :

# Top design unit: <top_design_name>

#

```

```

#

require value:

#

<N> require value constraints passed

#

<N> require_value constraints failed

#

#

require path:

<N> require_path constraints passed

#

#

<N> require_path constraints failed

#

#

require_structure:

#

<N> require_structure constraints passed

#

<N> require structure constraints failed

#

#

require strict path:

<N> require_strict_path constraints passed

#

#

<N> require_strict_path constraints failed

#

#

illegal path:

<N> illegal_path constraints passed

#

#

<N> illegal path constraints failed

#

#

NOTE : If a particular rule is disabled in the current

#

run, then there will not be a section corresponding to

that rule

#

Top design unit: top1

require_value:

'1' require value constraint passed

No require value constraint failed

require path:

'2' require path constraints passed

No require_path constraint failed

require_structure:

```

Reports in SpyGlass Connectivity Verify Product

```

No require structure constraint passed

'1' require structure constraint failed

require strict path:

'2' require strict path constraints passed

'2' require_strict_path constraints failed

illegal path:

'1' illegal_path constraint passed

'2' illegal path constraints failed

Top design unit: top2

require value:

No valid require_value constraint specified

require path:

No valid require_path constraint specified

require_structure:

No valid require_structure constraint specified

require_strict_path:

No valid require_strict_path constraint specified

illegal_path:

No valid illegal_path constraint specified

```

Reports in SpyGlass Connectivity Verify Product

# Rules in SpyGlass Connectivity Verify

#### **Overview**

The SpyGlass<sup>®</sup> Connectivity Verify product has the following rules:

| Rule        | Flags/Highlights                                                                               |

|-------------|------------------------------------------------------------------------------------------------|

| Soc_01      | Nodes that do not achieve expected values                                                      |

| Soc_02      | Missing net connections between specified nodes                                                |

| Soc_04      | Simulation results for the conditions specified by a tag                                       |

| Soc_07      | Structures that are not same as the user-specified structures between the user-specified nodes |

| Soc_08      | The path between the user-specified nodes                                                      |

| Soc_09      | Path between user specified nodes should not exist                                             |

| Soc_01_Info | Nodes that achieve expected values                                                             |

| Soc_02_Info | Valid net connections between specified nodes                                                  |

| Soc_07_Info | Structures that are same as the user-specified structures between the user-specified nodes     |

| Soc_10      | Reports nets with illegal node values                                                          |

| Soc_11      | Ensures that the node satisfies the specified constraint message tag expression                |

| Rule                  | Flags/Highlights                                                                    |

|-----------------------|-------------------------------------------------------------------------------------|

| Soc_12                | Ensures that the node does not have the specified constraint message tag expression |

| Soc_14                | Ensure that specified nets are having stable values under specified condition       |

| Atspeed_21            | Check required pulse pattern at specified node                                      |

| Info_Atspeed_2<br>1   | Expected pulse pattern at the specified node achieved.                              |

| Diagnose_testm<br>ode | Display instances that block the testmode propagation.                              |

| Info_testmode         | Display testmode simulation results                                                 |

# Soc\_01

## Ensure that the expected node value is achieved

## When to Use

Use this rule to identify the nodes that do not achieve the expected simulation value.

## Description

The Soc\_01 rule generates the SpyGlass Explorer highlight data for those nodes specified with *require\_value* constraints that do not achieve the specified simulation value when the specified tag condition is simulated.

Expected values at arbitrary nodes and the applied values that should cause or force the expected values are checked. This is useful for ensuring that unit-level test requirements are satisfied at the SoC level.

Consider the following require\_value constraint:

require\_value

-tag <tagName> -name <nodeNames> -value <value>

The Soc\_01 rule generates the SpyGlass Explorer highlight data for those nodes specified with the -name argument that do not achieve the simulation value <value> when the conditions of <tagName> are simulated.

To view the nodes that achieve the expected value, use the *Soc\_01\_Info* rule.

## Prerequisites

Specify the *require\_value* constraint.

## **Default Weight**

10

## Language

Verilog, VHDL

## Method

For each define\_tag, simulate power, ground and all conditions defined for this define\_tag.

For each require\_value with the current define\_tag, check that the defined pin has the

defined value. Otherwise, report a message.

# Parameter(s)

- dft\_conn\_check\_handle\_rtl\_negedge: Default value is off. Set the value of the parameter to yes to consider the input to the inverter, in front of the CP/CLR/PRE pin, as the start/end point of the connectivity check.

- *dftUseOffStateOfClockInClockPropagation*: The default value of the parameter is on. Set the value of the parameter to off so that clock lines are kept at X during shift, capture, or atspeed mode simulation.

# Constraint(s)

- define\_tag: Use this constraint to define a named condition for application of certain stimulus at the top port or an internal node.

- require\_value: Use this constraint to define a check that requires a logic value to be established on a certain node when the circuit has been simulated using the condition specified by the -tag argument.

# **Operating Mode**

Define\_tag

## **Messages and Suggested Fix**

The following violation messages are displayed for the Soc\_01 rule:

## Message 1

[ERROR] [constraint\_message\_tag: <value>] Node <name> has value <value1>. (Required: <value2>) under tag <tag-name>

## Arguments

- Constraint tag value, <value>

- Name of the node <name>

- Actual value <value1>

- Expected value <value2>

- Tag name <tag-name>

**NOTE:** The constraint tag value is prefixed to the violation message only if you specify the -constraint\_message\_tag argument for the require\_value constraint.

## **Potential Issues**

A violation is reported due to incomplete or incorrect simulation condition or incorrect design connectivity.

#### Consequences of Not Fixing

Not fixing the violation may result in unexpected code behavior.

#### How to Debug and Fix

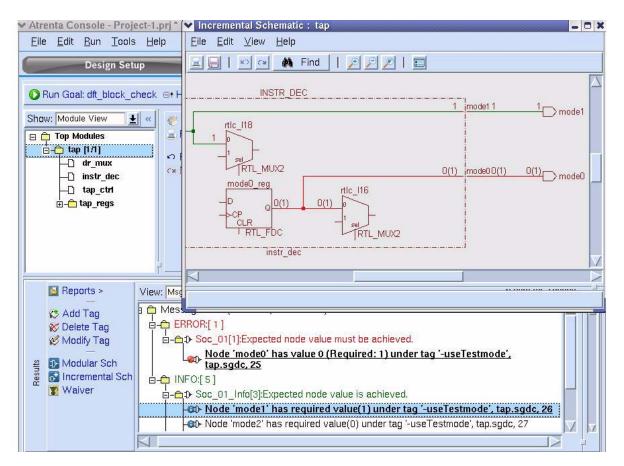

View the Incremental Schematic for the violation message. The Incremental Schematic highlights the node where the required simulation mismatches the actual simulation.

You can also view the violation for the Soc\_04 rule along with the violation of the Soc\_01 rule in the Incremental Schematic window. To do this, double-click the violation for the Soc\_01 rule and open the Incremental Schematic window.

The violation message for the Soc\_04 rule overlaps the violation message for the Soc\_01 rule in the Incremental Schematic window. This is useful in debugging the violation for the Soc\_01 rule.

To fix the violation, see Example Code and/or Schematic section.

## Message 2

**[WARNING]** [constraint\_message\_tag: <value>] illegal\_value command is using option -matchNBits (<value1>) without setting parameter dftShowWaveForm to 'on' under <tag-name>. Setting -matchNBits to value '1' for the rule checking purpose

## Arguments

- Constraint tag value, <value>

- Illegal value <value1>

- Tag name <tag-name>

## **Potential Issues**

A violation is reported when the following conditions hold true:

- Value of the *dftShowWaveForm* parameter is not set on

- The require\_value constraint uses the -matchNbits <value> argument under <tag-name> condition

- The value of the -matchNBits argument is greater than 1

The Soc\_01 rule does not report this violation message if the tag is defined using the *define\_tag* command.

#### Consequences of Not Fixing

Not fixing the violation may result in unexpected code behavior.

#### How to Debug and Fix

To fix the violation, set the value of the *dftShowWaveForm* parameter to on.

## **Example Code and/or Schematic**

Consider the following example:

require\_value -name mode2 -value 0 -matchNBits 1 -useTestmode require\_value -name mode3 -value 1 -matchNBits 1 -useTestmode

# **Default Severity Label**

Error

# **Rule Group**

SoC

# **Reports and Related Files**

*dft\_connectivity\_check\_summary*.rpt: Reports the number of *require\_value* constraints passed and failed.

# Soc\_02

#### Ensure that the paths between user-specified nodes exist

#### When to Use

Use this rule to identify the disjointed pair of user-specified nodes.

## **Rule Description**

The Soc\_02 rule reports connection violations between specified pair of nodes.

The Soc\_02 rule checks either conditional or unconditional paths between user-specified nodes.

**NOTE:** The Soc\_02 rule checks all require\_path constraints — without the -tag argument and with the -tag argument (earlier checked by the now obsolete Soc\_03 rule.)

While processing the *require\_path* constraints, Soc\_02 rule checking depends on -path type and simulation condition as discussed below:

| Specified field of require_path constraint | Simulation condition |

|--------------------------------------------|----------------------|

| -use_shift                                 | Shift                |

| -use_capture                               | Capture              |

| -use_captureATspeed                        | Capture (atspeed)    |

| -tag <tag_name></tag_name>                 | tag_name             |

| If none of the above specified             | Power ground         |

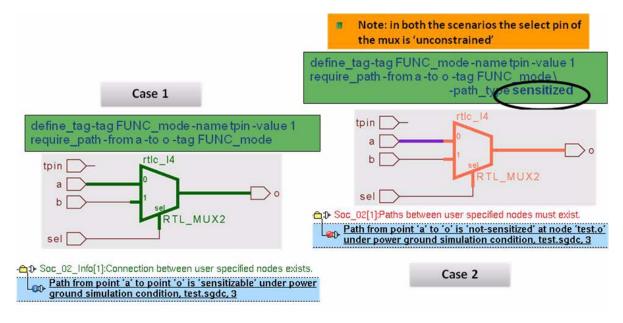

- If you specify the value of the -path\_type argument as sensitized, the Soc\_02 rule performs the strict functional checking. This ensures that the path is properly sensitized by the specified simulation condition.

- If you specify the value of the -path\_type argument as sensitizable, the Soc\_02 rule performs the functional checking. This ensures that the path is properly sensitizable and is not blocked by the simulation condition.

- □ If you specify the value of the -path\_type argument as buffered, the Soc\_02 rule looks for strict topological checking and checks for buffers and inverters only.

□ If you do not specify the value of the -path\_type argument, the default value of the argument, that is, sensitizable is used.

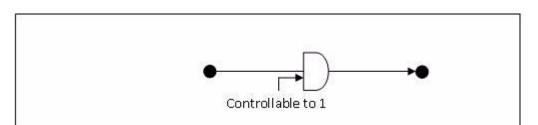

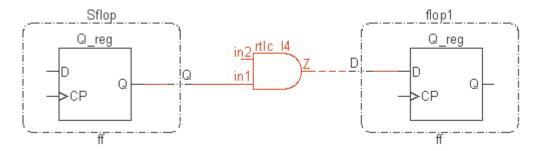

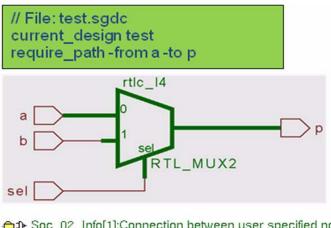

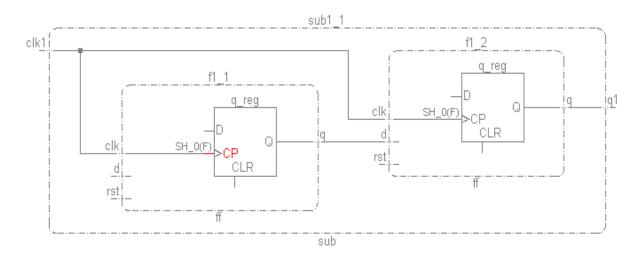

Consider the following example, where Shift\_Mode is equal to 1, that is, -use\_shift parameter is specified.

The above figure shows an example of the sensitized path. Here, the value of the -path\_type argument is set as sensitized, which ensures the existing logic connectivity between the start and end points. Consider the following example, where the clock is controllable to 1:

The above figure shows an example of the sensitizable path. Here, the value of the -path\_type argument is specified as sensitizable, which checks whether the target path is sensitizable during the specific simulation condition.

SoC integration often requires that connections between various units exist. This rule allows arbitrary from-to pin to be checked.

To view the valid paths, use the Soc\_02\_Info rule.

The Soc\_02 rule flags a violation if during traversal to find a path between

two nodes, a contentious net is found. This path is no longer considered a correct path, therefore, the *Soc\_02\_Info* rule does not highlight this path.

**NOTE:** If you do not specify the -undirected qualifier in the require\_path constraint, the Soc\_02 rule traces the path from -from node to -to node only.

## Prerequisites

Specify the *require\_path* constraint.

#### **Default Weight**

10

#### Language

Verilog, VHDL

#### Method

If specified, simulate require path for <path\_type> verification under specified simulation condition.

For each from-to pair of require\_path specification:

Walk the unblocked fan-out cone under the simulation condition from the start point while maintaining the phase inversion. If the walk doesn't terminate on the specified endpoint for the required path\_type>, report a violation.

# Parameter(s)

- *dftAllowNonXValueAtStartOfSensitizedPathInSoc\_02*: This parameter is deprecated and is ignored for rule-checking.

- dft\_allow\_path\_from\_enable\_to\_cgc\_clkout: The default value is off. Set the value of the parameter to on to allow a connectivity path from enable (data and test) to CGC clock-out pin.

- dft\_conn\_check\_allow\_non\_x\_value\_on\_sensitizable\_path: The default value is on. Set the value of the parameter to off to ignore non-X (0 or 1) value on the path while performing checks on the sensitizable paths.

- dft\_conn\_check\_handle\_rtl\_negedge: Default value is off. Set the value of the parameter to yes to consider the input to the inverter, in front of the CP/CLR/PRE pin, as the start/end point of the connectivity check.

- dft\_require\_path\_fail\_limit: The default value is 10. Set the value of the parameter to any natural number to control the number of violations reported by the Soc\_02 rule for the require\_path constraint failure when

either the -from\_one\_of or -to\_one\_of arguments of the *require\_path* constraint is specified.

- dft\_treat\_latches\_with\_X\_on\_enable\_as\_combinational\_for\_soc\_path\_checks: The default value is off. Set the value of the parameter to on to define the treatment of latches. That is, whether to consider them as combinational or sequential, where enable pin does not get either 0 or 1, when running Soc path check rules.

- dftUseOffStateOfClockInClockPropagation: The default value of the parameter is on. Set the value of the parameter to off so that clock lines are kept at X during shift, capture, or atspeed mode simulation.

- dft\_conn\_check\_allow\_trace: The default value is off. Set the value of the parameter to on to allow combinational traversal through the asynchronous pins of a flip-flop while performing the checks for require path (require\_path constraint) or illegal path (illegal\_path constraint).

# Constraint(s)

- require\_path (mandatory): Use this constraint to define a connectivity check for a path from a pin specified with the -from argument to a pin specified with the -to argument.

- test\_mode (optional): Use this constraint to specify the set of conditions, both pins and values, that when simulated, will force the circuit in test mode.

- define\_tag (optional): Use this constraint to define a named condition for application of certain stimulus at the top port or an internal node.

# **Operating Mode**

Scanshift, Capture, Power Ground, Define\_tag

# **Messages and Suggested Fix**

## Message 1

**[ERROR]** [constraint\_message\_tag: <value>] '<path\_type>' path(s) not found from '<from\_node\_name>' to '<to\_node\_count>' nodes under <simulation condition> within '<sequential\_depth>' sequential\_depth

## Arguments

To view the list of message arguments, click Arguments.

#### **Potential Issues**

The violation message appears if no valid path exists between the userspecified nodes.

#### **Consequences of Not Fixing**

Not fixing the violation may result in unsearchable expected path. This may impact the functionality of the design.

#### How to Debug and Fix

For more information on debugging and fixing the violation, click *How to Debug and Fix.*

#### Message 2

[ERROR] [constraint\_message\_tag: <value>] '<path\_type>' path(s) not found to '<to\_node\_name>' from '<from\_node\_count>' nodes under <simulation condition> within '<sequential\_depth>' sequential\_depth

#### Arguments

To view the list of message arguments, click Arguments.

#### **Potential Issues**

The violation message appears if no valid path exists between the userspecified nodes.

**NOTE:** This violation message is reported instead of Message 1, in case of '-from\_one\_of' field specified in 'require\_path' constraint.

#### **Consequences of Not Fixing**

Not fixing the violation may result in unsearchable expected path. This may impact the functionality of the design.

#### How to Debug and Fix

For more information on debugging and fixing the violation, click *How to Debug and Fix*.

#### Message 3

```

[ERROR] [constraint_message_tag: <value>] '<path_type>' path(s) not found from '<from_node_name>' to '<to_node_count>' nodes within '<sequential_depth>' sequential_depth

```

#### Arguments

To view the list of message arguments, click Arguments.

#### Potential Issues

The violation message appears if no valid path exists between the userspecified nodes.

**NOTE:** This violation message is reported instead of Message 1, when '-path\_type' is 'buffered' in 'require\_path' constraint.

#### **Consequences of Not Fixing**

Not fixing the violation may result in unsearchable expected path. This may impact the functionality of the design.

#### How to Debug and Fix

For more information on debugging and fixing the violation, click *How to Debug and Fix.*

#### Message 4

**[ERROR]** [constraint\_message\_tag: <value>] '<path\_type>' path(s) not found to '<to\_node\_name>' from '<from\_node\_count>' nodes within '<sequential\_depth>' sequential\_depth

#### Arguments

- Constraint tag value, <value>

- Expected path type, as specified by 'require\_path' constraint, <path\_type>

- Node name specified in the '-from' field of 'require\_path' constraint, <from\_node\_name>

- Node name specified in the '-to' field of 'require\_path' constraint, <to\_node\_name>

- No of '-to' nodes for which connectivity check failed from the specified 'from' node, <to\_node\_count>

- No of '-from' nodes from which connectivity check failed to the specified '-to' node, <from\_node\_count>

- Value specified by '-sequential\_depth' field of 'require\_path constraint, <sequential\_depth>

- Simulation condition specified in the 'require\_path' constraint, <simulation\_condition>

NOTE: The constraint tag value is prefixed to the violation message only if you specify the

-constraint\_message\_tag argument for the require\_path constraint.

#### **Potential Issues**

The violation message appears if no valid path exists between the userspecified nodes.

**NOTE:** This violation message is reported instead of Message 2, when '-path\_type' is 'buffered' in 'require\_path' constraint.

#### **Consequences of Not Fixing**

Not fixing the violation may result in unsearchable expected path. This may impact the functionality of the design.

#### How to Debug and Fix

Double-click the violation message to open the spreadsheet, which contains the list of all the violation messages. Click on a violation message in the spreadsheet to view the incremental schematic of the violation message. The incremental schematic displays the path specified in the violation message.

If endpoints are displayed start probing from either fan-out cone of from point or fan-in cone of to point to see why required path does not exist.

If the path from start point up to the instance which is blocking is displayed then analyze the text annotation date displayed to see why the path is blocked at the instance highlighted.

To fix the violation, see *Example Code and/or Schematic*.

#### Message 5

[ERROR] [constraint\_message\_tag: <value>] ' <no\_of\_paths>'

(<limit\_breached>) ' <path\_type>' path(s) found from

' <from\_node\_name> node under <simulation condition> within ' <

sequential\_depth >' sequential depth

#### Arguments

- Constraint tag value, <value>

- Expected path type, as specified by 'require\_path' constraint, <path\_type>

- Limit to the number of paths, <limit\_breached>

- Node name specified in the '-from' field of 'require\_path' constraint, <from\_node\_name>

- Simulation condition specified in the 'require\_path' constraint, <simulation\_condition>

- Value specified by '-sequential\_depth' field of 'require\_path constraint, <sequential\_depth>

#### **Potential Issues**

Specified number of paths are not present between user-specified nodes.

#### **Consequences of Not Fixing**

Not fixing the violation may result in unsearchable expected path. This may impact the functionality of the design.

#### How to Debug and Fix

Double-click the violation message to open the spreadsheet, which contains the list of all the violation messages. Click on a violation message in the spreadsheet to view the incremental schematic of the violation message. The incremental schematic displays the path specified in the violation message.

If endpoints are displayed start probing from either fan-out cone of from point or fan-in cone of to point to see why required path does not exist.

If the path from start point up to the instance which is blocking is displayed then analyze the text annotation date displayed to see why the path is blocked at the instance highlighted.

To fix the violation, see *Example Code and/or Schematic*.

## Message 6

**[WARNING]** [constraint\_message\_tag: <value>] min\_to\_paths('<min\_path\_value>') should have a value less than max\_to\_paths('<max\_path\_value>'), ignoring these values

#### Arguments

- Constraint tag value, <value>

- Minimum number of expected successful paths, <min\_path\_value>

- Maximum number of expected successful paths, <max\_path\_value>

#### Potential issues

The value specified is ignored.

#### How to debug and fix

Double-click the violation message to open the spreadsheet, which contains the list of all the violation messages. Click on a violation message in the spreadsheet to view the incremental schematic of the violation message. The incremental schematic displays the path specified in the violation message.

If endpoints are displayed start probing from either fan-out cone of from point or fan-in cone of to point to see why required path does not exist.

If the path from start point up to the instance which is blocking is displayed then analyze the text annotation date displayed to see why the path is blocked at the instance highlighted.

To fix the violation, review the constraint and modify to specify valid values.

## **Example Code and/or Schematic**

Consider the following example:

## Schematic highlight

Start and end point would be highlighted. (No topological connection) Path from start point till the place signal reached, would be highlighted in one color and from there to end point in different color. (Where path is blocked)

Path with the same phase in one color and invert phase in different color highlighted. This schematic is applicable only when the -invert or -noinvert argument is specified in the *require\_path* constraint.

## Default Severity Label

Error

## **Rule Group**

SoC

# Reports and Related Files

*dft\_connectivity\_check\_summary*.rpt: Reports the number of *require\_path* constraints passed and failed.

# Soc\_04

#### Show system state for a given tag.

#### When to Use

Use this rule to show the system state for each condition specified by the define tag constraint.

## Description

The Soc\_04 rule shows the simulation results for each condition specified by the define tag constraint.

The state of user-selected nodes, when a set of nodes are in a particular state, is checked. This is useful to verify that port requirements on one or more blocks in a design have required values when a set of nodes have particular values.

## Prerequisites

Specify the *define\_tag* constraint.

#### **Default Weight**

10

#### Language

Verilog, VHDL

#### Method

For each set of define\_tag conditions Simulate power, ground and the defined node/value pairs

## Parameter(s)

- dftShowWaveForm (optional): The default value is off. Set the value of the parameter to on to enable the generation of waveform corresponding to the rule message in the Waveform viewer of the SpyGlass Explorer.

- dftUseOffStateOfClockInClockPropagation: The default value of the parameter is on. Set the value of the parameter to off so that clock lines are kept at X during shift, capture, or atspeed mode simulation.

# Constraint(s)

*define\_tag* (optional): Use this constraint to define a named condition for application of certain stimulus at the top port or an internal node.

# **Operating Mode**

Define\_tag

# **Messages and Suggested Fix**

## Message 1

[INFO] Tag '<tag-name>' is displayed for design '<du-name>'

## Arguments

To view list of arguments, click Arguments.

## **Potential Issues**

Since this is an informational rule, there are no potential issues related to this violation message.

## Consequences of Not Fixing

Since this is an informational rule, there is no implicit impact of this violation message

## How to Debug and Fix

The Soc\_04 rule assists in debugging the violations reported by the Soc\_01, Soc\_01\_info, Soc\_02 and Soc\_02\_info rules. The Soc\_04 rule is an informative rule and requires no debug.

No fix is required as this is an informational rule.

## Message 2

[INFO] Tag '<tag name>\_\_as\_used\_in\_scan\_chain\_tracing\_\_' is displayed for design '<du-name>'

## Arguments

- Name of the tag, <tag-name>

- Name of the design unit, <du-name>

## **Potential Issues**

A violation message is displayed for those *define\_tag* tags that are used in *scan\_chain* to define scan enable condition (-scanenable field).

#### Consequences of Not Fixing

Since this is an informational rule, there is no implicit impact of this violation message

#### How to Debug and Fix

The Soc\_04 rule assists in debugging the violations reported by the Soc\_01, Soc\_01\_info, Soc\_02 and Soc\_02\_info rules. The Soc\_04 rule is an informative rule and requires no debug.

No fix is required as this is an informational rule.

## **Example Code and/or Schematic**

Currently Unavailable

## **Default Severity Label**

Info

## **Rule Group**

SoC Rules

## **Reports and Related Files**

No related reports or files.

# Soc\_07

## Checks the structure between the user-specified nodes

## When to Use

Use this rule when you want to use a specific structure.

# Description

The Soc\_07 rule checks whether the path all the -from nodes and at least one of the -from\_one\_of nodes to -to node have the same structure as specified in -type field of the *require\_structure* constraint. The Soc\_07 rule also allows functional buffers (1 input of OR/XOR gate is tied to 0, 1 input of AND is tied to 1). So, even if structure as specified in -type field acts as buffer, Soc\_07 considers them as valid objects on the path.

As an example of the rule's application, you can use this rule to run a check on memories. Memory-Controllers have PASS / FAIL status signals.

A GLOBAL-PASS is AND of all individual PASS signals as specified below:

require\_structure -from "BIST:: PASS" -to G\_PASS -structure and

A GLOBAL-FAIL is OR of all individual FAIL signals as specified below:

require\_structure -from "BIST::FAIL" -to G\_FAIL -structure or

Based on the above status, we may have 3 types of failures:

- Extra driver is specified in the from-node-list, which is not present in the combinational fanin cone of -to node. However, the violation message for the extra driver is not reported for nodes given through -from\_one\_of field, if at least one of them is found in the fan in cone of the -to node.

- Missing driver where a node is in the combinational fanin cone of tonode but is missing from the from-node-list.

- Incorrect GATE is found in the combinational cloud between from and to nodes.

# **Default Weight**

10

#### Language

Verilog, VHDL

## Parameter(s)

*dftUseOffStateOfClockInClockPropagation*: The default value of the parameter is on. Set the value of the parameter to off so that clock lines are kept at X during shift, capture, or atspeed mode simulation.

## Constraint(s)

*require\_structure* (mandatory): Use this constraint to define a structure check for all paths from source pins to destination pin.

## **Operating Mode**

None

## **Messages and Suggested Fix**

[WARNING] [constraint\_message\_tag: <value>] [Reason: <reason\_for\_vioaltion>]Path from point '<from\_node>' to point '<to-node>' is not of type '<structure>'

#### Arguments

- Constraint tag value, <value>

- One or combination of 'missing-driver', 'xtra-driver', incorrect-driver' may come as reason for violation, <reason\_for\_violation>

- Name of the source node, <from\_node>

- Name of the to destination node, <to\_node>

- Desired structure, <structure>

- **NOTE:** The constraint tag value is prefixed to the violation message only if you specify the -constraint\_message\_tag argument for the require\_structure constraint.

#### **Potential Issues**

The violation message appears if path between user-specified nodes is not user-specified.

#### **Consequences of Not Fixing**

Not fixing this violation may result in error in evaluations in the circuit.

## How to Debug and Fix

Double-click the violation message. The Incremental Schematic window highlights the path between points specified in -from and -to field of the *require\_structure* constraint.

To fix the violation, use user-specified structure only.

## **Example Code and/or Schematic**

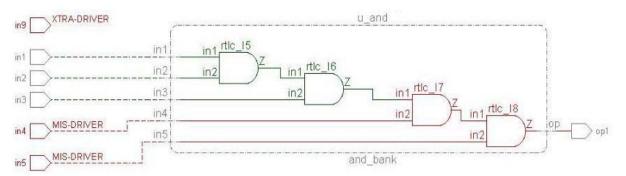

## Example 1

Consider the following SGDC declaration:

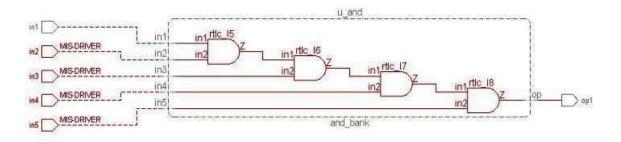

require\_structure -structure and -from in1 -to op1

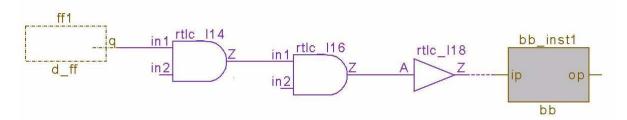

Now, consider the following figure illustrating the Soc\_07 rule violation because of a missing driver:

For the above example, the Soc\_07 rule reports the following violation message:

[Reason: missing-driver]Path from point 'in1' to point 'op1' is not of type 'and'

## Example 2

Consider the following SGDC declaration:

```

require_structure -structure and -from in1 in2 in3 in4 in5 in6 in7 in8 in9 -to op4

```

Consider the following figure illustrating the Soc\_07 rule violation because of an extra driver:

For the above example, the Soc\_07 rule reports the following violation message:

[Reason: xtra-driver]Path from point 'in9 in8 in7 in6 in5 in4 in3 in2 in1' to point 'op4' is not of type 'and'

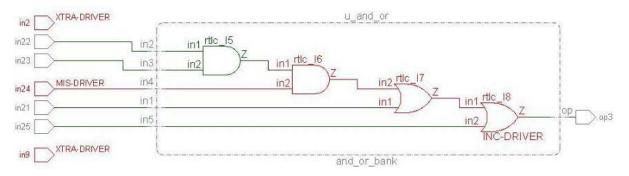

#### Example 3

Consider the following SGDC declaration:

```

require_structure -structure and -from in1 in2 in3 in9 -to op1

```

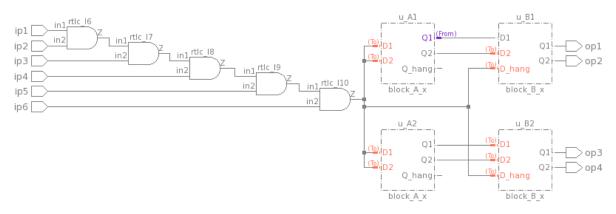

Consider the following figure illustrating the Soc\_07 rule violation because of extra and missing drivers:

For the above example, the Soc\_07 rule reports the following violation message:

[Reason: xtra-driver, missing-driver]Path from point 'in9 in3 in2 in1' to point 'op1' is not of type 'and'

## Example 4

Consider the following SGDC declaration:

```

require_structure -structure and -from in21 in22 in23 in25

-to op3

```

Consider the following figure illustrating the Soc\_07 rule violation because of an extra, missing, and incorrect drivers:

For the above example, the Soc\_07 rule reports the following violation message:

[Reason: xtra-driver, incorrect-driver, missing-driver]Path from point 'in9 in2 in25 in23 in22 in21' to point 'op3' is not of type 'and'

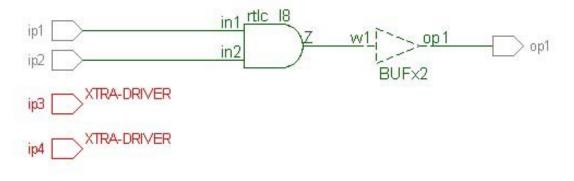

## Example 5

Consider the following SGDC declaration:

```

require_structure -from ip1 ip2 -from_one_of ip3 ip4 -to op1

-structure and

```

Now, consider the following figure illustrating the Soc\_07 rule violation because of using the -from\_one\_of and -structure fields of the require\_structure constraint simultaneously:

For the above example, the Soc\_07 rule reports the following violation message because none of the nodes specified using the -from\_one\_of field was found in the fanin of the -to node.

[Reason: xtra-driver]Path from point 'ip2 ip1, one of "ip4 ip3"' to point 'op1' is not of type 'and'

## **Default Severity Label**

Warning

## Rule Group

Soc

## **Reports and Related Files**

*dft\_connectivity\_check\_summary*.rpt: Reports the number of *require\_structure* constraints passed and failed.

# Soc\_08

## Checks the path between the user-specified nodes

## When to Use

Use this rule when you want to check the existence of a specific path.

# Description

The Soc\_08 rule checks if a path originating from the -from field to the -to field of the *require\_strict\_path* constraint exists in the design.

Default Weight

10

## Language

Verilog, VHDL

# Parameter(s)

- dftUseOffStateOfClockInClockPropagation: The default value of the parameter is on. Set the value of the parameter to off so that clock lines are kept at X during shift, capture, or atspeed mode simulation.

- dft\_allow\_path\_from\_enable\_to\_cgc\_clkout: The default value is off. Set the value of the parameter to on to allow a connectivity path from enable (data and test) to CGC clock-out pin.

- dft\_conn\_check\_allow\_trace: The default value is off. Set the value of the parameter to yes to allow combinational traversal through the asynchronous pins of a flip-flop while performing the checks for require path (require\_path constraint) or illegal path (illegal\_path constraint).

- dft\_conn\_check\_handle\_rtl\_negedge: Default value is off. Set the value of the parameter to yes to consider the input to the inverter, in front of the CP/CLR/PRE pin, as the start/end point of the connectivity check.

- dft\_require\_path\_fail\_limit: The default value is 10. Set the value of the parameter to 10. Set the value of the parameter to any natural number to controls the number of violations reported by the Soc\_08 rule for the require\_strict\_path constraint failure when either the -from\_one\_of or -to\_one\_of arguments of the require\_strict\_path constraint is specified.

- dft\_require\_path\_invalid\_limit: The default value is 10. Set the value of the parameter to any natural number to control the number of invalid path violations reported by the Soc\_08 rule for the require\_strict\_path constraint failure.

- dft\_require\_path\_pass\_limit: The default value is -1. Set the value of the parameter to any natural number to control the number of violations reported by the Soc\_08 rule for the require\_strict\_path constraint failure when either the -from\_one\_of or -to\_one\_of arguments of the require\_strict\_path constraint is specified.

- dft\_treat\_latches\_with\_X\_on\_enable\_as\_combinational\_for\_soc\_path\_checks: The default value is off. Set the value of the parameter to on to define the treatment of latches. That is, whether to consider them as combinational or sequential, where enable pin does not get either 0 or 1, when running Soc path check rules.

# Constraint(s)

- require\_strict\_path (mandatory): Use this constraint to define a connectivity check for a path from a pin specified with the -from argument to a pin specified with the -to argument.

- test\_mode (optional): Use this constraint to specify the set of conditions, both pins and values, that when simulated, will force the circuit in test mode.

- define\_tag (optional): Use this constraint to define a named condition for application of certain stimulus at the top port or an internal node.

## **Operating Mode**

Scanshift, Capture, Define\_tag, Power Ground

## **Messages and Suggested Fix**

#### Message 1

[INFO] [constraint\_message\_tag: <value>] Found valid path(s) from '<from-node>' to '<to-nodes-count>'desired nodes <mode-name>

#### Arguments

To view the list of arguments, click Arguments.

## **Potential Issues**

Since this is an informational message, there are no potential issues related to this message.

#### Consequences of Not Fixing

Since this is an informational message, there is no implicit impact of this violation message.

## How to Debug and Fix

No debug or fix is required as this is an informational message.

## Message 2

[WARNING] [constraint\_message\_tag: <value>] Found path from '<from-node>' to '<to-nodes-count>'undesired node <mode-name>

## Arguments

The node at which the traversal was stopped, <to-node>

To view the other arguments, click Arguments.

## **Potential Issues**

The violation is reported because a valid path to a design node, which was not specified in the -to field of the require\_strict\_path constraint, is found by SpyGlass.

## **Consequences of Not Fixing**

Not fixing this violation may result in unexpected results.

## How to Debug and Fix

Double-click the violation message to open the spreadsheet, which contains the list of all the violation messages. Click on a violation message in the spreadsheet to view the incremental schematic of the violation message. The incremental schematic displays the path specified in the violation message.

To fix the violation, verify the highlighted path. If the path is correct, add the <to-node> node in the -to field of the require\_strict\_path constraint in the SGDC file. However, if the path is not correct, specify any missing testmode constraint or check the design.

# Message 3

[WARNING] [constraint\_message\_tag: <value>] No Valid path(s)

from '<from-node>' to '<to-nodes-count>'desired nodes <modename>

#### Arguments

- Constraint tag value, <value>

- Source node from which the connectivity check is performed, <fromnode>

- Number of <to-nodes> at which the traversal was stopped, <tonodes-count>

Please note that this list may or may not be present in the -to field of the require strict path constraint.

- **NOTE:** The constraint tag value is prefixed to the violation message only if you specify the -constraint\_message\_tag argument for the require\_strict\_path constraint.

- The mode name, <mode-name>

The available mode names are specified in the following table:

| Specified Field of the<br>require_strict_path Constraint | Corresponding <mode-name></mode-name> |

|----------------------------------------------------------|---------------------------------------|

| -use_shift                                               | Shift                                 |

| -use_capture                                             | Capture                               |

| -use_captureATspeed                                      | Capture (atspeed)                     |

| -tag                                                     | Define_tag                            |

| If none of the above fields is specified                 | Power Ground                          |

#### **Potential Issues**

The violation message appears if no valid path exists between the user-specified nodes.

#### **Consequences of Not Fixing**

Not fixing this violation may impact the functionality of the design.

#### How to Debug and Fix