# SpyGlass<sup>®</sup> CDC Submethodology (for GuideWare 2017.12)

Version N-2017.12-SP2, June 2018

### **Copyright Notice and Proprietary Information**

©2018 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc. 690 E. Middlefield Road Mountain View, CA 94043 www.synopsys.com

### **Report an Error**

The SpyGlass Technical Publications team welcomes your feedback and suggestions on this publication. Please provide specific feedback and, if possible, attach a snapshot. Send your feedback to *spyglass\_support@synopsys.com*.

# Contents

| Introduction to SpyGlass CDC Methodology                                        | 7    |

|---------------------------------------------------------------------------------|------|

| Goals of SpyGlass CDC Methodology                                               | 9    |

| Tool and Methodology Version                                                    |      |

| References                                                                      | 11   |

| SpyGlass CDC Terminologies                                                      | 12   |

| The CDC Issues                                                                  | 13   |

| Metastability                                                                   | 14   |

| Data Hold in Fast-to-Slow Crossings                                             | 21   |

| Data Correlation and Race Conditions                                            |      |

| Complex Synchronizers                                                           |      |

| Issues Related to Reset Synchronization                                         |      |

|                                                                                 |      |

| Using SpyGlass CDC Methodology to Solve CDC Problem                             | ns27 |

| SpyGlass CDC Methodology Flow                                                   |      |

| Creating SpyGlass CDC Setup                                                     |      |

| Writing Constraints                                                             |      |

| Translating SDC Commands to SGDC Commands                                       |      |

| Predicting Constraints                                                          |      |

| Running the cdc_setup Goal<br>Generating Block-Level Constraints from SoC Level |      |

| Generating Clocks                                                               |      |

| Verifying SpyGlass CDC Setup                                                    |      |

| Constraining Clock Trees                                                        |      |

| Fixing Setup-Related Sanity Checks                                              |      |

| Performing Clocks and Reset Integrity Checks                                    |      |

| Performing Block-Level CDC Verification                                         | 34   |

| Focusing on Certain Violations on Priority Basis                                |      |

| Reducing Noise                                                                  |      |

| Dealing with Functional Checks                                                  |      |

| Waiving Violations                                                              |      |

| Performing SoC-Level CDC Verification                                           |      |

| Signing-Off SpyGlass CDC Verification                                           |      |

| SpyGlass CDC Hierarchical Verification Flow                     | 49 |

|-----------------------------------------------------------------|----|

| Identifying the Blocks to Abstract in SpyGlass CDC              |    |

| Generating Abstract View in SpyGlass CDC                        | 52 |

| Quality of Abstract View                                        |    |

| Performing Abstract View Validation in SpyGlass CDC             | 53 |

| Approach to Fix Violations During Abstract View Validation      | 54 |

| Examples of Fixing Violations During Abstract View Validation   |    |

| Points to be Considered in the Hierarchical CDC Flow            | 55 |

| Loss of Information While Generating the Abstract View          | 55 |

| Functional checks in an abstraction-based bottom-up methodology | 56 |

| Design Styles and Management                                    |    |

| Limitations of the Hierarchical CDC Verification Flow           | 58 |

| Recommended Guidelines to Perform SpyGlass CDC Verification     | 60 |

|                                                                 |    |

| Appendix                                                        | 61 |

| Rules of the cdc_setup Goal                                     | 62 |

| Rules of the clock_reset_integrity Goal                         |    |

| Rules in the cdc_verify Goal                                    |    |

| — ·                                                             |    |

| Rules in the cdc_abstract_validate Goal                         |    |

| The Setup Manager of SpyGlass CDC                               | 69 |

| Invoking the Setup Manager                                      | 71 |

Limitations of the Setup Manager......71

# Introduction to SpyGlass CDC Methodology

Clocks that are asynchronous with respect to each other may reach different flip-flops at slightly different times in each cycle. This timing uncertainty may cause setup and hold-time violations randomly in the design resulting in functional failure in an SoC.

Such issues cannot be detected by using traditional verification methods, such as simulation and static timing analysis. You can detect them by using static clock-domain-crossing analysis and verification of SpyGlass CDC solution.

SpyGlass CDC solution enables you to detect clock-domain crossings at the RTL level and ensure that proper synchronization is added in the circuit.

This document introduces a methodology that you can use to verify clock-domain crossing (CDC) issues in your design by using the SpyGlass® tool suite. The document is useful for novice and advanced users of SpyGlass. Advanced users can proceed directly to the relevant sections of the document.

The following table describes the sections covered in this document:

| Торіс                                                         | Information                                                                                                                                                                                                                |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The CDC Issues                                                | Describes basic CDC problems, such as metastability and complex synchronizers.                                                                                                                                             |

| Using SpyGlass<br>CDC Methodology<br>to Solve CDC<br>Problems | <ul> <li>Describes a step-by-step solution towards a SpyGlass CDC-clean design by using any of the following flows:</li> <li>SpyGlass CDC Methodology Flow</li> <li>SpyGlass CDC Hierarchical Verification Flow</li> </ul> |

# Goals of SpyGlass CDC Methodology

SpyGlass CDC methodology is integrated within GuideWare for different field of use. Below is a summary of goals (of SpyGlass CDC solution) deployed in various field of use of GuideWare. The set of goals (of SpyGlass CDC solution) used for each GuideWare stage is the same.

| SpyGlass CDC solution: Block |   |           |                 |                           |                   |            |              |

|------------------------------|---|-----------|-----------------|---------------------------|-------------------|------------|--------------|

|                              |   |           | (               | Goals                     |                   |            |              |

| GuideWare<br>Stage           |   | cdc_setup | cdc_setup_check | clock_reset_integr<br>ity | cdc_verify_struct | cdc_verify | cdc_abstract |

| initial_rtl                  | 0 | М         | М               | М                         | -                 | -          |              |

| rtl_handoff                  | 0 | М         | М               | М                         | М                 | М          |              |

| netlist_handoff              | 0 | М         | М               | М                         | М                 | М          |              |

| SpyGlass CDC solution: SoC |       |           |              |                 |                           |                           |                       |            |              |

|----------------------------|-------|-----------|--------------|-----------------|---------------------------|---------------------------|-----------------------|------------|--------------|

|                            | Goals |           |              |                 |                           |                           |                       |            |              |

| GuideWare<br>Stage         |       | cdc_setup | cdc_top_down | cdc_setup_check | clock_reset_inte<br>grity | cdc_abstract_val<br>idate | cdc_verify_struc<br>t | cdc_verify | cdc_abstract |

| initial_rtl                | 0     | -         | М            | М               | (                         | C                         | М                     | -          | -            |

| rtl_handoff                | 0     | 0         | М            | М               | (                         | C                         | М                     | -          | М            |

| netlist_handoff            | 0     | 0         | М            | М               | (                         | C                         | М                     | -          | М            |

| layout_handoff             | 0     | 0         | М            | М               | (                         | C                         | М                     | -          | -            |

**NOTE:** *M* means mandatory and *O* means optional.

In addition to the static SpyGlass CDC verification described here, SpyGlass CDC solution can be used to perform dynamic SpyGlass CDC verification. For dynamic SpyGlass CDC verification, SpyGlass CDC solution can generate simulation directives using Ac\_meta01 rule that will inject metastability errors during simulation using your own testbench. These directives may cause additional simulation mismatches due to the effect of metastability.

### **Tool** and Methodology Version

- SpyGlass Version: Version N-2017.12-SP2

- GuideWare Version: 2017.12

## References

- SpyGlass CDC Rules Reference Guide

- SpyGlass Explorer User Guide

# **SpyGlass CDC Terminologies**

The terminologies used in SpyGlass CDC are defined in the following table:

| Terminology                       | Description                                                                                                                                                                                                                               |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock domain                      | Refers to the clocks that have a constant phase relationship with each other.                                                                                                                                                             |

|                                   | Typically, a clock, its inverted form, and its divided form is<br>considered to be in the same domain. Divided forms have a<br>constant phase relationship until the division ratios have a<br>common factor.                             |

|                                   | Divide-by-2 and divide-by-4 have constant phasing but divide-by-3 and divide-by-5 do not have constant phasing.                                                                                                                           |

| CDC<br>(Clock Domain<br>Crossing) | Refers to the path connecting a sequential element, flip-flop,<br>primary input, or black box controlled by one clock domain to<br>another sequential element, flip-flop, primary input, or black<br>box clocked by another clock domain. |

| Synchronizer                      | Refers to the part of a design that transfers signal values across clock domains                                                                                                                                                          |

| Quasi-static                      | Refers to flip-flops that take constant values in a design.<br>They may change values during setup and initialization of the<br>design, or may change value when a block powers on or<br>power off.                                       |

|                                   | Often, quasi-static flip-flops do not require synchronizers even if they are involved in clock domain crossings.                                                                                                                          |

| LCM                               | Refers to the least common multiple to identify a common clock period for a design with multiple clocks of different periods.                                                                                                             |

| Correlated<br>Signals             | These are the signals whose combined values are used<br>in the design. An example of such signals is state<br>vector signals.                                                                                                             |

# The CDC Issues

Clocks that are synchronous with respect to each other are known as same domain clocks, and clocks that are asynchronous to each other are known as different domain clocks.

Edges of clocks coming from the same clock domain are always aligned for all registers in the design and for all time throughout design run. As a result, if setup and hold time for a flip-flop input is considered, there is no risk in capturing the data of the flip-flop throughout the design.

However, clocks from different domains may reach different flip-flops at different times in each cycle during design run. This timing uncertainty may cause random setup and hold-time violations. Such problems may result in the following CDC issues:

- Metastability

- Data Hold in Fast-to-Slow Crossings

- Data Correlation and Race Conditions

- Complex Synchronizers

- Issues Related to Reset Synchronization

### Metastability

Metastability is the design problem in which metastable values are created and propagated due to setup and hold-time issues in an asynchronous crossing.

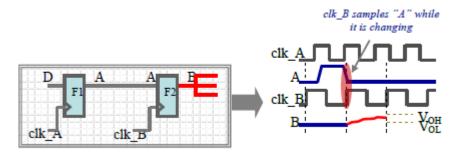

The following figure shows an example of such an issue:

FIGURE 1. Metastability Issue

In the above figure, the metastable waveform generated at B is subject to interpretation by each branch in the fan-out of B.

One gate in a fan-out can perceive the metastable wave as the logical value 1 while another fan-out perceives the same net as 0. This free interpretation causes functional failure in the design.

To remove metastability, use the following approaches:

Control signal synchronization

Control signals crossing clock domains are typically synchronized by using multi-flop synchronizers. In such cases, multiple stages of flip-flops transform the metastable values to a *cleaner* 0 or 1 before it is passed to a downstream logic.

Data signal synchronization

Data signals are synchronized by using enable techniques where the data is first stabilized on the crossing path and then the destination flip-flop is enabled to capture the stable data (so the setup and hold time is not violated).

Traditionally, a clock domain crossing is seen as a path from one memory element to another. However, designers typically design interfaces that

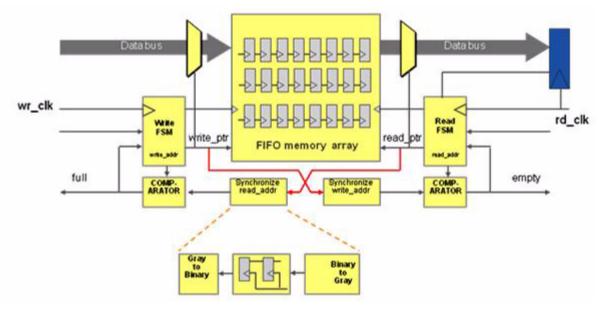

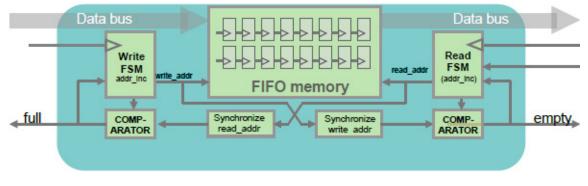

involve data, address, and control lines implementing complex synchronization protocols. For example, *Figure 2* illustrates a common FIFO where data is stored and read from a memory (data), pointers are designed to access the memory (address) for either read or write, and finally control logic that computes empty/full flags (control) is designed to ensure coherency and prevent metastability.

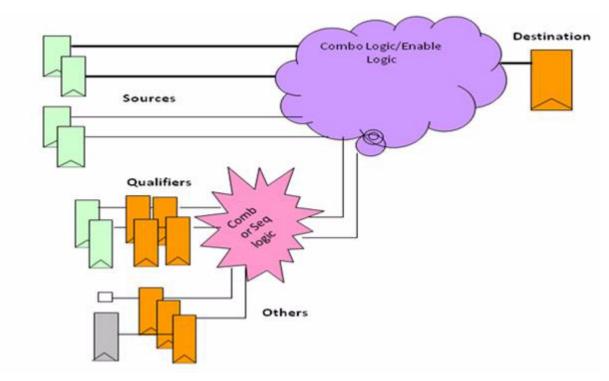

The key concept in common data synchronization techniques is a link between the sender and receiver of the data which ensures that the data is not captured while it is changing as this will cause an asynchronous event to propagate which can cause metastability. Based on this observation, an asynchronous interface is composed of a set of source signals, a destination signal (can be a bus), and a set of control logic. At least part of the control logic is responsible for proper synchronization. *Figure 3* illustrates a generic data crossing and signals involved in the synchronization.

FIGURE 3. Generic Data Crossing

The following signals are typically involved in a crossing:

- Destination of the crossing: Single-bit or multi-bit signal receiving data from one or multiple domains

- Source of the crossing: Data, Address, Control signals crossing clock domain without being flip-flopped in the destination domain. There can be multiple sets of sources from different domain crossing to the destination

- Qualifier: A control signal, typically from the source domain synchronized in the destination domain (typically using multi-flop synchronization technique) responsible for ensuring that the source is stable when captured by the destination

Signals from the destination domain: These signals are used as a control or for data computation/transformation purposes needed for the design.

Such signals are typically not important for synchronization verification, however, it is not a good idea to perform complex computation, or bring complex control logic on a crossing. Increased combinational logic on a crossing increases the risk of asynchronous glitch, especially after synthesis and optimization. We recommend performing data transformation/computation in the source domain or in the destination domain and keeping the asynchronous interface very simple

**NOTE:** Some custom interfaces such as source synchronous interfaces where the source is itself generated synchronously to the destination may not comply with the common synchronization techniques described here. Such structures are relatively rare and may require custom verification approaches.

As is implied by such an interface, the synchronization protocol must ensure that the data is stable when the qualifier is asserted to trigger data capture. This is a functional requirement that cannot be validated by looking at a design structure alone.

Furthermore, the above functional requirement only ensures that the source will not violate timing that can cause metastability. If any combinational logic on the crossing glitches, it may cause either metastability or generation of an undesired pulse.

SpyGlass CDC Verification performs a fast structural analysis that identifies elements of synchronization that indicates user intent to synchronize the crossing in order to prevent metastability as well as glitch issues.

SpyGlass CDC verification solution relies on the following concepts to declare a crossing as synchronized:

- Presence of qualifier signals: One or more signals coming from the source domain and synchronized to the destination using multi-flop synchronizer or a user-specified synchronizer cell. Qualifiers may be present beyond sequential logic such as a receiver state machine.

- **NOTE:** Synchronous resets may have all characteristics of a qualifier. They can be signals generated in a source domain, synchronized in a destination domain, and even gating the data capture into the destination. It is very important to define synchronous resets for SpyGlass CDC solution to avoid false positives. As stated above, functional verification must complement the structural verification to guarantee synchronization correctness. Indeed, although synchronous resets have full appearance of a qualifier they will fail functional data/enable or data-hold checks.

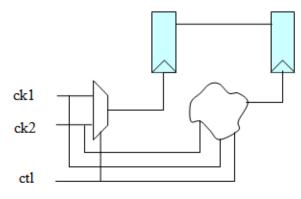

Gating mechanism: The qualifier must converge with the source in order to block the transfer when the source is being set up. SpyGlass CDC solution accepts common gating mechanisms such as AND and MUX synchronizers. An XOR gate is not considered as an acceptable gating mechanism as it allows asynchronous transfer regardless of the value of a qualifier feeding the gate.

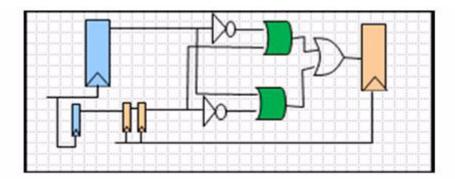

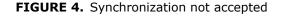

Furthermore, to avoid glitches, re-convergences are allowed only before the crossing is gated. Any re-convergence of the same asynchronous source after it is gated is prone to glitch and is not accepted. This includes cases where each branch of the re-convergence is synchronized. *Figure 4* illustrates a re-convergence of the source, although each path is gated by a qualifier, the crossing is not considered as synchronized based on a pessimistic assumption that the reconvergence can produce a glitch. Indeed, the logic in this figure represents a XOR and this crossing must not be considered as a synchronized crossing.

If source re-convergences are synchronized after they converge, then there is no glitch risk and the crossing is considered as synchronized. Such structures are considered as properly synchronized.

Note that there might be properly synchronized crossings where reconvergences exist on each branch of the crossing. However, such complex logic on a crossing is a risky design style that can cause glitches, especially after optimization and synthesis transformations. Due to the pessimistic nature of the analysis, such synchronized crossings are not considered as synchronized.

In case a data is found to be unsynchronized, it is important to understand the nature of the failure and the way to fix it. Following are possible reasons for synchronization failure:

- Lack of a qualifier: No qualifier converges with the crossing. This may be due to the presence of an unsynchronized control signal that is intended to qualify a crossing.

- Invalid gating of the crossing with a valid qualifier: This happens for example when the crossing and a qualifier converges on a XOR gate.

- A source diverges to multiple paths that are synchronized separately (refer to *Figure 3*)

- A source converges with the qualifier before the qualifier feeds the synchronizing gate

- Two sources from different domains converge before they are synchronized

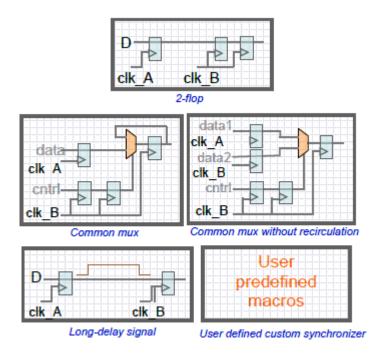

Some simple examples of control and data synchronizers are shown in *Figure 5*:

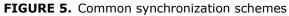

## **Data Hold in Fast-to-Slow Crossings**

This issue appears when a short pulse generated in a fast clock domain is fed in a slow clock domain. In such cases, short signals may miss the active edge of the slow clock domain and they are not captured in the destination.

The following figure shows the data hold problem in fast-to-slow crossings:

FIGURE 6. Example of Data Hold in Fast-to-Slow Crossings

To fix such issues, use the following approaches:

Use a custom circuit to extend the pulse for at least one complete cycle of the slow destination clock.

You must verify all the fast-to-slow crossings and ensure that such extenders exist and no short pulse is generated in the destination.

In case of enabled flip-flops involved in a crossing, ensure that the data is stable before the enable is asserted and the data does not change when the enable is on.

## **Data Correlation and Race Conditions**

If a source remains stable for long, its value is transferred to the destination. However, if the design has metastability issues, this transfer may not happen immediately. This can cause problems for *Correlated Signals* such that one or more signals are deferred relative to others.

This results in loss of correlation, which results in an unknown state at destination, thereby causing functional failure.

The following figure shows the example of such problem:

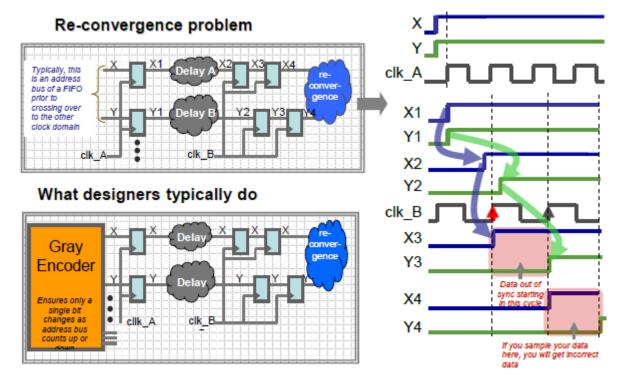

**FIGURE 7.** The re-convergence problem and a typical solution using gray coding

To fix this problem, introduce a gray encoder, which ensures that only a single bit is changed at a time.

You must ensure that *Correlated Signals* are gray encoded before they cross

clock domains. You can identify such signals where independent signals are converging and are used in the same combinational logic, or when a bus is used as a state vector or a memory pointer.

# **Complex Synchronizers**

FIFO mechanisms are often used to transfer data from one domain to another.

The following figure shows a FIFO synchronizer architecture:

#### FIGURE 8. FIFO synchronization scheme

For proper data transfer, it is important that the full and empty flags are generated on time and are not delayed or corrupted due to the pointers crossing clock domains. It is also important that the read and write FSMs make use of the full and empty flags to prevent writing into a full FIFO or reading from an empty FIFO.

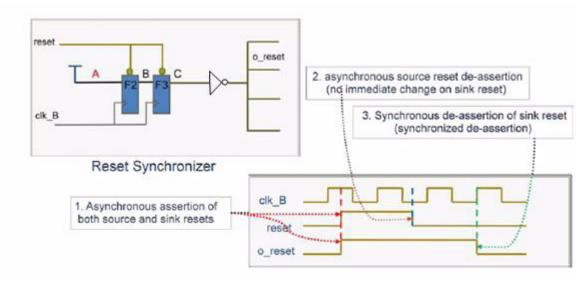

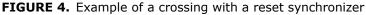

## **Issues Related to Reset Synchronization**

Reset synchronizers are especially built to avoid metastability while deasserting a reset signal. Such synchronizers must be verified for both metastability and functionality to avoid reset failures.

The following figure shows the example of reset synchronization:

FIGURE 9. Reset Synchronization

Issues Related to Reset Synchronization

# Using SpyGlass CDC Methodology to Solve CDC Problems

This section provides a step-by-step solution to make an SoC free from CDC issues by using any of the following flows:

- SpyGlass CDC Methodology Flow

- SpyGlass CDC Hierarchical Verification Flow

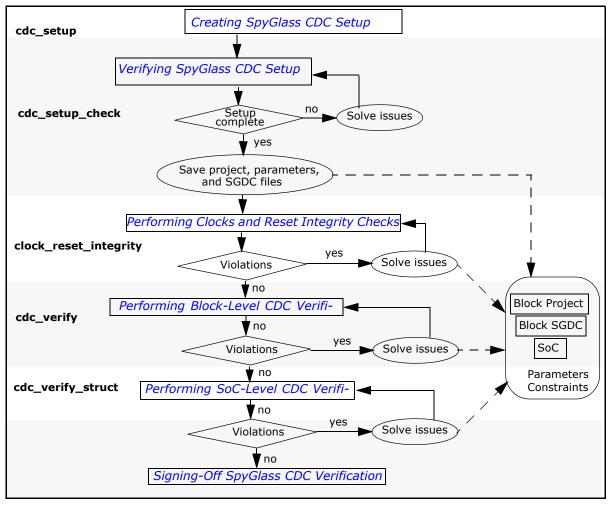

# SpyGlass CDC Methodology Flow

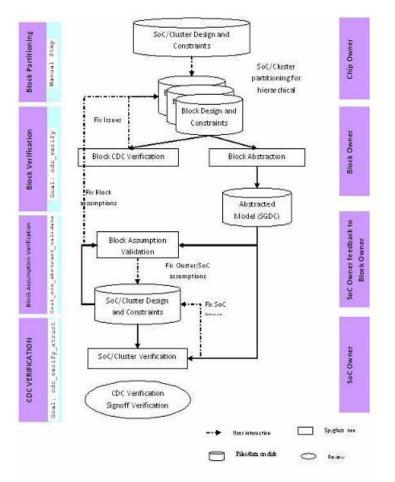

The following figure illustrates this flow to achieve a SpyGlass CDC clean SoC:

FIGURE 1. The SpyGlass CDC Methodology Flow

The following table shows the stages and their corresponding goals to achieve a SpyGlass CDC-clean design while using this flow:

| Stage                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Goals                 |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Creating SpyGlass CDC Setup                     | Specify constraints, parameters, and<br>other design components required for<br>accurate and complete SpyGlass CDC<br>verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cdc_setup             |

| Verifying SpyGlass CDC Setup                    | Check for the correctness and completeness of the setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | cdc_setup_check       |

| Performing Clocks and Reset<br>Integrity Checks | Fix clock and reset integrity problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | clock_reset_integrity |

| Performing Block-Level CDC<br>Verification      | <ul> <li>Fix block-level violations to make the block SpyGlass CDC clean. This stage involves the following tasks:</li> <li>Fixing Ac_sync_group Rule Violations</li> <li>Fixing Violations Related to Convergence</li> <li>Fixing Violations Related to Glitches</li> <li>Fixing Violations for Data Hold Checks</li> <li>Fixing Data Hold Issues in Synchronized Data Crossings</li> <li>Fixing Violations Related to Data Correlation and Race Conditions</li> <li>Fixing Violations Related to Reset Synchronization and Deassertion</li> <li>Fixing Violations Related to FIFO Recognition and Verification</li> </ul> | cdc_verify            |

| Performing SoC-Level CDC<br>Verification        | Verify the SoC using the verified blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | cdc_verify_struct     |

| Signing-Off SpyGlass CDC<br>Verification        | View reports and sign-off SpyGlass<br>CDC Verification on the SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                     |

### **Creating SpyGlass CDC Setup**

In this stage, you specify constraints, parameters, and other design components required for accurate and complete SpyGlass CDC verification.

Create a setup in the following ways:

Writing Constraints

SpyGlass CDC Methodology Flow

- Translating SDC Commands to SGDC Commands

- Predicting Constraints

- Running the cdc\_setup Goal

- Generating Block-Level Constraints from SoC Level

- Generating Clocks

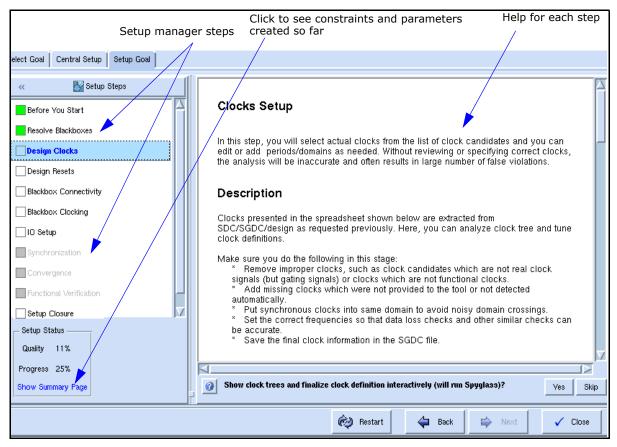

**NOTE:** You can also perform a setup by using The Setup Manager of SpyGlass CDC.

### **Writing Constraints**

Define constraints in an SGDC file if you have knowledge of block constraints.

### **Translating SDC Commands to SGDC Commands**

Use the sdc2sgdc project file command to translate block-level SDC commands to their corresponding SGDC constraints.

#### **Predicting Constraints**

Run the *cdc\_setup\_check* goal to generate constraints. The *Clock\_info15* rule of this goal generates constraints.

You must review these constraints before using them during SpyGlass CDC verification.

### Running the cdc\_setup Goal

Run the *cdc\_setup* goal to generate clocks (*clock* constraint) and resets (*reset* constraint) in a design.

After running this goal:

- Understand the design-clocks architecture by checking the reported clocks and resets.

- Resolve the clocks of black boxes by specifying a path through the black boxes by using the *assume\_path* constraint.

- Copy the *autoclocks.sgdc* and *autoresets.sgdc* in a new constraint file and edit the clocks and resets to provide valid clock/reset sources. Remove all the non clocks and non resets from the file.

- Provide the set\_case\_analysis constraint to add the known case-analysis values under which you want to perform SpyGlass CDC analysis.

### **Generating Block-Level Constraints from SoC Level**

You generate block-level constraints from the SoC-level constraints in the *SpyGlass CDC Hierarchical Verification Flow*.

Run the *cdc\_top\_down* goal to generate block-level constraints.

Note that using the generated block-level constraints for *Generating Abstract View in SpyGlass CDC* without *Performing Block-Level CDC Verification* may mask design bugs. For example, if a top module propagates to the P pin (of the A domain) of a block, you must verify that the P pin is feeding flip-flops in the A domain within the block or it is synchronized to another domain in which the pin is used.

SpyGlass CDC solution can also generate a block's peripheral domain information from within a block relying on the flip-flops interacting with these pins. For details, refer to the documentation of the rule Clock\_info15 in SpyGlass CDC Rules Reference Guide.

#### **Generating Clocks**

You can specify derived clocks or generated clock by using the generated\_clock constraint. These are the clocks that traverse from the output (hierarchical pin or net) of sequential elements.

To enable SpyGlass consider this constraint, set the enable\_generated\_clocks parameter to yes. When you set this parameter to yes, the following occurs:

- The specified generated\_clock constraints are considered during SpyGlass analysis.

- The derived clock information is generated in the form of generated\_clock constraints in the generated\_clocks.sgdc and cdc\_setup\_generated\_clocks.sgdc files.

This happens when the use\_inferred\_clocks parameter is set to yes.

### Verifying SpyGlass CDC Setup

After *Creating SpyGlass CDC Setup*, run the *cdc\_setup\_check* goal to correctness and completeness of the setup.

Fix all violations reported in this stage to avoid false violations in later stages. For example, you must ensure the following:

- All flip-flops are receiving a clock.

- set\_case\_analysis is properly defined so that multiple clocks do not control the same flip-flop. See Specifying set\_case\_analysis.

- Multiple clocks are not defined on the same clock path.

- Periods, edges, and domains are defined properly for clocks.

### **Constraining Clock Trees**

Constraint clock tree by:

- Constraining Clock Nets

- Specifying set\_case\_analysis

#### **Constraining Clock Nets**

Check the *Clock\_info03a* violations to locate the clock-tree parts to which top-level clocks do not reach. This occurs because of:

- Missing *clock* constraints in an SGDC file.

- Presence of black boxes through which a clock cannot propagate.

Black boxes appear because their structural information is missing or they have incorrect case analysis settings.

#### Specifying set\_case\_analysis

MUXes in clock trees use different clocks for different operating modes of the design. Configure MUXes by setting an operating mode by applying the *set\_case\_analysis* constraint on the MUX select pin.

#### **Consequences of Not Configuring MUXes**

Consider the scenario in the following figure:

FIGURE 2. Configuring the MUX

In the above scenario, if you do not configure the MUX by applying *set\_case\_analysis* on its select pin, multiple clocks may drive the same flip-flop. As a result, SpyGlass may infer the path between these flip-flops as asynchronous crossings even if these paths are synchronous. This results in false unsynchronized violations, which results in noise and more time for CDC verification closure.

#### **Fixing Violations for Non Configured MUXes**

Check for the *Clock\_info05* violations that report cases where you should define *set\_case\_analysis* on the MUX select pin.

Refer to the *Clock Setup* window that shows MUXes involved in clock paths from where you can interactively define a value for MUX selects.

### **Fixing Setup-Related Sanity Checks**

The setup verification performs basic sanity checks on the constraints specified in an SGDC file. These checks are always run to check for design-object existence and constraints correctness.

You can identify the violations of these checks with the  $SGDC_{}$  prefix in their names.

For information on these checks, refer to SpyGlass CDC Rules Reference Guide.

### **Performing Clocks and Reset Integrity Checks**

Run the *clock\_reset\_integrity* goal to fix clock and reset integrity problems.

This step ensures that clocks and resets are properly defined, and they are free of glitches, race conditions, and other hazards.

If you do not have the information about clocks and resets, you must run the setup. For details, see *Creating SpyGlass CDC Setup*.

### **Performing Block-Level CDC Verification**

Run the *cdc\_verify* goal to perform SpyGlass CDC verification at the block level.

This step uses all the information gathered while *Creating SpyGlass CDC Setup* and *Performing Clocks and Reset Integrity Checks* to perform SpyGlass CDC verification at block level.

This section covers the following topics:

- Focusing on Certain Violations on Priority Basis

- Reducing Noise

- Dealing with Functional Checks

- Waiving Violations

### Focusing on Certain Violations on Priority Basis

You may initially see a large number of reported CDC issues. It is important to approach them in a systematic way. This enables you to quickly reach to a handful of issues that you may need to consider.

The issues listed in the following sections cover the majority of important violations you should fix on priority:

- Fixing Ac\_sync\_group Rule Violations

- Fixing Violations Related to Convergence

- Fixing Violations Related to Glitches

- Fixing Violations for Data Hold Checks

- Fixing Data Hold Issues in Synchronized Data Crossings

- Fixing Violations Related to Data Correlation and Race Conditions

- Fixing Violations Related to Reset Synchronization and Deassertion

- Fixing Violations Related to FIFO Recognition and Verification

#### Fixing Ac\_sync\_group Rule Violations

This group of rules performs an architectural design analysis and presents an architectural view of design crossings.

You must fix the following violations of this group first before fixing the other violations:

- Ac\_unsync01 rule violations: These violations report scalar unsynchronized crossings. Such crossings act as control signals that synchronize complex data crossings.

- *Ac\_unsync02* rule violations: These violations report data crossings where no valid synchronization is found.

Run SpyGlass again with newly added constraints and verify that all *Ac\_unsync01* and *Ac\_unsync02* violations are fixed.

#### **Debugging Ac\_unsync Violations**

Use the following pointers to debug and fix such violations:

Open the spreadsheet to view all the violations of a rule. Look for common reasons or common sources in the spreadsheet.

Use filtering and sorting in the spreadsheet view to isolate common factors between violations. If you are using a naming methodology for static signals, filter by source name in the spreadsheet.

- Open the Incremental Schematic to view the cause for unsynchronized crossings. Check for the reason for such crossings in the violation message or spreadsheet.

- Check for the presence of qualifiers or potential qualifiers for a crossing.

- Filter violations by using the cdc\_false\_path constraint.

- Specify output net names for source and destination flip-flops.

- Check for mode or control-status registers that are static or quasi-static.

- Do not waive such violations. Use the <u>cdc\_false\_path</u> constraint instead to filter certain unsynchronized crossings in a design.

Note that the violations of the other rules that honor this constraint may get filtered due to this constraint specification.

#### False Ac\_unsync Violations

If the *clock* and *set\_case\_analysis* constraints are not properly defined during setup, you may see false *Ac\_unsync01* and *Ac\_unsync02* violations. For information on specifying these constraints during setup, see *Constraining Clock Trees*.

Such violations also appear due to configuration registers and other quasistatic signals need not to be synchronized. Section Noise Reduction describes various tools SpyGlass provides to reduce false violations and find real synchronization bugs faster.

#### **Conditions for an Unsynchronized Crossing**

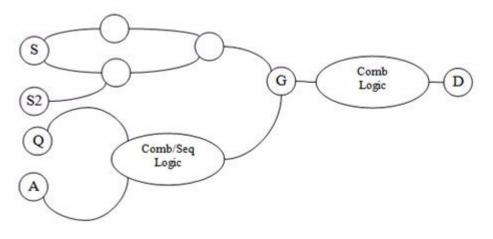

Consider the following figure:

FIGURE 3. Requirements for a synchronized crossing

In the above figure, a crossing is considered as unsynchronized if one of the following conditions is false for the source S:

- The Q qualifier whose source domain is the same as that of S exists and converges with S on the G gate.

- The type of the G gate is consistent with the type specified by the enable\_and\_sync, enable\_mux\_sync, and enable\_clock\_gate\_sync parameters.

- If S fans out to multiple gates, all the fan-out points must converge before G. In *Figure 3*, the two divergent paths from S converge before G, so this condition is met.

- The input of the synchronizing gate G that is driven by Q is not driven by another source of the crossing. In *Figure 3*, A should not be the source for the crossing. Flip-flops in the domain of the destination are allowed.

- If another source S2 converges with S before G, S2 must be in the same domain as that of S.

- The path from Q to G is considered based on the value of the enable delayed qualifier parameter.

#### **Declaring Synchronous Resets**

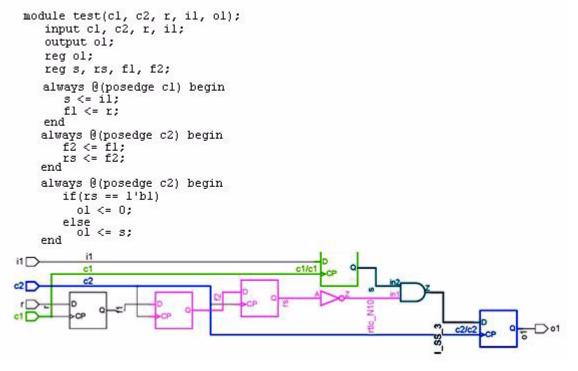

Consider the following figure:

In the above figure, the source s is reported as synchronized with the qualifier rs.

By looking at the Verilog description, it is clear that rs is the output of a reset synchronizer. Since the user missed to declare the input r as a reset, rs is considered as a qualifier.

To avoid such issues, declare all synchronous resets in the SGDC file to avoid considering their reset synchronizers as qualifier. Therefore, specify the following constraint to fix the issue in the above example:

```

reset -name r -sync

```

#### **Fixing Violations Related to Convergence**

Check for the Ac\_conv01, Ac\_conv02, Ac\_conv03, Ac\_conv04, and

Ac\_conv05 violations.

Convergence issues can occur when multiple signals cross from one domain to another but they are separately synchronized.

#### **Fixing Violations Related to Glitches**

Check for the *Ac\_glitch*\* or *Clock\_glitch*\* violations.

These rules report glitch-prone logic that can lead to problems similar to synchronization issues.

#### **Fixing Violations for Data Hold Checks**

Check for the Ac\_cdc01 violations.

Such violations indicate potential problems in signals or data crossing typically from a fast clock domain to a slower clock domain where data sent may have already changed by the time the capturing clock arrives.

The *Dealing with Functional Checks* section provides further detail on how to debug such functional checks.

#### Fixing Data Hold Issues in Synchronized Data Crossings

Check for the *Ac\_datahold01a* violations.

Such violations report clock domain crossings where data can be unstable while the enable is active. For every data change, the enable should be activated to capture the new data and should be deactivated before the next data is loaded.

The *Dealing with Functional Checks* section provides further detail on how to debug such functional checks.

#### **Fixing Violations Related to Data Correlation and Race Conditions**

Check for gray-code violations, such as *Ac\_cdc08*, *Ac\_conv01*, and *Ac\_conv02*.

Convergence of signals, such as control buses can cause major problems if they are not implemented using approved methods.

Typically, with control buses crossing clock domains, designers implement gray code schemes to handle such issues. Using a gray-encoded implementation for control bus signals ensures that only one bit of the control signal changes during any one clock cycle. For debug and analysis of the gray encoding check and other functional checks, see *Dealing with Functional Checks*.

#### Fixing Violations Related to Reset Synchronization and Deassertion

| Rule               | Violation Reported                                                                 |  |

|--------------------|------------------------------------------------------------------------------------|--|

| Ar_unsync01        | Reports unsynchronized reset signals in the design                                 |  |

| Ar_sync01          | Reports synchronized reset signals in the design                                   |  |

| Ar_asyncdeassert01 | Reports if reset signal is asynchronously de-asserted                              |  |

| Ar_syncdeassert01  | Reports if reset signal is synchronously de-asserted or<br>not de-asserted at all  |  |

| Reset_sync02       | Reports asynchronous reset signals that are generated in asynchronous clock domain |  |

Check for the following rule violations:

#### Fixing Violations Related to FIFO Recognition and Verification

Check for the Ac\_fifo01 and Ac\_sync\_group rule violations.

SpyGlass can automatically identify FIFOs. FIFO recognition may produce following results:

- Fully recognized FIFOs: This is the case if memory and pointers of a FIFO are identified

- Partially recognized FIFOs/Memory: A 2-dimensional memory or a lib/ sglib memory identified by SpyGlass for which read/write pointers were not identified.

- Disabled: When fa\_msgmode is set to none.

FIFO recognition will help SpyGlass CDC verification as follows:

Metastability violations reduction (Ac\_unsync02 violations reduction): Typically, a FIFO memory is clocked by write clock and the data is read out of memory in a read domain. This situation creates a clock domain crossing from write domain to the read domain that will potentially be reported as unsynchronized (Ac\_unsync02 violation). FIFO recognition will help in reducing such metastability violations (the crossing will be reported as properly synchronized by Ac\_sync02 rule). You can control FIFO based Ac\_unsync02 filtering with enable\_fifo option. If the option is set to "strict", only fully recognized FIFOs will contribute to Ac\_unsync02 violations reduction. If enable\_fifo is set to "soft", partially recognized FIFOs/Memory will also lead to Ac\_unsync02 violations reduction. Reading data out of a memory is not necessarily safe and may be subject to metastability; so usage of enable\_fifo set to soft is not advised unless you are sure that the control logic around the memories provide sufficient margin between the data being written into the memory and the read request out of the memory. List of FIFOs recognized in a design is given by Rule Ac\_fifo01.

Functional verification of FIFOs: For all fully recognized FIFOs, SpyGlass performs functional check to make sure the FIFO will not overflow or underflow. FIFO overflow/underflow violations are reported in Ac\_fifo01 rule.

SpyGlass recognizes commonly used FIFO architectures where memory and pointer counters can be identified. FIFOs cannot be extracted from a netlist design as the counters are mapped into gate level netlist. SpyGlass provides "fifo" constraint that can be used to provide FIFO attributes that would help FIFO recognition and verification. The fifo constraint can be used to provide FIFO attributes, such as memory and/or pointers in a constraint file (SGDC). Here is an example of "fifo" constraint:

```

fifo -memory "uart top.u13.u4"

```

For debug and closure of FIFO and other functional checks, see *Dealing with Functional Checks*.

#### **Reducing Noise**

You can reduce noise by:

- Setting Parameters

- Setting Constraints

- Filtering Violations in a Spreadsheet

#### **Setting Parameters**

For a particular design or project, set the following parameters to reduce the number of violations:

allow\_combo\_logic

Use this parameter to allow combinational logic between synchronizers.

Combinational logic on a crossing can create a glitch. It is harmless in a synchronous circuit. However, its presence in an asynchronous crossing may cause unwanted pulses causing functional failures.

cdc\_reduce\_pessimism

Use this parameter to filter out violations by setting this parameter to appropriate values.

clock\_reduce\_pessimism

Use this parameter to control clock-domain propagation and consequently control SpyGlass CDC solution violations.

#### **Setting Constraints**

Specify the following constraints to reduce noise:

cdc\_false\_path

Specify this constraint to filter certain unsynchronized crossings in a design. An example of such crossings is configuration and other quasi-static registers that do not need synchronizers.

Using this constraint, you can specify the paths that the Ac\_sync\_group rules should not check for clock crossings. This reduces the number of violations reported on that path. The following is an example of cdc false path:

```

cdc_false_path -from block1.flop1 -to block2.flop2

cdc_false_path -from block1.clk1

cdc_false_path -from config_module::fifo_config_reg[1]

```

The first line filters out the flop1-to-flop2 crossing from Ac\_sync\_group violations. The second constraint eliminates all the crossings from flip-flops controlled by clk1 regardless of their destination flip-flops.

■ reset -sync

If you are using a synchronous reset at the crossing or synchronizer flipflops, you can specify these resets using the reset constraint with sync argument (reset-sync). This allows combinational gates generated due to synchronous reset logic in the crossing or synchronizer path.

By default, synchronous reset gate will be considered as combinational

logic and a crossing will be considered unsynchronized.

#### Filtering Violations in a Spreadsheet

From Ac\_unsync01 and Ac\_unsync02 violations header you can access a spreadsheet view of all violations. In this spreadsheet, you can sort or filter violations based on several criteria (e.g. source or destination clocks, reason of failures, etc.). Explore the violations in the spreadsheet to determine false violations due to configuration registers, unconstrained paths, etc. You can select all such violations and request cdc\_false\_path constraint generation from the spreadsheet window; cdc\_false\_path constraints will prevent these violations from being reported in subsequent runs.

#### **Dealing with Functional Checks**

Functional verification of clock-domain crossings is an important aspect of SpyGlass CDC verification. Many critical bugs causing SoC spins are because of gray-encoding failure, FIFO failure, and other types of functional problems in clock-domain crossings.

Functional checks are more CPU-intensive than structural checks.

#### Focusing on Failed or Partially-Proved Checks

A functional check reports any of the following status:

| Status | Description                                                                                                                                                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAILED | Refers to functional checks that failed.<br>For such cases, SpyGlass provides a simulation trace that<br>you can view in the waveform viewer. To open the<br>waveform viewer, double-click the violation and click the<br>waveform viewer icon. |

| PASSED                | Refers to checks that passed.<br>SpyGlass reports a message for such checks only if<br>fa_msgmode is set to pass or all. These checks are<br>reported with the INFO severity.<br>This status indicates a proper functionality proof of<br>SpyGlass CDC solution.                                                                                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP (Partially Proved) | Refers to checks that could not be concluded.<br>SpyGlass provides the number of cycles that have been<br>explored during which no violation has been found.<br>Similar to passed checks, these checks are reported only<br>if fa_msgmode contains "pp" or "all"; by default both<br>failed and partially proved results are reported.<br>These checks are reported with the WARNING severity.<br>See <i>Dealing with Partially-Proved Checks</i> . |

Focus on failed and partially-proved checks as they may represent real design bugs.

#### **Dealing with Partially-Proved Checks**

Set the fa\_atime parameter to increase the amount of time that SpyGlass spends on validating a single property.

#### **Dealing with Long Run Times**

Formal verification is exhaustive and involves complex functional analysis of a design. The complexity of functional analysis increase with the number of asynchronous clocks in a design.

It is recommended to perform functional verification only where it is required. Avoiding unnecessary functional verification requires *Creating SpyGlass CDC Setup* properly and *Reducing Noise*.

You can deal with long run times in the following ways:

- Constraining Resets

- Dealing With Clock Frequencies

#### **Constraining Resets**

Consider a synchronous reset always converges with a data/control signal through a simple gate, such as an AND gate. This type of convergence,

although reported by *Ac\_conv01* and *Ac\_conv02*, can be considered as safe as long as the reset is static.

In this case, you should constraint the synchronous reset by using the reset -sync constraint. By doing so, you can reduce the number of  $Ac\_conv01$  and  $Ac\_conv02$  violations reported because of synchronous reset convergence. This consequently reduces the run time by preventing formal verification of such convergences.

#### **Dealing With Clock Frequencies**

Clock frequencies may greatly affect the complexity of functional analysis.

To understand how clock frequencies affect the functional analysis process, consider two clocks running with the 17 ns period and 13 ns period, respectively.

If the rising edges of the two clocks are aligned at the time 0 ns, the next time the rising edges will again be aligned corresponds to 221 ns (the LCM of two clock periods). This means that the design behaves asynchronously for 221 ns.

Any functional analysis that repeats itself many times (for proving a property, for example) analyzes the design for at least this period of time. This means it performs many evaluations of logic in the design. This time period is called the *Design Virtual Cycle*. A high design virtual cycle makes it hard to verify design functionality.

In some cases, if functional analysis enter into long design runs, modify clock periods to reduce the LCM. Consider the following example.

The device A has two asynchronous clocks:  $clk_33$  (clock period - 33 ns) and  $clk_100$  (clock period - 100 ns). If you specify these clock periods in an SGDC file, the LCM of the two clock periods is 3300 ns (33x100), which is quite large.

If you specify the 100 ns clock in the SGDC as the 99 ns clock, the design virtual cycle reduces to 99 ns. Note that changing the clock frequency by this amount affects the behavior of the design, and therefore the change should not be considered unless necessary.

SpyGlass reports the design virtual cycle in terms of the number of fastest clock cycles and the number of non-overlapping edges of all clocks covered by the design virtual cycle.

Note that the gray-encoding check is a relatively local check as the logic for

gray encoding is purely combinatorial and should not depend on the frequency. In this case, frequency numbers are not important. If frequency/period information is not provided, then SpyGlass assumes all clocks (clocks for which a period is not defined) as having a 10 ns period.

#### **Debugging Functional Checks**

A failed functional check generates a waveform indicating the circumstances of the failure.

To view the waveform viewer, double-click on the violation and click the waveform viewer icon.

Initially, a small set of signals are loaded in the waveform viewer. These signals are a good starting point for debugging. To check the signals in the vicinity of a signal, right-click on that signal and select the *fan-in* option from the shortcut menu. Select all or part of these signals and click *OK* to load their waveform in the viewer.

Note that you can cross-probe between the waveform viewer and the RTL-viewer.

#### **Removing False Violations of Functional Checks**

False violations appear if the design is not constrained properly or SpyGlass considers an inappropriate initial state of the design.

#### **Constraining the Design Properly**

Reset signals are used to initialize the design and they are usually disabled during functional checks. For example, a gray-encoding check may fail due to a reset signal being asserted in the middle of a binary count.

To prevent functional checks failure due to reset toggling, define the reset signal by using the reset constraint in an SGDC file.

If you want the reset to be considered as any other input during function check, declare the reset as soft by specifying the -soft argument with the reset constraint.

#### Specifying the Correct Initial State of the Design

Validate the Ac\_initstate01 rule message to know the initial state used

during functional verification.

Functional checks may fail or pass depending on the initial states considered by SpyGlass.

#### Waiving Violations

It is recommended to use the *cdc\_false\_path* constraint to reduce the number of false violations.

However, if you want to remove a specific violation that does not have any global impact of discarding a path, waive that violation. For example, you may waive a *Clock\_info03a* violation.

You can waive violations before or after SpyGlass analysis, as described below:

- Before analysis, specify the waive constraint to waive violations on a block that you do not want to analyze.

- After analysis, waive a violation that are safe to be ignored.

**NOTE:** Apply waivers to only those rules that do not directly involve a synchronizer.

## **Performing SoC-Level CDC Verification**

Run the *cdc\_verify\_struct* goal to perform SpyGlass CDC verification on the SoC.

If you are using the *SpyGlass CDC Hierarchical Verification Flow*, specify the SGDC files representing the abstract views of blocks with the SoC-level files while performing SoC-level verification.

This step verifies all structural issues in SpyGlass CDC solution on the SoC.

All violations, including those from the rules *Ac\_unsync01*, *Ac\_unsync02*, *Ac\_conv01*, *Ac\_conv02*, and *Ac\_conv03* should be analyzed and resolved.

## Signing-Off SpyGlass CDC Verification

Open SpyGlass CDC report from the GUI pull-down menu,

Report->clock-reset->CDC-report, and review the content as follow

- Examine the assumptions; the SpyGlass CDC report header contains all parameters that make the verification optimistic (e.g. use of allow\_combo\_logic). All optimistic assumptions need to be justified and documented.

- Check if all verification goals have been run and if there are any violations left unsolved. All such violations need to be justified and documented.

## **SpyGlass CDC Hierarchical Verification Flow**

Unlike the *SpyGlass CDC Methodology Flow*, in this flow you use abstract views of blocks while *Performing SoC-Level CDC Verification*. Using abstract views reduce SpyGlass CDC verification run time by focusing on SpyGlass CDC solution issues on block boundaries only.

Use this flow in the following cases:

#### Large SoCs

Performing SpyGlass CDC verification on large SoCs having 100M+ gates and many clocks can be time consuming. For such designs, use the SpyGlass CDC hierarchical verification flow for faster SpyGlass CDC verification sign-off.

#### Distributed Environment for SoC Development

In such environment, IPs are developed or acquired from different design teams and SoC integration happens in a different location. In such cases:

- Block owners verify blocks and handoff the abstract views of these blocks (along with the blocks) to the SoC integration team.

- □ SoC integration team uses abstract views without worrying about the block content.

If the abstract view of some blocks is not available, the SoC team does the following:

- Generate the abstract views for such blocks.

- Migrate constraints from top level to block level. For details, see *Generating Block-Level Constraints from SoC Level*.

- Consider such blocks as glue logic by specifying them with the ip\_block constraint.

The following figure illustrates this flow:

FIGURE 5. Abstract Bottom Up SoC level CDC verification flow

The following table shows the steps and their corresponding goals used in this flow:

| Steps                                                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Goals                 |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| <i>Identifying the Blocks to Abstract in SpyGlass CDC</i> | Identify the blocks whose abstract<br>view should be created.<br>This abstract view is used while<br><i>Performing SoC-Level CDC</i><br><i>Verification</i> .                                                                                                                                                                                                                                                                                                                                                    | -                     |

| Creating SpyGlass CDC Setup                               | Capture block constraints, such as clocks, input domains, resets, and other assumptions on the inputs                                                                                                                                                                                                                                                                                                                                                                                                            | cdc_setup_check       |

| Verifying SpyGlass CDC Setup                              | Check for the correctness and completeness of the setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cdc_setup_check       |

| Performing Clocks and Reset<br>Integrity Checks           | Fix clock and reset integrity problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | clock_reset_integrity |

| Performing Block-Level CDC<br>Verification                | Verify all the sub blocks.<br>The input constraints captured<br>while <i>Creating SpyGlass CDC</i><br><i>Setup</i> dictate the quality of the<br>block verification. If an input is in<br>a given domain then it should feed<br>the flip-flops in the same domain<br>or be synchronized before being<br>used in a different domain.<br>However, on the output side,<br>constraints, such as domains may<br>be neglected, as those will be<br>identified during verification and<br>generation of abstract model. | cdc_verif             |

| Generating Abstract View in<br>SpyGlass CDC               | Create an abstract view for a block                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | cdc_abstract          |

| Performing Abstract View<br>Validation in SpyGlass CDC    | Validate block assumptions<br>against the higher-level<br>hierarchy constraints                                                                                                                                                                                                                                                                                                                                                                                                                                  | cdc_abstract_validate |

#### **TABLE 1** Steps in SpyGlass CDC Hierarchical Verification Flow

| Steps                                    | Summary                                                              | Goals            |

|------------------------------------------|----------------------------------------------------------------------|------------------|

| Performing SoC-Level CDC<br>Verification | Verify the SoC using the abstract view of blocks                     | cdc_verif_struct |

| Signing-Off SpyGlass CDC<br>Verification | View reports and sign-off<br>SpyGlass CDC Verification on the<br>SoC | -                |

#### **TABLE 1** Steps in SpyGlass CDC Hierarchical Verification Flow

## Identifying the Blocks to Abstract in SpyGlass CDC

Decide the blocks to verify before moving to the verification of a higherlevel hierarchy.

Typically, for a full SoC, verifying the first level instances (often referred to as a clusters, or sub-modules) before moving to the SoC verification is good enough. However, if the size and complexity of a sub-module is so that the verification may take long time, 5M+ gates with dozens of asynchronous clocks, then it is a good idea to further partition the sub-module for verification before verifying the SoC.

Note that it is important to consider single clock blocks while verifying SpyGlass CDC solution of a design instantiating the block. For example, if an input of a single clock block is coming from another clock domain, then the block must synchronize the input before using it. Furthermore, if a multi-flop synchronizer feeds into a single clock module, it may converge with other multi-flop synchronizers within the module or further down after exiting the block.

## **Generating Abstract View in SpyGlass CDC**

Run the *cdc\_abstract* goal to generate the abstract view of a block. This goal runs the *Ac\_abstract01* rule that generates the abstract view of a block.

The abstract view is an SGDC file that is used by the SoC owner while *Performing SoC-Level CDC Verification*. The abstract view captures all the

block-level constraints. It also propagates synchronizer information (crossing information) to IOs by capturing this information in abstract port constraints.

**NOTE:** Abstraction is performed on a top-level module, hence set\_option top <blockname> must be specified during block level verification run.

#### **Quality of Abstract View**

The quality of an abstract view depends on the quality of *Performing Block-Level CDC Verification*.

If a block is not properly verified or the block constraints are incorrect or incomplete, clocks, domains, and other information assumed at block boundaries may be incorrect. This may result in false violations and mask real design issues.

Although SpyGlass CDC solution provides utilities to generate block assumptions (clocks, domains, etc.) automatically, this is not recommended for SpyGlass CDC verification sign-off. The user can review the abstract model, and adjust the blocks assumptions if needed

## Performing Abstract View Validation in SpyGlass CDC

Run the *cdc\_abstract\_validate* goal after providing the block and its abstract view by using the following command:

sgdc -import <block-name> <block-abstract-view-SGDC-file>

During abstract view validation, the abstract view of a block is validated in context of an SoC. Provide the abstract view of a block by specifying the following command in the SoC-level SGDC file:

The abstract view contains block-level assumptions, such as clocks, resets, and domains on block inputs. These assumptions are validated with the constraints of the higher-level hierarchy.

The following points describe some examples of inconsistencies reported during abstract view validation:

A block constraint associates two inputs to the same domain. However, these domains are controlled by different clocks in the higher-level hierarchy. Such issues are captured and fixed during validation. An abstract view defines a port to be equal to 1, while the higher-level block constraints causes the port to be equal to 0.

#### **Approach to Fix Violations During Abstract View Validation**

For a correct verification of an SoC, all violations reported during abstract block validation should be analyzed and fixed.

There are the following ways to fix these violations:

- If the SoC-level constraints are incorrect that caused the violations In this case, modify these constraints and rerun the *cdc\_validation* goal.

- Block-level constraints are incorrect

In this case, modify the incorrect constraints and repeat the following steps:

- Performing Block-Level CDC Verification

- Generating Abstract View in SpyGlass CDC

- D Performing Abstract View Validation in SpyGlass CDC

#### **Examples of Fixing Violations During Abstract View Validation**

#### Example 1

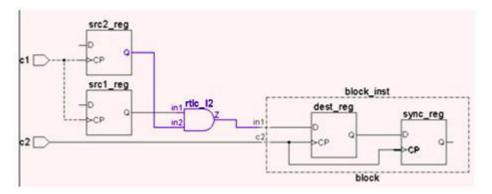

Consider the following schematic of a design:

FIGURE 6. Example of Abstract View Validation

In the above schematic, block is correctly synchronizing an asynchronous signal using multi-flop synchronizer. However, the transmitter at the toplevel is driving a combinational logic that is failing the block assumption that an asynchronous source signal should not be having combinational logic (it should be glitch free).

To fix such violation, latch the source signal in a flip-flop (on source domain) before it is sent to receiver block.

#### Example 2

The following example shows the violation that should be fixed in setup:

SGDC\_set\_case\_analysis\_validation02 Warning test.v 2720 2 Simulated value '0' reaches to port 'txhcfc\_en[3:0]' of block instance 'test.block\_inst (block: 'block') however no set\_case\_analysis is specified in block level constraint file

The above violation is suggesting that top-level constant is reaching the block port and in block constraints, set\_case\_analysis is not defined on the port. This will result in inaccurate SpyGlass CDC solution analysis of the block, because in absence of correct constants, either it may ne noisier or may miss certain violations.

**NOTE:** *Perform setup and setup-check at SoC level, prior to block validation step.*

### Points to be Considered in the Hierarchical CDC Flow

Consider the following points:

- Loss of Information While Generating the Abstract View

- Functional checks in an abstraction-based bottom-up methodology

#### Loss of Information While Generating the Abstract View

Generating Abstract View in SpyGlass CDC results in loss of information.

During abstraction, the functionality information of the block is removed and the crossing information is preserved. Therefore, you cannot use abstract views to verify design functionality. However, you can verify metastability, convergence, block-to-block or block-to-top connectivity, and other structural issues.

Abstract views generated by SpyGlass CDC contain information using which you can perform:

- All structural synchronization checks

- Limited checks for multi-sampled signals (reported by *Clock\_sync05*) and multi-synchronized crossings (reported by *Clock\_sync09*).

#### Functional checks in an abstraction-based bottom-up methodology

Typically, synchronization circuitry is implemented in, sub-modules as opposed to a top-level SoC design. Therefore, verifying the functionality of sub-modules may be sufficient to cover critical functional issues such as gray encoding, FIFO correctness, etc.